Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                               |

| Number of I/O              | 24                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 5x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 28-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f913-e-ss |

| Device    | Program Data Memory I/O 10-bit A/D |                 | LCD<br>(segment   | ССР | Timers |                      |     |          |  |

|-----------|------------------------------------|-----------------|-------------------|-----|--------|----------------------|-----|----------|--|

| Device    | Flash<br>(words/bytes)             | SRAM<br>(bytes) | EEPROM<br>(bytes) | 1/0 | (ch)   | (segment<br>drivers) | CCP | 8/16-bit |  |

| PIC16F913 | 4K/7K                              | 256             | 256               | 24  | 5      | 16 <sup>(1)</sup>    | 1   | 2/1      |  |

| PIC16F914 | 4K/7K                              | 256             | 256               | 35  | 8      | 24                   | 2   | 2/1      |  |

| PIC16F916 | 8K/14K                             | 352             | 256               | 24  | 5      | 16 <sup>(1)</sup>    | 1   | 2/1      |  |

| PIC16F917 | 8K/14K                             | 352             | 256               | 35  | 8      | 24                   | 2   | 2/1      |  |

| PIC16F946 | 8K/14K                             | 336             | 256               | 53  | 8      | 42                   | 2   | 2/1      |  |

**Note 1:** COM3 and SEG15 share the same physical pin on the PIC16F913/916, therefore SEG15 is not available when using 1/4 multiplex displays.

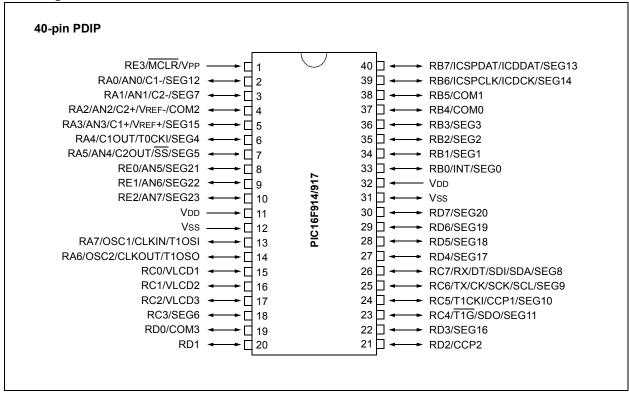

## Pin Diagrams - PIC16F914/917, 40-Pin

FIGURE 2-3: PIC16F913/916 SPECIAL FUNCTION REGISTERS

|                   | File    |                    | File    |                    | File    |                         | File    |

|-------------------|---------|--------------------|---------|--------------------|---------|-------------------------|---------|

| 727               | Address |                    | Address | 72.                | Address | 728                     | Address |

| ndirect addr. (1) | 00h     | Indirect addr. (1) | 80h     | Indirect addr. (1) | 100h    | Indirect addr. (1)      | 180h    |

| TMR0              | 01h     | OPTION_REG         | 81h     | TMR0               | 101h    | OPTION_REG              | 181h    |

| PCL               | 02h     | PCL                | 82h     | PCL                | 102h    | PCL                     | 182h    |

| STATUS            | 03h     | STATUS             | 83h     | STATUS             | 103h    | STATUS                  | 183h    |

| FSR               | 04h     | FSR                | 84h     | FSR                | 104h    | FSR                     | 184h    |

| PORTA             | 05h     | TRISA              | 85h     | WDTCON             | 105h    |                         | 185h    |

| PORTB             | 06h     | TRISB              | 86h     | PORTB              | 106h    | TRISB                   | 186h    |

| PORTC             | 07h     | TRISC              | 87h     | LCDCON             | 107h    |                         | 187h    |

|                   | 08h     |                    | 88h     | LCDPS              | 108h    |                         | 188h    |

| PORTE             | 09h     | TRISE              | 89h     | LVDCON             | 109h    |                         | 189h    |

| PCLATH            | 0Ah     | PCLATH             | 8Ah     | PCLATH             | 10Ah    | PCLATH                  | 18Ah    |

| INTCON            | 0Bh     | INTCON             | 8Bh     | INTCON             | 10Bh    | INTCON                  | 18Bh    |

| PIR1              | 0Ch     | PIE1               | 8Ch     | EEDATL             | 10Ch    | EECON1                  | 18Ch    |

| PIR2              | 0Dh     | PIE2               | 8Dh     | EEADRL             | 10Dh    | EECON2 <sup>(1)</sup>   | 18Dh    |

| TMR1L             | 0Eh     | PCON               | 8Eh     | EEDATH             | 10Eh    | Reserved                | 18Eh    |

| TMR1H             | 0Fh     | OSCCON             | 8Fh     | EEADRH             | 10Fh    | Reserved                | 18Fh    |

| T1CON             | 10h     | OSCTUNE            | 90h     | LCDDATA0           | 110h    |                         | 190h    |

| TMR2              | 11h     | ANSEL              | 91h     | LCDDATA1           | 111h    |                         |         |

| T2CON             | 12h     | PR2                | 92h     |                    | 112h    |                         |         |

| SSPBUF            | 13h     | SSPADD             | 93h     | LCDDATA3           | 113h    |                         |         |

| SSPCON            | 14h     | SSPSTAT            | 94h     | LCDDATA4           | 114h    |                         |         |

| CCPR1L            | 15h     | WPUB               | 95h     |                    | 115h    |                         |         |

| CCPR1H            | 16h     | IOCB               | 96h     | LCDDATA6           | 116h    |                         |         |

| CCP1CON           | 17h     | CMCON1             | 97h     | LCDDATA7           | 117h    |                         |         |

| RCSTA             | 18h     | TXSTA              | 98h     |                    | 118h    |                         |         |

| TXREG             | 19h     | SPBRG              | 99h     | LCDDATA9           | 119h    | General                 |         |

| RCREG             | 1Ah     |                    | 9Ah     | LCDDATA10          | 11Ah    | Purpose                 |         |

|                   | 1Bh     |                    | 9Bh     |                    | 11Bh    | Register <sup>(2)</sup> |         |

|                   | 1Ch     | CMCON0             | 9Ch     | LCDSE0             | 11Ch    |                         |         |

|                   | 1Dh     | VRCON              | 9Dh     | LCDSE1             | 11Dh    | 96 Bytes                |         |

| ADRESH            | 1Eh     | ADRESL             | 9Eh     |                    | 11Eh    |                         |         |

| ADCON0            | 1Fh     | ADCON1             | 9Fh     |                    | 11Fh    |                         |         |

|                   | 20h     |                    | A0h     |                    | 120h    |                         |         |

|                   |         | General            |         | General            |         |                         |         |

| General           |         | Purpose            |         | Purpose            |         |                         |         |

| Purpose           |         | Register           |         | Register           |         |                         |         |

| Register          |         | 00 D 4             |         | 00 P. (            |         |                         |         |

| 00.5.4            |         | 80 Bytes           |         | 80 Bytes           |         |                         |         |

| 96 Bytes          |         |                    | EFh     |                    | 16Fh    |                         | 1EFh    |

|                   |         | accesses           | F0h     | accesses           | 170h    | accesses                | 1F0h    |

|                   | 7Fh     | 70h-7Fh            | FFh     | 70h-7Fh            | 17Fh    | 70h-7Fh                 | 1FFh    |

| Bank 0            | •       | Bank 1             | •       | Bank 2             |         | Bank 3                  |         |

**Note 1:** Not a physical register.

**2:** On the PIC16F913, unimplemented data memory locations, read as '0'.

### 2.2.2.1 STATUS Register

The STATUS register, shown in Register 2-1, contains:

- · the arithmetic status of the ALU

- · the Reset status

- the bank select bits for data memory (SRAM)

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (see Section 17.0 "Instruction Set Summary").

Note 1: The C and DC bits operate as Borrow and Digit Borrow out bits, respectively, in subtraction.

### REGISTER 2-1: STATUS: STATUS REGISTER

| R/W-0 | R/W-0 | R/W-0 | R-1 | R-1 | R/W-x | R/W-x             | R/W-x            |

|-------|-------|-------|-----|-----|-------|-------------------|------------------|

| IRP   | RP1   | RP0   | TO  | PD  | Z     | DC <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7 |       |       |     |     |       |                   | bit 0            |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7 **IRP:** Register Bank Select bit (used for indirect addressing)

1 = Bank 2, 3 (100h-1FFh) 0 = Bank 0, 1 (00h-FFh)

bit 6-5 **RP<1:0>:** Register Bank Select bits (used for direct addressing)

00 = Bank 0 (00h-7Fh) 01 = Bank 1 (80h-FFh) 10 = Bank 2 (100h-17Fh) 11 = Bank 3 (180h-1FFh)

bit 4 TO: Time-out bit

1 = After power-up, CLRWDT instruction or SLEEP instruction

0 = A WDT time-out occurred

bit 3 **PD:** Power-down bit

1 = After power-up or by the CLRWDT instruction

0 = By execution of the SLEEP instruction

bit 2 **Z**: Zero bit

1 = The result of an arithmetic or logic operation is zero0 = The result of an arithmetic or logic operation is not zero

bit 1 DC: Digit Carry/Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)(1)

1 = A carry-out from the 4th low-order bit of the result occurred

0 = No carry-out from the 4th low-order bit of the result

bit 0 C: Carry/Borrow bit<sup>(1)</sup> (ADDWF, ADDLW, SUBLW, SUBWF instructions)<sup>(1)</sup>

1 = A carry-out from the Most Significant bit of the result occurred

0 = No carry-out from the Most Significant bit of the result occurred

Note 1: For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order bit of the source register.

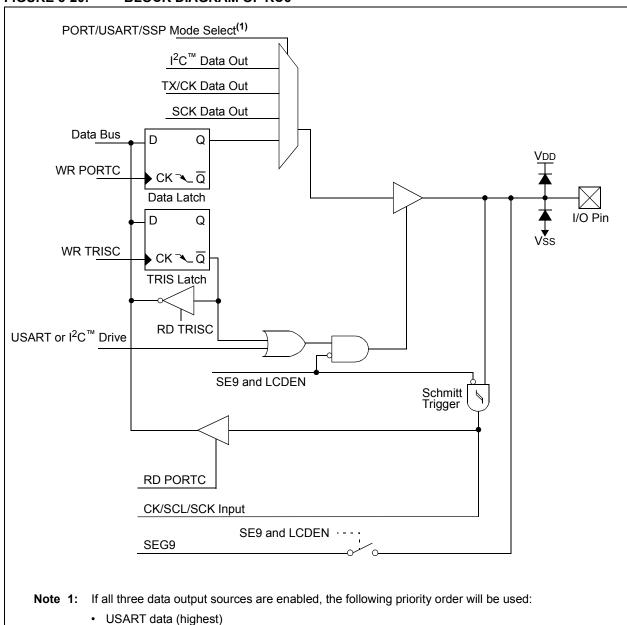

### 3.5.1.7 RC6/TX/CK/SCK/SCL/SEG9

Figure 3-20 shows the diagram for this pin. The RC6 pin is configurable to function as one of the following:

- a general purpose I/O

- · an asynchronous serial output

- · a synchronous clock I/O

- a SPI clock I/O

- an I<sup>2</sup>C data I/O

- · an analog output for the LCD

## FIGURE 3-20: BLOCK DIAGRAM OF RC6

SSP data

PORT data (lowest)

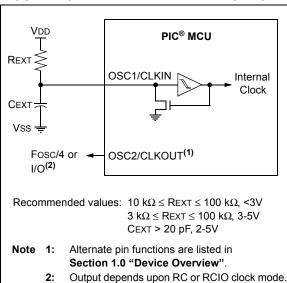

#### 4.4.4 EXTERNAL RC MODES

The external Resistor-Capacitor (RC) modes support the use of an external RC circuit. This allows the designer maximum flexibility in frequency choice while keeping costs to a minimum when clock accuracy is not required. There are two modes: RC and RCIO.

In RC mode, the RC circuit connects to OSC1. OSC2/CLKOUT outputs the RC oscillator frequency divided by 4. This signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements. Figure 4-5 shows the external RC mode connections.

FIGURE 4-5: EXTERNAL RC MODES

In RCIO mode, the RC circuit is connected to OSC1. OSC2 becomes an additional general purpose I/O pin.

The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. Other factors affecting the oscillator frequency are:

- · threshold voltage variation

- · component tolerances

- · packaging variations in capacitance

The user also needs to take into account variation due to tolerance of external RC components used.

#### 4.5 Internal Clock Modes

The Oscillator module has two independent, internal oscillators that can be configured or selected as the system clock source.

- 1. The **HFINTOSC** (High-Frequency Internal Oscillator) is factory calibrated and operates at 8 MHz. The frequency of the HFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 4-2).

- The LFINTOSC (Low-Frequency Internal Oscillator) is uncalibrated and operates at 31 kHz.

The system clock speed can be selected via software using the Internal Oscillator Frequency Select bits IRCF<2:0> of the OSCCON register.

The system clock can be selected between external or internal clock sources via the System Clock Selection (SCS) bit of the OSCCON register. See **Section 4.6** "Clock Switching" for more information.

### 4.5.1 INTOSC AND INTOSCIO MODES

The INTOSC and INTOSCIO modes configure the internal oscillators as the system clock source when the device is programmed using the oscillator selection or the FOSC<2:0> bits in the Configuration Word register (CONFIG). See Section 16.0 "Special Features of the CPU" for more information.

In **INTOSC** mode, OSC1/CLKIN is available for general purpose I/O. OSC2/CLKOUT outputs the selected internal oscillator frequency divided by 4. The CLKOUT signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements.

In **INTOSCIO** mode, OSC1/CLKIN and OSC2/CLKOUT are available for general purpose I/O.

### 4.5.2 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a factory calibrated 8 MHz internal clock source. The frequency of the HFINTOSC can be altered via software using the OSCTUNE register (Register 4-2).

The output of the HFINTOSC connects to a postscaler and multiplexer (see Figure 4-1). One of seven frequencies can be selected via software using the IRCF<2:0> bits of the OSCCON register. See Section 4.5.4 "Frequency Select Bits (IRCF)" for more information.

The HFINTOSC is enabled by selecting any frequency between 8 MHz and 125 kHz by setting the IRCF<2:0> bits of the OSCCON register  $\neq$  000. Then, set the System Clock Source (SCS) bit of the OSCCON register to '1' or enable Two-Speed Start-up by setting the IESO bit in the Configuration Word register (CONFIG) to '1'.

The HF Internal Oscillator (HTS) bit of the OSCCON register indicates whether the HFINTOSC is stable or not.

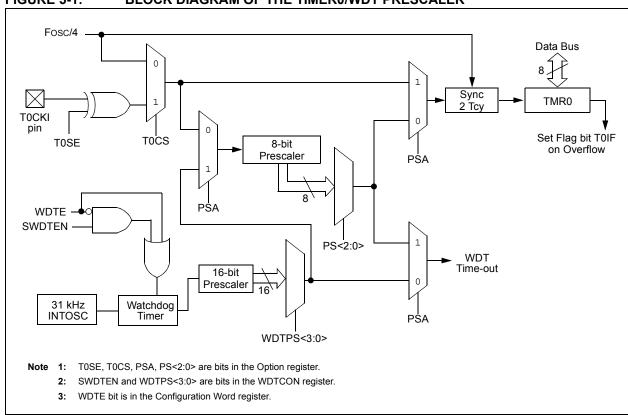

## 5.0 TIMERO MODULE

The Timer0 module is an 8-bit timer/counter with the following features:

- 8-bit timer/counter register (TMR0)

- 8-bit prescaler (shared with Watchdog Timer)

- · Programmable internal or external clock source

- · Programmable external clock edge selection

- · Interrupt on overflow

Figure 5-1 is a block diagram of the Timer0 module.

### 5.1 Timer0 Operation

When used as a timer, the Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

#### 5.1.1 8-BIT TIMER MODE

When used as a timer, the Timer0 module will increment every instruction cycle (without prescaler). Timer mode is selected by clearing the T0CS bit of the OPTION register to '0'.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

**Note:** The value written to the TMR0 register can be adjusted, in order to account for the two instruction cycle delay when TMR0 is written.

### 5.1.2 8-BIT COUNTER MODE

When used as a counter, the Timer0 module will increment on every rising or falling edge of the T0CKI pin. The incrementing edge is determined by the T0SE bit of the Option register. Counter mode is selected by setting the T0CS bit of the Option register to '1'.

## FIGURE 5-1: BLOCK DIAGRAM OF THE TIMERO/WDT PRESCALER

# 5.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A single software programmable prescaler is available for use with either Timer0 or the Watchdog Timer (WDT), but not both simultaneously. The prescaler assignment is controlled by the PSA bit of the Option register. To assign the prescaler to Timer0, the PSA bit must be cleared to a '0'.

There are 8 prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be assigned to the WDT module.

The prescaler is not readable or writable. When assigned to the Timer0 module, all instructions writing to the TMR0 register will clear the prescaler.

When the prescaler is assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT.

# 5.1.3.1 Switching Prescaler Between Timer0 and WDT Modules

As a result of having the prescaler assigned to either Timer0 or the WDT, it is possible to generate an unintended device Reset when switching prescaler values. When changing the prescaler assignment from Timer0 to the WDT module, the instruction sequence shown in Example 5-1, must be executed.

# EXAMPLE 5-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

|                   | (IIIVIEF        | RU 	o VVDI                 |

|-------------------|-----------------|----------------------------|

| BANKSEL<br>CLRWDT | TMR0            | ;<br>;Clear WDT            |

| CLRF              | TMR0            | ;Clear TMR0 and ;prescaler |

| BANKSEL           | OPTION_REG      | ;                          |

| BSF               | OPTION_REG, PSA | ;Select WDT                |

| CLRWDT            |                 | ;                          |

| MOVLW             | b'11111000'     | ;Mask prescaler            |

| ANDWF             | OPTION REG, W   | ;bits                      |

| IORLW             | b'00000101'     | ;Set WDT prescaler         |

| MOVWF             | OPTION_REG      | ;to 1:32                   |

When changing the prescaler assignment from the WDT to the Timer0 module, the following instruction sequence must be executed (see Example 5-2).

# EXAMPLE 5-2: CHANGING PRESCALER (WDT $\rightarrow$ TIMER0)

| CLRWDT  |              | ;Clear WDT and ;prescaler |

|---------|--------------|---------------------------|

|         |              | , presenter               |

| BANKSEL | OPTION_REG   | ;                         |

| MOVLW   | b'11110000'  | ;Mask TMR0 select and     |

| ANDWF   | OPTION_REG,W | ;prescaler bits           |

| IORLW   | b'00000011'  | ;Set prescale to 1:16     |

| MOVWF   | OPTION_REG   | ;                         |

|         |              |                           |

#### 5.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The T0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The T0IF bit must be cleared in software. The Timer0 interrupt enable is the T0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the    |

|-------|-----------------------------------------|

|       | processor from Sleep since the timer is |

|       | frozen during Sleep.                    |

# 5.1.5 USING TIMERO WITH AN EXTERNAL CLOCK

When Timer0 is in Counter mode, the synchronization of the T0CKI input and the Timer0 register is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, the high and low periods of the external clock source must meet the timing requirements as shown in Section 19.0 "Electrical Specifications"

## REGISTER 9-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER

| R/W-0 | R/W-0 | R/W-0               | R/W-0 | U-0 | R/W-0 | R-1  | R/W-0 |

|-------|-------|---------------------|-------|-----|-------|------|-------|

| CSRC  | TX9   | TXEN <sup>(1)</sup> | SYNC  | _   | BRGH  | TRMT | TX9D  |

| bit 7 |       |                     |       |     |       |      | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 CSRC: Clock Source Select bit

Asynchronous mode:

Don't care

Synchronous mode:

1 = Master mode (clock generated internally from BRG)

0 = Slave mode (clock from external source)

bit 6 **TX9:** 9-bit Transmit Enable bit

1 = Selects 9-bit transmission0 = Selects 8-bit transmission

-----(1)

bit 5 **TXEN:** Transmit Enable bit<sup>(1)</sup>

1 = Transmit enabled0 = Transmit disabled

bit 4 SYNC: AUSART Mode Select bit

1 = Synchronous mode0 = Asynchronous mode

bit 3 **Unimplemented:** Read as '0'

bit 2 BRGH: High Baud Rate Select bit

Asynchronous mode:

1 = High speed

0 = Low speed

Synchronous mode:

Unused in this mode

bit 1 TRMT: Transmit Shift Register Status bit

1 = TSR empty

0 = TSR full

bit 0 **TX9D:** Ninth bit of Transmit Data

Can be address/data bit or a parity bit.

Note 1: SREN/CREN overrides TXEN in Sync mode.

## REGISTER 9-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER<sup>(1)</sup>

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R-0  | R-0  | R-x   |

|-------|-------|-------|-------|-------|------|------|-------|

| SPEN  | RX9   | SREN  | CREN  | ADDEN | FERR | OERR | RX9D  |

| bit 7 |       |       |       |       |      |      | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 SPEN: Serial Port Enable bit

1 = Serial port enabled (configures RX/DT and TX/CK pins as serial port pins)

0 = Serial port disabled (held in Reset)

bit 6 **RX9:** 9-bit Receive Enable bit

1 = Selects 9-bit reception0 = Selects 8-bit reception

bit 5 SREN: Single Receive Enable bit

Asynchronous mode:

Don't care

Synchronous mode – Master:

1 = Enables single receive

0 = Disables single receive

This bit is cleared after reception is complete.

Synchronous mode - Slave

Don't care

bit 4 CREN: Continuous Receive Enable bit

Asynchronous mode:

1 = Enables receiver

0 = Disables receiver

Synchronous mode:

1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)

0 = Disables continuous receive

bit 3 ADDEN: Address Detect Enable bit

Asynchronous mode 9-bit (RX9 = 1):

1 = Enables address detection, enable interrupt and load the receive buffer when RSR<8> is set

0 = Disables address detection, all bytes are received and ninth bit can be used as parity bit

Asynchronous mode 8-bit (RX9 = 0):

Don't care

Synchronous mode:

Must be set to '0'

bit 2 FERR: Framing Error bit

1 = Framing error (can be updated by reading RCREG register and receive next valid byte)

0 = No framing error

bit 1 **OERR:** Overrun Error bit

1 = Overrun error (can be cleared by clearing bit CREN)

0 = No overrun error

bit 0 **RX9D:** Ninth bit of Received Data

This can be address/data bit or a parity bit and must be calculated by user firmware.

### 9.3.1.4 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the AUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCSTA register) or the Continuous Receive Enable bit (CREN of the RCSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit of the PIR1 register is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCREG. The RCIF bit remains set as long as there are un-read characters in the receive FIFO.

## 9.3.1.5 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

#### 9.3.1.6 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREG is read to access the FIFO. When this happens the OERR bit of the RCSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCREG. If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCSTA register.

#### 9.3.1.7 Receiving 9-bit Characters

The AUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the AUSART will shift 9-bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the 8 Least Significant bits from the RCREG.

Address detection in Synchronous modes is not supported, therefore the ADDEN bit of the RCSTA register must be cleared.

# 9.3.1.8 Synchronous Master Reception Set-up:

- Initialize the SPBRG register for the appropriate baud rate. Set or clear the BRGH bit, as required, to achieve the desired baud rate.

- Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- If 9-bit reception is desired, set bit RX9.

- Verify address detection is disabled by clearing the ADDEN bit of the RCSTA register.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- Interrupt flag bit RCIF of the PIR1 register will be set when reception of a character is complete.

An interrupt will be generated if the RCIE interrupt enable bit of the PIE1 register was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register.

- If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the AUSART.

### 14.0 SSP MODULE OVERVIEW

The Synchronous Serial Port (SSP) module is a serial interface used to communicate with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The SSP module can operate in one of two modes:

- · Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

Refer to Application Note AN578, "Use of the SSP Module in the Multi-Master Environment" (DS00578).

#### 14.1 SPI Mode

This section contains register definitions and operational characteristics of the SPI module.

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO)

- · Serial Data In (SDI)

- Serial Clock (SCK)

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS)

- Note 1: When the SPI is in Slave mode with SS pin control enabled (SSPM<3:0> bits of the SSPCON register = 0100), the SPI module will reset if the SS pin is set to VDD.

- 2: If the SPI is used in Slave mode with CKE = 1, then the SS pin control must be enabled.

- 3: When the SPI is in Slave mode with \$\overline{SS}\$ pin control enabled (SSPM<3:0> bits of the \$SPCON register = 0100), the state of the \$\overline{SS}\$ pin can affect the state read back from the TRISC<4> bit. The peripheral OE signal from the SSP module into PORTC controls the state that is read back from the TRISC<4> bit (see Section 19.0 "Electrical Specifications" for information on PORTC). If read-write-modify instructions, such as BSF, are performed on the TRISC register while the \$\overline{SS}\$ pin is high, this will cause the TRISC<4> bit to be set, thus disabling the SDO output.

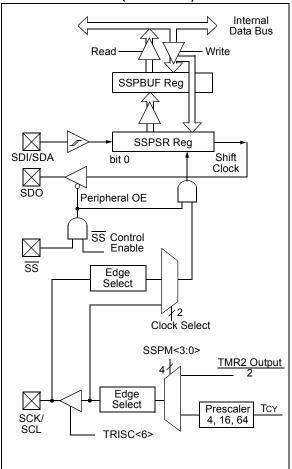

FIGURE 14-1: SSP BLOCK DIAGRAM (SPI MODE)

FIGURE 14-12: CLOCK SYNCHRONIZATION TIMING

TABLE 14-4: SUMMARY OF REGISTERS ASSOCIATED WITH I<sup>2</sup>C™ OPERATION

| Name    | Bit 7              | Bit 6              | Bit 5      | Bit 4        | Bit 3      | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|---------|--------------------|--------------------|------------|--------------|------------|--------|--------|--------|----------------------|---------------------------------|

| INTCON  | GIE                | PEIE               | T0IE       | INTE         | RBIE       | T0IF   | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| LCDCON  | LCDEN              | SLPEN              | WERR       | VLCDEN       | CS1        | CS0    | LMUX1  | LMUX0  | 0001 0011            | 0001 0011                       |

| LCDSE1  | SE15               | SE14               | SE13       | SE12         | SE11       | SE10   | SE9    | SE8    | 0000 0000            | 0000 0000                       |

| PIE1    | EEIE               | ADIE               | RCIE       | TXIE         | SSPIE      | CCP1IE | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| PIR1    | EEIF               | ADIF               | RCIF       | TXIF         | SSPIF      | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| RCSTA   | SPEN               | RX9                | SREN       | CREN         | ADDEN      | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| SSPBUF  | Synchrono          | ous Serial F       | ort Receiv | e Buffer/Tra | ansmit Reg | ister  | •      |        | xxxx xxxx            | uuuu uuuu                       |

| SSPCON  | WCOL               | SSPOV              | SSPEN      | CKP          | SSPM3      | SSPM2  | SSPM1  | SSPM0  | 0000 0000            | 0000 0000                       |

| SSPSTAT | SMP <sup>(1)</sup> | CKE <sup>(1)</sup> | D/Ā        | Р            | S          | R/W    | UA     | BF     | 0000 0000            | 0000 0000                       |

| TRISC   | TRISC7             | TRISC6             | TRISC5     | TRISC4       | TRISC3     | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

**Legend:** – = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the SSP module. **Note 1:** Maintain these bits clear.

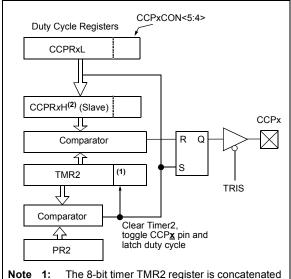

### 15.3 PWM Mode

The PWM mode generates a Pulse-Width Modulated signal on the CCPx pin. The duty cycle, period and resolution are determined by the following registers:

- PR2

- T2CON

- CCPRxL

- CCPxCON

In Pulse-Width Modulation (PWM) mode, the CCP module produces up to a 10-bit resolution PWM output on the CCPx pin. Since the CCPx pin is multiplexed with the PORT data latch, the TRIS for that pin must be cleared to enable the CCPx pin output driver.

**Note:** Clearing the CCPxCON register will relinquish CCPx control of the CCPx pin.

Figure 15-3 shows a simplified block diagram of PWM operation.

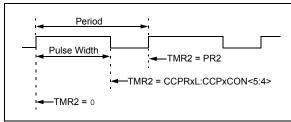

Figure 15-4 shows a typical waveform of the PWM signal.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see **Section 15.3.7** "**Setup for PWM Operation**".

# FIGURE 15-3: SIMPLIFIED PWM BLOCK DIAGRAM

- Note 1: The 8-bit timer TMR2 register is concatenated with the 2-bit internal system clock (Fosc), or 2 bits of the prescaler, to create the 10-bit time base

- 2: In PWM mode, CCPRxH is a read-only register.

The PWM output (Figure 15-2) has a time base (period) and a time that the output stays high (duty cycle).

## FIGURE 15-4: CCP PWM OUTPUT

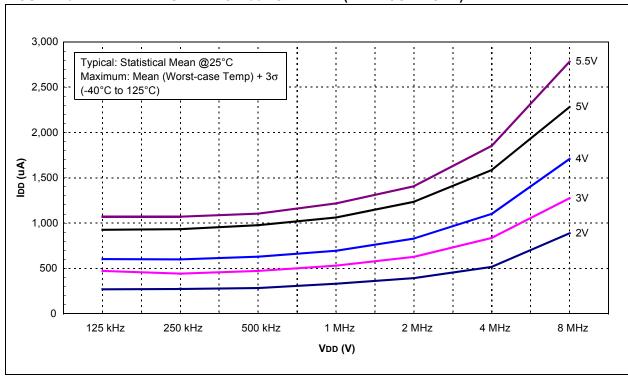

FIGURE 20-12: MAXIMUM IDD vs. Fosc OVER VDD (HFINTOSC MODE)

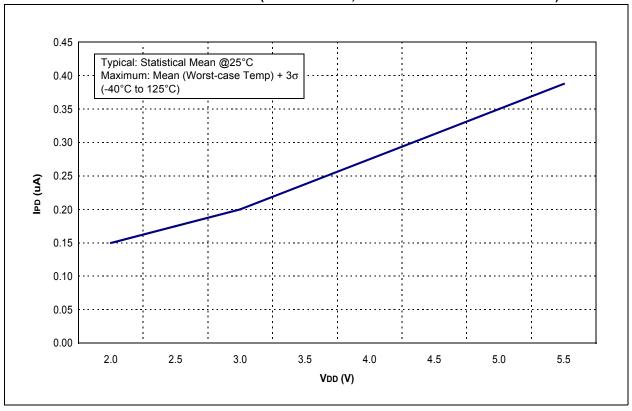

FIGURE 20-13: TYPICAL IPD vs. VDD (SLEEP MODE, ALL PERIPHERALS DISABLED)

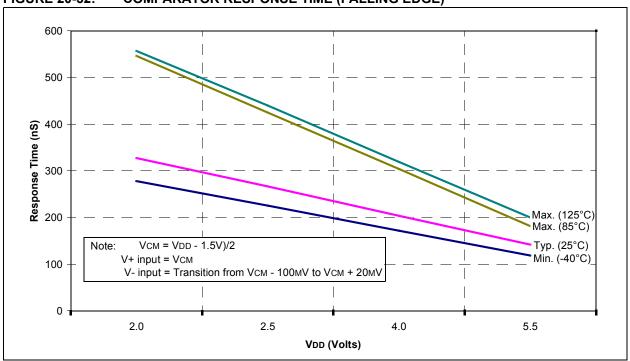

FIGURE 20-32: COMPARATOR RESPONSE TIME (FALLING EDGE)

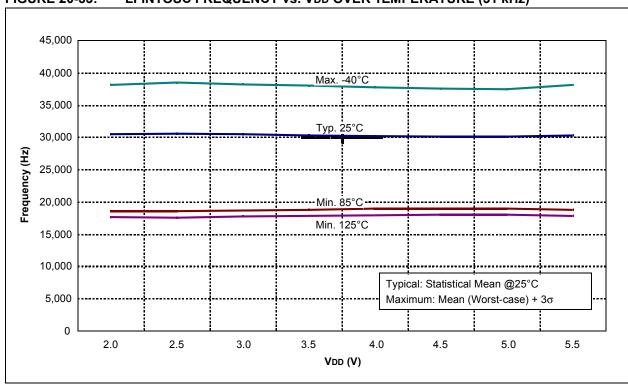

FIGURE 20-33: LFINTOSC FREQUENCY vs. VDD OVER TEMPERATURE (31 kHz)

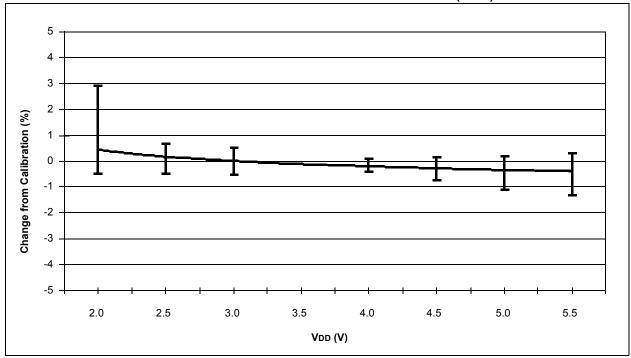

FIGURE 20-38: TYPICAL HFINTOSC FREQUENCY CHANGE vs. VDD (25°C)

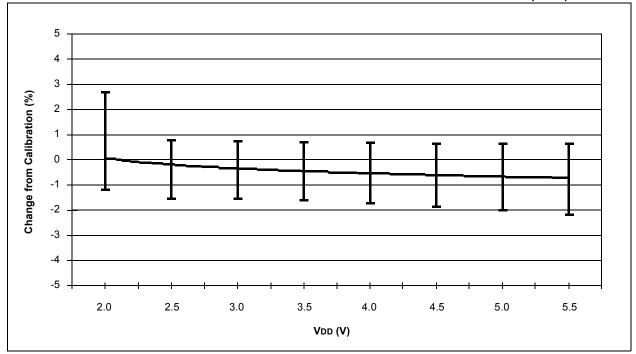

FIGURE 20-39: TYPICAL HFINTOSC FREQUENCY CHANGE OVER DEVICE VDD (85°C)

# APPENDIX C: CONVERSION CONSIDERATIONS

Considerations for converting from previous versions of devices to the ones listed in this data sheet are listed in Table C-1.

TABLE C-1: CONVERSION CONSIDERATIONS

| Characteristic                     | PIC16F91X/946                                               | PIC16F87X                                               | PIC16F87XA                                              |

|------------------------------------|-------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|

| Pins                               | 28/40/64                                                    | 28/40                                                   | 28/40                                                   |

| Timers                             | 3                                                           | 3                                                       | 3                                                       |

| Interrupts                         | 11 or 12                                                    | 13 or 14                                                | 14 or 15                                                |

| Communication                      | USART, SSP <sup>(1)</sup><br>(SPI, I <sup>2</sup> C™ Slave) | PSP, USART, SSP<br>(SPI, I <sup>2</sup> C Master/Slave) | PSP, USART, SSP<br>(SPI, I <sup>2</sup> C Master/Slave) |

| Frequency                          | 20 MHz                                                      | 20 MHz                                                  | 20 MHz                                                  |

| Voltage                            | 2.0V-5.5V                                                   | 2.2V-5.5V                                               | 2.0V-5.5V                                               |

| A/D                                | 10-bit,<br>7 conversion clock selects                       | 10-bit,<br>4 conversion clock selects                   | 10-bit, 7 conversion clock selects                      |

| CCP                                | 2                                                           | 2                                                       | 2                                                       |

| Comparator                         | 2                                                           | _                                                       | 2                                                       |

| Comparator Voltage<br>Reference    | Yes                                                         | _                                                       | Yes                                                     |

| Program Memory                     | 4K, 8K Flash                                                | 4K, 8K Flash<br>(Erase/Write on<br>single-word)         | 4K, 8K Flash<br>(Erase/Write on<br>four-word blocks)    |

| RAM                                | 256, 336, 352 bytes                                         | 192, 368 bytes                                          | 192, 368 bytes                                          |

| EEPROM Data                        | 256 bytes                                                   | 128, 256 bytes                                          | 128, 256 bytes                                          |

| Code Protection                    | On/Off                                                      | Segmented, starting at end of program memory            | On/Off                                                  |

| Program Memory<br>Write Protection | _                                                           | On/Off                                                  | Segmented, starting at beginning of program memory      |

| LCD Module                         | 16, 24 segment drivers,<br>4 commons                        | _                                                       | _                                                       |

| Other                              | In-Circuit Debugger,<br>Low-Voltage Programming             | In-Circuit Debugger,<br>Low-Voltage Programming         | In-Circuit Debugger,<br>Low-Voltage Programming         |

Note 1: SSP aand USART share the same pins on the PIC16F91X.

# PIC16F917/916/914/913

| RG Pins                                   | 85       | Assigning Prescaler to WDT                   | 100     |

|-------------------------------------------|----------|----------------------------------------------|---------|

| SSP (I <sup>2</sup> C Mode)               |          | Call of a Subroutine in Page 1 from Page 0   |         |

| SSP (SPI Mode)                            |          | Changing Between Capture Prescalers          |         |

| Timer1                                    |          | Indirect Addressing                          |         |

| Timer2                                    |          | Initializing PORTA                           |         |

| TMR0/WDT Prescaler                        |          | Initializing PORTB                           |         |

|                                           |          |                                              |         |

| Watchdog Timer (WDT)                      |          | Initializing PORTC                           |         |

| Brown-out Reset (BOR)                     |          | Initializing PORTD                           |         |

| Associated Registers                      |          | Initializing PORTE                           |         |

| Calibration                               |          | Initializing PORTF                           |         |

| Specifications                            |          | Initializing PORTG                           |         |

| Timing and Characteristics                | 268      | Loading the SSPBUF (SSPSR) Register          |         |

| С                                         |          | Saving Status and W Registers in RAM         |         |

|                                           |          | Code Protection                              |         |

| C Compilers                               | 050      | Comparator                                   |         |

| MPLAB C18                                 |          | C2OUT as T1 Gate                             |         |

| MPLAB C30                                 |          | Configurations                               |         |

| Capture Module. See Capture/Compare/PWM ( | •        | Interrupts                                   |         |

| Capture/Compare/PWM (CCP)                 |          | Operation                                    |         |

| Associated registers w/ Capture/Compare/  |          | Operation During Sleep                       | 115     |

| Capture Mode                              |          | Response Time                                | 114     |

| CCPx Pin Configuration                    |          | Synchronizing COUT w/Timer1                  | 117     |

| Compare Mode                              |          | Comparator Module                            |         |

| CCPx Pin Configuration                    | 214      | Associated registers                         | 119     |

| Software Interrupt Mode                   | 213, 214 | Comparator Voltage Reference (CVREF)         |         |

| Special Event Trigger                     | 214      | Response Time                                | 114     |

| Timer1 Mode Selection                     | 213, 214 | Comparator Voltage Reference (CVREF)         | 118     |

| Interaction of Two CCP Modules (table)    | 211      | Effects of a Reset                           | 115     |

| Prescaler                                 | 213      | Specifications                               | 271     |

| PWM Mode                                  | 215      | Comparators                                  |         |

| Duty Cycle                                | 216      | C2OUT as T1 Gate                             | 103     |

| Effects of Reset                          | 218      | Effects of a Reset                           | 115     |

| Example PWM Frequencies and               |          | Specifications                               |         |

| Resolutions, 20 MHZ                       | 217      | Compare Module. See Capture/Compare/PWM (CCI | P)      |

| Example PWM Frequencies and               |          | CONFIG1 Register                             |         |

| Resolutions, 8 MHz                        | 217      | Configuration Bits                           | 220     |

| Operation in Sleep Mode                   | 218      | Conversion Considerations                    |         |

| Setup for Operation                       | 218      | CPU Features                                 | 219     |

| System Clock Frequency Changes            | 218      | Customer Change Notification Service         | 325     |

| PWM Period                                | 216      | Customer Notification Service                | 325     |

| Setup for PWM Operation                   | 218      | Customer Support                             | 325     |

| Timer Resources                           | 211      | <u>_</u>                                     |         |

| CCP. See Capture/Compare/PWM (CCP)        |          | D                                            |         |

| CCPxCON Register                          | 212      | D/A bit                                      | 194     |

| CKE bit                                   | 194      | Data EEPROM Memory                           | 187     |

| CKP bit                                   | 195      | Associated Registers                         | 192     |

| Clock Sources                             |          | Reading                                      |         |

| External Modes                            | 89       | Writing                                      |         |

| EC                                        | 89       | Data Memory                                  |         |

| HS                                        | 90       | Data/Address bit (D/A)                       |         |

| LP                                        | 90       | DC and AC Characteristics                    |         |

| OST                                       | 89       | Graphs and Tables                            | 283     |

| RC                                        | 91       | DC Characteristics                           |         |

| XT                                        |          | Extended and Industrial                      | 261     |

| Internal Modes                            |          | Industrial and Extended                      |         |

| Frequency Selection                       |          | Development Support                          |         |

| HFINTOSC                                  |          | Device Overview                              |         |

| INTOSC                                    |          | 201100 010111011                             |         |

| INTOSCIO                                  |          | E                                            |         |

| LFINTOSC                                  |          | EEADRH Registers                             | 187 188 |

| Clock Switching                           |          | EEADRL Register                              |         |

| CMCON0 Register                           |          | EEADRL Registers                             |         |

| CMCON1 Register                           |          | EECON1 Register                              |         |

| Code Examples                             | 111      | EECON2 Register                              |         |

| A/D Conversion                            | 170      | EEDATH Register                              |         |

| Assigning Prescaler to Timer0             |          | EEDATL Register                              |         |

| Addigning a resocior to annero            |          | :                                            |         |

# PIC16F917/916/914/913

| Effects of Reset                            |     | SLEEP                                                                  | 248        |

|---------------------------------------------|-----|------------------------------------------------------------------------|------------|

| PWM mode                                    | 218 | SUBLW                                                                  | 248        |

| Electrical Specifications                   | 255 | SUBWF                                                                  | 249        |

| Errata                                      |     | SWAPF                                                                  |            |

|                                             |     | XORLW                                                                  |            |

| F                                           |     | XORWF                                                                  |            |

| Fail-Safe Clock Monitor                     | 97  | Summary Table                                                          |            |

| Fail-Safe Condition Clearing                |     | INTCON Register                                                        |            |

| Fail-Safe Detection                         |     | Inter-Integrated Circuit (I <sup>2</sup> C). See I <sup>2</sup> C Mode | 34         |

|                                             |     |                                                                        |            |

| Fail-Safe Operation                         |     | Internal Oscillator Block                                              |            |

| Reset or Wake-up from Sleep                 |     | INTOSC                                                                 |            |

| Firmware Instructions                       |     | Specifications                                                         |            |

| Flash Program Memory                        | 187 | Internal Sampling Switch (Rss) Impedance                               |            |

| Fuses. See Configuration Bits               |     | Internet Address                                                       | 325        |

| G                                           |     | Interrupts                                                             | 230        |

|                                             |     | ADC                                                                    | 179        |

| General Purpose Register File               | 24  | Associated Registers                                                   | 232        |

| 1                                           |     | Comparator                                                             |            |

| 1                                           |     | Context Saving                                                         |            |

| I/O Ports                                   | 43  | Interrupt-on-change                                                    |            |

| I <sup>2</sup> C Mode                       |     | PORTB Interrupt-on-Change                                              |            |

| Addressing                                  | 203 | RB0/INT/SEG0                                                           |            |

| Associated Registers                        |     | TMR0                                                                   |            |

| Master Mode                                 |     | •                                                                      |            |

| Mode Selection                              |     | TMR1                                                                   |            |

| Multi-Master Mode                           |     | INTOSC Specifications                                                  |            |

| Operation                                   |     | IOCB Register                                                          | 54         |

| Reception                                   |     | L                                                                      |            |

| •                                           | 204 | <del>-</del>                                                           |            |

| Slave Mode                                  | 000 | LCD                                                                    |            |

| SCL and SDA pins                            |     | Associated Registers                                                   |            |

| Transmission                                |     | Bias Types                                                             | 148        |

| ID Locations                                |     | Clock Source Selection                                                 | 148        |

| In-Circuit Debugger                         |     | Configuring the Module                                                 | 167        |

| In-Circuit Serial Programming (ICSP)        |     | Disabling the Module                                                   | 167        |

| Indirect Addressing, INDF and FSR Registers | 41  | Frame Frequency                                                        | 149        |

| Instruction Format                          | 241 | Interrupts                                                             |            |

| Instruction Set                             | 241 | LCDCON Register                                                        |            |

| ADDLW                                       | 243 | LCDDATA Register                                                       |            |

| ADDWF                                       | 243 | LCDPS Register                                                         |            |

| ANDLW                                       | 243 | Multiplex Types                                                        |            |

| ANDWF                                       | 243 | Operation During Sleep                                                 |            |

| BCF                                         |     | Pixel Control                                                          |            |

| BSF                                         |     |                                                                        |            |

| BTFSC                                       |     | Prescaler                                                              |            |

| BTFSS                                       |     | Segment Enables                                                        |            |

|                                             |     | Waveform Generation                                                    |            |

| CALL                                        |     | LCDCON Register                                                        |            |

| CLRF                                        |     | LCDDATA Register                                                       | 143        |

| CLRW                                        |     | LCDDATAx Registers                                                     | 147        |

| CLRWDT                                      |     | LCDPS Register                                                         | . 143, 146 |

| COMF                                        | 244 | LP Bits                                                                | 148        |

| DECF                                        | 244 | LCDSEn Registers                                                       | 147        |

| DECFSZ                                      | 245 | Liquid Crystal Display (LCD) Driver                                    |            |

| GOTO                                        | 245 | Load Conditions                                                        |            |

| INCF                                        | 245 |                                                                        |            |

| INCFSZ                                      | 245 | M                                                                      |            |

| IORLW                                       |     | MCLR                                                                   | 222        |

| IORWF                                       |     | Internal                                                               |            |

| MOVF                                        |     |                                                                        |            |

|                                             |     | Memory Organization                                                    |            |

| MOVLW                                       |     | Data                                                                   |            |

| MOVWF                                       |     | Program                                                                |            |

| NOP                                         |     | Microchip Internet Web Site                                            |            |

| RETFIE                                      |     | Migrating from other PIC Microcontroller Devices                       | 315        |

| RETLW                                       |     | MPLAB ASM30 Assembler, Linker, Librarian                               | 252        |

| RETURN                                      | 247 | MPLAB ICD 2 In-Circuit Debugger                                        | 253        |

| RLF                                         | 248 | MPLAB ICE 2000 High-Performance Universal                              |            |

| RRF                                         | 248 | In-Circuit Emulator                                                    | 253        |

|                                             |     |                                                                        |            |

# PIC16F917/916/914/913

| Serial Data Out (SDO pin)                      | 193     | Asynchronous Transmission                                  | . 124 |

|------------------------------------------------|---------|------------------------------------------------------------|-------|

| Slave Select                                   | 193     | Asynchronous Transmission (Back-to-Back)                   | . 124 |

| Slave Select Synchronization                   | 199     | Brown-out Reset (BOR)                                      | . 268 |

| Sleep Operation                                |         | Brown-out Reset Situations                                 |       |

| SPI Clock                                      |         | Capture/Compare/PWM                                        | . 27  |

| Typical Connection                             |         | CLKOUT and I/O                                             |       |

| SSP                                            |         | Clock Synchronization                                      |       |

| Overview                                       |         | Clock Timing                                               | . 26  |

| SPI Master/Slave Connection                    | 197     | Comparator Output                                          |       |

| SSP I <sup>2</sup> C Operation                 |         | Fail-Safe Clock Monitor (FSCM)                             |       |

| Slave Mode                                     |         | I <sup>2</sup> C Bus Data                                  |       |

| SSP Module                                     |         | I <sup>2</sup> C Bus Start/Stop Bits                       |       |

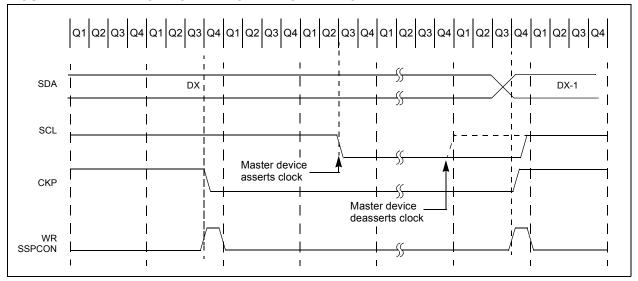

| Clock Synchronization and the CKP Bit          | 208     | I <sup>2</sup> C Reception (7-bit Address)                 |       |

| SPI Master Mode                                |         | I <sup>2</sup> C Slave Mode (Transmission, 10-bit Address) |       |

| SPI Slave Mode                                 |         | I <sup>2</sup> C Slave Mode with SEN = 0 (Reception,       |       |

| SSPBUF                                         |         | 10-bit Address)                                            | 201   |

| SSPSR                                          |         | I <sup>2</sup> C Transmission (7-bit Address)              |       |

|                                                |         |                                                            |       |

| SSPCON Register                                |         | INT Pin Interrupt                                          |       |

| SSPEN bit                                      |         | Internal Oscillator Switch Timing                          |       |

| SSPM bits                                      |         | LCD Interrupt Timing in Quarter-Duty Cycle Drive           |       |

| SSPOV bit                                      |         | LCD Sleep Entry/Exit when SLPEN = 1 or CS = 00.            |       |

| SSPSTAT Register                               |         | Reset, WDT, OST and Power-up Timer                         |       |

| STATUS Register                                |         | Slave Synchronization                                      |       |

| Synchronous Serial Port Enable bit (SSPEN)     |         | SPI Master Mode (CKE = 1, SMP = 1)                         |       |

| Synchronous Serial Port Mode Select bits (SSPM | 1) 195  | SPI Mode (Master Mode)                                     |       |

| Synchronous Serial Port. See SSP               |         | SPI Mode (Slave Mode with CKE = 0)                         | . 200 |

| Т                                              |         | SPI Mode (Slave Mode with CKE = 1)                         |       |

|                                                |         | SPI Slave Mode (CKE = 0)                                   |       |

| T1CON Register                                 |         | SPI Slave Mode (CKE = 1)                                   |       |

| T2CON Register                                 |         | Synchronous Reception (Master Mode, SREN)                  | . 138 |

| Thermal Considerations                         | 263     | Synchronous Transmission                                   | . 136 |

| Time-out Sequence                              | 224     | Synchronous Transmission (Through TXEN)                    | . 136 |

| Timer0                                         | 99      | Time-out Sequence                                          |       |

| Associated Registers                           | 101     | Case 1                                                     | . 22  |

| External Clock                                 | 100     | Case 2                                                     | . 22  |

| Interrupt                                      | 101     | Case 3                                                     | . 22  |

| Operation                                      | 99, 102 | Timer0 and Timer1 External Clock                           |       |

| Specifications                                 |         | Timer1 Incrementing Edge                                   |       |

| TOCKI                                          |         | Two Speed Start-up                                         |       |

| Timer1                                         |         | Type-A in 1/2 Mux, 1/2 Bias Drive                          |       |

| Associated registers                           |         | Type-A in 1/2 Mux, 1/3 Bias Drive                          |       |

| Asynchronous Counter Mode                      |         | Type-A in 1/3 Mux, 1/2 Bias Drive                          |       |

| Reading and Writing                            |         | Type-A in 1/3 Mux, 1/3 Bias Drive                          |       |

| Interrupt                                      |         | Type-A in 1/4 Mux, 1/3 Bias Drive                          |       |

| Modes of Operation                             |         | Type-A/Type-B in Static Drive                              |       |

| •                                              |         | 31 31                                                      |       |

| Operation During Sleep<br>Oscillator           |         | Type-B in 1/2 Mux, 1/2 Bias Drive                          |       |

|                                                |         | Type-B in 1/2 Mux, 1/3 Bias Drive                          |       |

| Prescaler                                      |         | Type-B in 1/3 Mux, 1/2 Bias Drive                          |       |

| Specifications                                 | 270     | Type-B in 1/3 Mux, 1/3 Bias Drive                          |       |

| Timer1 Gate                                    | 400     | Type-B in 1/4 Mux, 1/3 Bias Drive                          |       |

| Inverting Gate                                 |         | USART Synchronous Receive (Master/Slave)                   |       |

| Selecting Source                               |         | USART Synchronous Transmission (Master/Slave).             |       |

| Synchronizing COUT w/Timer1                    |         | Wake-up from Interrupt                                     |       |

| TMR1H Register                                 |         | Timing Parameter Symbology                                 | . 264 |

| TMR1L Register                                 | 102     | Timing Requirements                                        |       |

| Timer2                                         |         | I <sup>2</sup> C Bus Data                                  | . 282 |

| Associated registers                           | 108     | I2C Bus Start/Stop Bits                                    | . 28  |

| Timers                                         |         | SPI Mode                                                   | . 280 |

| Timer1                                         |         | TRISA                                                      |       |

| T1CON                                          | 105     | Registers                                                  | 44    |

| Timer2                                         |         | TRISA Register                                             |       |

| T2CON                                          | 108     | TRISB                                                      |       |

| Timing Diagrams                                |         | Registers                                                  | 53    |

| A/D Conversion                                 | 274     | TRISB Register                                             |       |

| A/D Conversion (Sleep Mode)                    |         | TRISC                                                      | -     |

| Asynchronous Recention                         | 128     | - <del>-</del>                                             |       |