Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

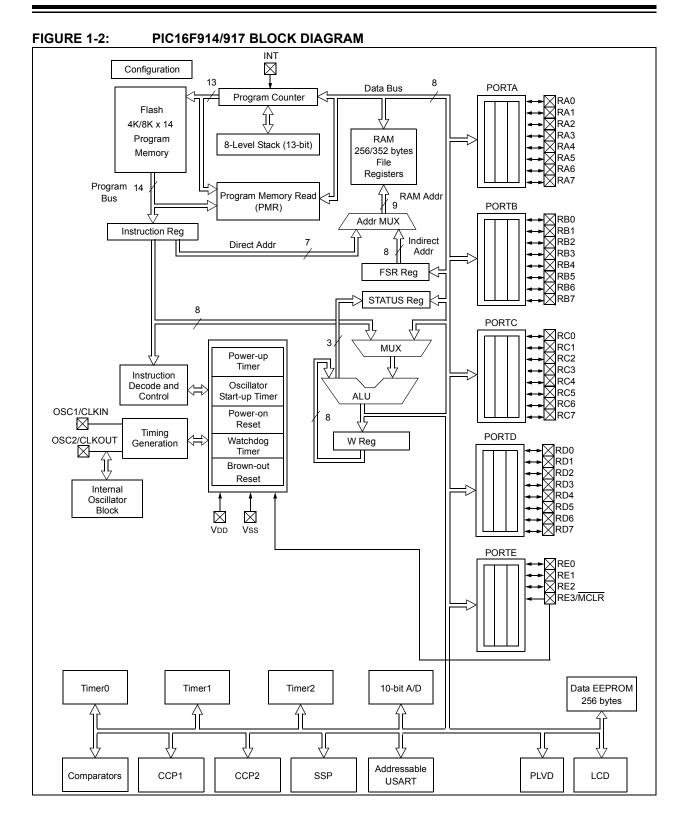

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                               |

| Number of I/O              | 24                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

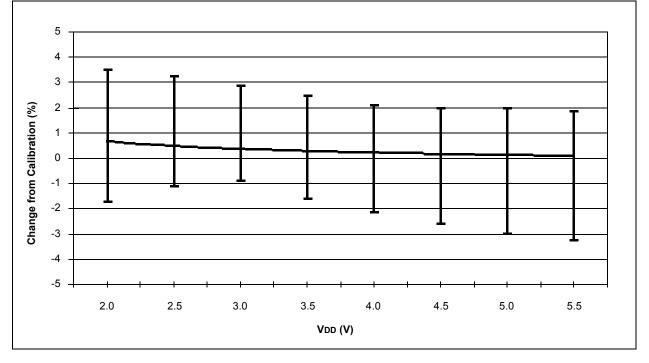

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 5x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 28-SPDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f913-i-sp |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

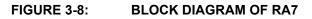

#### 3.2.1.8 RA7/OSC1/CLKIN/T1OSI

Figure 3-8 shows the diagram for this pin. The RA7 pin is configurable to function as one of the following:

- a general purpose I/O

- a crystal/resonator connection

- · a clock input

- a Timer1 oscillator connection

#### TABLE 3-1: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Name                  | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0  | Value on<br>POR, BOR | Value on all other Resets |

|-----------------------|--------|--------|---------|---------|---------|--------|---------|--------|----------------------|---------------------------|

| ADCON0                | ADFM   | VCFG1  | VCFG0   | CHS2    | CHS1    | CHS0   | GO/DONE | ADON   | 0000 0000            | 0000 0000                 |

| ANSEL                 | ANS7   | ANS6   | ANS5    | ANS4    | ANS3    | ANS2   | ANS1    | ANS0   | 1111 1111            | 1111 1111                 |

| CMCON0                | C2OUT  | C1OUT  | C2INV   | C1INV   | CIS     | CM2    | CM1     | CM0    | 0000 0000            | 0000 0000                 |

| CONFIG <sup>(1)</sup> | CPD    | CP     | MCLRE   | PWRTE   | WDTE    | FOSC2  | FOSC1   | FOSC0  | —                    | —                         |

| OPTION_REG            | RBPU   | INTEDG | TOCS    | T0SE    | PSA     | PS2    | PS1     | PS0    | 1111 1111            | 1111 1111                 |

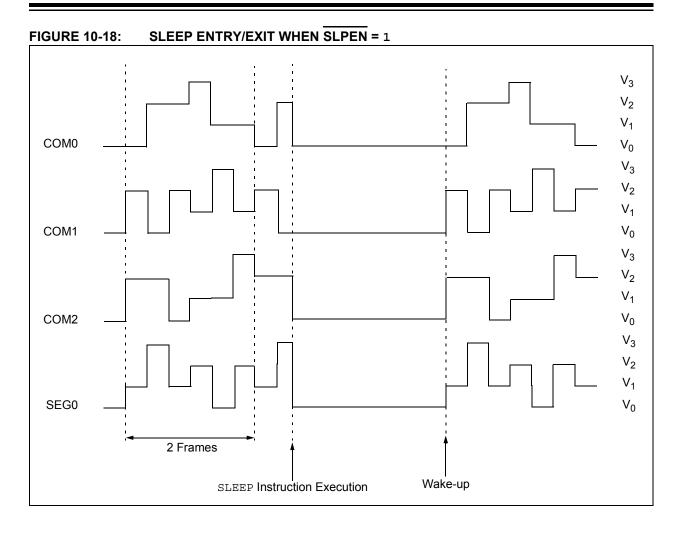

| LCDCON                | LCDEN  | SLPEN  | WERR    | VLCDEN  | CS1     | CS0    | LMUX1   | LMUX0  | 0001 0011            | 0001 0011                 |

| LCDSE0                | SE7    | SE6    | SE5     | SE4     | SE3     | SE2    | SE1     | SE0    | 0000 0000            | uuuu uuuu                 |

| LCDSE1                | SE15   | SE14   | SE13    | SE12    | SE11    | SE10   | SE9     | SE8    | 0000 0000            | uuuu uuuu                 |

| PORTA                 | RA7    | RA6    | RA5     | RA4     | RA3     | RA2    | RA1     | RA0    | XXXX XXXX            | uuuu uuuu                 |

| SSPCON                | WCOL   | SSPOV  | SSPEN   | CKP     | SSPM3   | SSPM2  | SSPM1   | SSPM0  | 0000 0000            | 0000 0000                 |

| T1CON                 | T1GINV | TMR1GE | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS  | TMR10N | 0000 0000            | uuuu uuuu                 |

| TRISA                 | TRISA7 | TRISA6 | TRISA5  | TRISA4  | TRISA3  | TRISA2 | TRISA1  | TRISA0 | 1111 1111            | 1111 1111                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

**Note** 1: See Configuration Word register (CONFIG) for operation of all register bits.

#### 4.2 Oscillator Control

The Oscillator Control (OSCCON) register (Figure 4-1) controls the system clock and frequency selection options. The OSCCON register contains the following bits:

- Frequency selection bits (IRCF)

- Frequency Status bits (HTS, LTS)

- System clock control bits (OSTS, SCS)

#### REGISTER 4-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0   | R/W-1 | R/W-1 | R/W-0 | R-1                 | R-0 | R-0 | R/W-0 |

|-------|-------|-------|-------|---------------------|-----|-----|-------|

| —     | IRCF2 | IRCF1 | IRCF0 | OSTS <sup>(1)</sup> | HTS | LTS | SCS   |

| bit 7 |       |       |       |                     |     |     | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | Unimplemented: Read as '0'                                                                                                                                                                       |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-4 | IRCF<2:0>: Internal Oscillator Frequency Select bits                                                                                                                                             |

|         | 111 = 8 MHz                                                                                                                                                                                      |

|         | 110 = 4 MHz (default)                                                                                                                                                                            |

|         | 101 = 2 MHz                                                                                                                                                                                      |

|         | 100 = 1 MHz                                                                                                                                                                                      |

|         | 011 = 500 kHz                                                                                                                                                                                    |

|         | 010 = 250  kHz                                                                                                                                                                                   |

|         | 001 = 125 kHz                                                                                                                                                                                    |

|         | 000 = 31  kHz (LFINTOSC)                                                                                                                                                                         |

| bit 3   | OSTS: Oscillator Start-up Time-out Status bit <sup>(1)</sup>                                                                                                                                     |

|         | <ul> <li>1 = Device is running from the clock defined by FOSC&lt;2:0&gt; of the Configuration Word</li> <li>0 = Device is running from the internal oscillator (HFINTOSC or LFINTOSC)</li> </ul> |

| bit 2   | HTS: HFINTOSC Status bit (High Frequency – 8 MHz to 125 kHz)                                                                                                                                     |

|         | 1 = HFINTOSC is stable                                                                                                                                                                           |

|         | 0 = HFINTOSC is not stable                                                                                                                                                                       |

| bit 1   | LTS: LFINTOSC Stable bit (Low Frequency – 31 kHz)                                                                                                                                                |

|         | 1 = LFINTOSC is stable                                                                                                                                                                           |

|         | 0 = LFINTOSC is not stable                                                                                                                                                                       |

| bit 0   | SCS: System Clock Select bit                                                                                                                                                                     |

|         | 1 = Internal oscillator is used for system clock                                                                                                                                                 |

|         | <ul> <li>Clock source defined by FOSC&lt;2:0&gt; of the Configuration Word</li> </ul>                                                                                                            |

| Note 1  | Dit reports to 'o' with Two Speed Start up and LD VT or US selected as the Oscillator mode or Eail Sc                                                                                            |

**Note 1:** Bit resets to '0' with Two-Speed Start-up and LP, XT or HS selected as the Oscillator mode or Fail-Safe mode is enabled.

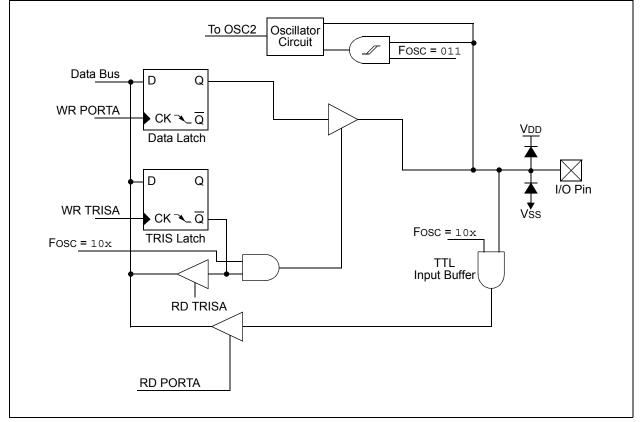

### 6.0 TIMER1 MODULE WITH GATE CONTROL

The Timer1 module is a 16-bit timer/counter with the following features:

- 16-bit timer/counter register pair (TMR1H:TMR1L)

- · Programmable internal or external clock source

- 3-bit prescaler

- Optional LP oscillator

- Synchronous or asynchronous operation

- Timer1 gate (count enable) via comparator or  $\overline{T1G}$  pin

- Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- · Clock source for LCD module

Figure 6-1 is a block diagram of the Timer1 module.

#### 6.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer. When used with an external clock source, the module can be used as either a timer or counter.

### 6.2 Clock Source Selection

The TMR1CS bit of the T1CON register is used to select the clock source. When TMR1CS = 0, the clock source is FOSC/4. When TMR1CS = 1, the clock source is supplied externally.

| Clock Source | TMR1CS |

|--------------|--------|

| Fosc/4       | 0      |

| T1CKI pin    | 1      |

### FIGURE 6-1: TIMER1 BLOCK DIAGRAM

| REGISTER /      | -1. 1200                    |                       |               | LOISTER           |                 |                |         |  |  |  |  |  |

|-----------------|-----------------------------|-----------------------|---------------|-------------------|-----------------|----------------|---------|--|--|--|--|--|

| U-0             | R/W-0                       | R/W-0                 | R/W-0         | R/W-0             | R/W-0           | R/W-0          | R/W-0   |  |  |  |  |  |

| —               | TOUTPS3                     | TOUTPS2               | TOUTPS1       | TOUTPS0           | TMR2ON          | T2CKPS1        | T2CKPS0 |  |  |  |  |  |

| bit 7           | ·                           |                       |               |                   |                 | ·              | bit 0   |  |  |  |  |  |

|                 |                             |                       |               |                   |                 |                |         |  |  |  |  |  |

| Legend:         |                             |                       |               |                   |                 |                |         |  |  |  |  |  |

| R = Readable    | bit                         | W = Writable          | bit           | U = Unimplen      | nented bit, rea | d as '0'       |         |  |  |  |  |  |

| -n = Value at F | POR                         | '1' = Bit is set      |               | '0' = Bit is clea | ared            | x = Bit is unk | nown    |  |  |  |  |  |

|                 |                             |                       |               |                   |                 |                |         |  |  |  |  |  |

| bit 7           | Unimplemen                  | ted: Read as '        | 0'            |                   |                 |                |         |  |  |  |  |  |

| bit 6-3         | -                           | )>: Timer2 Out        |               | Select bits       |                 |                |         |  |  |  |  |  |

|                 | 0000 <b>= 1:1 P</b>         |                       |               |                   |                 |                |         |  |  |  |  |  |

|                 | 0001 <b>= 1:2 P</b>         |                       |               |                   |                 |                |         |  |  |  |  |  |

|                 | 0010 <b>= 1:3 P</b>         | 0010 = 1:3 Postscaler |               |                   |                 |                |         |  |  |  |  |  |

|                 | 0011 = 1:4 Postscaler       |                       |               |                   |                 |                |         |  |  |  |  |  |

|                 | 0100 = 1:5 Postscaler       |                       |               |                   |                 |                |         |  |  |  |  |  |

|                 | 0101 = 1:6 Postscaler       |                       |               |                   |                 |                |         |  |  |  |  |  |

|                 | 0110 = 1:7 Postscaler       |                       |               |                   |                 |                |         |  |  |  |  |  |

|                 | 0111 = 1:8 P                |                       |               |                   |                 |                |         |  |  |  |  |  |

|                 | 1000 = 1:9 P<br>1001 = 1:10 |                       |               |                   |                 |                |         |  |  |  |  |  |

|                 | 1010 = 1.101                |                       |               |                   |                 |                |         |  |  |  |  |  |

|                 | 1011 = 1:12                 |                       |               |                   |                 |                |         |  |  |  |  |  |

|                 | 1100 = 1:13                 |                       |               |                   |                 |                |         |  |  |  |  |  |

|                 | 1101 <b>= 1:14</b>          | Postscaler            |               |                   |                 |                |         |  |  |  |  |  |

|                 | 1110 = 1:15 Postscaler      |                       |               |                   |                 |                |         |  |  |  |  |  |

|                 | 1111 = 1:16                 | Postscaler            |               |                   |                 |                |         |  |  |  |  |  |

| bit 2           | TMR2ON: Tir                 | mer2 On bit           |               |                   |                 |                |         |  |  |  |  |  |

|                 | 1 = Timer2 is               |                       |               |                   |                 |                |         |  |  |  |  |  |

|                 | 0 = Timer2 is               | s off                 |               |                   |                 |                |         |  |  |  |  |  |

| bit 1-0         | T2CKPS<1:0                  | >: Timer2 Cloc        | k Prescale Se | lect bits         |                 |                |         |  |  |  |  |  |

|                 | 00 = Prescale               | er is 1               |               |                   |                 |                |         |  |  |  |  |  |

|                 | 01 = Prescale               |                       |               |                   |                 |                |         |  |  |  |  |  |

|                 | 1x = Prescale               | er is 16              |               |                   |                 |                |         |  |  |  |  |  |

| TABLE 7-1:      |                             | V OF REGIS            | TERS ASSO     | CIATED WITH       |                 |                |         |  |  |  |  |  |

|                 |                             |                       |               |                   |                 |                |         |  |  |  |  |  |

#### REGISTER 7-1: T2CON: TIMER 2 CONTROL REGISTER

| Name   | Bit 7                                        | Bit 6        | Bit 5    | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------------------------------------------|--------------|----------|---------|---------|--------|---------|---------|----------------------|---------------------------------|

| INTCON | GIE                                          | PEIE         | T0IE     | INTE    | RBIE    | T0IF   | INTF    | RBIF    | x000 0000x           | 0000 000x                       |

| PIE1   | EEIE                                         | ADIE         | RCIE     | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000            | 0000 0000                       |

| PIR1   | EEIF                                         | ADIF         | RCIF     | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000            | 0000 0000                       |

| PR2    | Timer2 M                                     | odule Period | Register |         |         |        |         |         | 1111 1111            | 1111 1111                       |

| TMR2   | Holding Register for the 8-bit TMR2 Register |              |          |         |         |        |         |         |                      | 0000 0000                       |

| T2CON  | —                                            | TOUTPS3      | TOUTPS2  | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000            | -000 0000                       |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for Timer2 module.

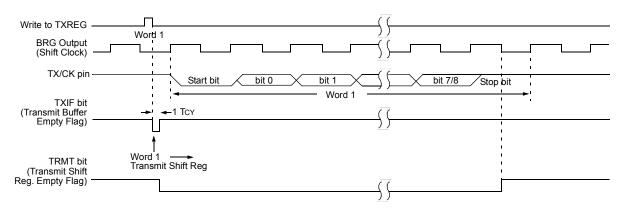

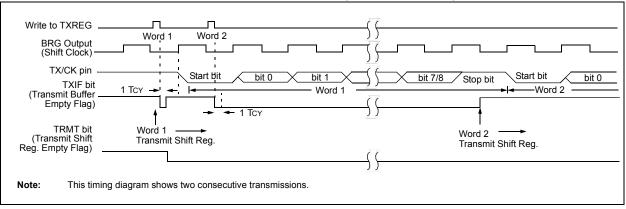

#### 9.1.1.4 TSR Status

The TRMT bit of the TXSTA register indicates the status of the TSR register. This is a read-only bit. The TRMT bit is set when the TSR register is empty and is cleared when a character is transferred to the TSR register from the TXREG. The TRMT bit remains clear until all bits have been shifted out of the TSR register. No interrupt logic is tied to this bit, so the user has to poll this bit to determine the TSR status.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

#### 9.1.1.5 Transmitting 9-Bit Characters

The AUSART supports 9-bit character transmissions. When the TX9 bit of the TXSTA register is set the AUSART will shift 9 bits out for each character transmitted. The TX9D bit of the TXSTA register is the ninth, and Most Significant, data bit. When transmitting 9-bit data, the TX9D data bit must be written before writing the 8 Least Significant bits into the TXREG. All nine bits of data will be transferred to the TSR shift register immediately after the TXREG is written.

A special 9-bit Address mode is available for use with multiple receivers. See Section 9.1.2.7 "Address Detection" for more information on the Address mode.

#### 9.1.1.6 Asynchronous Transmission Set-up:

- Initialize the SPBRG register and the BRGH bit to 1 achieve the desired baud rate (see Section 9.2 "AUSART Baud Rate Generator (BRG)").

- Enable the asynchronous serial port by clearing 2 the SYNC bit and setting the SPEN bit.

- If 9-bit transmission is desired, set the TX9 con-3. trol bit. A set ninth data bit will indicate that the 8 Least Significant data bits are an address when the receiver is set for address detection.

- 4 Enable the transmission by setting the TXEN control bit. This will cause the TXIF interrupt bit to be set.

- If interrupts are desired, set the TXIE interrupt 5. enable bit of the PIE1 register. An interrupt will occur immediately provided that the GIE and PEIE bits of the INTCON register are also set.

- If 9-bit transmission is selected, the ninth bit 6 should be loaded into the TX9D data bit.

- 7 Load 8-bit data into the TXREG register. This will start the transmission.

#### FIGURE 9-4: ASYNCHRONOUS TRANSMISSION (BACK-TO-BACK)

ASYNCHRONOUS TRANSMISSION

FIGURE 9-3:

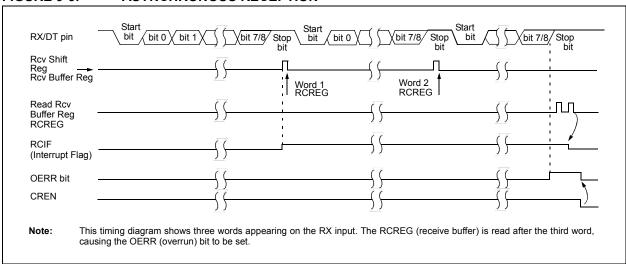

#### 9.1.2.8 Asynchronous Reception Set-up:

- Initialize the SPBRG register and the BRGH bit to achieve the desired baud rate (see Section 9.2 "AUSART Baud Rate Generator (BRG)").

- Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Enable reception by setting the CREN bit.

- 6. The RCIF interrupt flag bit of the PIR1 register will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE bit of the PIE1 register was also set.

- 7. Read the RCSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 8. Get the received 8 Least Significant data bits from the receive buffer by reading the RCREG register.

- 9. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

#### 9.1.2.9 9-bit Address Detection Mode Set-up

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRG register and the BRGH bit to achieve the desired baud rate (see Section 9.2 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. Enable 9-bit reception by setting the RX9 bit.

- 5. Enable address detection by setting the ADDEN bit.

- 6. Enable reception by setting the CREN bit.

- The RCIF interrupt flag bit of the PIR1 register will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit of the PIE1 register was also set.

- 8. Read the RCSTA register to get the error flags. The ninth data bit will always be set.

- Get the received 8 Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

### FIGURE 9-5: ASYNCHRONOUS RECEPTION

| U-0           | U-0                                                                                                                                              | R/W-0                                                                                                                                                                  | R/W-0                                                                                                                                              | R/W-0                                                                | R/W-0                                     | R/W-0           | R/W-0  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------|-----------------|--------|

| _             | —                                                                                                                                                | CCPxX                                                                                                                                                                  | CCPxY                                                                                                                                              | CCP1M3                                                               | CCP1M2                                    | CCP1M1          | CCP1M0 |

| bit 7         |                                                                                                                                                  |                                                                                                                                                                        |                                                                                                                                                    |                                                                      |                                           |                 | bit 0  |

|               |                                                                                                                                                  |                                                                                                                                                                        |                                                                                                                                                    |                                                                      |                                           |                 |        |

| Legend:       |                                                                                                                                                  |                                                                                                                                                                        |                                                                                                                                                    |                                                                      |                                           |                 |        |

| R = Readable  | e bit                                                                                                                                            | W = Writable                                                                                                                                                           | bit                                                                                                                                                | U = Unimpler                                                         | nented bit, read                          | d as '0'        |        |

| -n = Value at | POR                                                                                                                                              | '1' = Bit is set                                                                                                                                                       |                                                                                                                                                    | '0' = Bit is cle                                                     | ared                                      | x = Bit is unki | nown   |

|               |                                                                                                                                                  |                                                                                                                                                                        |                                                                                                                                                    |                                                                      |                                           |                 |        |

| bit 7-6       | Unimplemen                                                                                                                                       | ted: Read as '                                                                                                                                                         | 0'                                                                                                                                                 |                                                                      |                                           |                 |        |

| bit 5-4       | Capture mode<br>Unused<br>Compare mod<br>Unused<br>PWM mode:                                                                                     | de:                                                                                                                                                                    | -                                                                                                                                                  | luty cycle. The                                                      | eight MSbs are                            | found in CCP    | RxL.   |

| bit 3-0       | 0000 = Capt<br>0001 = Unus<br>0010 = Unus<br>0011 = Unus<br>0100 = Capt<br>0101 = Capt<br>0110 = Capt<br>0111 = Capt<br>1000 = Com<br>1001 = Com | sed (reserved)<br>sed (reserved)<br>sed (reserved)<br>ure mode, eve<br>ure mode, eve<br>ure mode, eve<br>pare mode, se<br>pare mode, cle<br>pare mode, ge<br>affected) | PWM off (rese<br>ry falling edge<br>ry rising edge<br>ry 4th rising ed<br>ry 16th rising ed<br>t output on ma<br>ear output on r<br>nerate softwar | dge<br>edge<br>atch (CCPxIF bi<br>natch (CCPxIF<br>re interrupt on r | t is set)<br>bit is set)<br>natch (CCPxIF |                 | -      |

#### REGISTER 15-1: CCPxCON: CCPx CONTROL REGISTER

#### 16.1 Configuration Bits

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1') to select various device configurations as shown in Register 16-1. These bits are mapped in program memory location 2007h.

Note: Address 2007h is beyond the user program memory space. It belongs to the special configuration memory space (2000h-3FFFh), which can be accessed only during programming. See "PIC16F91X/946 Memory Programming Specification" (DS41244) for more information.

#### REGISTER 16-1: CONFIG1: CONFIGURATION WORD REGISTER 1

| _      | _ | _ | DEBUG | FCMEN | IESO | BOREN1 | BOREN0 |

|--------|---|---|-------|-------|------|--------|--------|

| bit 15 |   |   |       |       |      |        | bit 8  |

| CPD   | CP | MCLRE | PWRTE | WDTE | FOSC2 | FOSC1 | FOSC0 |

|-------|----|-------|-------|------|-------|-------|-------|

| bit 7 |    |       |       |      |       |       | bit 0 |

| bit 15-13           | Unimplemented: Read as '1'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 12              | <b>DEBUG:</b> In-Circuit Debugger Mode bit<br>1 = In-Circuit Debugger disabled, RB6/ICSPCLK and RB7/ICSPDAT are general purpose I/O pins<br>0 = In-Circuit Debugger enabled, RB6/ICSPCLK and RB7/ICSPDAT are dedicated to the debugger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| bit 11              | FCMEN: Fail-Safe Clock Monitor Enabled bit<br>1 = Fail-Safe Clock Monitor is enabled<br>0 = Fail-Safe Clock Monitor is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| bit 10              | IESO: Internal External Switchover bit<br>1 = Internal/External Switchover mode is enabled<br>0 = Internal/External Switchover mode is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| bit 9-8             | BOREN<1:0>: Brown-out Reset Selection bits <sup>(1)</sup><br>11 = BOR enabled<br>10 = BOR enabled during operation and disabled in Sleep<br>01 = BOR controlled by SBOREN bit of the PCON register<br>00 = BOR disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| bit 7               | <b>CPD:</b> Data Code Protection bit <sup>(2)</sup><br>1 = Data memory code protection is disabled<br>0 = Data memory code protection is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| bit 6               | <b>CP:</b> Code Protection bit <sup>(3)</sup><br>1 = Program memory code protection is disabled<br>0 = Program memory code protection is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| bit 5               | MCLRE: RE3/MCLR pin functi <u>on sel</u> ect bit <sup>(4)</sup><br>1 = RE3/MCLR pin function is MCLR<br>0 = RE3/MCLR pin function is digital input, MCLR internally tied to VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| bit 4               | <b>PWRTE:</b> Power-up Timer Enable bit<br>1 = PWRT disabled<br>0 = PWRT enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| bit 3               | WDTE: Watchdog Timer Enable bit<br>1 = WDT enabled<br>0 = WDT disabled and can be enabled by SWDTEN bit of the WDTCON register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 2-0             | <b>FOSC&lt;2:0&gt;:</b> Oscillator Selection bits<br>111 = RC oscillator: CLKOUT function on RA6/OSC2/CLKOUT/T1OSO pin, RC on RA7/OSC1/CLKIN/T1OSI<br>100 = RCIO oscillator: I/O function on RA6/OSC2/CLKOUT/T1OSO pin, RC on RA7/OSC1/CLKIN/T1OSI<br>101 = INTOSC oscillator: CLKOUT function on RA6/OSC2/CLKOUT/T1OSO pin, I/O function on RA7/OSC1/CLKIN/T1OSI<br>100 = INTOSCIO oscillator: I/O function on RA6/OSC2/CLKOUT/T1OSO pin, I/O function on RA7/OSC1/CLKIN/T1OSI<br>101 = EC: I/O function on RA6/OSC2/CLKOUT/T1OSO pin, I/O function on RA7/OSC1/CLKIN/T1OSI<br>101 = EC: I/O function on RA6/OSC2/CLKOUT/T1OSO pin, CLKIN on RA7/OSC1/CLKIN/T1OSI<br>100 = HS oscillator: High-speed crystal/resonator on RA6/OSC2/CLKOUT/T1OSO and RA7/OSC1/CLKIN/T1OSI<br>101 = XT oscillator: Crystal/resonator on RA6/OSC2/CLKOUT/T1OSO and RA7/OSC1/CLKIN/T1OSI<br>100 = LP oscillator: Low-power crystal on RA6/OSC2/CLKOUT/T1OSO and RA7/OSC1/CLKIN/T1OSI |

| Note 1:<br>2:<br>3: | Enabling Brown-out Reset does not automatically enable Power-up Timer.<br>The entire data EEPROM will be erased when the code protection is turned off.<br>The en <u>tire program memory will be erased when the code protection is turned off.</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

4: When MCLR is asserted in INTOSC or RC mode, the internal clock oscillator is disabled.

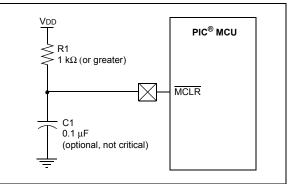

#### 16.2.1 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in Reset until VDD has reached a high enough level for proper operation. To take advantage of the POR, simply connect the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See **Section 19.0 "Electrical Specifications**" for details. If the BOR is enabled, the maximum rise time specification does not apply. The BOR circuitry will keep the device in Reset until VDD reaches VBOR (see **Section 16.2.4 "Brown-Out Reset (BOR)"**).

Note: The POR circuit does not produce an internal Reset when VDD declines. To re-enable the POR, VDD must reach Vss for a minimum of 100 μs.

When the device starts normal operation (exits the Reset condition), device operating parameters (i.e., voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS00607).

#### 16.2.2 MCLR

PIC16F91X/946 has a noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive MCLR pin low.

Voltages applied to the pin that exceed its specification can result in both MCLR Resets and excessive current beyond the device specification during the ESD event. For this reason, Microchip recommends that the MCLR pin no longer be tied directly to VDD. The use of an RC network, as shown in Figure 16-2, is suggested.

An internal  $\overline{\text{MCLR}}$  option is enabled by clearing the  $\overline{\text{MCLRE}}$  bit in the Configuration Word register. When  $\overline{\text{MCLRE}} = 0$ , the Reset signal to the chip is generated internally. When the  $\overline{\text{MCLRE}} = 1$ , the RE3/ $\overline{\text{MCLR}}$  pin becomes an external Reset input. In this mode, the RE3/ $\overline{\text{MCLR}}$  pin has a weak pull-up to VDD. In-Circuit Serial Programming is not affected by selecting the internal  $\overline{\text{MCLR}}$  option.

#### FIGURE 16-2: F

####

### 16.2.3 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 64 ms (nominal) time-out on power-up only, from POR or Brown-out Reset. The Power-up Timer operates from the 31 kHz LFINTOSC oscillator. For more information, see **Section 4.5 "Internal Clock Modes"**. The chip is kept in Reset as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A Configuration bit, PWRTE, can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-up Timer should be enabled when Brown-out Reset is enabled, although it is not required.

The Power-up Timer delay will vary from chip-to-chip and vary due to:

- VDD variation

- Temperature variation

- Process variation

See DC parameters for details (Section 19.0 "Electrical Specifications").

### 16.3 Interrupts

The PIC16F91X/946 has multiple sources of interrupt:

- External Interrupt RB0/INT/SEG0

- TMR0 Overflow Interrupt

- PORTB Change Interrupts

- 2 Comparator Interrupts

- A/D Interrupt

- Timer1 Overflow Interrupt

- EEPROM Data Write Interrupt

- Fail-Safe Clock Monitor Interrupt

- LCD Interrupt

- PLVD Interrupt

- · USART Receive and Transmit interrupts

- CCP1 and CCP2 Interrupts

- Timer2 Interrupt

The Interrupt Control (INTCON), Peripheral Interrupt Request 1 (PIR1) and Peripheral Interrupt Request 2 (PIR2) registers record individual interrupt requests in flag bits. The INTCON register also has individual and global interrupt enable bits.

A Global Interrupt Enable bit, GIE of the INTCON register, enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in the INTCON, PIE1 and PIE2 registers. GIE is cleared on Reset.

The Return from Interrupt instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit, which re-enables unmasked interrupts.

The following interrupt flags are contained in the INTCON register:

- INT Pin Interrupt

- PORTB Change Interrupt

- TMR0 Overflow Interrupt

The peripheral interrupt flags are contained in the special registers, PIR1 and PIR2. The corresponding interrupt enable bit are contained in the special registers, PIE1 and PIE2.

The following interrupt flags are contained in the PIR1 register:

- EEPROM Data Write Interrupt

- A/D Interrupt

- USART Receive and Transmit Interrupts

- Timer1 Overflow Interrupt

- CCP1 Interrupt

- SSP Interrupt

- Timer2 Interrupt

The following interrupt flags are contained in the PIR2 register:

- Fail-Safe Clock Monitor Interrupt

- Comparator 1 and 2 Interrupts

- LCD Interrupt

- PLVD Interrupt

- CCP2 Interrupt

When an interrupt is serviced:

- · The GIE is cleared to disable any further interrupt.

- · The return address is pushed onto the stack.

- The PC is loaded with 0004h.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends upon when the interrupt event occurs (see Figure 16-8). The latency is the same for one or two-cycle instructions. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests.

- Note 1: Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit or the GIE bit.

- 2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The interrupts, which were ignored, are still pending to be serviced when the GIE bit is set again.

For additional information on how a module generates an interrupt, refer to the respective peripheral section.

Note: The ANSEL and CMCON0 registers must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'. Also, if a LCD output function is active on an external interrupt pin, that interrupt function will be disabled.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                           |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECFSZ f,d                                                                                                                                                                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                                                                                |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                       |

| Status Affected: | None                                                                                                                                                                                                                                                                                                             |

| Description:     | The contents of register 'f' are decremented. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'.<br>If the result is '1', the next instruction is executed. If the result is '0', then a NOP is executed instead, making it a 2-cycle instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                              |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                                                                                         |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                     |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                          |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', a NOP is executed<br>instead, making it a 2-cycle<br>instruction. |  |  |

| GOTO             | Unconditional Branch                                                                                                                                                                             |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                          |  |  |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                               |  |  |

| Operation:       | $k \rightarrow PC < 10:0>$<br>PCLATH<4:3> $\rightarrow PC < 12:11>$                                                                                                                              |  |  |

| Status Affected: | None                                                                                                                                                                                             |  |  |

| Description:     | GOTO is an unconditional branch.<br>The eleven-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a<br>two-cycle instruction. |  |  |

| IORLW            | Inclusive OR literal with W                                                                                               |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                         |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                              |  |  |

| Status Affected: | Z                                                                                                                         |  |  |

| Description:     | The contents of the W register are<br>OR'ed with the eight-bit literal 'k'.<br>The result is placed in the<br>W register. |  |  |

| INCF             | Increment f                                                                                                                                                                |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] INCF f,d                                                                                                                                                  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ensuremath{\left[0,1\right]} \end{array}$                                                                                    |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                        |  |  |  |

| Status Affected: | Z                                                                                                                                                                          |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |  |  |  |

| IORWF            | Inclusive OR W with f                                                                                                                                                       |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ensuremath{\left[ 0,1 \right]} \end{array}$                                                                                   |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                    |  |  |

| Status Affected: | Z                                                                                                                                                                           |  |  |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is '0', the result is<br>placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |  |  |

### 18.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB® IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C18 and MPLAB C30 C Compilers

- MPLINK™ Object Linker/

- MPLIB™ Object Librarian

- MPLAB ASM30 Assembler/Linker/Library

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD 2

- Device Programmers

- PICSTART® Plus Development Programmer

- MPLAB PM3 Device Programmer

- PICkit™ 2 Development Programmer

- Low-Cost Demonstration and Development Boards and Evaluation Kits

#### 18.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- · A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High-level source code debugging

- Visual device initializer for easy register initialization

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as HI-TECH Software C Compilers and IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either assembly or C)

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- · Debug using:

- Source files (assembly or C)

- Mixed assembly and C

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

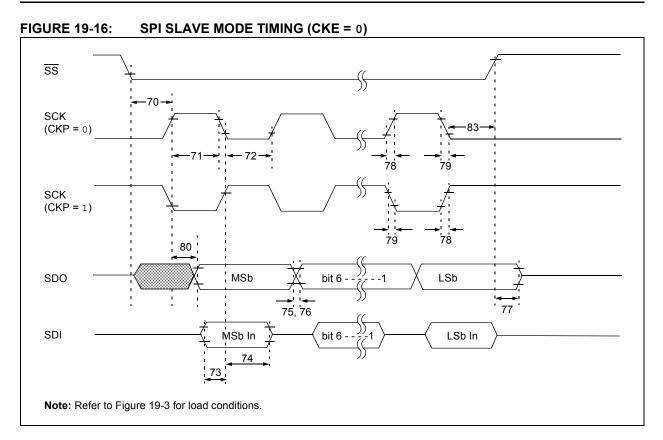

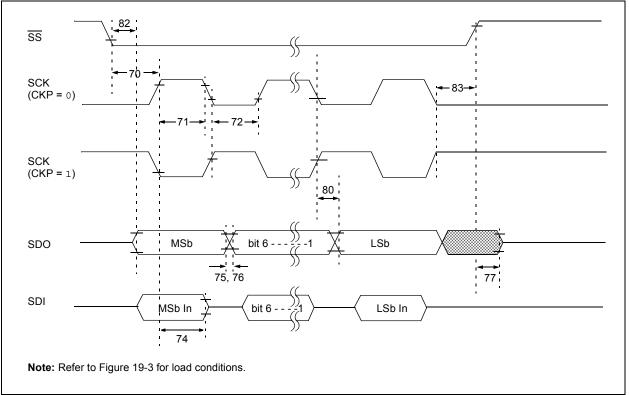

#### FIGURE 19-17: SPI SLAVE MODE TIMING (CKE = 1)

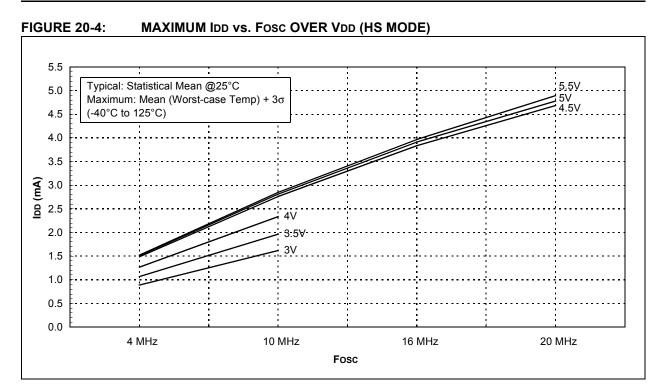

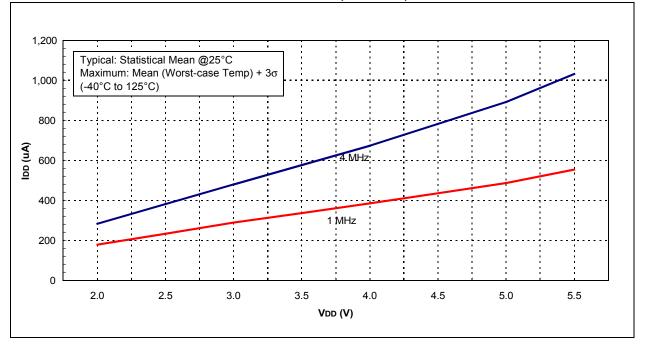

FIGURE 20-5: TYPICAL IDD vs. VDD OVER Fosc (XT MODE)

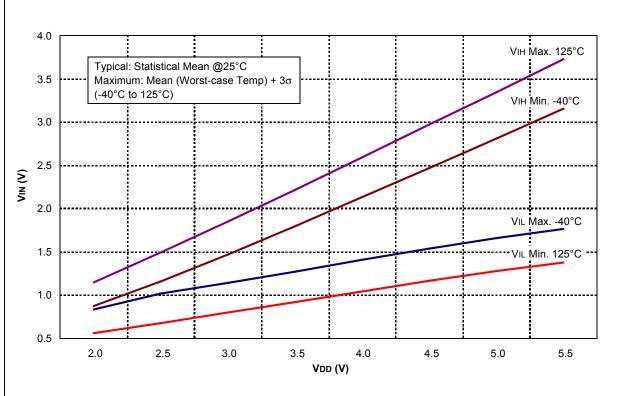

FIGURE 20-30: SCHMITT TRIGGER INPUT THRESHOLD VIN vs. VDD OVER TEMPERATURE

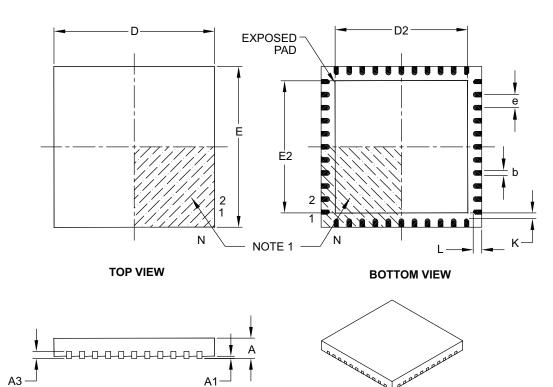

### 44-Lead Plastic Quad Flat, No Lead Package (ML) – 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                  |                  | MILLIMETERS |      |      |

|------------------------|------------------|-------------|------|------|

|                        | Dimension Limits | MIN         | NOM  | MAX  |

| Number of Pins         | N                | 44          |      |      |

| Pitch                  | е                | 0.65 BSC    |      |      |

| Overall Height         | A                | 0.80        | 0.90 | 1.00 |

| Standoff               | A1               | 0.00        | 0.02 | 0.05 |

| Contact Thickness      | A3               | 0.20 REF    |      |      |

| Overall Width          | E                | 8.00 BSC    |      |      |

| Exposed Pad Width      | E2               | 6.30        | 6.45 | 6.80 |

| Overall Length         | D                | 8.00 BSC    |      |      |

| Exposed Pad Length     | D2               | 6.30        | 6.45 | 6.80 |

| Contact Width          | b                | 0.25        | 0.30 | 0.38 |

| Contact Length         | L                | 0.30        | 0.40 | 0.50 |

| Contact-to-Exposed Pad |                  | 0.20        | -    | -    |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-103B