#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                               |

| Number of I/O              | 24                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 5x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 28-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f913-i-ss |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1-1: PIC16F91X/946 PINOUT DESCRIPTIONS (CONTINUED)

| Name                                                              | Function    | Input<br>Type     | Output<br>Type | Description                                                                            |

|-------------------------------------------------------------------|-------------|-------------------|----------------|----------------------------------------------------------------------------------------|

| RC6/TX/CK/SCK/SCL/SEG9                                            | RC6         | ST                | CMOS           | General purpose I/O.                                                                   |

|                                                                   | TX          |                   | CMOS           | USART asynchronous serial transmit.                                                    |

|                                                                   | СК          | ST                | CMOS           | USART synchronous serial clock.                                                        |

|                                                                   | SCK         | ST                | CMOS           | SPI clock.                                                                             |

|                                                                   | SCL         | ST <sup>(4)</sup> | OD             | l <sup>2</sup> C™ clock.                                                               |

|                                                                   | SEG9        |                   | AN             | LCD analog output.                                                                     |

| RC7/RX/DT/SDI/SDA/SEG8                                            | RC7         | ST                | CMOS           | General purpose I/O.                                                                   |

|                                                                   | RX          | ST                |                | USART asynchronous serial receive.                                                     |

|                                                                   | DT          | ST                | CMOS           | USART synchronous serial data.                                                         |

|                                                                   | SDI         | ST                | CMOS           | SPI data input.                                                                        |

|                                                                   | SDA         | ST <sup>(4)</sup> | OD             | l <sup>2</sup> C™ data.                                                                |

|                                                                   | SEG8        |                   | AN             | LCD analog output.                                                                     |

| RD0/COM3 <sup>(1, 2)</sup>                                        | RD0         | ST                | CMOS           | General purpose I/O.                                                                   |

|                                                                   | COM3        |                   | AN             | LCD analog output.                                                                     |

| RD1 <sup>(2)</sup>                                                | RD1         | ST                | CMOS           | General purpose I/O.                                                                   |

| RD2/CCP2 <sup>(2)</sup>                                           | RD2         | ST                | CMOS           | General purpose I/O.                                                                   |

|                                                                   | CCP2        | ST                | CMOS           | Capture 2 input/Compare 2 output/PWM 2 output.                                         |

| RD3/SEG16 <sup>(2)</sup>                                          | RD3         | ST                | CMOS           | General purpose I/O.                                                                   |

|                                                                   | SEG16       |                   | AN             | LCD analog output.                                                                     |

| RD4/SEG17 <sup>(2)</sup>                                          | RD4         | ST                | CMOS           | General purpose I/O.                                                                   |

|                                                                   | SEG17       |                   | AN             | LCD analog output.                                                                     |

| RD5/SEG18 <sup>(2)</sup>                                          | RD5         | ST                | CMOS           | General purpose I/O.                                                                   |

|                                                                   | SEG18       | _                 | AN             | LCD analog output.                                                                     |

| RD6/SEG19 <sup>(2)</sup>                                          | RD6         | ST                | CMOS           | General purpose I/O.                                                                   |

|                                                                   | SEG19       |                   | AN             | LCD analog output.                                                                     |

| RD7/SEG20 <sup>(2)</sup>                                          | RD7         | ST                | CMOS           | General purpose I/O.                                                                   |

|                                                                   | SEG20       |                   | AN             | LCD analog output.                                                                     |

| RE0/AN5/SEG21 <sup>(2)</sup>                                      | RE0         | ST                | CMOS           | General purpose I/O.                                                                   |

|                                                                   | AN5         | AN                |                | Analog input Channel 5.                                                                |

|                                                                   | SEG21       |                   | AN             | LCD analog output.                                                                     |

| RE1/AN6/SEG22 <sup>(2)</sup>                                      | RE1         | ST                | CMOS           | General purpose I/O.                                                                   |

|                                                                   | AN6         | AN                |                | Analog input Channel 6.                                                                |

|                                                                   | SEG22       |                   | AN             | LCD analog output.                                                                     |

| RE2/AN7/SEG23 <sup>(2)</sup>                                      | RE2         | ST                | CMOS           | General purpose I/O.                                                                   |

|                                                                   | AN7         | AN                | —              | Analog input Channel 7.                                                                |

|                                                                   | SEG23       | —                 | AN             | LCD analog output.                                                                     |

| RE3/MCLR/Vpp                                                      | RE3         | ST                | _              | Digital input only.                                                                    |

|                                                                   | MCLR        | ST                | _              | Master Clear with internal pull-up.                                                    |

|                                                                   | Vpp         | ΗV                | —              | Programming voltage.                                                                   |

| Legend: AN = Analog inpu<br>TTL = TTL compate<br>HV = High Voltag | tible input | ST =              |                | compatible input or output OD = Open Drain<br>Trigger input with CMOS levels P = Power |

Note 1: COM3 is available on RA3 for the PIC16F913/916 and on RD0 for the PIC16F914/917 and PIC16F946.

**2:** Pins available on PIC16F914/917 and PIC16F946 only.

**3:** Pins available on PIC16F946 only.

4: I<sup>2</sup>C Schmitt trigger inputs have special input levels.

| Addr               | Name                 | Bit 7              | Bit 6                                                             | Bit 5              | Bit 4              | Bit 3         | Bit 2              | Bit 1              | Bit 0                 | Value on<br>POR, BOR | Page    |

|--------------------|----------------------|--------------------|-------------------------------------------------------------------|--------------------|--------------------|---------------|--------------------|--------------------|-----------------------|----------------------|---------|

| Bank 0             |                      |                    |                                                                   |                    |                    |               |                    |                    |                       |                      |         |

| 00h                | INDF                 | Addressing         | g this locatio                                                    | n uses conte       | nts of FSR to      | address dat   | a memory (r        | not a physica      | l register)           | xxxx xxxx            | 41,226  |

| 01h                | TMR0                 | Timer0 Mc          | dule Registe                                                      | er                 |                    |               |                    |                    |                       | xxxx xxxx            | 99,226  |

| 02h                | PCL                  | Program C          | Counter's (PC                                                     | C) Least Sign      | ificant Byte       |               |                    |                    |                       | 0000 0000            | 40,226  |

| 03h                | STATUS               | IRP                | RP1                                                               | RP0                | TO                 | PD            | Z                  | DC                 | С                     | 0001 1xxx            | 32,226  |

| 04h                | FSR                  | Indirect Da        | ata Memory A                                                      | Address Poin       | ter                |               |                    |                    |                       | xxxx xxxx            | 41,226  |

| 05h                | PORTA                | RA7                | RA6                                                               | RA5                | RA4                | RA3           | RA2                | RA1                | RA0                   | xxxx xxxx            | 44,226  |

| 06h                | PORTB                | RB7                | RB6                                                               | RB5                | RB4                | RB3           | RB2                | RB1                | RB0                   | xxxx xxxx            | 54,226  |

| 07h                | PORTC                | RC7                | RC6                                                               | RC5                | RC4                | RC3           | RC2                | RC1                | RC0                   | xxxx xxxx            | 62,226  |

| 08h                | PORTD <sup>(2)</sup> | RD7                | RD6                                                               | RD5                | RD4                | RD3           | RD2                | RD1                | RD0                   | xxxx xxxx            | 71,226  |

| 09h                | PORTE                | RE7 <sup>(3)</sup> | RE6 <sup>(3)</sup>                                                | RE5 <sup>(3)</sup> | RE4 <sup>(3)</sup> | RE3           | RE2 <sup>(2)</sup> | RE1 <sup>(2)</sup> | RE0 <sup>(2)</sup>    | xxxx xxxx            | 76,226  |

| 0Ah                | PCLATH               | _                  | —                                                                 | _                  | Write Buffer       | for upper 5   | bits of Progr      | am Counter         |                       | 0 0000               | 40,226  |

| 0Bh                | INTCON               | GIE                | PEIE                                                              | T0IE               | INTE               | RBIE          | T0IF               | INTF               | RBIF                  | 0000 000x            | 34,226  |

| 0Ch                | PIR1                 | EEIF               | ADIF                                                              | RCIF               | TXIF               | SSPIF         | CCP1IF             | TMR2IF             | TMR1IF                | 0000 0000            | 37,226  |

| 0Dh                | PIR2                 | OSFIF              | C2IF                                                              | C1IF               | LCDIF              | _             | LVDIF              | _                  | CCP2IF <sup>(2)</sup> | 0000 -0-0            | 38,226  |

| 0Eh                | TMR1L                | Holding Re         | egister for the                                                   | e Least Signi      | ficant Byte of     | the 16-bit TI | MR1                |                    |                       | xxxx xxxx            | 102,226 |

| 0Fh                | TMR1H                | Holding Re         | Holding Register for the Most Significant Byte of the 16-bit TMR1 |                    |                    |               |                    |                    |                       | xxxx xxxx            | 102,226 |

| 10h                | T1CON                | T1GINV             | TMR1GE                                                            | T1CKPS1            | T1CKPS0            | T1OSCEN       | T1SYNC             | TMR1CS             | TMR10N                | 0000 0000            | 105,226 |

| 11h                | TMR2                 | Timer2 Mc          | dule Registe                                                      | er                 |                    |               |                    |                    |                       | 0000 0000            | 107,226 |

| 12h                | T2CON                | _                  | TOUTPS3                                                           | TOUTPS2            | TOUTPS1            | TOUTPS0       | TMR2ON             | T2CKPS1            | T2CKPS0               | -000 0000            | 108,226 |

| 13h                | SSPBUF               | Synchrono          | ous Serial Po                                                     | rt Receive B       | uffer/Transmi      | t Register    |                    |                    |                       | xxxx xxxx            | 196,226 |

| 14h                | SSPCON               | WCOL               | SSPOV                                                             | SSPEN              | CKP                | SSPM3         | SSPM2              | SSPM1              | SSPM0                 | 0000 0000            | 195,226 |

| 15h                | CCPR1L               | Capture/C          | ompare/PWN                                                        | A Register 1       | (LSB)              |               |                    |                    |                       | xxxx xxxx            | 213,226 |

| 16h                | CCPR1H               | Capture/C          | ompare/PWN                                                        | A Register 1       | (MSB)              |               |                    |                    |                       | xxxx xxxx            | 213,226 |

| 17h                | CCP1CON              | _                  | —                                                                 | CCP1X              | CCP1Y              | CCP1M3        | CCP1M2             | CCP1M1             | CCP1M0                | 00 0000              | 212,226 |

| 18h                | RCSTA                | SPEN               | RX9                                                               | SREN               | CREN               | ADDEN         | FERR               | OERR               | RX9D                  | 0000 000x            | 131,226 |

| 19h                | TXREG                | USART Tr           | ansmit Data                                                       | Register           |                    |               |                    |                    | •                     | 0000 0000            | 130,226 |

| 1Ah                | RCREG                | USART Re           | eceive Data F                                                     | Register           |                    |               |                    |                    |                       | 0000 0000            | 128,227 |

| 1Bh <sup>(2)</sup> | CCPR2L               | Capture/C          | ompare/PWN                                                        | A Register 2       | (LSB)              |               |                    |                    |                       | xxxx xxxx            | 213,227 |

| 1Ch <sup>(2)</sup> | CCPR2H               | Capture/C          | ompare/PWN                                                        | A Register 2       | (MSB)              |               |                    |                    |                       | xxxx xxxx            | 213,227 |

| 1Dh <sup>(2)</sup> | CCP2CON              | —                  | _                                                                 | CCP2X              | CCP2Y              | CCP2M3        | CCP2M2             | CCP2M1             | CCP2M0                | 00 0000              | 212,227 |

| 1Eh                | ADRESH               | A/D Resul          | t Register Hig                                                    | gh Byte            |                    |               | •                  |                    |                       | xxxx xxxx            | 182,227 |

| 1Fh                | ADCON0               | ADFM               | VCFG1                                                             | VCFG0              | CHS2               | CHS1          | CHS0               | GO/DONE            | ADON                  | 0000 0000            | 180,227 |

#### TABLE 2-1: PIC16F91X/946 SPECIAL FUNCTION REGISTERS SUMMARY BANK 0

Legend: -= Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

Note 1: Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

2: PIC16F914/917 and PIC16F946 only, forced '0' on PIC16F913/916.

3: PIC16F946 only, forced to '0' on PIC16F91X.

#### 2.2.2.7 PIR2 Register

The PIR2 register contains the interrupt flag bits, as shown in Register 2-7.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-7: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | R/W-0 | U-0 | R/W-0                 |

|-------|-------|-------|-------|-----|-------|-----|-----------------------|

| OSFIF | C2IF  | C1IF  | LCDIF | —   | LVDIF | —   | CCP2IF <sup>(1)</sup> |

| bit 7 |       |       |       |     |       |     | bit 0                 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | OSFIF: Oscillator Fail Interrupt Flag bit                                                                                                                  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = System oscillator failed, clock input has changed to INTOSC (must be cleared in software)</li> <li>0 = System clock operating</li> </ul>      |

| bit 6   | C2IF: Comparator C2 Interrupt Flag bit                                                                                                                     |

|         | <ul> <li>1 = Comparator output (C2OUT bit) has changed (must be cleared in software)</li> <li>0 = Comparator output (C2OUT bit) has not changed</li> </ul> |

| bit 5   | C1IF: Comparator C1 Interrupt Flag bit                                                                                                                     |

|         | <ul> <li>1 = Comparator output (C1OUT bit) has changed (must be cleared in software)</li> <li>0 = Comparator output (C1OUT bit) has not changed</li> </ul> |

| bit 4   | LCDIF: LCD Module Interrupt bit                                                                                                                            |

|         | 1 = LCD has generated an interrupt                                                                                                                         |

|         | 0 = LCD has not generated an interrupt                                                                                                                     |

| bit 3   | Unimplemented: Read as '0'                                                                                                                                 |

| bit 2   | LVDIF: Low Voltage Detect Interrupt Flag bit                                                                                                               |

|         | 1 = LVD has generated an interrupt                                                                                                                         |

|         | 0 = LVD has not generated an interrupt                                                                                                                     |

| bit 1   | Unimplemented: Read as '0'                                                                                                                                 |

| bit 0   | CCP2IF: CCP2 Interrupt Flag bit <sup>(1)</sup>                                                                                                             |

|         | Capture Mode:                                                                                                                                              |

|         | <ul> <li>1 = A TMR1 register capture occurred (must be cleared in software)</li> <li>0 = No TMR1 register capture occurred</li> </ul>                      |

|         | Compare Mode:                                                                                                                                              |

|         | <ul> <li>1 = A TMR1 register compare match occurred (must be cleared in software)</li> <li>0 = No TMR1 register compare match occurred</li> </ul>          |

|         | PWM mode:                                                                                                                                                  |

|         | Unused in this mode                                                                                                                                        |

| Note 1: | PIC16F914/PIC16F917/PIC16F946 only.                                                                                                                        |

#### REGISTER 3-4: PORTB: PORTB REGISTER

| R/W-x                              | R/W-x | R/W-x | R/W-x             | R/W-x            | R/W-x           | R/W-x | R/W-x |

|------------------------------------|-------|-------|-------------------|------------------|-----------------|-------|-------|

| RB7                                | RB6   | RB5   | RB4               | RB3              | RB2             | RB1   | RB0   |

| bit 7                              |       |       |                   |                  |                 |       | bit 0 |

|                                    |       |       |                   |                  |                 |       |       |

| Legend:                            |       |       |                   |                  |                 |       |       |

| R = Readable bit W = Writable bit  |       |       | U = Unimplen      | nented bit, read | l as '0'        |       |       |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |       |

bit 7-0 **RB<7:0>:** PORTB I/O Pin bits 1 = Port pin is >VIH min. 0 = Port pin is <VIL max.

#### REGISTER 3-5: TRISB: PORTB TRI-STATE REGISTER

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0

TRISB<7:0>: PORTB Tri-State Control bits

1 = PORTB pin configured as an input (tri-stated)

0 = PORTB pin configured as an output

#### REGISTER 3-6: IOCB: PORTB INTERRUPT-ON-CHANGE REGISTER

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-------|-------|-----|-----|-----|-------|

| IOCB7 | IOCB6 | IOCB5 | IOCB4 | —   | —   | —   | —     |

| bit 7 |       |       |       |     |     |     | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-4 **IOCB<7:4>:** Interrupt-on-Change bits 1 = Interrupt-on-change enabled 0 = Interrupt-on-change disabled

bit 3-0 Unimplemented: Read as '0'

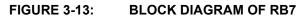

#### 3.4.3.8 RB7/ICSPDAT/ICDDAT/SEG13

Figure 3-13 shows the diagram for this pin. The RB7 pin is configurable to function as one of the following:

- a general purpose I/O

- an In-Circuit Serial Programming<sup>™</sup> I/O

- an ICD data I/O

- an analog output for the LCD

#### 4.5.3 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is an uncalibrated 31 kHz internal clock source.

The output of the LFINTOSC connects to a postscaler and multiplexer (see Figure 4-1). Select 31 kHz, via software, using the IRCF<2:0> bits of the OSCCON register. See **Section 4.5.4 "Frequency Select Bits (IRCF)**" for more information. The LFINTOSC is also the frequency for the Power-up Timer (PWRT), Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The LFINTOSC is enabled by selecting 31 kHz (IRCF<2:0> bits of the OSCCON register = 000) as the system clock source (SCS bit of the OSCCON register = 1), or when any of the following are enabled:

- Two-Speed Start-up IESO bit of the Configuration Word register = 1 and IRCF<2:0> bits of the OSCCON register = 000

- Power-up Timer (PWRT)

- Watchdog Timer (WDT)

- Fail-Safe Clock Monitor (FSCM)

The LF Internal Oscillator (LTS) bit of the OSCCON register indicates whether the LFINTOSC is stable or not.

#### 4.5.4 FREQUENCY SELECT BITS (IRCF)

The output of the 8 MHz HFINTOSC and 31 kHz LFINTOSC connects to a postscaler and multiplexer (see Figure 4-1). The Internal Oscillator Frequency Select bits IRCF<2:0> of the OSCCON register select the frequency output of the internal oscillators. One of eight frequencies can be selected via software:

- 8 MHz

- 4 MHz (Default after Reset)

- 2 MHz

- 1 MHz

- 500 kHz

- 250 kHz

- 125 kHz

- 31 kHz (LFINTOSC)

| Note: | Following any Reset, the IRCF<2:0> bits of |

|-------|--------------------------------------------|

|       | the OSCCON register are set to '110' and   |

|       | the frequency selection is set to 4 MHz.   |

|       | The user can modify the IRCF bits to       |

|       | select a different frequency.              |

#### 4.5.5 HF AND LF INTOSC CLOCK SWITCH TIMING

When switching between the LFINTOSC and the HFINTOSC, the new oscillator may already be shut down to save power (see Figure 4-6). If this is the case, there is a delay after the IRCF<2:0> bits of the OSCCON register are modified before the frequency selection takes place. The LTS and HTS bits of the OSCCON register will reflect the current active status of the LFINTOSC and HFINTOSC oscillators. The timing of a frequency selection is as follows:

- 1. IRCF<2:0> bits of the OSCCON register are modified.

- 2. If the new clock is shut down, a clock start-up delay is started.

- 3. Clock switch circuitry waits for a falling edge of the current clock.

- 4. CLKOUT is held low and the clock switch circuitry waits for a rising edge in the new clock.

- CLKOUT is now connected with the new clock. LTS and HTS bits of the OSCCON register are updated as required.

- 6. Clock switch is complete.

See Figure 4-1 for more details.

If the internal oscillator speed selected is between 8 MHz and 125 kHz, there is no start-up delay before the new frequency is selected. This is because the old and new frequencies are derived from the HFINTOSC via the postscaler and multiplexer.

Start-up delay specifications are located under the oscillator parameters of **Section 19.0** "**Electrical Specifications**".

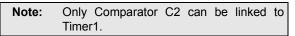

### 8.0 COMPARATOR MODULE

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. The comparators are very useful mixed signal building blocks because they provide analog functionality independent of the program execution. The Analog Comparator module includes the following features:

- Dual comparators

- Multiple comparator configurations

- Comparator outputs are available internally/externally

- Programmable output polarity

- · Interrupt-on-change

- · Wake-up from Sleep

- Timer1 gate (count enable)

- Output synchronization to Timer1 clock input

- Programmable voltage reference

#### 8.1 Comparator Overview

A comparator is shown in Figure 8-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

This device contains two comparators as shown in Figure 8-2 and Figure 8-3. The comparators are not independently configurable.

|        | SYNC = 0, BRGH = 1 |            |                             |                   |            |                             |                  |            |                             |                  |            |                             |

|--------|--------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fosc = 4.000 MHz   |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 2.000 MHz |            |                             | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    |                    | _          | _                           | _                 |            | _                           |                  | _          | _                           | 300              | 0.16       | 207                         |

| 1200   | 1202               | 0.16       | 207                         | 1200              | 0.00       | 191                         | 1202             | 0.16       | 103                         | 1202             | 0.16       | 51                          |

| 2400   | 2404               | 0.16       | 103                         | 2400              | 0.00       | 95                          | 2404             | 0.16       | 51                          | 2404             | 0.16       | 25                          |

| 9600   | 9615               | 0.16       | 25                          | 9600              | 0.00       | 23                          | 9615             | 0.16       | 12                          | _                | _          | _                           |

| 10417  | 10417              | 0.00       | 23                          | 10473             | 0.53       | 21                          | 10417            | 0.00       | 11                          | 10417            | 0.00       | 5                           |

| 19.2k  | 19.23k             | 0.16       | 12                          | 19.2k             | 0.00       | 11                          | _                | _          | _                           | _                | _          | _                           |

| 57.6k  | —                  | _          | _                           | 57.60k            | 0.00       | 3                           | —                | _          | _                           | —                | _          | _                           |

| 115.2k | —                  | _          | —                           | 115.2k            | 0.00       | 1                           | _                | _          | —                           | _                | _          | —                           |

#### TABLE 9-5: BAUD RATES FOR ASYNCHRONOUS MODES

#### 9.3.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the AUSART for Synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the AUSART.

The LCD SEG8 and SEG9 functions must be disabled by clearing the SE8 and SE9 bits of the LCDSE1 register, if the RX/DT and TX/CK pins are shared with the LCD peripheral.

#### 9.3.2.1 AUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see Section 9.3.1.2 "Synchronous Master Transmission"), except in the case of the Sleep mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in TXREG register.

- 3. The TXIF bit will not be set.

- After the first character has been shifted out of TSR, the TXREG register will transfer the second character to the TSR and the TXIF bit will now be set.

- 5. If the PEIE and TXIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 9.3.2.2 Synchronous Slave Transmission Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the CREN and SREN bits.

- 3. If using interrupts, ensure that the GIE and PEIE bits of the INTCON register are set and set the TXIE bit.

- 4. If 9-bit transmission is desired, set the TX9 bit.

- 5. Enable transmission by setting the TXEN bit.

- 6. Verify address detection is disabled by clearing the ADDEN bit of the RCSTA register.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant 8 bits to the TXREG register.

| Name   | Bit 7                              | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|------------------------------------|--------|--------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE                                | PEIE   | T0IE   | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| LCDCON | LCDEN                              | SLPEN  | WERR   | VLCDEN | CS1    | CS0    | LMUX1  | LMUX0  | 0001 0011            | 0001 0011                       |

| LCDSE1 | SE15                               | SE14   | SE13   | SE12   | SE11   | SE10   | SE9    | SE8    | 0000 0000            | 0000 0000                       |

| PIE1   | EEIE                               | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | EEIF                               | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN                               | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | X000 000X            | 0000 000X                       |

| SSPCON | WCOL                               | SSPOV  | SSPEN  | CKP    | SSPM3  | SSPM2  | SSPM1  | SSPM0  | 0000 0000            | 0000 0000                       |

| TRISC  | TRISC7                             | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| TXREG  | XREG AUSART Transmit Data Register |        |        |        |        |        |        |        |                      | 0000 0000                       |

| TXSTA  | CSRC                               | TX9    | TXEN   | SYNC   | _      | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

TABLE 9-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Slave Transmission.

NOTES:

| R/W-0         | R/W-0                        | R-0                                 | R-0              | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|---------------|------------------------------|-------------------------------------|------------------|------------------|-----------------|-----------------|-------|

| WFT           | BIASMD                       | LCDA                                | WA               | LP3              | LP2             | LP1             | LP0   |

| bit 7         | 1                            |                                     |                  |                  | 1               | •               | bit   |

|               |                              |                                     |                  |                  |                 |                 |       |

| Legend:       |                              |                                     |                  |                  |                 |                 |       |

| R = Readabl   | le bit                       | W = Writable                        | bit              | U = Unimple      | mented bit, rea | d as '0'        |       |

| -n = Value at | POR                          | '1' = Bit is set                    |                  | '0' = Bit is cle | eared           | x = Bit is unkr | nown  |

| bit 7         | WFT: Wavefe                  | orm Type Selec                      | t bit            |                  |                 |                 |       |

|               |                              | vaveform (phas<br>vaveform (phas    |                  |                  |                 |                 |       |

| bit 6         | BIASMD: Bia                  | as Mode Select                      | bit              |                  |                 |                 |       |

|               | When LMUX                    | < <u>1:0&gt; = 00:</u>              |                  |                  |                 |                 |       |

|               | 0 = Static Bia               | as mode (do no                      | t set this bit t | oʻ1')            |                 |                 |       |

|               | When LMUX                    |                                     |                  |                  |                 |                 |       |

|               | 1 = 1/2 Bias                 |                                     |                  |                  |                 |                 |       |

|               | 0 = 1/3 Bias<br>When LMUX    |                                     |                  |                  |                 |                 |       |

|               | 1 = 1/2 Bias                 |                                     |                  |                  |                 |                 |       |

|               | 1 = 1/2 Bias<br>0 = 1/3 Bias |                                     |                  |                  |                 |                 |       |

|               | When LMUX                    |                                     |                  |                  |                 |                 |       |

|               | 0 = 1/3 Bias                 | mode (do not s                      | et this bit to ' | 1')              |                 |                 |       |

| bit 5         | LCDA: LCD                    | Active Status bi                    | t                |                  |                 |                 |       |

|               |                              | er module is ac<br>er module is ina |                  |                  |                 |                 |       |

| bit 4         | WA: LCD W                    | rite Allow Status                   | bit              |                  |                 |                 |       |

|               |                              | o the LCDDATA<br>o the LCDDATA      |                  |                  |                 |                 |       |

| bit 3-0       |                              | D Prescaler Se                      | -                |                  |                 |                 |       |

|               | 1111 <b>= 1:16</b>           |                                     |                  |                  |                 |                 |       |

|               | 1110 = 1:15                  |                                     |                  |                  |                 |                 |       |

|               | 1101 = 1:14<br>1100 = 1:13   |                                     |                  |                  |                 |                 |       |

|               | 1011 = 1:12                  |                                     |                  |                  |                 |                 |       |

|               | 1010 = 1:11                  |                                     |                  |                  |                 |                 |       |

|               | 1001 = 1:10                  |                                     |                  |                  |                 |                 |       |

|               | 1000 = 1:9                   |                                     |                  |                  |                 |                 |       |

|               | 0111 = 1:8                   |                                     |                  |                  |                 |                 |       |

|               | 0110 = 1:7<br>0101 = 1:6     |                                     |                  |                  |                 |                 |       |

|               | 0100 = 1:5                   |                                     |                  |                  |                 |                 |       |

|               | 0011 = 1:4                   |                                     |                  |                  |                 |                 |       |

|               | 0010 = 1:3                   |                                     |                  |                  |                 |                 |       |

|               | 0001 = 1:2                   |                                     |                  |                  |                 |                 |       |

|               | 0000 = 1:1                   |                                     |                  |                  |                 |                 |       |

#### REGISTER 10-2: LCDPS: LCD PRESCALER SELECT REGISTER

#### 14.12.3 TRANSMISSION

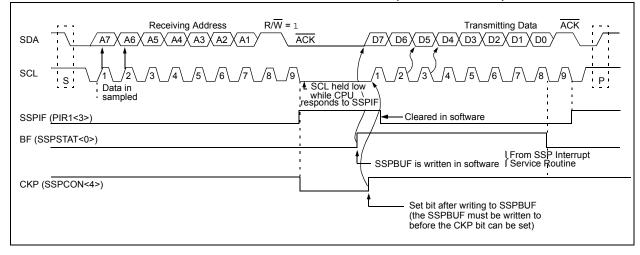

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will ninth bit. be sent on the and pin RC6/TX/CK/SCK/SCL/SEG9 is held low. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then, pin RC6/TX/CK/SCK/SCL/SEG9 should be enabled by setting bit CKP of the SSPCON register. The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 14-10).

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF must be cleared in software, and the SSPSTAT register is used to determine the status of the byte. Flag bit SSPIF is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the  $\overline{ACK}$  pulse from the master receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not  $\overline{ACK}$ ), then the data transfer is complete. When the  $\overline{ACK}$  is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave then monitors for another occurrence of the Start bit. If the SDA line was low ( $\overline{ACK}$ ), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin RC6/TX/CK/SCK/SCL/SEG9 should be enabled by setting bit CKP.

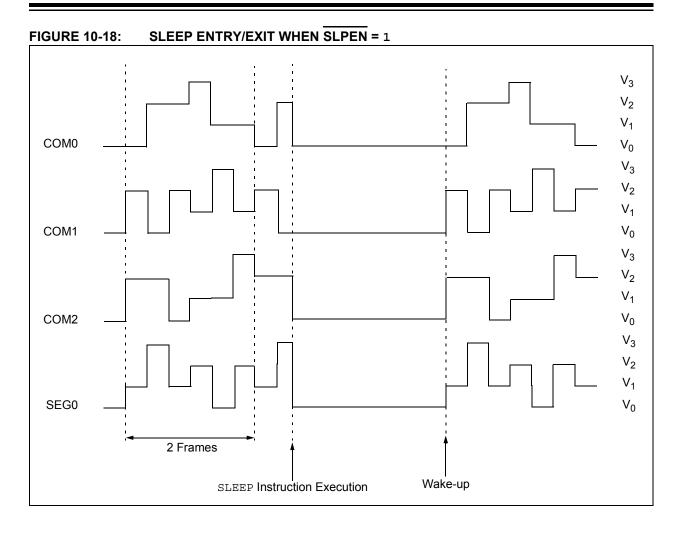

#### FIGURE 14-10: I<sup>2</sup>C<sup>™</sup> WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

| REGISTER 16-2: | WDTCON – WATCHDOG TIMER CONTROL REGISTER (ADDRESS: 105h) |            |                 |        |        |        |        |        |  |  |  |

|----------------|----------------------------------------------------------|------------|-----------------|--------|--------|--------|--------|--------|--|--|--|

|                | U-0                                                      | U-0        | U-0             | R/W-0  | R/W-1  | R/W-0  | R/W-0  | R/W-0  |  |  |  |

|                |                                                          | _          | —               | WDTPS3 | WDTPS2 | WDTPS1 | WDTPS0 | SWDTEN |  |  |  |

|                | bit 7                                                    |            |                 |        |        |        |        | bit 0  |  |  |  |

|                |                                                          |            |                 |        |        |        |        |        |  |  |  |

| bit 7-5        | Unimplem                                                 | ented: Rea | <b>d as</b> '0' |        |        |        |        |        |  |  |  |

|                |                                                          |            |                 |        |        |        |        |        |  |  |  |

bit 4-1 WDTPS<3:0>: Watchdog Timer Period Select bits

Bit Value = Prescale Rate 0000 = 1:320001 = 1:64 0010 = 1:128 0011 = 1:256 0100 = 1:512 (Reset value) 0101 = 1:1024 0110 = 1:2048 0111 = 1:4096 1000 = 1:8192 1001 = 1:16384 1010 = 1:32768 1011 = 1:65536 1100 = reserved 1101 = reserved 1110 = reserved 1111 = reserved

SWDTEN: Software Enable or Disable the Watchdog Timer bit<sup>(1)</sup> bit 0

1 = WDT is turned on

0 = WDT is turned off (Reset value)

Note 1: If WDTE Configuration bit = 1, then WDT is always enabled, irrespective of this control bit. If WDTE Configuration bit = 0, then it is possible to turn WDT on/off with this control bit.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### SUMMARY OF WATCHDOG TIMER REGISTERS TABLE 16-8:

| Name       | Bit 7 | Bit 6  | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|------------|-------|--------|-------|--------|--------|--------|--------|--------|

| CONFIG     | CPD   | CP     | MCLRE | PWRTE  | WDTE   | FOSC2  | FOSC1  | FOSC0  |

| OPTION_REG | RBPU  | INTEDG | TOCS  | T0SE   | PSA    | PS2    | PS1    | PS0    |

| WDTCON     | -     | —      | —     | WDTPS3 | WDTPS2 | WSTPS1 | WDTPS0 | SWDTEN |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Register 16-1 for operation of all Configuration Word register bits.

#### 18.11 PICSTART Plus Development Programmer

The PICSTART Plus Development Programmer is an easy-to-use, low-cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. The PICSTART Plus Development Programmer supports most PIC devices in DIP packages up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus Development Programmer is CE compliant.

### 18.12 PICkit 2 Development Programmer

The PICkit<sup>™</sup> 2 Development Programmer is a low-cost programmer and selected Flash device debugger with an easy-to-use interface for programming many of Microchip's baseline, mid-range and PIC18F families of Flash memory microcontrollers. The PICkit 2 Starter Kit includes a prototyping development board, twelve sequential lessons, software and HI-TECH's PICC<sup>™</sup> Lite C compiler, and is designed to help get up to speed quickly using PIC<sup>®</sup> microcontrollers. The kit provides everything needed to program, evaluate and develop applications using Microchip's powerful, mid-range Flash memory family of microcontrollers.

### 18.13 Demonstration, Development and Evaluation Boards

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart<sup>®</sup> battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Check the Microchip web page (www.microchip.com) and the latest *"Product Selector Guide"* (DS00148) for the complete list of demonstration, development and evaluation kits.

#### 19.3 DC Characteristics: PIC16F913/914/916/917/946-I (Industrial)

| DC CHARACTERISTICS |                             |      | ard Oper |      |       |            | <b>s otherwise stated)</b><br>35°C for industrial |  |  |

|--------------------|-----------------------------|------|----------|------|-------|------------|---------------------------------------------------|--|--|

| Param P            |                             | Min  | Truck    |      | Unite | Conditions |                                                   |  |  |

| No.                | Device Characteristics      | Min. | Тур†     | Max. | Units | VDD        | Note                                              |  |  |

| D020               | Power-down Base             | _    | 0.05     | 1.2  | μA    | 2.0        | WDT, BOR, Comparators, VREF and                   |  |  |

|                    | Current(IPD) <sup>(2)</sup> | —    | 0.15     | 1.5  | μA    | 3.0        | T1OSC disabled                                    |  |  |

|                    |                             | —    | 0.35     | 1.8  | μA    | 5.0        |                                                   |  |  |

|                    |                             | _    | 150      | 500  | nA    | 3.0        | $-40^{\circ}C \le T_A \le +25^{\circ}C$           |  |  |

| D021               |                             | _    | 1.0      | 2.2  | μA    | 2.0        | WDT Current <sup>(1)</sup>                        |  |  |

|                    |                             | —    | 2.0      | 4.0  | μA    | 3.0        |                                                   |  |  |

|                    |                             | _    | 3.0      | 7.0  | μA    | 5.0        |                                                   |  |  |

| D022A              |                             | _    | 42       | 60   | μA    | 3.0        | BOR Current <sup>(1)</sup>                        |  |  |

|                    |                             | _    | 85       | 122  | μA    | 5.0        |                                                   |  |  |

| D022B              |                             | _    | 22       | 28   | μA    | 2.0        | PLVD Current                                      |  |  |

|                    |                             | _    | 25       | 35   | μA    | 3.0        |                                                   |  |  |

|                    |                             | —    | 33       | 45   | μA    | 5.0        |                                                   |  |  |

| D023               |                             | _    | 32       | 45   | μA    | 2.0        | Comparator Current <sup>(1)</sup> , both          |  |  |

|                    |                             | _    | 60       | 78   | μA    | 3.0        | comparators enabled                               |  |  |

|                    |                             | —    | 120      | 160  | μA    | 5.0        |                                                   |  |  |

| D024               |                             | —    | 30       | 36   | μA    | 2.0        | CVREF Current <sup>(1)</sup> (high range)         |  |  |

|                    |                             | _    | 45       | 55   | μA    | 3.0        |                                                   |  |  |

|                    |                             | _    | 75       | 95   | μA    | 5.0        |                                                   |  |  |

| D025*              |                             | _    | 39       | 47   | μA    | 2.0        | CVREF Current <sup>(1)</sup> (low range)          |  |  |

|                    |                             | —    | 59       | 72   | μA    | 3.0        |                                                   |  |  |

|                    |                             | —    | 98       | 124  | μA    | 5.0        |                                                   |  |  |

| D026               |                             | _    | 2.0      | 5.0  | μA    | 2.0        | T1OSC Current <sup>(1)</sup> , 32.768 kHz         |  |  |

|                    |                             |      | 2.5      | 5.5  | μA    | 3.0        |                                                   |  |  |

|                    |                             |      | 3.0      | 7.0  | μA    | 5.0        |                                                   |  |  |

| D027               |                             | —    | 0.30     | 1.6  | μA    | 3.0        | A/D Current <sup>(1)</sup> , no conversion in     |  |  |

|                    |                             | _    | 0.36     | 1.9  | μA    | 5.0        | progress                                          |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral ∆ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

### Package Marking Information (Continued)

44-Lead QFN

#### 28-Lead SOIC

#### 28-Lead SSOP

#### 44-Lead TQFP

#### 64-Lead TQFP (10x10x1mm)

#### Example

#### Example

#### Example

#### Example

#### Example

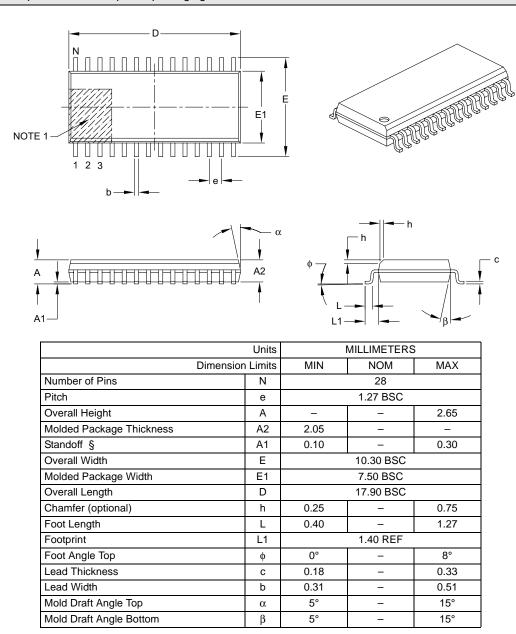

#### 28-Lead Plastic Small Outline (SO) – Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-052B

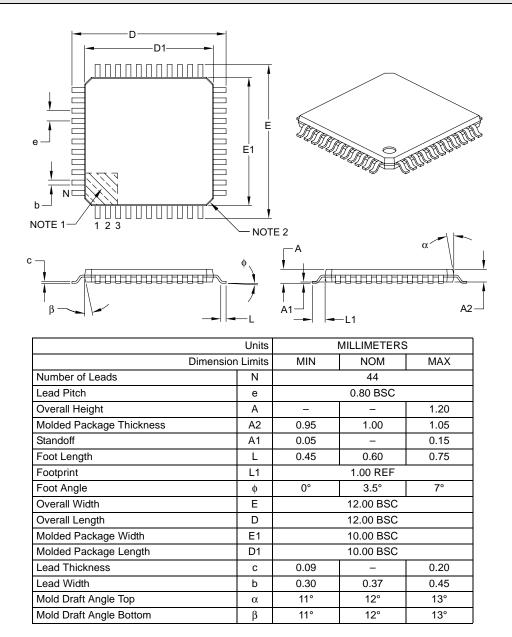

#### 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076B

| Registers                     | 62 |

|-------------------------------|----|

| TRISC Register                | 62 |

| TRISD                         |    |

| Registers                     | 71 |

| TRISD Register                | 71 |

| TRISE                         |    |

| Registers                     | 76 |

| TRISE Register                | 76 |

| TRISF                         |    |

| Registers                     | 81 |

| TRISF Register                | 81 |

| TRISG                         |    |

| Registers                     |    |

| TRISG Register                |    |

| Two-Speed Clock Start-up Mode |    |

| TXREG                         |    |

| TXSTA Register                |    |

| BRGH Bit                      |    |

### U

| UA                                           |  |

|----------------------------------------------|--|

| Synchronous Master Mode                      |  |

| Requirements, Synchronous Receive            |  |

| Requirements, Synchronous Transmission 275   |  |

| Timing Diagram, Synchronous Receive          |  |

| Timing Diagram, Synchronous Transmission 275 |  |

|                                              |  |

#### V

| Voltage Reference. See Comparator Voltage |   |

|-------------------------------------------|---|

| Reference (CVREF)                         |   |

| Voltage References                        |   |

| Associated registers11                    | 9 |

| VREF. SEE ADC Reference Voltage           |   |

#### W

| Wake-up Using Interrupts          | 236 |

|-----------------------------------|-----|

| Watchdog Timer (WDT)              | 234 |

| Associated Registers              | 235 |

| Clock Source                      | 234 |

| Modes                             | 234 |

| Period                            | 234 |

| Specifications                    | 269 |

| WCOL bit                          | 195 |

| WDTCON Register                   | 235 |

| WPUB Register                     | 55  |

| Write Collision Detect bit (WCOL) | 195 |

| WWW Address                       | 325 |

| WWW, On-Line Support              | 13  |

|                                   |     |