Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I²C, SPI, UART/USART                                                      |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                |

| Number of I/O              | 24                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-QFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f913t-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| IABL | BLE 6: PIC16F946 64-PIN (TQFP) SUMMARY (CONTINUED) |     |       |             |        |     |        |     |           |         |       |

|------|----------------------------------------------------|-----|-------|-------------|--------|-----|--------|-----|-----------|---------|-------|

| I/O  | Pin                                                | A/D | LCD   | Comparators | Timers | ССР | AUSART | SSP | Interrupt | Pull-Up | Basic |

| RF3  | 14                                                 |     | SEG35 | —           | _      |     | —      |     |           | —       | _     |

| RF4  | 45                                                 |     | SEG28 | _           |        |     | _      |     |           | _       | _     |

| RF5  | 46                                                 | _   | SEG29 | _           | _      | _   | _      | _   | _         | _       | —     |

| RF6  | 47                                                 | _   | SEG30 | _           | —      | _   | _      | _   | _         | —       | —     |

| RF7  | 48                                                 | _   | SEG31 | _           | _      | _   | _      | _   | _         | _       | —     |

| RG0  | 3                                                  | _   | SEG36 | _           | —      | _   | _      | _   | _         | —       | —     |

| RG1  | 4                                                  |     | SEG37 | _           | _      | _   | _      | _   | _         | _       | _     |

| RG2  | 5                                                  | _   | SEG38 | _           | —      | _   | —      | _   | _         | —       | —     |

| RG3  | 6                                                  | _   | SEG39 | _           | _      | _   | _      | _   | _         | _       | —     |

| RG4  | 7                                                  | _   | SEG40 | _           | —      | _   | _      | _   | _         | —       | —     |

| RG5  | 8                                                  | _   | SEG41 | _           | _      | _   | _      | _   | _         | _       | —     |

| _    | 26                                                 | _   | —     | _           | —      | _   | _      | _   | _         | —       | AVDD  |

| _    | 25                                                 |     | _     | _           | —      | _   | _      | _   | _         | _       | AVss  |

| _    | 10                                                 | _   | —     | _           | —      | _   | _      | _   | _         | —       | Vdd   |

| _    | 19                                                 |     | _     | _           | —      | _   | _      | _   | _         | _       | Vdd   |

| —    | 38                                                 | _   | _     | _           | —      | _   | —      | _   | —         | —       | VDD   |

| _    | 57                                                 |     | _     | _           | _      | _   | _      | _   | _         | _       | Vdd   |

| —    | 9                                                  | _   | _     | _           | _      | _   | _      | _   | _         | _       | Vss   |

| _    | 20                                                 | _   | _     | _           | _      | _   | —      | _   | _         | _       | Vss   |

| —    | 41                                                 | _   | _     | _           | _      | _   | _      | _   | _         | _       | Vss   |

|      | 56                                                 | —   | —     | —           | —      | _   | —      | _   | —         | —       | Vss   |

|      |                                                    |     |       |             |        |     |        |     |           |         |       |

## TABLE 6: PIC16F946 64-PIN (TQFP) SUMMARY (CONTINUED)

**Note 1:** Pull-up enabled only with external MCLR configuration.

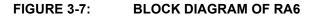

### 3.2.1.7 RA6/OSC2/CLKOUT/T1OSO

Figure 3-7 shows the diagram for this pin. The RA6 pin is configurable to function as one of the following:

- a general purpose I/O

- a crystal/resonator connection

- · a clock output

- a Timer1 oscillator connection

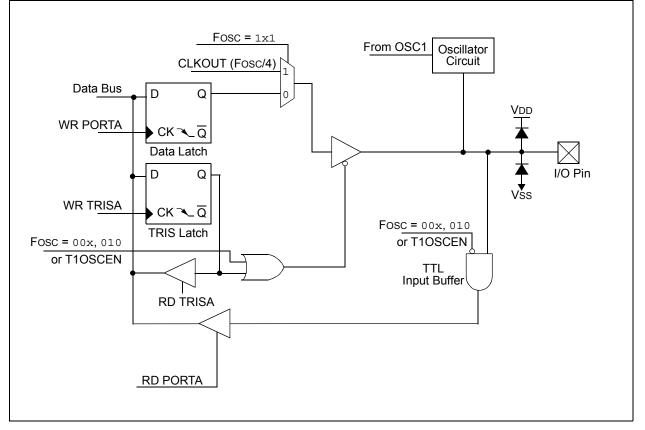

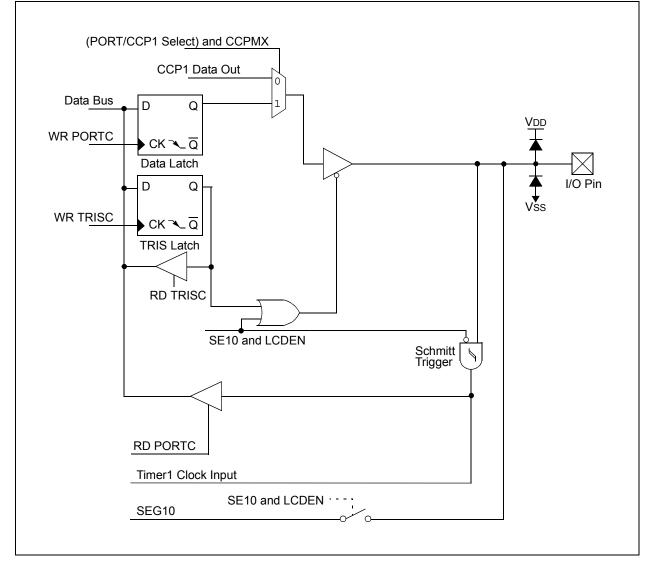

#### 3.5.1.6 RC5/T1CKI/CCP1/SEG10

Figure 3-19 shows the diagram for this pin. The RC5 pin is configurable to function as one of the following:

- a general purpose I/O

- a Timer1 clock input

- a Capture input, Compare output or PWM output

- an analog output for the LCD

## 3.8 PORTF and TRISF Registers

PORTF is an 8-bit port with Schmitt Trigger input buffers. RF<7:0> are individually configured as inputs or outputs, depending on the state of the port direction. The port bits are also multiplexed with LCD segment functions. PORTF is available on the PIC16F946 only.

#### EXAMPLE 3-6: INITIALIZING PORTF

| BANKSEL | PORTF | ;                      |

|---------|-------|------------------------|

| CLRF    | PORTF | ;Init PORTF            |

| BANKSEL | TRISF | ;                      |

| MOVLW   | OFFh  | ;Set RF<7:0> as inputs |

| MOVWF   | TRISF | ;                      |

## REGISTER 3-14: PORTF: PORTF REGISTER<sup>(1)</sup>

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| RF7   | RF6   | RF5   | RF4   | RF3   | RF2   | RF1   | RF0   |

| bit 7 |       |       | -     |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 **RF<7:0>**: PORTF I/O Pin bits

1 = Port pin is >VIH min.0 = Port pin is <VIL max.</li>

Note 1: PIC16F946 only.

#### REGISTER 3-15: TRISF: PORTF TRI-STATE REGISTER<sup>(1)</sup>

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TRISF7 | TRISF6 | TRISF5 | TRISF4 | TRISF3 | TRISF2 | TRISF1 | TRISF0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-0 **TRISF<7:0>:** PORTF Tri-State Control bits

1 = PORTF pin configured as an input (tri-stated)0 = PORTF pin configured as an output

Note 1: PIC16F946 only.

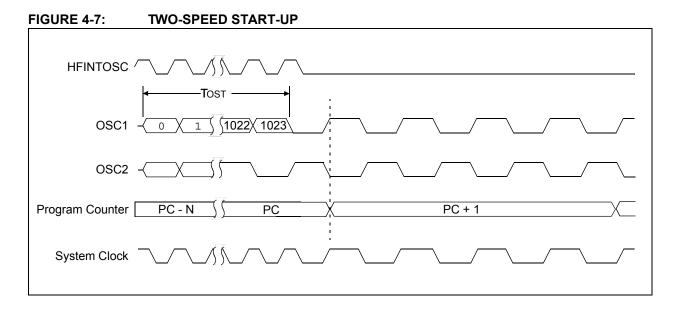

#### 4.7.3 CHECKING TWO-SPEED CLOCK STATUS

Checking the state of the OSTS bit of the OSCCON register will confirm if the microcontroller is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Word register (CONFIG), or the internal oscillator.

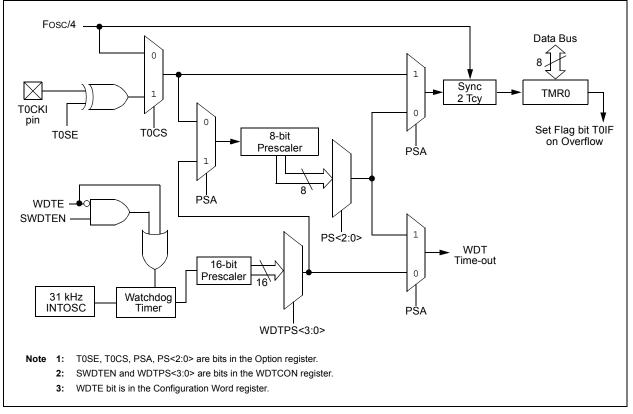

## 5.0 TIMER0 MODULE

The Timer0 module is an 8-bit timer/counter with the following features:

- 8-bit timer/counter register (TMR0)

- 8-bit prescaler (shared with Watchdog Timer)

- Programmable internal or external clock source

- · Programmable external clock edge selection

- · Interrupt on overflow

Figure 5-1 is a block diagram of the Timer0 module.

### 5.1 Timer0 Operation

When used as a timer, the Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

#### 5.1.1 8-BIT TIMER MODE

When used as a timer, the Timer0 module will increment every instruction cycle (without prescaler). Timer mode is selected by clearing the T0CS bit of the OPTION register to '0'.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

Note: The value written to the TMR0 register can be adjusted, in order to account for the two instruction cycle delay when TMR0 is written.

#### 5.1.2 8-BIT COUNTER MODE

When used as a counter, the Timer0 module will increment on every rising or falling edge of the T0CKI pin. The incrementing edge is determined by the T0SE bit of the Option register. Counter mode is selected by setting the T0CS bit of the Option register to '1'.

#### FIGURE 5-1: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

| REGISTER /      | -1. 1200                    |                  |               | LOISTER           |                 |                |         |  |  |  |  |

|-----------------|-----------------------------|------------------|---------------|-------------------|-----------------|----------------|---------|--|--|--|--|

| U-0             | R/W-0                       | R/W-0            | R/W-0         | R/W-0             | R/W-0           | R/W-0          | R/W-0   |  |  |  |  |

| —               | TOUTPS3                     | TOUTPS2          | TOUTPS1       | TOUTPS0           | TMR2ON          | T2CKPS1        | T2CKPS0 |  |  |  |  |

| bit 7           | ·                           |                  |               |                   |                 | ·              | bit 0   |  |  |  |  |

|                 |                             |                  |               |                   |                 |                |         |  |  |  |  |

| Legend:         |                             |                  |               |                   |                 |                |         |  |  |  |  |

| R = Readable    | bit                         | W = Writable     | bit           | U = Unimplen      | nented bit, rea | d as '0'       |         |  |  |  |  |

| -n = Value at F | POR                         | '1' = Bit is set |               | '0' = Bit is clea | ared            | x = Bit is unk | nown    |  |  |  |  |

|                 |                             |                  |               |                   |                 |                |         |  |  |  |  |

| bit 7           | Unimplemen                  | ted: Read as '   | 0'            |                   |                 |                |         |  |  |  |  |

| bit 6-3         | -                           | )>: Timer2 Out   |               | Select bits       |                 |                |         |  |  |  |  |

|                 | 0000 <b>= 1:1 P</b>         |                  |               |                   |                 |                |         |  |  |  |  |

|                 | 0001 <b>= 1:2</b> P         |                  |               |                   |                 |                |         |  |  |  |  |

|                 | 0010 <b>= 1:3 P</b>         | ostscaler        |               |                   |                 |                |         |  |  |  |  |

|                 | 0011 <b>= 1:4 P</b>         | ostscaler        |               |                   |                 |                |         |  |  |  |  |

|                 | 0100 = 1:5 Postscaler       |                  |               |                   |                 |                |         |  |  |  |  |

|                 | 0101 = 1:6 Postscaler       |                  |               |                   |                 |                |         |  |  |  |  |

|                 | 0110 = 1:7 P                |                  |               |                   |                 |                |         |  |  |  |  |

|                 | 0111 = 1:8 P                |                  |               |                   |                 |                |         |  |  |  |  |

|                 | 1000 = 1:9 P<br>1001 = 1:10 |                  |               |                   |                 |                |         |  |  |  |  |

|                 | 1010 = 1.101                |                  |               |                   |                 |                |         |  |  |  |  |

|                 | 1011 = 1:12                 |                  |               |                   |                 |                |         |  |  |  |  |

|                 | 1100 = 1:13                 |                  |               |                   |                 |                |         |  |  |  |  |

|                 | 1101 <b>= 1:14</b>          | Postscaler       |               |                   |                 |                |         |  |  |  |  |

|                 | 1110 <b>= 1:15</b>          | Postscaler       |               |                   |                 |                |         |  |  |  |  |

|                 | 1111 = 1:16                 | Postscaler       |               |                   |                 |                |         |  |  |  |  |

| bit 2           | TMR2ON: Tir                 | mer2 On bit      |               |                   |                 |                |         |  |  |  |  |

|                 | 1 = Timer2 is               |                  |               |                   |                 |                |         |  |  |  |  |

|                 | 0 = Timer2 is               | s off            |               |                   |                 |                |         |  |  |  |  |

| bit 1-0         | T2CKPS<1:0                  | >: Timer2 Cloc   | k Prescale Se | lect bits         |                 |                |         |  |  |  |  |

|                 | 00 = Prescale               | er is 1          |               |                   |                 |                |         |  |  |  |  |

|                 | 01 = Prescale               |                  |               |                   |                 |                |         |  |  |  |  |

|                 | 1x = Prescale               | er is 16         |               |                   |                 |                |         |  |  |  |  |

| TABLE 7-1:      |                             | V OF REGIS       | TERS ASSO     | CIATED WITH       |                 |                |         |  |  |  |  |

|                 |                             |                  |               |                   |                 |                |         |  |  |  |  |

### REGISTER 7-1: T2CON: TIMER 2 CONTROL REGISTER

| Name   | Bit 7                                        | Bit 6        | Bit 5    | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------------------------------------------|--------------|----------|---------|---------|--------|---------|---------|----------------------|---------------------------------|

| INTCON | GIE                                          | PEIE         | T0IE     | INTE    | RBIE    | T0IF   | INTF    | RBIF    | x000 0000x           | 0000 000x                       |

| PIE1   | EEIE                                         | ADIE         | RCIE     | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000            | 0000 0000                       |

| PIR1   | EEIF                                         | ADIF         | RCIF     | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000            | 0000 0000                       |

| PR2    | Timer2 M                                     | odule Period | Register |         |         |        |         |         | 1111 1111            | 1111 1111                       |

| TMR2   | Holding Register for the 8-bit TMR2 Register |              |          |         |         |        |         |         | 0000 0000            | 0000 0000                       |

| T2CON  | —                                            | TOUTPS3      | TOUTPS2  | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000            | -000 0000                       |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for Timer2 module.

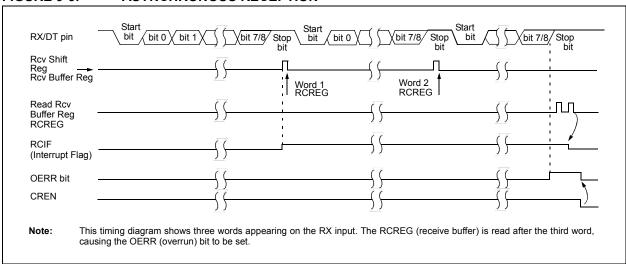

#### 9.1.2.8 Asynchronous Reception Set-up:

- Initialize the SPBRG register and the BRGH bit to achieve the desired baud rate (see Section 9.2 "AUSART Baud Rate Generator (BRG)").

- Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Enable reception by setting the CREN bit.

- The RCIF interrupt flag bit of the PIR1 register will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE bit of the PIE1 register was also set.

- 7. Read the RCSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 8. Get the received 8 Least Significant data bits from the receive buffer by reading the RCREG register.

- 9. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

#### 9.1.2.9 9-bit Address Detection Mode Set-up

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRG register and the BRGH bit to achieve the desired baud rate (see Section 9.2 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. Enable 9-bit reception by setting the RX9 bit.

- 5. Enable address detection by setting the ADDEN bit.

- 6. Enable reception by setting the CREN bit.

- The RCIF interrupt flag bit of the PIR1 register will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit of the PIE1 register was also set.

- 8. Read the RCSTA register to get the error flags. The ninth data bit will always be set.

- Get the received 8 Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

### FIGURE 9-5: ASYNCHRONOUS RECEPTION

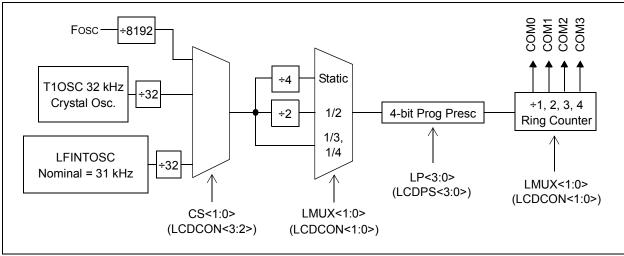

## FIGURE 10-3: LCD CLOCK GENERATION

NOTES:

| R/W-x            | U-0                             | U-0                                    | U-0          | R/W-x             | R/W-0            | R/S-0           | R/S-0          |

|------------------|---------------------------------|----------------------------------------|--------------|-------------------|------------------|-----------------|----------------|

| EEPGD            | —                               | _                                      | _            | WRERR             | WREN             | WR              | RD             |

| bit 7            |                                 | -                                      |              |                   |                  |                 | bit 0          |

|                  |                                 |                                        |              |                   |                  |                 |                |

| Legend:          |                                 |                                        |              |                   |                  |                 |                |

| S = Bit can only | / be set                        |                                        |              |                   |                  |                 |                |

| R = Readable b   | pit                             | W = Writable                           | bit          | U = Unimplen      | nented bit, read | l as '0'        |                |

| -n = Value at P  | OR                              | '1' = Bit is set                       |              | '0' = Bit is clea | ared             | x = Bit is unkr | nown           |

|                  |                                 |                                        |              |                   |                  |                 |                |

| bit 7            | EEPGD: Prog                     | gram/Data EEP                          | ROM Select   | bit               |                  |                 |                |

|                  |                                 | s program men                          | nory         |                   |                  |                 |                |

|                  |                                 | s data memory                          | .,           |                   |                  |                 |                |

| bit 6-4          | •                               | ted: Read as '                         |              |                   |                  |                 |                |

| bit 3            |                                 | PROM Error Fla                         | 0            | ninated (any MC   |                  |                 | rina           |

|                  |                                 | peration or BO                         |              |                   | LR Resel, any    | VDI Reseluu     | ing            |

|                  |                                 | operation com                          | ,            |                   |                  |                 |                |

| bit 2            | WREN: EEPP                      | ROM Write Ena                          | ble bit      |                   |                  |                 |                |

|                  | 1 = Allows wr                   | ,                                      |              |                   |                  |                 |                |

|                  |                                 | rite to the data                       | EEPROM       |                   |                  |                 |                |

| bit 1            | WR: Write Co                    | ontrol bit                             |              |                   |                  |                 |                |

|                  | EEPGD = 1:<br>This bit is ign   | ored                                   |              |                   |                  |                 |                |

|                  | <u>EEPGD = <math>0</math></u> : |                                        |              |                   |                  |                 |                |

|                  |                                 |                                        |              | ed by hardware    | once write is co | omplete. The W  | R bit can only |

|                  |                                 | ot cleared, in so<br>cle to the data E |              | omplete           |                  |                 |                |

| bit 0            | RD: Read Co                     |                                        |              |                   |                  |                 |                |

|                  |                                 |                                        | d (the RD is | cleared in hard   | lware and can    | only be set. n  | ot cleared. in |

|                  | software                        | .)                                     |              |                   |                  | , <b>.</b> ,    | ,              |

|                  | 0 = Does not                    | initiate a mem                         | ory read     |                   |                  |                 |                |

#### REGISTER 13-5: EECON1: EEPROM CONTROL REGISTER

#### 14.12.2 RECEPTION

ſ

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address <u>byte</u> overflow condition exists, then no Acknowledge ( $\overline{ACK}$ ) pulse is given. An overflow condition is defined as either bit BF of the SSPSTAT register is set, or bit SSPOV of the SSPCON register is set. This is an error condition due to the user's firmware.

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF of the PIR1 register must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

| FIGURE 14-8: I <sup>+</sup> C <sup>™</sup> WAVEFORMS FOR RECEPTION (7-BIT ADDRES | FIGURE 14-8: | I <sup>2</sup> C <sup>™</sup> WAVEFORMS FOR RECEPTION (7-BIT ADDRESS |

|----------------------------------------------------------------------------------|--------------|----------------------------------------------------------------------|

|----------------------------------------------------------------------------------|--------------|----------------------------------------------------------------------|

| · R/                                       | $\overline{V} = 0$                                                                                                                                         |                          |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Receiving Address                          | ACK Receiving Data ACK Receiving Data                                                                                                                      | ACK                      |

| SDA I / A7 / A6 / A5 / A4 / A3 / A2 / A1 / | <u>/D7XD6XD5XD4XD3XD2XD1XD0</u> <u>/D7XD6XD5XD4XD3XD2XD1</u>                                                                                               |                          |

|                                            |                                                                                                                                                            |                          |

| SCL                                        | <u>└</u> 9 <u>+</u> /1 <u>/</u> 2 <u>/</u> 3 <u>/</u> 4 <u>/</u> 5 <u>6</u> /7 <u>8</u> /9 <u>+</u> /1 <u>/</u> 2 <u>3</u> 4 <u></u> 5 <u>6</u> /7 <u></u> | /8 <del>\</del> /9\ / PI |

|                                            |                                                                                                                                                            |                          |

| SSPIF (PIR1<3>)                            |                                                                                                                                                            |                          |

| 33FIF (FIR 1<3>)                           | Cleared in software                                                                                                                                        | Bus Master<br>terminates |

|                                            | i<br>I                                                                                                                                                     | transfer                 |

| BF (SSPSTAT<0>)                            | <ul> <li>SSPBUF register is read</li> </ul>                                                                                                                |                          |

|                                            |                                                                                                                                                            | 1                        |

|                                            |                                                                                                                                                            |                          |

| SSPOV (SSPCON<6>)                          |                                                                                                                                                            |                          |

|                                            | Bit SSPOV is set because the SSPBUF register is still full.                                                                                                | . 🔺 📔                    |

|                                            | ACK is not sen                                                                                                                                             |                          |

|                                            | ACK IS NOT SEN                                                                                                                                             | l.—                      |

|                                            |                                                                                                                                                            |                          |

#### 15.3.3 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is 10 bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 15-4.

#### EQUATION 15-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PR2 + 1)]}{\log(2)}$$

bits

Note: If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

| TABLE 15-3: | EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz) |

|-------------|---------------------------------------------------------|

|-------------|---------------------------------------------------------|

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

#### TABLE 15-4: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

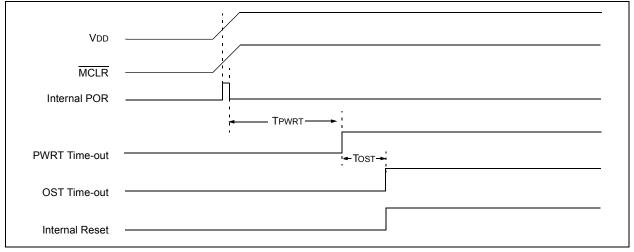

- 3: CLKOUT is available only in INTOSC and RC Oscillator modes.

- 4: For minimum width of INT pulse, refer to AC specifications in Section 19.0 "Electrical Specifications".

- 5: INTF is enabled to be set any time during the Q4-Q1 cycles.

| TABLE 16-6: SUMMARY OF INTERRUPT REGISTERS |  |

|--------------------------------------------|--|

|--------------------------------------------|--|

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on all other Resets |

|--------|-------|-------|-------|-------|-------|--------|--------|--------|----------------------|---------------------------|

| INTCON | GIE   | PEIE  | TOIE  | INTE  | RBIE  | T0IF   | INTF   | RBIF   | x000 0000            | 0000 000x                 |

| PIR1   | EEIF  | ADIF  | RCIF  | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                 |

| PIR2   | OSFIF | C2IF  | C1IF  | LCDIF | -     | LVDIF  | -      | CCP2IF | 0000 -0-0            | 0000 - 0 - 0              |

| PIE1   | EEIE  | ADIE  | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                 |

| PIE2   | OSFIE | C2IE  | C1IE  | LCDIE | _     | LVDIE  | _      | CCP2IE | 0000 -0-0            | 0000 -0-0                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by the Interrupt Module.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

#### FIGURE 16-10: WAKE-UP FROM SLEEP THROUGH INTERRUPT

|                           | Q1 Q2 Q3 Q4 C                                                                                | 01 Q2 Q3  Q4                           | Q1                                |                     |                     | Q1 Q2 Q3 Q4           | Q1   Q2   Q3   Q4   | Q1 Q2 Q3 Q4 |

|---------------------------|----------------------------------------------------------------------------------------------|----------------------------------------|-----------------------------------|---------------------|---------------------|-----------------------|---------------------|-------------|

| OSC1 <sup>(1</sup>        |                                                                                              |                                        |                                   |                     |                     |                       |                     |             |

| CLKOU                     | ⊤[4)                                                                                         |                                        |                                   | Tost <sup>(2)</sup> |                     | <u> </u>              |                     | i           |

| INT pir                   |                                                                                              | 1                                      |                                   | <br>                | 1<br>1              | 1                     | 1                   |             |

| INTF flag<br>(INTCON reg  | .)                                                                                           |                                        |                                   |                     | Interrupt Laten     | <sub>CY</sub> (3)     | ;<br>               |             |

| GIE bit<br>(INTCON reg    | · · · · · · · · · · · · · · · · · · ·                                                        |                                        | Processor in                      |                     |                     |                       |                     |             |

| Instruction Flow          | N                                                                                            |                                        |                                   |                     |                     |                       |                     | 1           |

| PC                        | X PC X                                                                                       | PC + 1                                 | V PC                              | + 2                 | X PC + 2            | ( PC+2 )              | 0004h               | X 0005h     |

| Instruction<br>Fetched    | Inst(PC) = Sleep                                                                             | Inst(PC + 1)                           |                                   | 1<br>1<br>1         | Inst(PC + 2)        | <br> <br>             | Inst(0004h)         | Inst(0005h) |

| Instruction<br>Executed   | Inst(PC - 1)                                                                                 | Sleep                                  |                                   | 1<br>1<br>7         | Inst(PC + 1)        | Dummy Cycle           | Dummy Cycle         | Inst(0004h) |

| Note 1:<br>2:<br>3:<br>4: | XT, HS or LP Oscillat<br>Tost = 1024 Tosc (di<br>GIE = 1 assumed. In<br>CLKOUT is not availa | rawing not to sca<br>this case after w | ale). This dela<br>vake-up, the p | processor           | r jumps to 0004h. I | If GIE = 0, execution | on will continue in | ⊢line.      |

### 16.9 In-Circuit Debugger

When the debug bit in the Configuration Word register is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB<sup>®</sup> ICD 2. When the microcontroller has this feature enabled, some of the resources are not available for general use. See Table 16-9 for more detail.

Note: The user's application must have the circuitry required to support ICD functionality. Once the ICD circuitry is enabled, normal device pin functions on RB6/ICSPCLK/ICDCK/SEG14 and RB7/ICSPDAT/ICDDAT/SEG13 will not be usable. The ICD circuitry uses these pins for communication with the ICD2 external debugger.

For more information, see "*Using MPLAB*<sup>®</sup> *ICD 2*" (DS51265), available on Microchip's web site (www.microchip.com).

#### 16.9.1 ICD PINOUT

The devices in the PIC16F91X/946 family carry the circuitry for the In-Circuit Debugger on-chip and on existing device pins. This eliminates the need for a separate die or package for the ICD device. The pinout for the ICD device is the same as the devices (see **Section 1.0 "Device Overview"** for complete pinout and pin descriptions). Table 16-9 shows the location and function of the ICD related pins on the 28 and 40-pin devices.

| TABLE 16-9: | PIC16F91X/946-ICD PIN DESCRIPTIONS |

|-------------|------------------------------------|

|             |                                    |

|               | Pin Numbers   |                |          |      |         | Description                             |  |

|---------------|---------------|----------------|----------|------|---------|-----------------------------------------|--|

| PDIP          |               | TQFP           | Name     | Туре | Pull-up |                                         |  |

| PIC16F914/917 | PIC16F913/916 | PIC16F946      |          |      |         |                                         |  |

| 40            | 28            | 24             | ICDDATA  | TTL  | —       | In Circuit Debugger Bidirectional data  |  |

| 39            | 27            | 23             | ICDCLK   | ST   | _       | In Circuit Debugger Bidirectional clock |  |

| 1             | 1             | 36             | MCLR/VPP | HV   | _       | Programming voltage                     |  |

| 11,32         | 20            | 10, 19, 38, 51 | Vdd      | Р    | _       | Power                                   |  |

| 12,31         | 8,19          | 9, 20, 41, 56  | Vss      | Р    | _       | Ground                                  |  |

| _             | —             | 26             | AVdd     | Р    | _       | Analog power                            |  |

| _             | _             | 25             | AVss     | Р    | _       | Analog ground                           |  |

**Legend:** TTL = TTL input buffer, ST = Schmitt Trigger input buffer, P = Power, HV = High Voltage

NOTES:

## APPENDIX A: DATA SHEET REVISION HISTORY

### **Revision A**

This is a new data sheet.

### **Revision B**

Updated Peripheral Features. Page 2, Table: Corrected I/O numbers. Figure 8-3: Revised Comparator I/O operating modes. Register 9-1, Table: Corrected max. number of pixels.

### **Revision C**

Correction to Pin Description Table. Correction to IPD base and T1OSC.

### **Revision D**

Revised references 31.25 kHz to 31 kHz. Revised Standby Current to 100 nA. Revised 9.1: internal RC oscillator to internal LF oscillator.

### **Revision E**

Removed "Advance Information" from Section 19.0 Electrical Specifications. Removed 28-Lead Plastic Quad Flat No Lead Package (ML) (QFN-S) package.

#### **Revision F**

Updates throughout document. Removed "Preliminary" from Data Sheet. Added Characterization Data chapter. Update Electrical Specifications chapter. Added PIC16F946 device.

## APPENDIX B: MIGRATING FROM OTHER PIC® DEVICES

This discusses some of the issues in migrating from other  $\text{PIC}^{\textcircled{B}}$  devices to the PIC16F91X/946 family of devices.

### B.1 PIC16F676 to PIC16F91X/946

#### TABLE B-1: FEATURE COMPARISON

| Feature                               | PIC16F676         | PIC16F91X/<br>946 |

|---------------------------------------|-------------------|-------------------|

| Max. Operating Speed                  | 20 MHz            | 20 MHz            |

| Max. Program<br>Memory (Words)        | 1K                | 8K                |

| Max. SRAM (Bytes)                     | 64                | 352               |

| A/D Resolution                        | 10-bit            | 10-bit            |

| Data EEPROM (bytes)                   | 128               | 256               |

| Timers (8/16-bit)                     | 1/1               | 2/1               |

| Oscillator Modes                      | 8                 | 8                 |

| Brown-out Reset                       | Y                 | Y                 |

| Internal Pull-ups                     | RB0/1/2/4/5       | RB<7:0>           |

| Interrupt-on-change                   | RB0/1/2/3<br>/4/5 | RB<7:4>           |

| Comparator                            | 1                 | 2                 |

| USART                                 | N                 | Y                 |

| Extended WDT                          | N                 | Y                 |

| Software Control<br>Option of WDT/BOR | Ν                 | Y                 |

| INTOSC Frequencies                    | 4 MHz             | 32 kHz -<br>8 MHz |

| Clock Switching                       | Ν                 | Y                 |

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com, click on Customer Change Notification and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

- Development Systems Information Line

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://support.microchip.com