Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                              |

| Number of I/O              | 35                                                                      |

| Program Memory Size        | 7KB (4K x 14)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 256 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                |

| Supplier Device Package    | 40-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f914-e-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|     | E 1: | 110       |       | /917 40-PIN |        |      |        |         |           |         |                |

|-----|------|-----------|-------|-------------|--------|------|--------|---------|-----------|---------|----------------|

| I/O | Pin  | A/D       | LCD   | Comparators | Timers | ССР  | AUSART | SSP     | Interrupt | Pull-Up | Basic          |

| RA0 | 2    | AN0       | SEG12 | C1-         | _      | _    | _      | -       | -         | —       | —              |

| RA1 | 3    | AN1       | SEG7  | C2-         | _      | _    | _      | _       | _         | _       | —              |

| RA2 | 4    | AN2/VREF- | COM2  | C2+         |        |      |        | —       | _         | —       |                |

| RA3 | 5    | AN3/VREF+ | SEG15 | C1+         | —      | _    | _      | —       | _         | _       | _              |

| RA4 | 6    |           | SEG4  | C1OUT       | T0CKI  | _    | _      | _       | _         | _       | _              |

| RA5 | 7    | AN4       | SEG5  | C2OUT       |        |      | -      | SS      | _         | —       | _              |

| RA6 | 14   | _         | —     | _           | T10S0  |      |        | —       | —         | —       | OSC2/CLKOUT    |

| RA7 | 13   | —         | —     | —           | T10SI  |      |        | _       | _         | _       | OSC1/CLKIN     |

| RB0 | 33   | _         | SEG0  | _           |        |      |        | —       | INT       | Y       |                |

| RB1 | 34   | —         | SEG1  | —           |        |      |        | _       | _         | Y       |                |

| RB2 | 35   | _         | SEG2  | _           |        |      |        | —       | —         | Y       |                |

| RB3 | 36   | —         | SEG3  | —           |        |      |        | —       | —         | Y       |                |

| RB4 | 37   | _         | COM0  | _           |        |      |        | —       | IOC       | Y       |                |

| RB5 | 38   | —         | COM1  | —           |        |      |        | —       | IOC       | Y       |                |

| RB6 | 39   | _         | SEG14 | _           |        |      |        | —       | IOC       | Y       | ICSPCLK/ICDCK  |

| RB7 | 40   | —         | SEG13 | —           |        |      |        | —       | IOC       | Y       | ICSPDAT/ICDDAT |

| RC0 | 15   | _         | VLCD1 | _           |        |      |        | —       | —         | —       |                |

| RC1 | 16   | —         | VLCD2 | —           |        |      |        | —       | —         | —       |                |

| RC2 | 17   | _         | VLCD3 | _           |        |      |        | —       | —         | —       |                |

| RC3 | 18   | —         | SEG6  | —           |        |      |        | —       | —         | —       |                |

| RC4 | 23   | _         | SEG11 | _           | T1G    |      |        | SDO     | —         | —       |                |

| RC5 | 24   | —         | SEG10 | —           | T1CKI  | CCP1 |        | —       | —         | —       |                |

| RC6 | 25   | _         | SEG9  | _           |        |      | TX/CK  | SCK/SCL | —         | —       |                |

| RC7 | 26   | —         | SEG8  | —           |        |      | RX/DT  | SDI/SDA | —         | —       |                |

| RD0 | 19   | _         | COM3  | _           |        |      |        | —       | —         | —       |                |

| RD1 | 20   | —         | —     | —           |        |      |        | —       | —         | —       |                |

| RD2 | 21   | _         | —     | _           |        | CCP2 |        | —       | —         | —       |                |

| RD3 | 22   | —         | SEG16 | —           |        |      |        | —       | —         | —       |                |

| RD4 | 27   | _         | SEG17 | _           |        |      |        | —       | —         | —       |                |

| RD5 | 28   | —         | SEG18 | —           |        |      |        | —       | —         | —       |                |

| RD6 | 29   | _         | SEG19 | _           |        |      |        | —       | —         | —       |                |

| RD7 | 30   | _         | SEG20 | —           | _      | _    | _      | _       | _         | _       | —              |

| RE0 | 8    | AN5       | SEG21 | —           | _      | _    | _      | _       | _         | _       | _              |

| RE1 | 9    | AN6       | SEG22 | —           | _      | _    | _      | _       | _         | _       | —              |

| RE2 | 10   | AN7       | SEG23 | —           | _      | _    | _      | _       | _         | _       | _              |

| RE3 | 1    | —         |       | —           |        | _    | _      | _       | _         | Y(1)    | MCLR/VPP       |

| _   | 11   |           | _     | —           | _      | _    | _      | —       | _         | _       | Vdd            |

| —   | 32   | —         | _     | —           |        |      |        | _       | _         | —       | Vdd            |

| _   | 12   |           | _     | —           |        |      |        | _       | _         | _       | Vss            |

| _   | 31   | _         | _     |             | _      | _    |        | _       |           | _       | Vss            |

| TABLE 1: | PIC16F914/917 40-PIN SUMMARY |

|----------|------------------------------|

|----------|------------------------------|

**Note 1:** Pull-up enabled only with external MCLR configuration.

#### REGISTER 3-4: PORTB: PORTB REGISTER

| R/W-x                              | R/W-x | R/W-x | R/W-x                                   | R/W-x            | R/W-x    | R/W-x | R/W-x |

|------------------------------------|-------|-------|-----------------------------------------|------------------|----------|-------|-------|

| RB7                                | RB6   | RB5   | RB4                                     | RB3              | RB2      | RB1   | RB0   |

| bit 7                              |       |       |                                         |                  |          |       | bit 0 |

|                                    |       |       |                                         |                  |          |       |       |

| Legend:                            |       |       |                                         |                  |          |       |       |

| R = Readable bit W = Writable bit  |       |       | U = Unimplen                            | nented bit, read | l as '0' |       |       |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cleared x = Bit is unknown |                  |          |       |       |

bit 7-0 **RB<7:0>:** PORTB I/O Pin bits 1 = Port pin is >VIH min. 0 = Port pin is <VIL max.

#### REGISTER 3-5: TRISB: PORTB TRI-STATE REGISTER

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0

TRISB<7:0>: PORTB Tri-State Control bits

1 = PORTB pin configured as an input (tri-stated)

0 = PORTB pin configured as an output

#### REGISTER 3-6: IOCB: PORTB INTERRUPT-ON-CHANGE REGISTER

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-------|-------|-----|-----|-----|-------|

| IOCB7 | IOCB6 | IOCB5 | IOCB4 | —   | —   | —   | —     |

| bit 7 |       |       |       |     |     |     | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-4 **IOCB<7:4>:** Interrupt-on-Change bits 1 = Interrupt-on-change enabled 0 = Interrupt-on-change disabled

bit 3-0 Unimplemented: Read as '0'

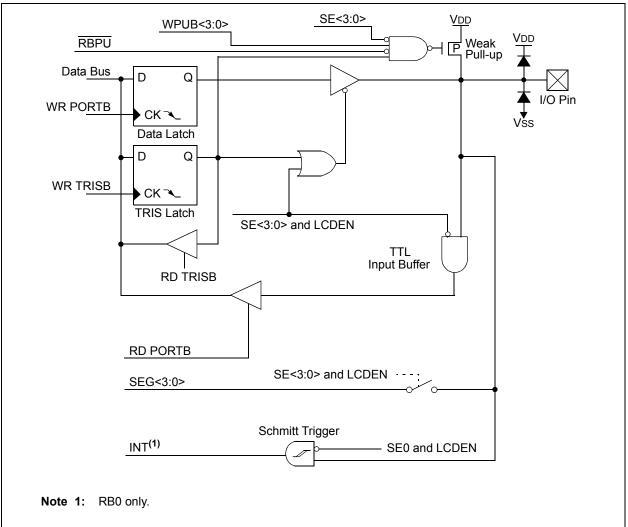

## 3.4.3 PIN DESCRIPTIONS AND DIAGRAMS

Each PORTB pin is multiplexed with other functions. The pins and their combined functions are briefly described here. For specific information about individual functions such as the LCD or interrupts, refer to the appropriate section in this data sheet.

### 3.4.3.1 RB0/INT/SEG0

Figure 3-9 shows the diagram for this pin. The RB0 pin is configurable to function as one of the following:

- a general purpose I/O

- · an external edge triggered interrupt

- an analog output for the LCD

### 3.4.3.2 RB1/SEG1

Figure 3-9 shows the diagram for this pin. The RB1 pin is configurable to function as one of the following:

- a general purpose I/O

- · an analog output for the LCD

#### 3.4.3.3 RB2/SEG2

Figure 3-9 shows the diagram for this pin. The RB2 pin is configurable to function as one of the following:

- a general purpose I/O

- · an analog output for the LCD

#### 3.4.3.4 RB3/SEG3

Figure 3-9 shows the diagram for this pin. The RB3 pin is configurable to function as one of the following:

- a general purpose I/O

- · an analog output for the LCD

## FIGURE 3-9: BLOCK DIAGRAM OF RB<3:0>

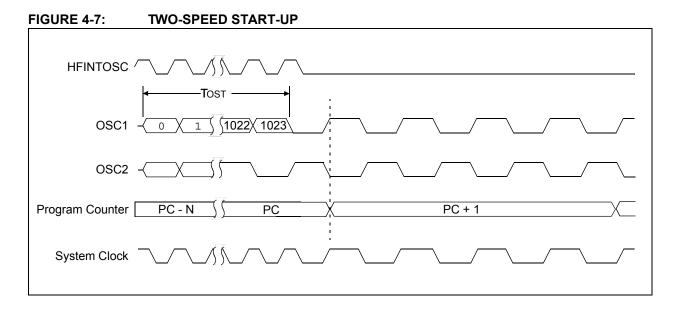

#### 4.7.3 CHECKING TWO-SPEED CLOCK STATUS

Checking the state of the OSTS bit of the OSCCON register will confirm if the microcontroller is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Word register (CONFIG), or the internal oscillator.

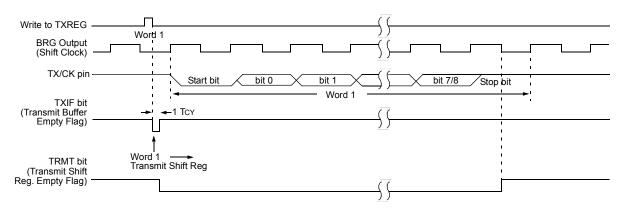

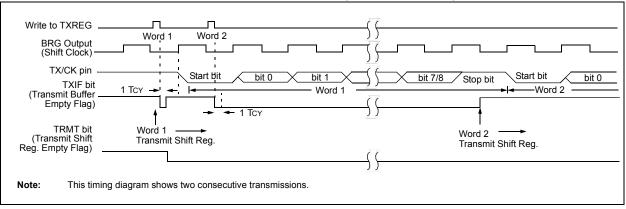

#### 9.1.1.4 TSR Status

The TRMT bit of the TXSTA register indicates the status of the TSR register. This is a read-only bit. The TRMT bit is set when the TSR register is empty and is cleared when a character is transferred to the TSR register from the TXREG. The TRMT bit remains clear until all bits have been shifted out of the TSR register. No interrupt logic is tied to this bit, so the user has to poll this bit to determine the TSR status.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

#### 9.1.1.5 Transmitting 9-Bit Characters

The AUSART supports 9-bit character transmissions. When the TX9 bit of the TXSTA register is set the AUSART will shift 9 bits out for each character transmitted. The TX9D bit of the TXSTA register is the ninth, and Most Significant, data bit. When transmitting 9-bit data, the TX9D data bit must be written before writing the 8 Least Significant bits into the TXREG. All nine bits of data will be transferred to the TSR shift register immediately after the TXREG is written.

A special 9-bit Address mode is available for use with multiple receivers. See Section 9.1.2.7 "Address Detection" for more information on the Address mode.

#### 9.1.1.6 Asynchronous Transmission Set-up:

- Initialize the SPBRG register and the BRGH bit to 1 achieve the desired baud rate (see Section 9.2 "AUSART Baud Rate Generator (BRG)").

- Enable the asynchronous serial port by clearing 2 the SYNC bit and setting the SPEN bit.

- If 9-bit transmission is desired, set the TX9 con-3. trol bit. A set ninth data bit will indicate that the 8 Least Significant data bits are an address when the receiver is set for address detection.

- 4 Enable the transmission by setting the TXEN control bit. This will cause the TXIF interrupt bit to be set.

- If interrupts are desired, set the TXIE interrupt 5. enable bit of the PIE1 register. An interrupt will occur immediately provided that the GIE and PEIE bits of the INTCON register are also set.

- If 9-bit transmission is selected, the ninth bit 6 should be loaded into the TX9D data bit.

- 7 Load 8-bit data into the TXREG register. This will start the transmission.

#### FIGURE 9-4: ASYNCHRONOUS TRANSMISSION (BACK-TO-BACK)

ASYNCHRONOUS TRANSMISSION

FIGURE 9-3:

### 9.3 AUSART Synchronous Mode

Synchronous serial communications are typically used in systems with a single master and one or more slaves. The master device contains the necessary circuitry for baud rate generation and supplies the clock for all devices in the system. Slave devices can take advantage of the master clock by eliminating the internal clock generation circuitry.

There are two signal lines in Synchronous mode: a bidirectional data line and a clock line. Slaves use the external clock supplied by the master to shift the serial data into and out of their respective receive and transmit shift registers. Since the data line is bidirectional, synchronous operation is half-duplex only. Half-duplex refers to the fact that master and slave devices can receive and transmit data but not both simultaneously. The AUSART can operate as either a master or slave device.

Start and Stop bits are not used in synchronous transmissions.

#### 9.3.1 SYNCHRONOUS MASTER MODE

The following bits are used to configure the AUSART for Synchronous Master operation:

- SYNC = 1

- CSRC = 1

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Setting the CSRC bit of the TXSTA register configures the device as a master. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the AUSART.

The LCD SEG8 and SEG9 functions must be disabled by clearing the SE8 and SE9 bits of the LCDSE1 register, if the RX/DT and TX/CK pins are shared with the LCD peripheral.

#### 9.3.1.1 Master Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a master transmits the clock on the TX/CK line. The TX/CK pin output driver is automatically enabled when the AUSART is configured for synchronous transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One clock cycle is generated for each data bit. Only as many clock cycles are generated as there are data bits.

#### 9.3.1.2 Synchronous Master Transmission

Data is transferred out of the device on the RX/DT pin. The RX/DT and TX/CK pin output drivers are automatically enabled when the AUSART is configured for synchronous master transmit operation.

A transmission is initiated by writing a character to the TXREG register. If the TSR still contains all or part of a previous character the new character data is held in the TXREG until the last bit of the previous character has been transmitted. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR. The transmission of the character commences immediately following the transfer of the data to the TSR from the TXREG.

Each data bit changes on the leading edge of the master clock and remains valid until the subsequent leading clock edge.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

- 9.3.1.3 Synchronous Master Transmission Set-up:

- Initialize the SPBRG register and the BRGH bit to achieve the desired baud rate (see Section 9.2 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- 3. Disable Receive mode by clearing bits SREN and CREN.

- 4. Enable Transmit mode by setting the TXEN bit.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in the TX9D bit.

- 8. Start transmission by loading data to the TXREG register.

#### 9.3.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the AUSART for Synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the AUSART.

The LCD SEG8 and SEG9 functions must be disabled by clearing the SE8 and SE9 bits of the LCDSE1 register, if the RX/DT and TX/CK pins are shared with the LCD peripheral.

#### 9.3.2.1 AUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see Section 9.3.1.2 "Synchronous Master Transmission"), except in the case of the Sleep mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in TXREG register.

- 3. The TXIF bit will not be set.

- After the first character has been shifted out of TSR, the TXREG register will transfer the second character to the TSR and the TXIF bit will now be set.

- 5. If the PEIE and TXIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 9.3.2.2 Synchronous Slave Transmission Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the CREN and SREN bits.

- 3. If using interrupts, ensure that the GIE and PEIE bits of the INTCON register are set and set the TXIE bit.

- 4. If 9-bit transmission is desired, set the TX9 bit.

- 5. Enable transmission by setting the TXEN bit.

- 6. Verify address detection is disabled by clearing the ADDEN bit of the RCSTA register.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant 8 bits to the TXREG register.

| Name   | Bit 7                         | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-------------------------------|--------|--------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE                           | PEIE   | T0IE   | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| LCDCON | LCDEN                         | SLPEN  | WERR   | VLCDEN | CS1    | CS0    | LMUX1  | LMUX0  | 0001 0011            | 0001 0011                       |

| LCDSE1 | SE15                          | SE14   | SE13   | SE12   | SE11   | SE10   | SE9    | SE8    | 0000 0000            | 0000 0000                       |

| PIE1   | EEIE                          | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | EEIF                          | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN                          | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | X000 000X            | 0000 000X                       |

| SSPCON | WCOL                          | SSPOV  | SSPEN  | CKP    | SSPM3  | SSPM2  | SSPM1  | SSPM0  | 0000 0000            | 0000 0000                       |

| TRISC  | TRISC7                        | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| TXREG  | AUSART Transmit Data Register |        |        |        |        |        |        |        | 0000 0000            | 0000 0000                       |

| TXSTA  | CSRC                          | TX9    | TXEN   | SYNC   | _      | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

TABLE 9-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Slave Transmission.

NOTES:

### 10.2 LCD Clock Source Selection

The LCD driver module has 3 possible clock sources:

- Fosc/8192

- T1OSC/32

- · LFINTOSC/32

The first clock source is the system clock divided by 8192 (Fosc/8192). This divider ratio is chosen to provide about 1 kHz output when the system clock is 8 MHz. The divider is not programmable. Instead, the LCD prescaler bits LP<3:0> of the LCDPS register are used to set the LCD frame clock rate.

The second clock source is the T1OSC/32. This also gives about 1 kHz when a 32.768 kHz crystal is used with the Timer1 oscillator. To use the Timer1 oscillator as a clock source, the T1OSCEN bit of the T1CON register should be set.

The third clock source is the 31 kHz LFINTOSC/32, which provides approximately 1 kHz output.

The second and third clock sources may be used to continue running the LCD while the processor is in Sleep.

Using bits CS<1:0> of the LCDCON register can select any of these clock sources.

#### 10.2.1 LCD PRESCALER

A 4-bit counter is available as a prescaler for the LCD clock. The prescaler is not directly readable or writable; its value is set by the LP<3:0> bits of the LCDPS register, which determine the prescaler assignment and prescale ratio.

The prescale values are selectable from 1:1 through 1:16.

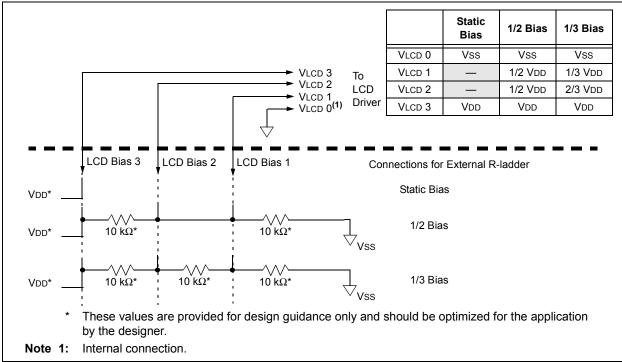

### 10.3 LCD Bias Types

The LCD driver module can be configured into one of three bias types:

- Static Bias (2 voltage levels: Vss and VDD)

- 1/2 Bias (3 voltage levels: Vss, 1/2 VDD and VDD)

- 1/3 Bias (4 voltage levels: Vss, 1/3 VDD, 2/3 VDD and VDD)

This module uses an external resistor ladder to generate the LCD bias voltages.

The external resistor ladder should be connected to the VLCD1 pin (Bias 1), VLCD2 pin (Bias 2), VLCD3 pin (Bias 3) and Vss. The VLCD3 pin should also be connected to VDD.

Figure 10-2 shows the proper way to connect the resistor ladder to the Bias pins..

Note: VLCD pins used to supply LCD bias voltage are enabled on power-up (POR) and must be disabled by the user by clearing the VLCDEN bit of the LCDCON register.

## FIGURE 10-2: LCD BIAS RESISTOR LADDER CONNECTION DIAGRAM

#### 13.1.2 READING THE DATA EEPROM MEMORY

To read a data memory location, the user must write the address to the EEADRL register, clear the EEPGD control bit, and then set control bit RD of the EECON1 register. The data is available in the very next cycle, in the EEDATL register; therefore, it can be read in the next instruction. EEDATL will hold this value until another read or until it is written to by the user (during a write operation).

| EXAMPLE 13-1: | DATA EEPROM READ |

|---------------|------------------|

|               |                  |

| BANKSEL | EEADRL         | ;                |

|---------|----------------|------------------|

| MOVF    | DATA_EE_ADDR,W | ;Data Memory     |

| MOVWF   | EEADRL         | ;Address to read |

| BANKSEL | EECON1         | i                |

| BCF     | EECON1, EEPGD  | ;Point to Data   |

|         |                | ;memory          |

| BSF     | EECON1,RD      | ;EE Read         |

| BANKSEL | EEDATL         | i                |

| MOVF    | EEDATL,W       | ;W = EEPROM Data |

|         |                |                  |

## 13.1.3 WRITING TO THE DATA EEPROM MEMORY

To write an EEPROM data location, the user must first write the address to the EEADRL register and the data to the EEDATL register. Then the user must follow a specific sequence to initiate the write for each byte.

The write will not initiate if the sequence described below is not followed exactly (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte. Interrupts should be disabled during this code segment.

Additionally, the WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM due to errant (unexpected) code execution (i.e., lost programs). The user should keep the WREN bit clear at all times, except when updating EEPROM. The WREN bit is not cleared by hardware.

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. The WR bit will be inhibited from being set unless the WREN bit is set.

At the completion of the write cycle, the WR bit is cleared in hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. EEIF must be cleared by software. The steps to write to EEPROM data memory are:

- 1. If step 10 is not implemented, check the WR bit to see if a write is in progress.

- 2. Write the address to EEADRL. Make sure that the address is not larger than the memory size of the device.

- 3. Write the 8-bit data value to be programmed in the EEDATL register.

- 4. Clear the EEPGD bit to point to EEPROM data memory.

- 5. Set the WREN bit to enable program operations.

- 6. Disable interrupts (if enabled).

- 7. Execute the special five instruction sequence:

- Write 55h to EECON2 in two steps (first to W, then to EECON2)

- Write AAh to EECON2 in two steps (first to W, then to EECON2)

- Set the WR bit

- 8. Enable interrupts (if using interrupts).

- 9. Clear the WREN bit to disable program operations.

- At the completion of the write cycle, the WR bit is cleared and the EEIF interrupt flag bit is set. (EEIF must be cleared by firmware.) If step 1 is not implemented, then firmware should check for EEIF to be set, or WR to clear, to indicate the end of the program cycle.

#### EXAMPLE 13-2: DATA EEPROM WRITE

|   |             | BANKSEL                 | EECON1         | ;                  |

|---|-------------|-------------------------|----------------|--------------------|

|   |             | BTFSC                   | EECON1,WR      | ;Wait for write    |

|   |             | GOTO                    | \$-1           | ;to complete       |

|   |             | BANKSEL                 | EEADRL         | ;                  |

|   |             | MOVF                    | DATA_EE_ADDR,W | ;Data Memory       |

|   |             | MOVWF                   | EEADRL         | ;Address to write  |

|   |             | MOVF                    | DATA_EE_DATA,W | ;Data Memory Value |

|   |             | MOVWF                   | EEDATL         | ;to write          |

|   |             | BANKSEL                 | EECON1         | ;                  |

|   |             | BCF                     | EECON1, EEPGD  | ;Point to DATA     |

|   |             |                         |                | ;memory            |

|   |             | BSF                     | EECON1,WREN    | ;Enable writes     |

|   |             |                         |                |                    |

|   |             | BCF                     | INTCON,GIE     | ;Disable INTs.     |

| ſ |             | MOVLW                   | 55h            | ;                  |

|   | g g         | MOVWF<br>MOVLW<br>MOVWF | EECON2         | ;Write 55h         |

|   | uire<br>Jen | MOVLW                   | AAh            | ;                  |

|   | equ         | MOVWF                   | EECON2         | ;Write AAh         |

|   | шv          | BSF                     | EECON1,WR      | ;Set WR bit to     |

| l |             |                         |                | ;begin write       |

|   |             | BSF                     | INTCON,GIE     | ;Enable INTs.      |

|   |             | BCF                     | EECON1,WREN    | ;Disable writes    |

|   |             |                         |                |                    |

NOTES:

#### 16.1 Configuration Bits

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1') to select various device configurations as shown in Register 16-1. These bits are mapped in program memory location 2007h.

Note: Address 2007h is beyond the user program memory space. It belongs to the special configuration memory space (2000h-3FFFh), which can be accessed only during programming. See "PIC16F91X/946 Memory Programming Specification" (DS41244) for more information.

#### REGISTER 16-1: CONFIG1: CONFIGURATION WORD REGISTER 1

| _      | _ | _ | DEBUG | FCMEN | IESO | BOREN1 | BOREN0 |

|--------|---|---|-------|-------|------|--------|--------|

| bit 15 |   |   |       |       |      |        | bit 8  |

| CPD   | CP | MCLRE | PWRTE | WDTE | FOSC2 | FOSC1 | FOSC0 |

|-------|----|-------|-------|------|-------|-------|-------|

| bit 7 |    |       |       |      |       |       | bit 0 |

| bit 15-13           | Unimplemented: Read as '1'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 12              | <b>DEBUG:</b> In-Circuit Debugger Mode bit<br>1 = In-Circuit Debugger disabled, RB6/ICSPCLK and RB7/ICSPDAT are general purpose I/O pins<br>0 = In-Circuit Debugger enabled, RB6/ICSPCLK and RB7/ICSPDAT are dedicated to the debugger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| bit 11              | <b>FCMEN:</b> Fail-Safe Clock Monitor Enabled bit<br>1 = Fail-Safe Clock Monitor is enabled<br>0 = Fail-Safe Clock Monitor is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| bit 10              | IESO: Internal External Switchover bit<br>1 = Internal/External Switchover mode is enabled<br>0 = Internal/External Switchover mode is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| bit 9-8             | BOREN<1:0>: Brown-out Reset Selection bits <sup>(1)</sup><br>11 = BOR enabled<br>10 = BOR enabled during operation and disabled in Sleep<br>01 = BOR controlled by SBOREN bit of the PCON register<br>00 = BOR disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| bit 7               | <b>CPD:</b> Data Code Protection bit <sup>(2)</sup><br>1 = Data memory code protection is disabled<br>0 = Data memory code protection is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| bit 6               | <b>CP:</b> Code Protection bit <sup>(3)</sup><br>1 = Program memory code protection is disabled<br>0 = Program memory code protection is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| bit 5               | MCLRE: <u>RE3/MCLR</u> pin functi <u>on sel</u> ect bit <sup>(4)</sup><br>1 = RE3/ <u>MCLR</u> pin function is MCLR<br>0 = RE3/MCLR pin function is digital input, <u>MCLR</u> internally tied to VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| bit 4               | <b>PWRTE:</b> Power-up Timer Enable bit<br>1 = PWRT disabled<br>0 = PWRT enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| bit 3               | WDTE: Watchdog Timer Enable bit<br>1 = WDT enabled<br>0 = WDT disabled and can be enabled by SWDTEN bit of the WDTCON register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| bit 2-0             | FOSC<2:0>: Oscillator Selection bits<br>111 = RC oscillator: CLKOUT function on RA6/OSC2/CLKOUT/T1OSO pin, RC on RA7/OSC1/CLKIN/T1OSI<br>100 = RCIO oscillator: I/O function on RA6/OSC2/CLKOUT/T1OSO pin, RC on RA7/OSC1/CLKIN/T1OSI<br>101 = INTOSC oscillator: CLKOUT function on RA6/OSC2/CLKOUT/T1OSO pin, I/O function on RA7/OSC1/CLKIN/T1OSI<br>100 = INTOSCIO oscillator: I/O function on RA6/OSC2/CLKOUT/T1OSO pin, I/O function on RA7/OSC1/CLKIN/T1OSI<br>101 = EC: I/O function on RA6/OSC2/CLKOUT/T1OSO pin, CLKIN on RA7/OSC1/CLKIN/T1OSI<br>101 = HS oscillator: High-speed crystal/resonator on RA6/OSC2/CLKOUT/T1OSO and RA7/OSC1/CLKIN/T1OSI<br>101 = XT oscillator: Crystal/resonator on RA6/OSC2/CLKOUT/T1OSO and RA7/OSC1/CLKIN/T1OSI<br>100 = LP oscillator: Low-power crystal on RA6/OSC2/CLKOUT/T1OSO and RA7/OSC1/CLKIN/T1OSI |

| Note 1:<br>2:<br>3: | The entire data EEPROM will be erased when the code protection is turned off.<br>The en <u>tire pr</u> ogram memory will be erased when the code protection is turned off.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

4: When MCLR is asserted in INTOSC or RC mode, the internal clock oscillator is disabled.

#### 16.9 In-Circuit Debugger

When the debug bit in the Configuration Word register is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB<sup>®</sup> ICD 2. When the microcontroller has this feature enabled, some of the resources are not available for general use. See Table 16-9 for more detail.

Note: The user's application must have the circuitry required to support ICD functionality. Once the ICD circuitry is enabled, normal device pin functions on RB6/ICSPCLK/ICDCK/SEG14 and RB7/ICSPDAT/ICDDAT/SEG13 will not be usable. The ICD circuitry uses these pins for communication with the ICD2 external debugger.

For more information, see "*Using MPLAB*<sup>®</sup> *ICD 2*" (DS51265), available on Microchip's web site (www.microchip.com).

#### 16.9.1 ICD PINOUT

The devices in the PIC16F91X/946 family carry the circuitry for the In-Circuit Debugger on-chip and on existing device pins. This eliminates the need for a separate die or package for the ICD device. The pinout for the ICD device is the same as the devices (see **Section 1.0 "Device Overview"** for complete pinout and pin descriptions). Table 16-9 shows the location and function of the ICD related pins on the 28 and 40-pin devices.

| TABLE 16-9: | PIC16F91X/946-ICD PIN DESCRIPTIONS |

|-------------|------------------------------------|

|             |                                    |

| Pin Numbers   |               |                |          |      |         |                                         |  |

|---------------|---------------|----------------|----------|------|---------|-----------------------------------------|--|

| PDIP          |               | TQFP           | Name     | Туре | Pull-up | Description                             |  |

| PIC16F914/917 | PIC16F913/916 | PIC16F946      |          |      |         |                                         |  |

| 40            | 28            | 24             | ICDDATA  | TTL  | —       | In Circuit Debugger Bidirectional data  |  |

| 39            | 27            | 23             | ICDCLK   | ST   | _       | In Circuit Debugger Bidirectional clock |  |

| 1             | 1             | 36             | MCLR/VPP | HV   | _       | Programming voltage                     |  |

| 11,32         | 20            | 10, 19, 38, 51 | Vdd      | Р    | _       | Power                                   |  |

| 12,31         | 8,19          | 9, 20, 41, 56  | Vss      | Р    | _       | Ground                                  |  |

| _             | —             | 26             | AVdd     | Р    | _       | Analog power                            |  |

| _             | _             | 25             | AVss     | Р    | _       | Analog ground                           |  |

**Legend:** TTL = TTL input buffer, ST = Schmitt Trigger input buffer, P = Power, HV = High Voltage

| RLF              | Rotate Left f through Carry                                                                                                                                                                                          |             |       |      |      |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|------|------|--|--|

| Syntax:          | [ label ]                                                                                                                                                                                                            | RLF         | f,d   |      |      |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                   |             |       |      |      |  |  |

| Operation:       | See des                                                                                                                                                                                                              | scription I | belov | v    |      |  |  |

| Status Affected: | С                                                                                                                                                                                                                    |             |       |      |      |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry flag. If 'd' is '0', the<br>result is placed in the W register.<br>If 'd' is '1', the result is stored<br>back in register 'f'. |             |       |      |      |  |  |

| Words:           | 1                                                                                                                                                                                                                    |             |       |      |      |  |  |

| Cycles:          | 1                                                                                                                                                                                                                    |             |       |      |      |  |  |

| Example:         | RLF                                                                                                                                                                                                                  | REG1,       | 0     |      |      |  |  |

|                  | Before Instruction                                                                                                                                                                                                   |             |       |      |      |  |  |

|                  |                                                                                                                                                                                                                      | REG1        | =     | 1110 | 0110 |  |  |

|                  | C = 0                                                                                                                                                                                                                |             |       |      |      |  |  |

|                  | After In                                                                                                                                                                                                             | struction   |       |      |      |  |  |

|                  |                                                                                                                                                                                                                      | REG1        | =     |      | 0110 |  |  |

|                  |                                                                                                                                                                                                                      | W           | =     | 1100 | 1100 |  |  |

|                  |                                                                                                                                                                                                                      | C           | =     | 1    |      |  |  |

| SLEEP            | Enter Sleep mode                                                                                                                                                                                                       |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                          |

| Operands:        | None                                                                                                                                                                                                                   |

| Operation:       | $\begin{array}{l} \text{00h} \rightarrow \text{WDT,} \\ 0 \rightarrow \text{WDT prescaler,} \\ 1 \rightarrow \overline{\text{TO}}, \\ 0 \rightarrow \overline{\text{PD}} \end{array}$                                  |

| Status Affected: | TO, PD                                                                                                                                                                                                                 |

| Description:     | The power-down Status bit, $\overline{PD}$ is cleared. Time-out Status bit, $\overline{TO}$ is set. Watchdog Timer and its prescaler are cleared.<br>The processor is put into Sleep mode with the oscillator stopped. |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                                        |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                                            |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                  |

| Operation:       | See description below                                                                                                                                                                                                               |

| Status Affected: | С                                                                                                                                                                                                                                   |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry flag. If 'd' is ' $^{0}$ ', the<br>result is placed in the W register.<br>If 'd' is ' $^{1}$ ', the result is placed<br>back in register 'f'. |

|                  | C Register f                                                                                                                                                                                                                        |

| SUBLW            | Subtract W from literal                                                                                                      |                 |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                     |                 |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                            |                 |  |  |  |  |  |

| Operation:       | $k -(W) \to (W)$                                                                                                             | N)              |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                     |                 |  |  |  |  |  |

| Description:     | The W register is subtracted (2's complement method) from the eight-bit literal 'k'. The result is placed in the W register. |                 |  |  |  |  |  |

|                  | C = 0 W > k                                                                                                                  |                 |  |  |  |  |  |

|                  | $C = 1$ $W \le k$                                                                                                            |                 |  |  |  |  |  |

|                  | DC = 0                                                                                                                       | W<3:0> > k<3:0> |  |  |  |  |  |

DC = 0 DC = 1

W<3:0> ≤ k<3:0>

#### 19.2 DC Characteristics: PIC16F913/914/916/917/946-I (Industrial) PIC16F913/914/916/917/946-E (Extended)

| DC CH4                       | ARACTERISTICS                          | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |       |      |       |     |                           |

|------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|-----|---------------------------|

| Param Device Characteristics |                                        | Min.                                                                                                                                                                                    | Тур†  | Max. | Units |     | Conditions                |

| No.                          |                                        |                                                                                                                                                                                         | - 761 | max. | •     | VDD | Note                      |

| D010                         | Supply Current (IDD) <sup>(1, 2)</sup> |                                                                                                                                                                                         | 13    | 19   | μA    | 2.0 | Fosc = 32 kHz             |

|                              |                                        |                                                                                                                                                                                         | 22    | 30   | μΑ    | 3.0 | LP Oscillator mode        |

|                              |                                        |                                                                                                                                                                                         | 33    | 60   | μA    | 5.0 |                           |

| D011*                        |                                        | —                                                                                                                                                                                       | 180   | 250  | μA    | 2.0 | Fosc = 1 MHz              |

|                              |                                        |                                                                                                                                                                                         | 290   | 400  | μΑ    | 3.0 | XT Oscillator mode        |

|                              |                                        | _                                                                                                                                                                                       | 490   | 650  | μΑ    | 5.0 |                           |

| D012                         |                                        | _                                                                                                                                                                                       | 280   | 380  | μA    | 2.0 | Fosc = 4 MHz              |

|                              |                                        |                                                                                                                                                                                         | 480   | 670  | μΑ    | 3.0 | XT Oscillator mode        |

|                              |                                        | —                                                                                                                                                                                       | 0.9   | 1.4  | mA    | 5.0 |                           |

| D013*                        |                                        | —                                                                                                                                                                                       | 170   | 295  | μA    | 2.0 | Fosc = 1 MHz              |

|                              |                                        |                                                                                                                                                                                         | 280   | 480  | μΑ    | 3.0 | EC Oscillator mode        |

|                              |                                        |                                                                                                                                                                                         | 470   | 690  | μA    | 5.0 |                           |

| D014                         |                                        | —                                                                                                                                                                                       | 290   | 450  | μA    | 2.0 | Fosc = 4 MHz              |

|                              |                                        | _                                                                                                                                                                                       | 490   | 720  | μA    | 3.0 | EC Oscillator mode        |

|                              |                                        | _                                                                                                                                                                                       | 0.85  | 1.3  | mA    | 5.0 |                           |

| D015                         |                                        | _                                                                                                                                                                                       | 8     | 20   | μA    | 2.0 | Fosc = 31 kHz             |

|                              |                                        | _                                                                                                                                                                                       | 16    | 40   | μA    | 3.0 | LFINTOSC mode             |

|                              |                                        | _                                                                                                                                                                                       | 31    | 65   | μA    | 5.0 |                           |

| D016*                        |                                        | _                                                                                                                                                                                       | 416   | 520  | μA    | 2.0 | Fosc = 4 MHz              |

|                              |                                        |                                                                                                                                                                                         | 640   | 840  | μA    | 3.0 | HFINTOSC mode             |

|                              |                                        | _                                                                                                                                                                                       | 1.13  | 1.6  | mA    | 5.0 |                           |

| D017                         |                                        |                                                                                                                                                                                         | 0.65  | 0.9  | mA    | 2.0 | Fosc = 8 MHz              |

|                              |                                        |                                                                                                                                                                                         | 1.01  | 1.3  | mA    | 3.0 | HFINTOSC mode             |

|                              |                                        | —                                                                                                                                                                                       | 1.86  | 2.3  | mA    | 5.0 |                           |

| D018                         |                                        | —                                                                                                                                                                                       | 340   | 580  | μA    | 2.0 | Fosc = 4 MHz              |

|                              |                                        |                                                                                                                                                                                         | 550   | 900  | μA    | 3.0 | EXTRC mode <sup>(3)</sup> |

|                              |                                        |                                                                                                                                                                                         | 0.92  | 1.4  | mA    | 5.0 | ]                         |

| D019                         |                                        | —                                                                                                                                                                                       | 3.8   | 4.7  | mA    | 4.5 | Fosc = 20 MHz             |

|                              |                                        | _                                                                                                                                                                                       | 4.0   | 4.8  | mA    | 5.0 | HS Oscillator mode        |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

**2:** The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in kΩ.

### TABLE 19-2: OSCILLATOR PARAMETERS

| Standard Operating Conditions (unless otherwise stated)<br>Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |             |                                                            |                    |      |      |      |       |                                                                                                       |  |  |

|--------------------------------------------------------------------------------------------------------------------------|-------------|------------------------------------------------------------|--------------------|------|------|------|-------|-------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.                                                                                                             | Sym.        | Characteristic                                             | Freq.<br>Tolerance | Min. | Тур† | Max. | Units | Conditions                                                                                            |  |  |

| OS06                                                                                                                     | Twarm       | Internal Oscillator Switch when running <sup>(3)</sup>     | _                  |      | —    | 2    | Tosc  | Slowest clock                                                                                         |  |  |

| OS07                                                                                                                     | Tsc         | Fail-Safe Sample Clock<br>Period <sup>(1)</sup>            | —                  | -    | 21   | -    | ms    | LFINTOSC/64                                                                                           |  |  |

| OS08                                                                                                                     | HFosc       | Internal Calibrated<br>HFINTOSC Frequency <sup>(2)</sup>   | ±1%                | 7.92 | 8.0  | 8.08 | MHz   | VDD = 3.5V, 25°C                                                                                      |  |  |

|                                                                                                                          |             |                                                            | ±2%                | 7.84 | 8.0  | 8.16 | MHz   | $2.5V \le VDD \le 5.5V$ ,<br>$0^{\circ}C \le TA \le +85^{\circ}C$                                     |  |  |

|                                                                                                                          |             |                                                            | ±5%                | 7.60 | 8.0  | 8.40 | MHz   | $2.0V \le VDD \le 5.5V$ ,<br>-40°C $\le$ TA $\le$ +85°C (Ind.),<br>-40°C $\le$ TA $\le$ +125°C (Ext.) |  |  |

| OS09*                                                                                                                    | LFosc       | Internal Uncalibrated<br>LFINTOSC Frequency                | —                  | 15   | 31   | 45   | kHz   |                                                                                                       |  |  |

| OS10*                                                                                                                    | Tiosc<br>st | HFINTOSC Oscillator<br>Wake-up from Sleep<br>Start-up Time | _                  | 5.5  | 12   | 24   | μs    | VDD = 2.0V, -40°C to +85°C                                                                            |  |  |

|                                                                                                                          |             |                                                            | —                  | 3.5  | 7    | 14   | μs    | VDD = 3.0V, -40°C to +85°C                                                                            |  |  |

|                                                                                                                          |             |                                                            | —                  | 3    | 6    | 11   | μs    | VDD = 5.0V, -40°C to +85°C                                                                            |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to the OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

- 2: To ensure these oscillator frequency tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1  $\mu$ F and 0.01  $\mu$ F values in parallel are recommended.

- 3: By design.

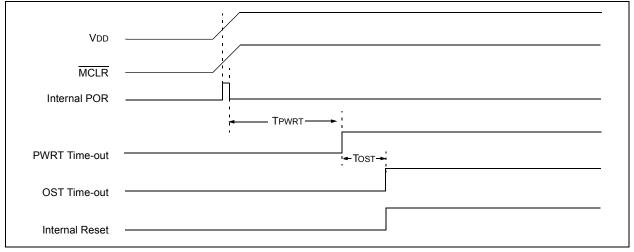

#### **FIGURE 19-8:** TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

#### **TABLE 19-5**: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Symbol    |                                                                                        | Characterist                   | ic             | Min.                                      | Тур†   | Max.   | Units | Conditions                         |

|--------------|-----------|----------------------------------------------------------------------------------------|--------------------------------|----------------|-------------------------------------------|--------|--------|-------|------------------------------------|

| 40*          | T⊤0H      | T0CKI High Pulse Width No Prescaler With Prescaler                                     |                                | No Prescaler   | 0.5 Tcy + 20                              | —      | _      | ns    |                                    |

|              |           |                                                                                        |                                | 10             | —                                         | _      | ns     |       |                                    |

| 41*          | T⊤0L      | T0CKI Low Pulse Width No Prescaler<br>With Prescale                                    |                                | No Prescaler   | 0.5 TCY + 20                              | —      | _      | ns    |                                    |

|              |           |                                                                                        |                                | With Prescaler | 10                                        | —      | _      | ns    |                                    |

| 42*          | Тт0Р      | T0CKI Period                                                                           |                                |                | Greater of:<br>20 or <u>Tcy + 40</u><br>N | —      | _      | ns    | N = prescale value<br>(2, 4,, 256) |

| 45*          | T⊤1H      | T1CKI High<br>Time                                                                     | Synchronous, No Prescaler      |                | 0.5 TCY + 20                              | —      | _      | ns    |                                    |

|              |           |                                                                                        | Synchronous,<br>with Prescaler |                | 15                                        | —      | _      | ns    |                                    |

|              |           |                                                                                        | Asynchronous                   |                | 30                                        | —      | _      | ns    |                                    |

| 46*          | T⊤1L      | T1CKI Low<br>Time                                                                      | Synchronous, No Prescaler      |                | 0.5 TCY + 20                              | —      | _      | ns    |                                    |

|              |           |                                                                                        | Synchronous,<br>with Prescaler |                | 15                                        | —      |        | ns    |                                    |

|              |           |                                                                                        | Asynchronous                   |                | 30                                        | —      | _      | ns    |                                    |

| 47*          | T⊤1P      | T1CKI Input<br>Period                                                                  | Synchronous                    |                | Greater of:<br>30 or <u>Tcy + 40</u><br>N | —      | _      | ns    | N = prescale value<br>(1, 2, 4, 8) |

|              |           |                                                                                        | Asynchronous                   |                | 60                                        | —      |        | ns    |                                    |