#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I²C, SPI, UART/USART                                                    |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                              |

| Number of I/O              | 35                                                                      |

| Program Memory Size        | 7KB (4K x 14)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 256 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                |

| Supplier Device Package    | 40-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f914-i-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2.4 PIE1 Register

The PIE1 register contains the interrupt enable bits, as shown in Register 2-4.

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

#### REGISTER 2-4: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 R/W-0 |        |

|-------|-----------|-------|-------|-------|--------|-------------|--------|

| EEIE  | ADIE RCIE |       | TXIE  | SSPIE | CCP1IE | TMR2IE      | TMR1IE |

| bit 7 |           |       |       |       |        |             | bit 0  |

| Legend:              |                                                |                                                                                           |                         |                    |  |  |  |  |  |

|----------------------|------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------|--------------------|--|--|--|--|--|

| R = Readable bit W = |                                                | W = Writable bit                                                                          | U = Unimplemented bit,  | read as '0'        |  |  |  |  |  |

| -n = Value a         | at POR                                         | '1' = Bit is set                                                                          | '0' = Bit is cleared    | x = Bit is unknown |  |  |  |  |  |

| bit 7                | EEIE. CO                                       | Write Complete Interrupt F                                                                | nahla hit               |                    |  |  |  |  |  |

|                      |                                                | E Write Complete Interrupt En<br>les the EE write complete in                             |                         |                    |  |  |  |  |  |

|                      |                                                | bles the EE write complete in                                                             | •                       |                    |  |  |  |  |  |

| bit 6                |                                                | D Converter (ADC) Interrupt                                                               |                         |                    |  |  |  |  |  |

|                      | 1 = Enab                                       | 1 = Enables the ADC interrupt                                                             |                         |                    |  |  |  |  |  |

|                      | 0 = Disat                                      | oles the ADC interrupt                                                                    |                         |                    |  |  |  |  |  |

| bit 5                | RCIE: US                                       | SART Receive Interrupt Enal                                                               | ble bit                 |                    |  |  |  |  |  |

|                      |                                                | 1 = Enables the USART receive interrupt                                                   |                         |                    |  |  |  |  |  |

|                      |                                                | bles the USART receive inter                                                              | -                       |                    |  |  |  |  |  |

| bit 4                |                                                | SART Transmit Interrupt Ena                                                               |                         |                    |  |  |  |  |  |

|                      |                                                | les the USART transmit inte                                                               |                         |                    |  |  |  |  |  |

| h:1 0                |                                                | bles the USART transmit inte                                                              |                         |                    |  |  |  |  |  |

| bit 3                |                                                | Synchronous Serial Port (SSI                                                              | P) Interrupt Enable bit |                    |  |  |  |  |  |

|                      |                                                | <ul> <li>1 = Enables the SSP interrupt</li> <li>0 = Disables the SSP interrupt</li> </ul> |                         |                    |  |  |  |  |  |

| bit 2                |                                                | CCP1 Interrupt Enable bit                                                                 |                         |                    |  |  |  |  |  |

|                      |                                                | les the CCP1 interrupt                                                                    |                         |                    |  |  |  |  |  |

|                      |                                                | oles the CCP1 interrupt                                                                   |                         |                    |  |  |  |  |  |

| bit 1                | TMR2IE: TMR2 to PR2 Match Interrupt Enable bit |                                                                                           |                         |                    |  |  |  |  |  |

|                      | 1 = Enab                                       | les the Timer2 to PR2 match                                                               | n interrupt             |                    |  |  |  |  |  |

|                      | 0 = Disat                                      | oles the Timer2 to PR2 matc                                                               | h interrupt             |                    |  |  |  |  |  |

| bit 0                |                                                | Timer1 Overflow Interrupt E                                                               |                         |                    |  |  |  |  |  |

|                      |                                                | les the Timer1 overflow inter                                                             | •                       |                    |  |  |  |  |  |

|                      | 0 = Disat                                      | bles the Timer1 overflow inte                                                             | rrupt                   |                    |  |  |  |  |  |

# 3.0 I/O PORTS

The PIC16F913/914/916/917/946 family of devices includes several 8-bit PORT registers along with their corresponding TRIS registers and one four bit port:

- PORTA and TRISA

- PORTB and TRISB

- PORTC and TRISC

- PORTD and TRISD<sup>(1)</sup>

- PORTE and TRISE

- PORTF and TRISF<sup>(2)</sup>

- PORTG and TRISG<sup>(2)</sup>

Note 1: PIC16F914/917 and PIC16F946 only.

2: PIC16F946 only

PORTA, PORTB, PORTC and RE3/MCLR/VPP are implemented on all devices. PORTD and RE<2:0> (PORTE) are implemented only on the PIC16F914/917 and PIC16F946. RE<7:4> (PORTE), PORTF and PORTG are implemented only on the PIC16F946.

### 3.1 ANSEL Register

The ANSEL register (Register 3-1) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSEL bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSEL bits has no affect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

#### REGISTER 3-1: ANSEL: ANALOG SELECT REGISTER

| R/W-1               | R/W-1               | R/W-1                                   | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|---------------------|---------------------|-----------------------------------------|-------|-------|-------|-------|-------|

| ANS7 <sup>(2)</sup> | ANS6 <sup>(2)</sup> | ANS6 <sup>(2)</sup> ANS5 <sup>(2)</sup> |       | ANS3  | ANS2  | ANS1  | ANS0  |

| bit 7               |                     |                                         |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-0 ANS<7:0>: Analog Select bits

Analog select between analog or digital function on pins AN<7:0>, respectively.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>.

- 0 = Digital I/O. Pin is assigned to port or special function.

- **Note 1:** Setting a pin to an analog input automatically disables the digital input circuitry, weak pull-ups, and interrupt-on-change if available. The corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

- 2: PIC16F914/PIC16F917/PIC16F946 only.

#### 3.2.1 PIN DESCRIPTIONS AND DIAGRAMS

Each PORTA pin is multiplexed with other functions. The pins and their combined functions are briefly described here. For specific information about individual functions, refer to the appropriate section in this data sheet.

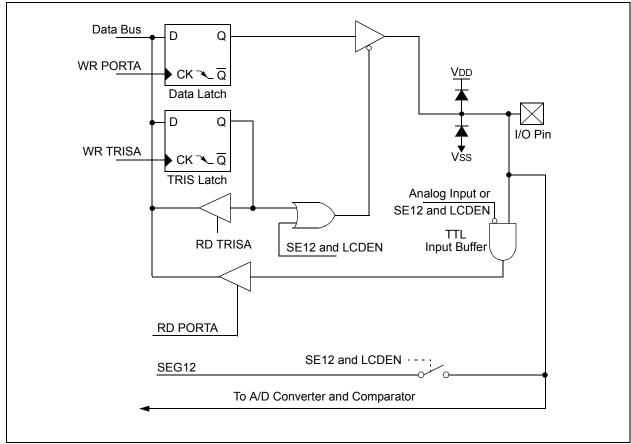

#### 3.2.1.1 RA0/AN0/C1-/SEG12

Figure 3-1 shows the diagram for this pin. The RA0 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

- an analog input for Comparator C1

- an analog output for the LCD

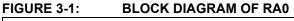

#### 3.2.1.3 RA2/AN2/C2+/VREF-/COM2

Figure 3-3 shows the diagram for this pin. The RA2 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

- an analog input for Comparator C2

- a voltage reference input for the ADC

- an analog output for the LCD

## 4.2 Oscillator Control

The Oscillator Control (OSCCON) register (Figure 4-1) controls the system clock and frequency selection options. The OSCCON register contains the following bits:

- Frequency selection bits (IRCF)

- Frequency Status bits (HTS, LTS)

- System clock control bits (OSTS, SCS)

#### REGISTER 4-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0   | R/W-1 R/W-1 |       | R/W-0 R-1 |                     | R-0 | R-0 | R/W-0 |

|-------|-------------|-------|-----------|---------------------|-----|-----|-------|

| —     | IRCF2       | IRCF1 | IRCF0     | OSTS <sup>(1)</sup> | HTS | LTS | SCS   |

| bit 7 |             |       |           |                     |     |     | bit 0 |

| Legend:           |                               |                                          |                    |  |  |  |

|-------------------|-------------------------------|------------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit              | e bit U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | Value at POR '1' = Bit is set |                                          | x = Bit is unknown |  |  |  |

| bit 7   | Unimplemented: Read as '0'                                                                                                                                                                       |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-4 | IRCF<2:0>: Internal Oscillator Frequency Select bits                                                                                                                                             |

|         | 111 = 8 MHz                                                                                                                                                                                      |

|         | 110 = 4 MHz (default)                                                                                                                                                                            |

|         | 101 = 2 MHz                                                                                                                                                                                      |

|         | 100 = 1 MHz                                                                                                                                                                                      |

|         | 011 = 500 kHz                                                                                                                                                                                    |

|         | 010 = 250  kHz                                                                                                                                                                                   |

|         | 001 = 125 kHz                                                                                                                                                                                    |

|         | 000 = 31  kHz (LFINTOSC)                                                                                                                                                                         |

| bit 3   | OSTS: Oscillator Start-up Time-out Status bit <sup>(1)</sup>                                                                                                                                     |

|         | <ul> <li>1 = Device is running from the clock defined by FOSC&lt;2:0&gt; of the Configuration Word</li> <li>0 = Device is running from the internal oscillator (HFINTOSC or LFINTOSC)</li> </ul> |

| bit 2   | HTS: HFINTOSC Status bit (High Frequency – 8 MHz to 125 kHz)                                                                                                                                     |

|         | 1 = HFINTOSC is stable                                                                                                                                                                           |

|         | 0 = HFINTOSC is not stable                                                                                                                                                                       |

| bit 1   | LTS: LFINTOSC Stable bit (Low Frequency – 31 kHz)                                                                                                                                                |

|         | 1 = LFINTOSC is stable                                                                                                                                                                           |

|         | 0 = LFINTOSC is not stable                                                                                                                                                                       |

| bit 0   | SCS: System Clock Select bit                                                                                                                                                                     |

|         | 1 = Internal oscillator is used for system clock                                                                                                                                                 |

|         | <ul> <li>Clock source defined by FOSC&lt;2:0&gt; of the Configuration Word</li> </ul>                                                                                                            |

| Note 1  | Dit reports to 'o' with Two Speed Start up and LD VT or US selected as the Oscillator mode or Eail Sc                                                                                            |

**Note 1:** Bit resets to '0' with Two-Speed Start-up and LP, XT or HS selected as the Oscillator mode or Fail-Safe mode is enabled.

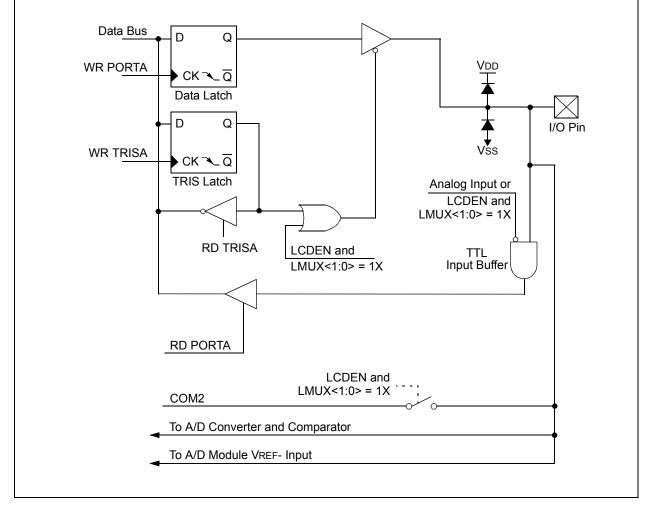

## 4.4.3 LP, XT, HS MODES

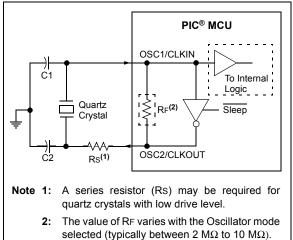

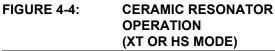

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 4-3). The mode selects a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 4-3 and Figure 4-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- **2:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

- 2: The value of RF varies with the Oscillator mode selected (typically between 2 M $\Omega$  to 10 M $\Omega$ ).

- **3:** An additional parallel feedback resistor (RP) may be required for proper ceramic resonator operation.

# 4.6 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS) bit of the OSCCON register.

### 4.6.1 SYSTEM CLOCK SELECT (SCS) BIT

The System Clock Select (SCS) bit of the OSCCON register selects the system clock source that is used for the CPU and peripherals.

- When the SCS bit of the OSCCON register = 0, the system clock source is determined by configuration of the FOSC<2:0> bits in the Configuration Word register (CONFIG).

- When the SCS bit of the OSCCON register = 1, the system clock source is chosen by the internal oscillator frequency selected by the IRCF<2:0> bits of the OSCCON register. After a Reset, the SCS bit of the OSCCON register is always cleared.

- Note: Any automatic clock switch, which may occur from Two-Speed Start-up or Fail-Safe Clock Monitor, does not update the SCS bit of the OSCCON register. The user can monitor the OSTS bit of the OSCCON register to determine the current system clock source.

# 4.6.2 OSCILLATOR START-UP TIME-OUT STATUS (OSTS) BIT

The Oscillator Start-up Time-out Status (OSTS) bit of the OSCCON register indicates whether the system clock is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Word register (CONFIG), or from the internal clock source. In particular, OSTS indicates that the Oscillator Start-up Timer (OST) has timed out for LP, XT or HS modes.

### 4.7 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device.

This mode allows the application to wake-up from Sleep, perform a few instructions using the INTOSC as the clock source and go back to Sleep without waiting for the primary oscillator to become stable.

Note: Executing a SLEEP instruction will abort the oscillator start-up time and will cause the OSTS bit of the OSCCON register to remain clear. When the Oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) is enabled (see **Section 4.4.1 "Oscillator Start-up Timer (OST)"**). The OST will suspend program execution until 1024 oscillations are counted. Two-Speed Start-up mode minimizes the delay in code execution by operating from the internal oscillator as the OST is counting. When the OST count reaches 1024 and the OSTS bit of the OSCCON register is set, program execution switches to the external oscillator.

#### 4.7.1 TWO-SPEED START-UP MODE CONFIGURATION

Two-Speed Start-up mode is configured by the following settings:

- IESO (of the Configuration Word register) = 1; Internal/External Switchover bit (Two-Speed Start-up mode enabled).

- SCS (of the OSCCON register) = 0.

- FOSC<2:0> bits in the Configuration Word register (CONFIG) configured for LP, XT or HS mode.

Two-Speed Start-up mode is entered after:

- Power-on Reset (POR) and, if enabled, after Power-up Timer (PWRT) has expired, or

- Wake-up from Sleep.

If the external clock oscillator is configured to be anything other than LP, XT or HS mode, then Two-Speed Start-up is disabled. This is because the external clock oscillator does not require any stabilization time after POR or an exit from Sleep.

#### 4.7.2 TWO-SPEED START-UP SEQUENCE

- 1. Wake-up from Power-on Reset or Sleep.

- Instructions begin execution by the internal oscillator at the frequency set in the IRCF<2:0> bits of the OSCCON register.

- 3. OST enabled to count 1024 clock cycles.

- 4. OST timed out, wait for falling edge of the internal oscillator.

- 5. OSTS is set.

- 6. System clock held low until the next falling edge of new clock (LP, XT or HS mode).

- 7. System clock is switched to external clock source.

## 4.8 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM can detect oscillator failure any time after the Oscillator Start-up Timer (OST) has expired. The FSCM is enabled by setting the FCMEN bit in the Configuration Word register (CONFIG). The FSCM is applicable to all external oscillator modes (LP, XT, HS, EC, RC and RCIO).

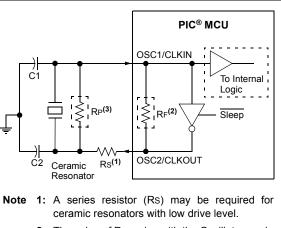

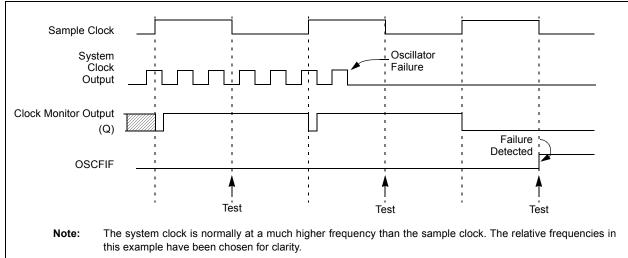

FIGURE 4-8: FSCM BLOCK DIAGRAM

#### 4.8.1 FAIL-SAFE DETECTION

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64. See Figure 4-8. Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the primary clock goes low.

### 4.8.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM switches the device clock to an internal clock source and sets the bit flag OSFIF of the PIR2 register. Setting this flag will generate an interrupt if the OSFIE bit of the PIE2 register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation.

The internal clock source chosen by the FSCM is determined by the IRCF<2:0> bits of the OSCCON register. This allows the internal oscillator to be configured before a failure occurs.

### 4.8.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, executing a SLEEP instruction or toggling the SCS bit of the OSCCON register. When the SCS bit is toggled, the OST is restarted. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON. When the OST times out, the Fail-Safe condition is cleared and the device will be operating from the external clock source. The Fail-Safe condition must be cleared before the OSFIF flag can be cleared.

#### 4.8.4 RESET OR WAKE-UP FROM SLEEP

The FSCM is designed to detect an oscillator failure after the Oscillator Start-up Timer (OST) has expired. The OST is used after waking up from Sleep and after any type of Reset. The OST is not used with the EC or RC Clock modes so that the FSCM will be active as soon as the Reset or wake-up has completed. When the FSCM is enabled, the Two-Speed Start-up is also enabled. Therefore, the device will always be executing code while the OST is operating.

Note: Due to the wide range of oscillator start-up times, the Fail-Safe circuit is not active during oscillator start-up (i.e., after exiting Reset or Sleep). After an appropriate amount of time, the user should check the OSTS bit of the OSCCON register to verify the oscillator start-up and that the system clock switchover has successfully completed.

#### FIGURE 4-9: FSCM TIMING DIAGRAM

| TABLE 4-2: | SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK SOURCES |

|------------|----------------------------------------------------|

|            |                                                    |

| Name                  | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets <sup>(1)</sup> |

|-----------------------|--------|--------|---------|---------|---------|--------|--------|--------|----------------------|------------------------------------------------|

| CONFIG <sup>(2)</sup> | CPD    | CP     | MCLRE   | PWRTE   | WDTE    | FOSC2  | FOSC1  | FOSC0  | _                    | _                                              |

| INTCON                | GIE    | PEIE   | T0IE    | INTE    | RBIE    | T0IF   | INTF   | RBIF   | 0000 000x            | 0000 000x                                      |

| OSCCON                | _      | IRCF2  | IRCF1   | IRCF0   | OSTS    | HTS    | LTS    | SCS    | -110 x000            | -110 x000                                      |

| OSCTUNE               | _      | —      | —       | TUN4    | TUN3    | TUN2   | TUN1   | TUN0   | 0 0000               | u uuuu                                         |

| PIE2                  | OSFIE  | C2IE   | C1IE    | LCDIE   | _       | LVDIE  | _      | CCP2IE | 0000 -0-0            | 0000 -0-0                                      |

| PIR2                  | OSFIF  | C2IF   | C1IF    | LCDIF   | _       | LVDIF  |        | CCP2IF | 0000 -0-0            | 0000 -0-0                                      |

| T1CON                 | T1GINV | TMR1GE | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 0000 0000            | 0000 0000                                      |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by oscillators.

Note 1: Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

2: See Configuration Word register (CONFIG) for operation of all register bits.

| TABLE 6-1: | SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1 |

|------------|---------------------------------------------|

|------------|---------------------------------------------|

| Name   | Bit 7                                                                       | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-----------------------------------------------------------------------------|--------|---------|---------|---------|--------|--------|--------|----------------------|---------------------------------|

| CMCON1 | —                                                                           | _      | _       | —       | _       |        | T1GSS  | C2SYNC | 10                   | 10                              |

| INTCON | GIE                                                                         | PEIE   | T0IE    | INTE    | RBIE    | T0IF   | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | EEIE                                                                        | ADIE   | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | EEIF                                                                        | ADIF   | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| TMR1H  | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register  |        |         |         |         |        |        |        |                      | uuuu uuuu                       |

| TMR1L  | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |        |         |         |         |        |        |        | xxxx xxxx            | uuuu uuuu                       |

| T1CON  | T1GINV                                                                      | TMR1GE | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 0000 0000            | uuuu uuuu                       |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

# © 2007 Microchip Technology Inc.

| Name                     | Bit 7         | Bit 6         | Bit 5         | Bit 4         | Bit 3         | Bit 2         | Bit 1         | Bit 0         | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------------------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|----------------------|---------------------------------|

| CMCON0                   | C2OUT         | C1OUT         | C2INV         | C1INV         | CIS           | CM2           | CM1           | CM0           | 0000 0000            | 0000 0000                       |

| INTCON                   | GIE           | PEIE          | T0IE          | INTE          | RBIE          | T0IF          | INTF          | RBIF          | 0000 000x            | 0000 000x                       |

| LCDCON                   | LCDEN         | SLPEN         | WERR          | VLCDEN        | CS1           | CS0           | LMUX1         | LMUX0         | 0001 0011            | 0001 0011                       |

| LCDDATA0                 | SEG7<br>COM0  | SEG6<br>COM0  | SEG5<br>COM0  | SEG4<br>COM0  | SEG3<br>COM0  | SEG2<br>COM0  | SEG1<br>COM0  | SEG0<br>COM0  | XXXX XXXX            | uuuu uuuu                       |

| LCDDATA1                 | SEG15<br>COM0 | SEG14<br>COM0 | SEG13<br>COM0 | SEG12<br>COM0 | SEG11<br>COM0 | SEG10<br>COM0 | SEG9<br>COM0  | SEG8<br>COM0  | XXXX XXXX            | uuuu uuuu                       |

| LCDDATA2 <sup>(2)</sup>  | SEG23<br>COM0 | SEG22<br>COM0 | SEG21<br>COM0 | SEG20<br>COM0 | SEG19<br>COM0 | SEG18<br>COM0 | SEG17<br>COM0 | SEG16<br>COM0 | xxxx xxxx            | uuuu uuuu                       |

| LCDDATA3                 | SEG7<br>COM1  | SEG6<br>COM1  | SEG5<br>COM1  | SEG4<br>COM1  | SEG3<br>COM1  | SEG2<br>COM1  | SEG1<br>COM1  | SEG0<br>COM1  | xxxx xxxx            | uuuu uuuu                       |

| LCDDATA4                 | SEG15<br>COM1 | SEG14<br>COM1 | SEG13<br>COM1 | SEG12<br>COM1 | SEG11<br>COM1 | SEG10<br>COM1 | SEG9<br>COM1  | SEG8<br>COM1  | xxxx xxxx            | uuuu uuuu                       |

| LCDDATA5 <sup>(2)</sup>  | SEG23<br>COM1 | SEG22<br>COM1 | SEG21<br>COM1 | SEG20<br>COM1 | SEG19<br>COM1 | SEG18<br>COM1 | SEG17<br>COM1 | SEG16<br>COM1 | xxxx xxxx            | uuuu uuuu                       |

| LCDDATA6                 | SEG7<br>COM2  | SEG6<br>COM2  | SEG5<br>COM2  | SEG4<br>COM2  | SEG3<br>COM2  | SEG2<br>COM2  | SEG1<br>COM2  | SEG0<br>COM2  | xxxx xxxx            | uuuu uuuu                       |

| LCDDATA7                 | SEG15<br>COM2 | SEG14<br>COM2 | SEG13<br>COM2 | SEG12<br>COM2 | SEG11<br>COM2 | SEG10<br>COM2 | SEG9<br>COM2  | SEG8<br>COM2  | XXXX XXXX            | uuuu uuuu                       |

| LCDDATA8 <sup>(2)</sup>  | SEG23<br>COM2 | SEG22<br>COM2 | SEG21<br>COM2 | SEG20<br>COM2 | SEG19<br>COM2 | SEG18<br>COM2 | SEG17<br>COM2 | SEG16<br>COM2 | XXXX XXXX            | uuuu uuuu                       |

| LCDDATA9                 | SEG7<br>COM3  | SEG6<br>COM3  | SEG5<br>COM3  | SEG4<br>COM3  | SEG3<br>COM3  | SEG2<br>COM3  | SEG1<br>COM3  | SEG0<br>COM3  | XXXX XXXX            | uuuu uuuu                       |

| LCDDATA10                | SEG15<br>COM3 | SEG14<br>COM3 | SEG13<br>COM3 | SEG12<br>COM3 | SEG11<br>COM3 | SEG10<br>COM3 | SEG9<br>COM3  | SEG8<br>COM3  | XXXX XXXX            | uuuu uuuu                       |

| LCDDATA11 <sup>(2)</sup> | SEG23<br>COM3 | SEG22<br>COM3 | SEG21<br>COM3 | SEG20<br>COM3 | SEG19<br>COM3 | SEG18<br>COM3 | SEG17<br>COM3 | SEG16<br>COM3 | XXXX XXXX            | uuuu uuuu                       |

| LCDDATA12 <sup>(3)</sup> | SEG31<br>COM0 | SEG30<br>COM0 | SEG29<br>COM0 | SEG28<br>COM0 | SEG27<br>COM0 | SEG26<br>COM0 | SEG25<br>COM0 | SEG24<br>COM0 | XXXX XXXX            | uuuu uuuu                       |

| LCDDATA13 <sup>(3)</sup> | SEG39<br>COM0 | SEG38<br>COM0 | SEG37<br>COM0 | SEG36<br>COM0 | SEG35<br>COM0 | SEG34<br>COM0 | SE33<br>COM0  | SEG32<br>COM0 | XXXX XXXX            | uuuu uuuu                       |

| LCDDATA14 <sup>(3)</sup> | —             | _             | —             | —             | _             | —             | SEG41<br>COM0 | SEG40<br>COM0 | xx                   | uu                              |

| LCDDATA15 <sup>(3)</sup> | SEG31<br>COM1 | SEG30<br>COM1 | SEG29<br>COM1 | SEG28<br>COM1 | SEG27<br>COM1 | SEG26<br>COM1 | SEG25<br>COM1 | SEG24<br>COM1 | xxxx xxxx            | uuuu uuuu                       |

| LCDDATA16 <sup>(3)</sup> | SEG39<br>COM1 | SEG38<br>COM1 | SEG37<br>COM1 | SEG36<br>COM1 | SEG35<br>COM1 | SEG34<br>COM1 | SEG33<br>COM1 | SEG32<br>COM1 | XXXX XXXX            | uuuu uuuu                       |

| LCDDATA17 <sup>(3)</sup> | —             | —             | —             | —             | —             | —             | SEG41<br>COM1 | SEG40<br>COM1 | xx                   | uu                              |

| LCDDATA18 <sup>(3)</sup> | SEG31<br>COM2 | SEG30<br>COM2 | SEG29<br>COM2 | SEG28<br>COM2 | SEG27<br>COM2 | SEG26<br>COM2 | SEG25<br>COM2 | SEG24<br>COM2 | XXXX XXXX            | uuuu uuuu                       |

| LCDDATA19 <sup>(3)</sup> | SEG39<br>COM2 | SEG38<br>COM2 | SEG37<br>COM2 | SEG36<br>COM2 | SEG35<br>COM2 | SEG34<br>COM2 | SEG33<br>COM2 | SEG32<br>COM2 | xxxx xxxx            | uuuu uuuu                       |

| LCDDATA20 <sup>(3)</sup> | _             | —             | _             | —             | _             | —             | SEG41<br>COM2 | SEG40<br>COM2 | xx                   | uu                              |

| LCDDATA21 <sup>(3)</sup> | SEG31<br>COM3 | SEG30<br>COM3 | SEG29<br>COM3 | SEG28<br>COM3 | SEG27<br>COM3 | SEG26<br>COM3 | SEG25<br>COM3 | SEG24<br>COM3 | XXXX XXXX            | uuuu uuuu                       |

| LCDDATA22 <sup>(3)</sup> | SEG39<br>COM3 | SEG38<br>COM3 | SEG37<br>COM3 | SEG36<br>COM3 | SEG35<br>COM3 | SEG34<br>COM3 | SEG33<br>COM3 | SEG32<br>COM3 | xxxx xxxx            | uuuu uuuu                       |

| LCDDATA23 <sup>(3)</sup> | —             | —             | —             | —             | —             | —             | SEG41<br>COM3 | SEG40<br>COM3 | xx                   | uu                              |

| LCDPS                    | WFT           | BIASMD        | LCDA          | WA            | LP3           | LP2           | LP1           | LP0           | 0000 0000            | 0000 0000                       |

| LCDSE0                   | SE7           | SE6           | SE5           | SE4           | SE3           | SE2           | SE1           | SE0           | 0000 0000            | uuuu uuuu                       |

| LCDSE1                   | SE15          | SE14          | SE13          | SE12          | SE11          | SE10          | SE9           | SE8           | 0000 0000            | uuuu uuuu                       |

x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the LCD module. These pins may be configured as port pins, depending on the oscillator mode selected. PIC16F914/917 and PIC16F946 only. PIC16F946 only. Legend:

Note 1:

2: 3:

#### 14.5 Master Mode

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2, Figure 14-2) is to broadcast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SDO output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and Status bits appropriately set). This could be useful in receiver applications as a Line Activity Monitor mode. The clock polarity is selected by appropriately programming the CKP bit of the SSPCON register. This then, would give waveforms for SPI communication as shown in Figure 14-3, Figure 14-5 and Figure 14-6, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 Tcy)

- Fosc/64 (or 16 Tcy)

- Timer2 output/2

This allows a maximum data rate (at 20 MHz) of 5 Mbps.

Figure 14-3 shows the waveforms for Master mode. When the CKE bit is set, the SDO data is valid before there is a clock edge on SCK. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPBUF is loaded with the received data is shown.

Write to SSPBUF SCK (CKP = 0  $\dot{C}KE = 0$ ) SCK (CKP = 1  $\dot{C}KE = 0$ 4 Clock Modes SCK (CKP = 0)ČKE = 1) SCK (CKP = 1 CKE = 1) SDO bit 6 bit 5 bit 4 bit 2 bit 1 bit 0 bit 7 bit 3 (CKE = 0)SDO bit 6 bit 5 bit 4 bit 2 bit 1 bit 0 bit 7 bit 3 (CKE = 1) SDI (SMP = 0)hit 7 bit 0 Input Sample  $(SM\dot{P} = 0)$ SDI (SMP = 1) bit 7 bit 0 Input Sample (SMP = 1)I SSPIF Next Q4 Cycle SSPSR to after Q2↓ SSPBUF

FIGURE 14-3: SPI MODE WAVEFORM (MASTER MODE)

#### 14.12.1 ADDRESSING

Once the SSP module has been enabled, it waits for a Start condition to occur. Following the Start condition, the 8-bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPADD <7:1> is compared to the value of register SSPADD <7:1>. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- a) The SSPSR register value is loaded into the SSPBUF register.

- b) The buffer full bit, BF is set.

- c) An ACK pulse is generated.

- d) SSP interrupt flag bit, SSPIF of the PIR1 register is set (interrupt is generated if enabled) on the falling edge of the ninth SCL pulse.

In 10-bit Address mode, two address bytes need to be received by the slave (Figure 14-8). The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address.

The sequence of events for 10-bit address is as follows, with steps 7-9 for slave-transmitter:

- 1. Receive first (high) byte of address (bits SSPIF, BF and bit UA (SSPSTAT<1>) are set).

- Update the SSPADD register with second (low) byte of address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of address (bits SSPIF, BF and UA are set).

- 5. Update the SSPADD register with the first (high) byte of address; if match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive repeated Start condition.

- 8. Receive first (high) byte of address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

#### TABLE 14-3: DATA TRANSFER RECEIVED BYTE ACTIONS

| Status Bits as Data<br>Transfer is Received |       | $SSPSR \to SSPBUF$ | Generate ACK<br>Pulse | Set bit SSPIF<br>(SSP Interrupt occurs |  |

|---------------------------------------------|-------|--------------------|-----------------------|----------------------------------------|--|

| BF                                          | SSPOV |                    | Fuise                 | if enabled)                            |  |

| 0                                           | 0     | Yes                | Yes                   | Yes                                    |  |

| 1                                           | 0     | No                 | No                    | Yes                                    |  |

| 1                                           | 1     | No                 | No                    | Yes                                    |  |

| 0                                           | 1     | No                 | No                    | Yes                                    |  |

**Note:** Shaded cells show the conditions where the user software did not properly clear the overflow condition.

| ADDLW            | Add literal and W                                                                                                          |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                          |  |  |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                                          |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                   |  |  |  |  |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k'<br>and the result is placed in the<br>W register. |  |  |  |  |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]BCF f,b                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | 0 → (f <b>)</b>                                                     |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| ADDWF            | Add W and f                                                                                                                                                                        |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                         |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                 |  |  |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                              |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                           |  |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back<br>in register 'f'. |  |  |  |  |  |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]BSF f,b                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND literal with W                                                                                                     |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                               |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                      |  |  |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |  |  |  |  |

| Status Affected: | Z                                                                                                                      |  |  |  |  |

| Description:     | The contents of W register are<br>AND'ed with the eight-bit literal<br>'k'. The result is placed in the W<br>register. |  |  |  |  |

|                  | register.                                                                                                             |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|

| ANDWF            | AND W with f                                                                                                          |  |  |  |

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                            |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                    |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                             |  |  |  |

| Status Affected: | Z                                                                                                                     |  |  |  |

| Description:     | AND the W register with register<br>'f'. If 'd' is '0', the result is stored in<br>the W register. If 'd' is '1', the |  |  |  |

result is stored back in register 'f'.

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                     |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ]BTFSC f,b                                                                                                                                                                                                     |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                           |  |  |  |  |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                                       |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                          |  |  |  |  |

| Description:     | If bit 'b' in register 'f' is '1', the next<br>instruction is executed.<br>If bit 'b', in register 'f', is '0', the<br>next instruction is discarded, and<br>a NOP is executed instead, making<br>this a 2-cycle instruction. |  |  |  |  |

NOTES:

#### PIC16F913/914/916/917/946-I (Industrial) 19.5 **DC Characteristics:** PIC16F913/914/916/917/946-E (Extended) (Continued)

| DC CHARACTERISTICS               |       | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array}$ |      |      |      |       |                                                                        |

|----------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|------------------------------------------------------------------------|

| Param<br>No. Sym. Characteristic |       | Characteristic                                                                                                                                                                                                                                                 | Min. | Typ† | Max. | Units | Conditions                                                             |

|                                  |       | Capacitive Loading Specs on<br>Output Pins                                                                                                                                                                                                                     |      |      |      |       |                                                                        |

| D101*                            | COSC2 | OSC2 pin                                                                                                                                                                                                                                                       | _    | -    | 15   | pF    | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1 |

| D101A*                           | Сю    | All I/O pins                                                                                                                                                                                                                                                   | —    | _    | 50   | pF    |                                                                        |

|                                  |       | Data EEPROM Memory                                                                                                                                                                                                                                             |      |      |      |       |                                                                        |

| D120                             | ED    | Byte Endurance                                                                                                                                                                                                                                                 | 100K | 1M   | _    | E/W   | $-40^{\circ}C \le TA \le +85^{\circ}C$                                 |

| D120A                            | ED    | Byte Endurance                                                                                                                                                                                                                                                 | 10K  | 100K | —    | E/W   | $+85^{\circ}C \le TA \le +125^{\circ}C$                                |

| D121                             | Vdrw  | VDD for Read/Write                                                                                                                                                                                                                                             | VMIN | —    | 5.5  | V     | Using EECON1 to read/write<br>VMIN = Minimum operating<br>voltage      |

| D122                             | TDEW  | Erase/Write Cycle Time                                                                                                                                                                                                                                         | _    | 5    | 6    | ms    |                                                                        |

| D123                             | TRETD | Characteristic Retention                                                                                                                                                                                                                                       | 40   | _    | —    | Year  | Provided no other specifications are violated                          |

| D124                             | TREF  | Number of Total Erase/Write<br>Cycles before Refresh <sup>(4)</sup>                                                                                                                                                                                            | 1M   | 10M  | —    | E/W   | $-40^{\circ}C \le TA \le +85^{\circ}C$                                 |

|                                  |       | Program Flash Memory                                                                                                                                                                                                                                           |      |      |      |       |                                                                        |

| D130                             | Eр    | Cell Endurance                                                                                                                                                                                                                                                 | 10K  | 100K | —    | E/W   | $-40^{\circ}C \le TA \le +85^{\circ}C$                                 |

| D130A                            | ED    | Cell Endurance                                                                                                                                                                                                                                                 | 1K   | 10K  | _    | E/W   | +85°C ≤ TA ≤ +125°C                                                    |

| D131                             | Vpr   | VDD for Read                                                                                                                                                                                                                                                   | Vmin | -    | 5.5  | V     | VMIN = Minimum operating<br>voltage                                    |

| D132                             | VPEW  | VDD for Erase/Write                                                                                                                                                                                                                                            | 4.5  | —    | 5.5  | V     |                                                                        |

| D133                             | TPEW  | Erase/Write cycle time                                                                                                                                                                                                                                         | —    | —    | 3    | ms    |                                                                        |

| D134                             | TRETD | Characteristic Retention                                                                                                                                                                                                                                       | 40   | -    | —    | Year  | Provided no other specifications are violated                          |

These parameters are characterized but not tested.

t Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: See Section 13.0 "Data EEPROM and Flash Program Memory Control" for additional information.

5: Including OSC2 in CLKOUT mode.

| DC CHARACTERISTICS |                    |                 | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |          |                |                 |       |                          |

|--------------------|--------------------|-----------------|------------------------------------------------------|----------|----------------|-----------------|-------|--------------------------|

| Sym.               | Characteristic     |                 | Min.                                                 | Тур†     | Max.<br>(85°C) | Max.<br>(125°C) | Units | Conditions               |

| VPLVD              | PLVD<br>Voltage    | LVDL<2:0> = 001 | 1.900                                                | 2.0      | 2.100          | 2.125           | V     |                          |

|                    |                    | LVDL<2:0> = 010 | 2.000                                                | 2.1      | 2.200          | 2.225           | V     |                          |

|                    |                    | LVDL<2:0> = 011 | 2.100                                                | 2.2      | 2.300          | 2.325           | V     |                          |

|                    |                    | LVDL<2:0> = 100 | 2.200                                                | 2.3      | 2.400          | 2.425           | V     |                          |

|                    |                    | LVDL<2:0> = 101 | 3.825                                                | 4.0      | 4.175          | 4.200           | V     |                          |

|                    |                    | LVDL<2:0> = 110 | 4.025                                                | 4.2      | 4.375          | 4.400           | V     |                          |

|                    |                    | LVDL<2:0> = 111 | 4.425                                                | 4.5      | 4.675          | 4.700           | V     |                          |

| *TPLVDS            | PLVD Settling time |                 | —                                                    | 50<br>25 |                |                 | μs    | VDD = 5.0V<br>VDD = 3.0V |

#### TABLE 19-13: PIC16F913/914/916/917/946 PLVD CHARACTERISTICS:

\* These parameters are characterized but not tested

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com, click on Customer Change Notification and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

- Development Systems Information Line

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://support.microchip.com