Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

|                            | Activo                                                                   |

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                               |

| Number of I/O              | 35                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-TQFP                                                                  |

| Supplier Device Package    | 44-TQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f914-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

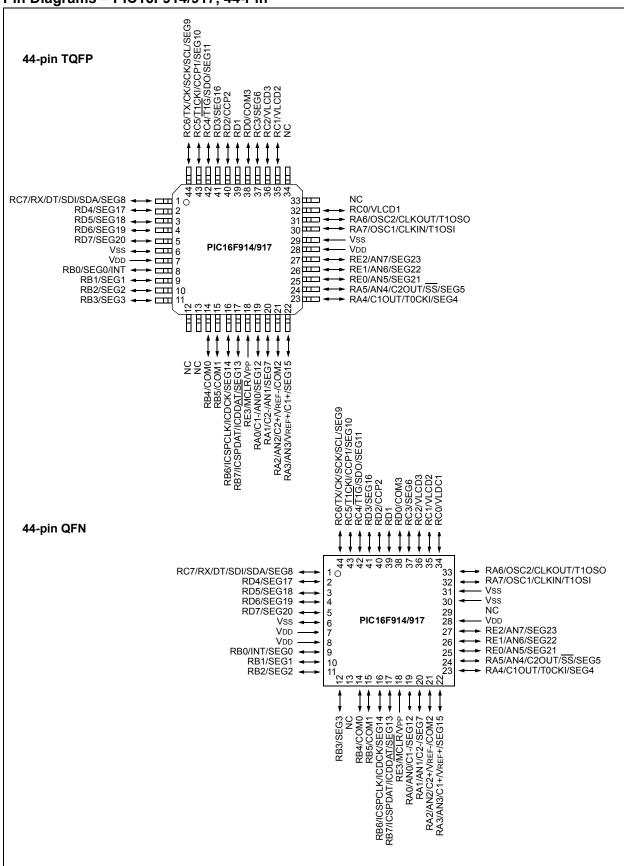

### Pin Diagrams - PIC16F914/917, 44-Pin

NOTES:

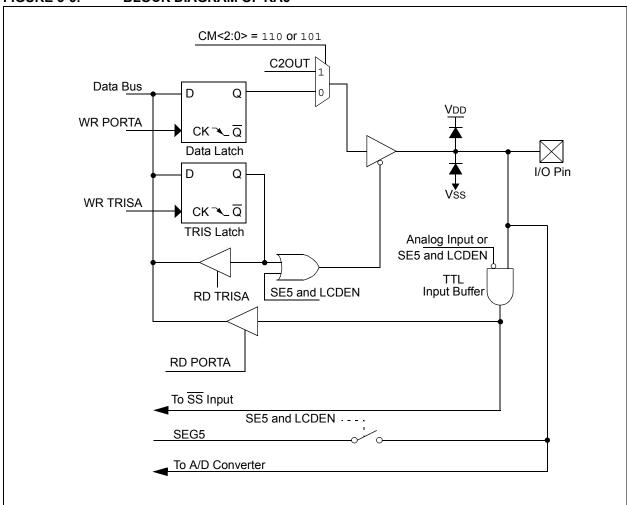

### 3.2.1.6 RA5/AN4/C2OUT/SS/SEG5

Figure 3-6 shows the diagram for this pin. The RA5 pin is configurable to function as one of the following:

- · a general purpose I/O

- · a digital output from Comparator C2

- · a slave select input

- · an analog output for the LCD

- · an analog input for the ADC

### FIGURE 3-6: BLOCK DIAGRAM OF RA5

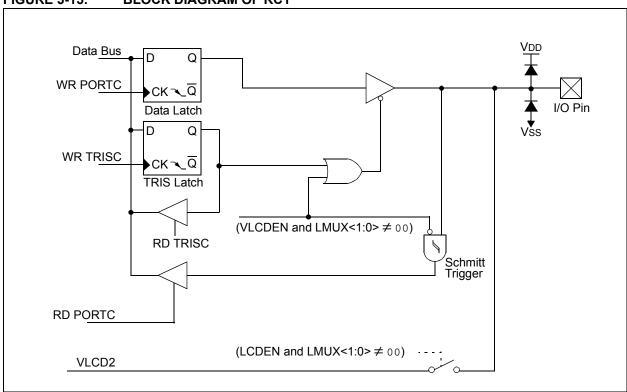

FIGURE 3-15: BLOCK DIAGRAM OF RC1

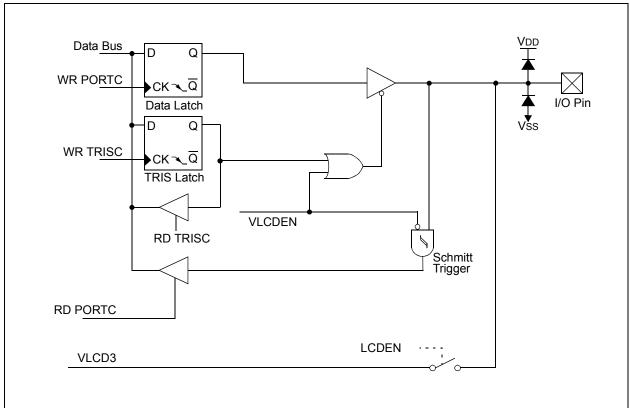

FIGURE 3-16: BLOCK DIAGRAM OF RC2

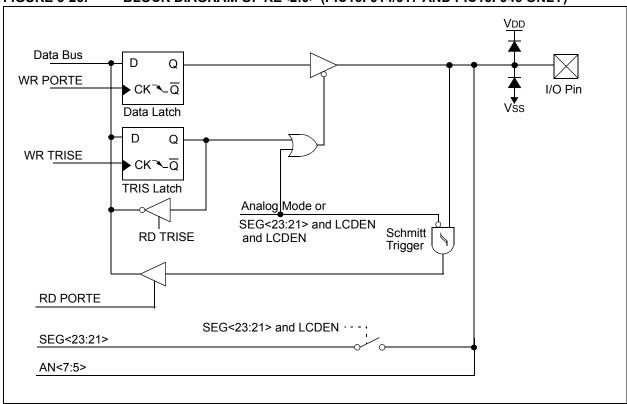

FIGURE 3-26: BLOCK DIAGRAM OF RE<2:0> (PIC16F914/917 AND PIC16F946 ONLY)

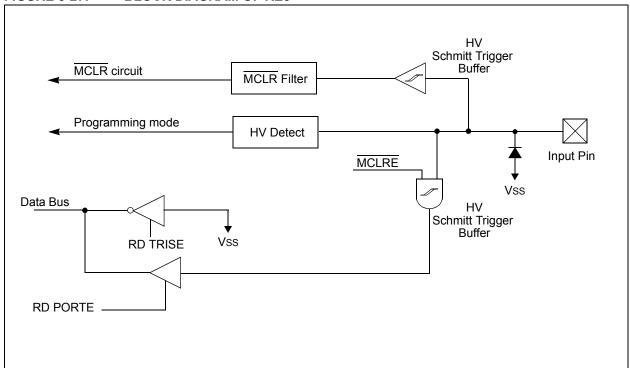

FIGURE 3-27: BLOCK DIAGRAM OF RE3

#### 4.5.3 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is an uncalibrated 31 kHz internal clock source.

The output of the LFINTOSC connects to a postscaler and multiplexer (see Figure 4-1). Select 31 kHz, via software, using the IRCF<2:0> bits of the OSCCON register. See **Section 4.5.4 "Frequency Select Bits (IRCF)"** for more information. The LFINTOSC is also the frequency for the Power-up Timer (PWRT), Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The LFINTOSC is enabled by selecting 31 kHz (IRCF<2:0> bits of the OSCCON register = 000) as the system clock source (SCS bit of the OSCCON register = 1), or when any of the following are enabled:

- Two-Speed Start-up IESO bit of the Configuration Word register = 1 and IRCF<2:0> bits of the OSCCON register = 000

- · Power-up Timer (PWRT)

- Watchdog Timer (WDT)

- Fail-Safe Clock Monitor (FSCM)

The LF Internal Oscillator (LTS) bit of the OSCCON register indicates whether the LFINTOSC is stable or not.

### 4.5.4 FREQUENCY SELECT BITS (IRCF)

The output of the 8 MHz HFINTOSC and 31 kHz LFINTOSC connects to a postscaler and multiplexer (see Figure 4-1). The Internal Oscillator Frequency Select bits IRCF<2:0> of the OSCCON register select the frequency output of the internal oscillators. One of eight frequencies can be selected via software:

- 8 MHz

- · 4 MHz (Default after Reset)

- 2 MHz

- 1 MHz

- 500 kHz

- 250 kHz

- 125 kHz

- 31 kHz (LFINTOSC)

Note:

Following any Reset, the IRCF<2:0> bits of the OSCCON register are set to '110' and the frequency selection is set to 4 MHz. The user can modify the IRCF bits to select a different frequency.

# 4.5.5 HF AND LF INTOSC CLOCK SWITCH TIMING

When switching between the LFINTOSC and the HFINTOSC, the new oscillator may already be shut down to save power (see Figure 4-6). If this is the case, there is a delay after the IRCF<2:0> bits of the OSCCON register are modified before the frequency selection takes place. The LTS and HTS bits of the OSCCON register will reflect the current active status of the LFINTOSC and HFINTOSC oscillators. The timing of a frequency selection is as follows:

- IRCF<2:0> bits of the OSCCON register are modified.

- If the new clock is shut down, a clock start-up delay is started.

- Clock switch circuitry waits for a falling edge of the current clock.

- CLKOUT is held low and the clock switch circuitry waits for a rising edge in the new clock.

- CLKOUT is now connected with the new clock. LTS and HTS bits of the OSCCON register are updated as required.

- 6. Clock switch is complete.

See Figure 4-1 for more details.

If the internal oscillator speed selected is between 8 MHz and 125 kHz, there is no start-up delay before the new frequency is selected. This is because the old and new frequencies are derived from the HFINTOSC via the postscaler and multiplexer.

Start-up delay specifications are located under the oscillator parameters of **Section 19.0** "Electrical **Specifications**".

### 4.8 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM can detect oscillator failure any time after the Oscillator Start-up Timer (OST) has expired. The FSCM is enabled by setting the FCMEN bit in the Configuration Word register (CONFIG). The FSCM is applicable to all external oscillator modes (LP, XT, HS, EC, RC and RCIO).

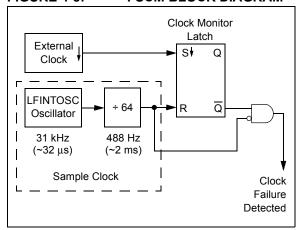

FIGURE 4-8: FSCM BLOCK DIAGRAM

### 4.8.1 FAIL-SAFE DETECTION

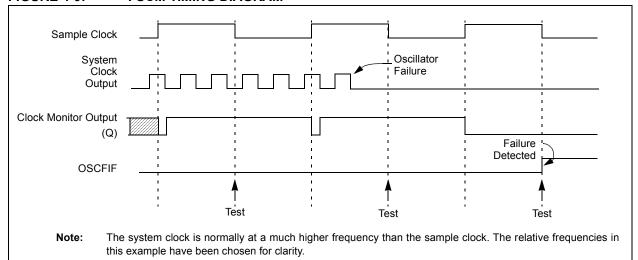

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64. See Figure 4-8. Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the primary clock goes low.

### 4.8.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM switches the device clock to an internal clock source and sets the bit flag OSFIF of the PIR2 register. Setting this flag will generate an interrupt if the OSFIE bit of the PIE2 register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation.

The internal clock source chosen by the FSCM is determined by the IRCF<2:0> bits of the OSCCON register. This allows the internal oscillator to be configured before a failure occurs.

#### 4.8.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, executing a SLEEP instruction or toggling the SCS bit of the OSCCON register. When the SCS bit is toggled, the OST is restarted. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON. When the OST times out, the Fail-Safe condition is cleared and the device will be operating from the external clock source. The Fail-Safe condition must be cleared before the OSFIF flag can be cleared.

### 4.8.4 RESET OR WAKE-UP FROM SLEEP

The FSCM is designed to detect an oscillator failure after the Oscillator Start-up Timer (OST) has expired. The OST is used after waking up from Sleep and after any type of Reset. The OST is not used with the EC or RC Clock modes so that the FSCM will be active as soon as the Reset or wake-up has completed. When the FSCM is enabled, the Two-Speed Start-up is also enabled. Therefore, the device will always be executing code while the OST is operating.

Note: Due to the wide range of oscillator start-up times, the Fail-Safe circuit is not active during oscillator start-up (i.e., after exiting Reset or Sleep). After an appropriate amount of time, the user should check the OSTS bit of the OSCCON register to verify the oscillator start-up and that the system clock switchover has successfully completed.

FIGURE 4-9: **FSCM TIMING DIAGRAM**

**TABLE 4-2:** SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK SOURCES

| Name                  | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets <sup>(1)</sup> |

|-----------------------|--------|--------|---------|---------|---------|--------|--------|--------|----------------------|------------------------------------------------|

| CONFIG <sup>(2)</sup> | CPD    | CP     | MCLRE   | PWRTE   | WDTE    | FOSC2  | FOSC1  | FOSC0  | _                    | _                                              |

| INTCON                | GIE    | PEIE   | T0IE    | INTE    | RBIE    | T0IF   | INTF   | RBIF   | 0000 000x            | 0000 000x                                      |

| OSCCON                | _      | IRCF2  | IRCF1   | IRCF0   | OSTS    | HTS    | LTS    | SCS    | -110 x000            | -110 x000                                      |

| OSCTUNE               | _      | _      | _       | TUN4    | TUN3    | TUN2   | TUN1   | TUN0   | 0 0000               | u uuuu                                         |

| PIE2                  | OSFIE  | C2IE   | C1IE    | LCDIE   | _       | LVDIE  | _      | CCP2IE | 0000 -0-0            | 0000 -0-0                                      |

| PIR2                  | OSFIF  | C2IF   | C1IF    | LCDIF   | _       | LVDIF  | _      | CCP2IF | 0000 -0-0            | 0000 -0-0                                      |

| T1CON                 | T1GINV | TMR1GE | T1CKPS1 | T1CKPS0 | T10SCEN | T1SYNC | TMR1CS | TMR10N | 0000 0000            | 0000 0000                                      |

${\bf x}$  = unknown,  ${\bf u}$  = unchanged, – = unimplemented locations read as 'o'. Shaded cells are not used by oscillators. Other (non Power-up) Resets include  $\overline{\text{MCLR}}$  Reset and Watchdog Timer Reset during normal operation. Legend:

Note 1:

See Configuration Word register (CONFIG) for operation of all register bits.

### REGISTER 8-1: CMCON0: COMPARATOR CONFIGURATION REGISTER

| R-0   | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| C2OUT | C1OUT | C2INV | C1INV | CIS   | CM2   | CM1   | CM0   |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 **C2OUT:** Comparator 2 Output bit

When C2INV = 0:

1 = C2 VIN+ > C2 VIN-

0 = C2 VIN+ < C2 VIN-

When C2INV = 1:

1 = C2 VIN+ < C2 VIN-

0 = C2 VIN+ > C2 VIN-

bit 6 C1OUT: Comparator 1 Output bit

When C1INV = 0:

1 = C1 VIN+ > C1 VIN-

0 = C1 VIN+ < C1 VIN-

When C1INV = 1:

1 = C1 VIN+ < C1 VIN-

0 = C1 VIN+ > C1 VIN-

bit 5 C2INV: Comparator 2 Output Inversion bit

1 = C2 output inverted

0 = C2 output not inverted

bit 4 C1INV: Comparator 1 Output Inversion bit

1 = C1 Output inverted

o = C1 Output not inverted

bit 3 CIS: Comparator Input Switch bit

When CM<2:0> = 010:

1 = C1IN+ connects to C1 VIN-

C2IN+ connects to C2 VIN-

0 = C1IN- connects to C1 VIN-

C2IN- connects to C2 VIN-

When CM < 2:0 > = 001:

1 = C1IN+ connects to C1 VIN-

0 = C1IN- connects to C1 VIN-

When CM<2:0> = 101: (16F91x/946)

1 = C2 VIN+ connects to fixed voltage reference

0 = C2 VIN+ connects to C2IN+

bit 2-0 CM<2:0>: Comparator Mode bits (See Figure 8-5)

000 = Comparators off. CxIN pins are configured as analog

001 = Three inputs multiplexed to two comparators

010 = Four inputs multiplexed to two comparators

011 = Two common reference comparators

100 = Two independent comparators

101 = One independent comparator

110 = Two comparators with outputs and common reference

111 = Comparators off. CxIN pins are configured as digital I/O

TABLE 9-5: BAUD RATES FOR ASYNCHRONOUS MODES

|        |                |                  |                             |                |                   | SYNC = 0,                   | BRGH = :       | 1                |                             |                |                  |                             |  |

|--------|----------------|------------------|-----------------------------|----------------|-------------------|-----------------------------|----------------|------------------|-----------------------------|----------------|------------------|-----------------------------|--|

| BAUD   | Fos            | Fosc = 4.000 MHz |                             |                | Fosc = 3.6864 MHz |                             |                | Fosc = 2.000 MHz |                             |                | Fosc = 1.000 MHz |                             |  |

| RATE   | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) |  |

| 300    | _              | _                | _                           | _              | _                 | _                           |                | _                | _                           | 300            | 0.16             | 207                         |  |

| 1200   | 1202           | 0.16             | 207                         | 1200           | 0.00              | 191                         | 1202           | 0.16             | 103                         | 1202           | 0.16             | 51                          |  |

| 2400   | 2404           | 0.16             | 103                         | 2400           | 0.00              | 95                          | 2404           | 0.16             | 51                          | 2404           | 0.16             | 25                          |  |

| 9600   | 9615           | 0.16             | 25                          | 9600           | 0.00              | 23                          | 9615           | 0.16             | 12                          | _              | _                | _                           |  |

| 10417  | 10417          | 0.00             | 23                          | 10473          | 0.53              | 21                          | 10417          | 0.00             | 11                          | 10417          | 0.00             | 5                           |  |

| 19.2k  | 19.23k         | 0.16             | 12                          | 19.2k          | 0.00              | 11                          | _              | _                | _                           | _              | _                | _                           |  |

| 57.6k  | _              | _                | _                           | 57.60k         | 0.00              | 3                           | _              | _                | _                           | _              | _                | _                           |  |

| 115.2k | _              | _                | _                           | 115.2k         | 0.00              | 1                           | _              | _                | _                           | _              | _                | _                           |  |

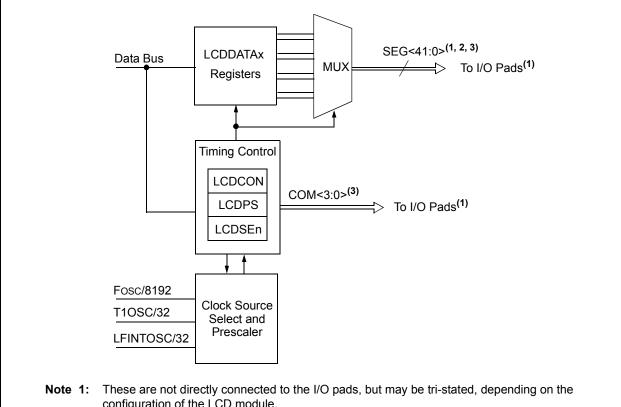

**FIGURE 10-1:** LCD DRIVER MODULE BLOCK DIAGRAM

- configuration of the LCD module.

- 2: SEG<23:0> on PIC16F914/917, SEG<15:0> on PIC16F913/916.

- 3: COM3 and SEG15 share the same physical pin on the PIC16F913/916, therefore SEG15 is not available when using 1/4 multiplex displays.

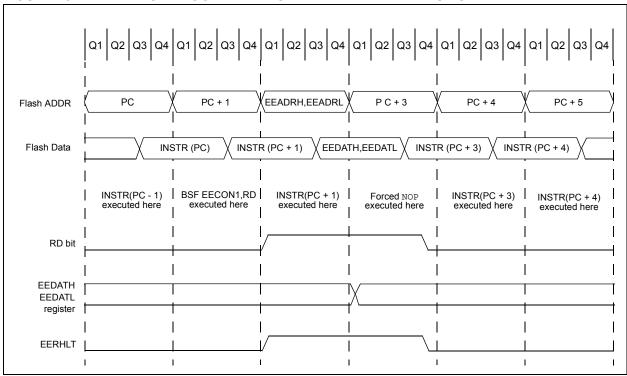

FIGURE 13-1: FLASH PROGRAM MEMORY READ CYCLE EXECUTION

TABLE 13-1: SUMMARY OF ASSOCIATED REGISTERS WITH DATA EEPROM

| Name   | Bit 7    | Bit 6         | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------|---------------|---------|---------|---------|---------|---------|---------|----------------------|---------------------------------|

| INTCON | GIE      | PEIE          | T0IE    | INTE    | RBIE    | T0IF    | INTF    | RBIF    | 0000 000x            | 0000 000x                       |

| PIE1   | EEIE     | ADIE          | RCIE    | TXIE    | SSPIE   | CCP1IE  | TMR2IE  | TMR1IE  | 0000 0000            | 0000 0000                       |

| PIR1   | EEIF     | ADIF          | RCIF    | TXIF    | SSPIF   | CCP1IF  | TMR2IF  | TMR1IF  | 0000 0000            | 0000 0000                       |

| EEADRH | -        | _             | _       | EEADRH4 | EEADRH3 | EEADRH2 | EEADRH1 | EEADRH0 | 0 0000               | 0 0000                          |

| EEADRL | EEADRL7  | EEADRL6       | EEADRL5 | EEADRL4 | EEADRL3 | EEADRL2 | EEADRL1 | EEADRL0 | 0000 0000            | 0000 0000                       |

| EECON1 | EEPGD    | _             | _       | _       | WRERR   | WREN    | WR      | RD      | 0 x000               | d000                            |

| EECON2 | EEPROM C | ontrol Regist |         |         |         |         |         |         |                      |                                 |

| EEDATH | _        | _             | EEDATH5 | EEDATH4 | EEDATH3 | EEDATH2 | EEDATH1 | EEDATH0 | 00 0000              | 00 0000                         |

| EEDATL | EEDATL7  | EEDATL6       | EEDATL5 | EEDATL4 | EEDATL3 | EEDATL2 | EEDATL1 | EEDATL0 | 0000 0000            | 0000 0000                       |

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends upon condition. Shaded cells are not used by data EEPROM module.

### 14.3 Enabling SPI I/O

To enable the serial port, SSP Enable bit SSPEN of the SSPCON register must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSPCON registers and then set the SSPEN bit. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, their data direction bits (in the TRISA and TRISC registers) should be set as follows:

- TRISC<7> bit must be set

- · SDI is automatically controlled by the SPI module

- · SDO must have TRISC<4> bit cleared

- SCK (Master mode) must have TRISC<6> bit cleared

- SCK (Slave mode) must have TRISC<6> bit set

- If enabled, SS must have TRISA<5> bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRISA and TRISC) registers to the opposite value.

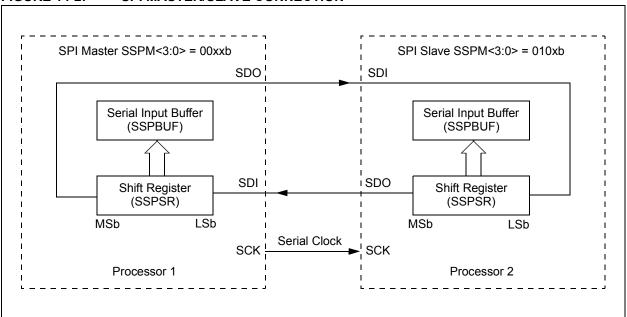

### 14.4 Typical Connection

Figure 14-2 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge and latched on the opposite edge of the clock. Both processors should be programmed to the same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- Master sends data Slave sends dummy data

- · Master sends data Slave sends data

- · Master sends dummy data Slave sends data

FIGURE 14-2: SPI MASTER/SLAVE CONNECTION

### 19.4 DC Characteristics: PIC16F913/914/916/917/946-E (Extended)

| DC CHARACTERISTICS |                              |      | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for extended |      |       |             |                                               |  |  |

|--------------------|------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------------|-----------------------------------------------|--|--|

| Param              | Davies Characteristics       | NA:  | T 1                                                                                                                                                     | Mass | Units | Conditions  |                                               |  |  |

| No.                | Device Characteristics       | Min. | Typ†                                                                                                                                                    | Max. | Units | <b>V</b> DD | Note                                          |  |  |

| D020E              | Power-down Base              | _    | 0.05                                                                                                                                                    | 9    | μΑ    | 2.0         | WDT, BOR, Comparators, VREF and               |  |  |

|                    | Current (IPD) <sup>(2)</sup> | _    | 0.15                                                                                                                                                    | 11   | μΑ    | 3.0         | T1OSC disabled                                |  |  |

|                    |                              |      | 0.35                                                                                                                                                    | 15   | μΑ    | 5.0         |                                               |  |  |

| D021E              |                              |      | 1                                                                                                                                                       | 28   | μΑ    | 2.0         | WDT Current <sup>(1)</sup>                    |  |  |

|                    |                              | _    | 2                                                                                                                                                       | 30   | μΑ    | 3.0         |                                               |  |  |

|                    |                              | _    | 3                                                                                                                                                       | 35   | μΑ    | 5.0         |                                               |  |  |

| D022E              |                              | _    | 42                                                                                                                                                      | 65   | μΑ    | 3.0         | BOR Current <sup>(1)</sup>                    |  |  |

|                    |                              | _    | 85                                                                                                                                                      | 127  | μΑ    | 5.0         |                                               |  |  |

| D022B              |                              | _    | 22                                                                                                                                                      | 48   | μΑ    | 2.0         | PLVD Current                                  |  |  |

|                    |                              |      | 25                                                                                                                                                      | 55   | μΑ    | 3.0         |                                               |  |  |

|                    |                              | _    | 33                                                                                                                                                      | 65   | μΑ    | 5.0         |                                               |  |  |

| D023E              |                              | _    | 32                                                                                                                                                      | 45   | μΑ    | 2.0         | Comparator Current <sup>(1)</sup> , both      |  |  |

|                    |                              |      | 60                                                                                                                                                      | 78   | μΑ    | 3.0         | comparators enabled                           |  |  |

|                    |                              | _    | 120                                                                                                                                                     | 160  | μΑ    | 5.0         |                                               |  |  |

| D024E              |                              | _    | 30                                                                                                                                                      | 70   | μΑ    | 2.0         | CVREF Current <sup>(1)</sup> (high range)     |  |  |

|                    |                              |      | 45                                                                                                                                                      | 90   | μΑ    | 3.0         |                                               |  |  |

|                    |                              | _    | 75                                                                                                                                                      | 120  | μΑ    | 5.0         |                                               |  |  |

| D025E*             |                              |      | 39                                                                                                                                                      | 91   | μΑ    | 2.0         | CVREF Current <sup>(1)</sup> (low range)      |  |  |

|                    |                              | _    | 59                                                                                                                                                      | 117  | μΑ    | 3.0         |                                               |  |  |

|                    |                              | _    | 98                                                                                                                                                      | 156  | μΑ    | 5.0         | 7                                             |  |  |

| D026E              |                              |      | 3.5                                                                                                                                                     | 18   | μΑ    | 2.0         | T1OSC Current <sup>(1)</sup> , 32.768 kHz     |  |  |

|                    |                              | _    | 4                                                                                                                                                       | 21   | μΑ    | 3.0         |                                               |  |  |

|                    |                              | _    | 5                                                                                                                                                       | 24   | μА    | 5.0         |                                               |  |  |

| D027E              |                              | _    | 0.30                                                                                                                                                    | 12   | μА    | 3.0         | A/D Current <sup>(1)</sup> , no conversion in |  |  |

|                    |                              | _    | 0.36                                                                                                                                                    | 16   | μΑ    | 5.0         | progress                                      |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral  $\Delta$  current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

<sup>2:</sup> The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

#### 19.6 **Thermal Considerations**

Standard Operating Conditions (unless otherwise stated) Operating temperature  $-40^{\circ}C \le TA \le +125^{\circ}C$ **Param Conditions Symbol** Units Characteristic Тур. No. TH01 60.0 °C/W 28-pin PDIP package  $\theta$ JA Thermal Resistance Junction to Ambient 0.08 °C/W 28-pin SOIC package 90.0 °C/W 28-pin SSOP package °C/W 27.5 28-pin QFN 6x6 mm package 47.2 °C/W 40-pin PDIP package °C/W 44-pin TQFP package 46.0 24.4 °C/W 44-pin QFN 8x8 mm package 77.0 °C/W 64-pin TQFP package TH02 θЈС Thermal Resistance 31.4 °C/W 28-pin PDIP package Junction to Case 24.0 °C/W 28-pin SOIC package 24.0 °C/W 28-pin SSOP package 20.0 °C/W 28-pin QFN 6x6 mm package 24.7 °C/W 40-pin PDIP package 14.5 °C/W 44-pin TQFP package 20.0 °C/W 44-pin QFN 8x8 mm package 24.4 °C/W 64-pin TQFP package TH03 °C TJ 150 For derated power calculations Junction Temperature TH04 PD PD = PINTERNAL + PI/O Power Dissipation W \_ TH05 PINTERNAL Internal Power Dissipation W PINTERNAL = IDD x VDD (NOTE 1) **TH06** Pı/o I/O Power Dissipation W  $P_{I}/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ PDER TH07 **Derated Power** PDER = (TJ - TA)/θJA

Note 1: IDD is current to run the chip alone without driving any load on the output pins.

W

(NOTE 2, 3)

TA = Ambient Temperature.

<sup>3:</sup> Maximum allowable power dissipation is the lower value of either the absolute maximum total power dissipation or derated power (PDER).

TABLE 19-13: PIC16F913/914/916/917/946 PLVD CHARACTERISTICS:

| DC CHA  | RACTERIS | STICS           | Standard Operating Conditions (unless otherwise stated)  Operating Temperature $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ Operating Voltage VDD Range 2.0V-5.5V |      |                |                 |       |            |  |

|---------|----------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------|-----------------|-------|------------|--|

| Sym.    | Cł       | naracteristic   | Min.                                                                                                                                                                              | Typ† | Max.<br>(85°C) | Max.<br>(125°C) | Units | Conditions |  |

| VPLVD   | PLVD     | LVDL<2:0> = 001 | 1.900                                                                                                                                                                             | 2.0  | 2.100          | 2.125           | V     |            |  |

|         | Voltage  | LVDL<2:0> = 010 | 2.000                                                                                                                                                                             | 2.1  | 2.200          | 2.225           | V     |            |  |

|         |          | LVDL<2:0> = 011 | 2.100                                                                                                                                                                             | 2.2  | 2.300          | 2.325           | V     |            |  |

|         |          | LVDL<2:0> = 100 | 2.200                                                                                                                                                                             | 2.3  | 2.400          | 2.425           | V     |            |  |

|         |          | LVDL<2:0> = 101 | 3.825                                                                                                                                                                             | 4.0  | 4.175          | 4.200           | V     |            |  |

|         |          | LVDL<2:0> = 110 | 4.025                                                                                                                                                                             | 4.2  | 4.375          | 4.400           | V     |            |  |

|         |          | LVDL<2:0> = 111 | 4.425                                                                                                                                                                             | 4.5  | 4.675          | 4.700           | V     |            |  |

| *TPLVDS | PLVD Set | tling time      | _                                                                                                                                                                                 | 50   |                | _               | μs    | VDD = 5.0V |  |

|         |          |                 |                                                                                                                                                                                   | 25   |                |                 |       | VDD = 3.0V |  |

<sup>\*</sup> These parameters are characterized but not tested

<sup>†</sup> Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

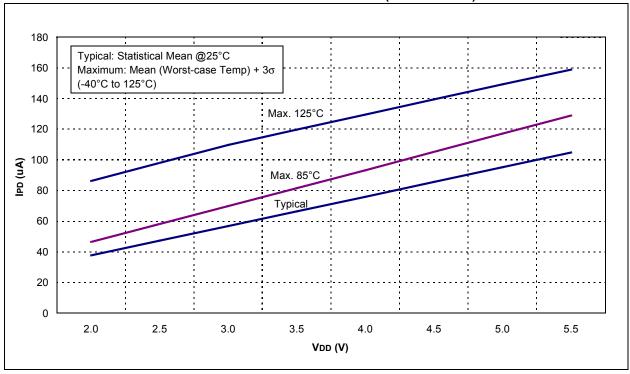

FIGURE 20-22: CVREF IPD vs. VDD OVER TEMPERATURE (LOW RANGE)

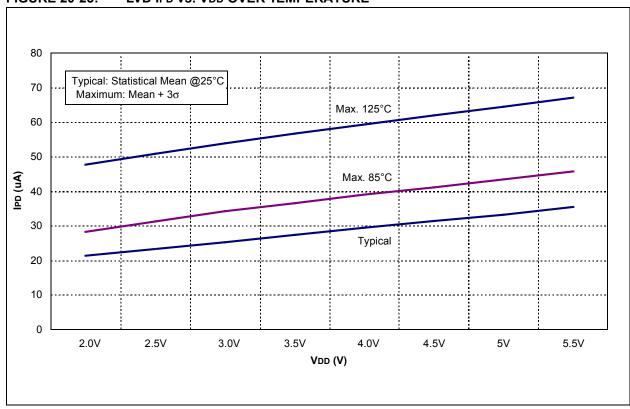

FIGURE 20-23: LVD IPD vs. VDD OVER TEMPERATURE

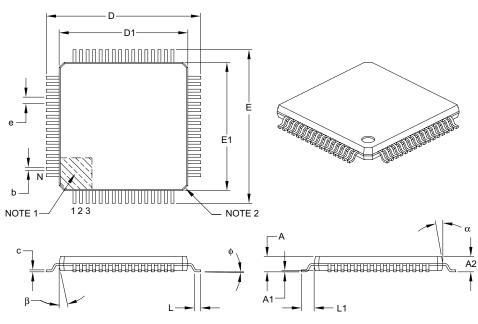

### 64-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**ote:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |           | MILLIMETERS | 3    |  |

|--------------------------|------------------|-----------|-------------|------|--|

|                          | Dimension Limits | MIN       | NOM         | MAX  |  |

| Number of Leads          | N                |           | 64          |      |  |

| Lead Pitch               | е                |           | 0.50 BSC    |      |  |

| Overall Height           | A                | -         | -           | 1.20 |  |

| Molded Package Thickness | A2               | 0.95      | 1.00        | 1.05 |  |

| Standoff                 | A1               | 0.05      | _           | 0.15 |  |

| Foot Length              | L                | 0.45      | 0.60        | 0.75 |  |

| Footprint                | L1 1.00 REF      |           |             |      |  |

| Foot Angle               | ф                | 0°        | 3.5°        | 7°   |  |

| Overall Width            | E                | 12.00 BSC |             |      |  |

| Overall Length           | D                | 12.00 BSC |             |      |  |

| Molded Package Width     | E1               | 10.00 BSC |             |      |  |

| Molded Package Length    | D1               | 10.00 BSC |             |      |  |

| Lead Thickness           | С                | 0.09      | _           | 0.20 |  |

| Lead Width               | b                | 0.17      | 0.22        | 0.27 |  |

| Mold Draft Angle Top     | α                | 11°       | 12°         | 13°  |  |

| Mold Draft Angle Bottom  | β                | 11°       | 12°         | 13°  |  |

#### Notes

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-085B

### **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| lo:   | Technical Publications Manager          | Total Pages Sent                                       |

|-------|-----------------------------------------|--------------------------------------------------------|

| RE:   | Reader Response                         |                                                        |

| From  | n: Name                                 |                                                        |

|       | Company                                 |                                                        |

|       | Address                                 |                                                        |

|       | City / State / ZIP / Country            |                                                        |

|       | Telephone: ()                           | FAX: ()                                                |

| Appli | ication (optional):                     |                                                        |

| Wou   | ld you like a reply?YN                  |                                                        |

| Devi  | ce: PIC16F913/914/916/917/946           | Literature Number: DS41250F                            |

| Ques  | stions:                                 |                                                        |

| 1. \  | What are the best features of this doo  | cument?                                                |

| _     |                                         |                                                        |

| 2. H  | How does this document meet your h      | nardware and software development needs?               |

| _     |                                         |                                                        |

| 3. [  | Do you find the organization of this do | ocument easy to follow? If not, why?                   |

|       | ,                                       |                                                        |

| _     |                                         |                                                        |

| 4. \  | What additions to the document do y     | ou think would enhance the structure and subject?      |

| _     |                                         |                                                        |

| 5. \  | What deletions from the document co     | ould be made without affecting the overall usefulness? |

| _     |                                         |                                                        |

| _     |                                         |                                                        |

| 6. I  | s there any incorrect or misleading ir  | nformation (what and where)?                           |

| -     |                                         |                                                        |

| 7. H  | How would you improve this docume       | nt?                                                    |

| -     |                                         |                                                        |

| _     |                                         |                                                        |