Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                               |

| Number of I/O              | 24                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 352 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 5x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-VQFN Exposed Pad                                                      |

| Supplier Device Package    | 28-QFN (6x6)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f916-i-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### REGISTER 3-4: PORTB: PORTB REGISTER

| R/W-x           | R/W-x | R/W-x            | R/W-x                                               | R/W-x        | R/W-x            | R/W-x    | R/W-x |

|-----------------|-------|------------------|-----------------------------------------------------|--------------|------------------|----------|-------|

| RB7             | RB6   | RB5              | RB4                                                 | RB3          | RB2              | RB1      | RB0   |

| bit 7           |       |                  |                                                     |              |                  |          | bit 0 |

|                 |       |                  |                                                     |              |                  |          |       |

| Legend:         |       |                  |                                                     |              |                  |          |       |

| R = Readable    | bit   | W = Writable     | bit                                                 | U = Unimplen | nented bit, read | l as '0' |       |

| -n = Value at F | POR   | '1' = Bit is set | = Bit is set '0' = Bit is cleared x = Bit is unknow |              |                  | nown     |       |

bit 7-0 **RB<7:0>:** PORTB I/O Pin bits 1 = Port pin is >VIH min. 0 = Port pin is <VIL max.

#### REGISTER 3-5: TRISB: PORTB TRI-STATE REGISTER

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0

TRISB<7:0>: PORTB Tri-State Control bits

1 = PORTB pin configured as an input (tri-stated)

0 = PORTB pin configured as an output

#### REGISTER 3-6: IOCB: PORTB INTERRUPT-ON-CHANGE REGISTER

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-------|-------|-----|-----|-----|-------|

| IOCB7 | IOCB6 | IOCB5 | IOCB4 | —   | —   | —   | —     |

| bit 7 |       |       |       |     |     |     | bit 0 |

| Legend:           |                  |                        |                                    |  |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |  |

bit 7-4 **IOCB<7:4>:** Interrupt-on-Change bits 1 = Interrupt-on-change enabled 0 = Interrupt-on-change disabled

bit 3-0 Unimplemented: Read as '0'

### 5.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A single software programmable prescaler is available for use with either Timer0 or the Watchdog Timer (WDT), but not both simultaneously. The prescaler assignment is controlled by the PSA bit of the Option register. To assign the prescaler to Timer0, the PSA bit must be cleared to a '0'.

There are 8 prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be assigned to the WDT module.

The prescaler is not readable or writable. When assigned to the Timer0 module, all instructions writing to the TMR0 register will clear the prescaler.

When the prescaler is assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT.

#### 5.1.3.1 Switching Prescaler Between Timer0 and WDT Modules

As a result of having the prescaler assigned to either Timer0 or the WDT, it is possible to generate an unintended device Reset when switching prescaler values. When changing the prescaler assignment from Timer0 to the WDT module, the instruction sequence shown in Example 5-1, must be executed.

### EXAMPLE 5-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

| BANKSEL | TMR 0           |                    |

|---------|-----------------|--------------------|

| CLRWDT  | IMICO           | ,<br>;Clear WDT    |

| CLRF    | TMR 0           | ;Clear TMR0 and    |

| CLIKF   | IMRO            |                    |

|         |                 | ;prescaler         |

| BANKSEL | OPTION_REG      | ;                  |

| BSF     | OPTION_REG, PSA | ;Select WDT        |

| CLRWDT  |                 | ;                  |

|         |                 | ;                  |

| MOVLW   | b'11111000'     | ;Mask prescaler    |

| ANDWF   | OPTION_REG,W    | ;bits              |

| IORLW   | b'00000101'     | ;Set WDT prescaler |

| MOVWF   | OPTION_REG      | ;to 1:32           |

|         |                 |                    |

When changing the prescaler assignment from the WDT to the Timer0 module, the following instruction sequence must be executed (see Example 5-2).

| EXAMPLE 5-2: | CHANGING PRESCALER         |

|--------------|----------------------------|

|              | (WDT $\rightarrow$ TIMER0) |

| CLRWDT  |              | ;Clear WDT and<br>;prescaler |

|---------|--------------|------------------------------|

| DANKGET | OPTION REG   | , presearer                  |

| DANKSEL | OFIION_REG   | i                            |

| MOVLW   | b'11110000'  | ;Mask TMR0 select and        |

| ANDWF   | OPTION_REG,W | ;prescaler bits              |

| IORLW   | b'00000011'  | ;Set prescale to 1:16        |

| MOVWF   | OPTION_REG   | i                            |

#### 5.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The T0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The T0IF bit must be cleared in software. The Timer0 interrupt enable is the T0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the    |  |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|--|

|       | processor from Sleep since the timer is |  |  |  |  |  |  |

|       | frozen during Sleep.                    |  |  |  |  |  |  |

### 5.1.5 USING TIMER0 WITH AN EXTERNAL CLOCK

When Timer0 is in Counter mode, the synchronization of the T0CKI input and the Timer0 register is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, the high and low periods of the external clock source must meet the timing requirements as shown in Section 19.0 "Electrical Specifications"

| TABLE 6-1: | SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1 |

|------------|---------------------------------------------|

|------------|---------------------------------------------|

| Name   | Bit 7       | Bit 6                                                                       | Bit 5         | Bit 4          | Bit 3         | Bit 2       | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-------------|-----------------------------------------------------------------------------|---------------|----------------|---------------|-------------|--------|--------|----------------------|---------------------------------|

| CMCON1 | —           | _                                                                           | _             | —              | _             |             | T1GSS  | C2SYNC | 10                   | 10                              |

| INTCON | GIE         | PEIE                                                                        | T0IE          | INTE           | RBIE          | T0IF        | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | EEIE        | ADIE                                                                        | RCIE          | TXIE           | SSPIE         | CCP1IE      | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | EEIF        | ADIF                                                                        | RCIF          | TXIF           | SSPIF         | CCP1IF      | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| TMR1H  | Holding Reg | gister for the                                                              | Most Signific | ant Byte of th | ne 16-bit TMF | R1 Register |        |        | xxxx xxxx            | uuuu uuuu                       |

| TMR1L  | Holding Reg | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |               |                |               |             |        |        | xxxx xxxx            | uuuu uuuu                       |

| T1CON  | T1GINV      | TMR1GE                                                                      | T1CKPS1       | T1CKPS0        | T1OSCEN       | T1SYNC      | TMR1CS | TMR10N | 0000 0000            | uuuu uuuu                       |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

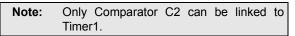

#### 8.0 COMPARATOR MODULE

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. The comparators are very useful mixed signal building blocks because they provide analog functionality independent of the program execution. The Analog Comparator module includes the following features:

- Dual comparators

- Multiple comparator configurations

- Comparator outputs are available internally/externally

- Programmable output polarity

- · Interrupt-on-change

- · Wake-up from Sleep

- Timer1 gate (count enable)

- Output synchronization to Timer1 clock input

- Programmable voltage reference

#### 8.1 Comparator Overview

A comparator is shown in Figure 8-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

This device contains two comparators as shown in Figure 8-2 and Figure 8-3. The comparators are not independently configurable.

#### 8.3 Comparator Control

The CMCON0 register (Register 8-1) provides access to the following comparator features:

- Mode selection

- · Output state

- · Output polarity

- Input switch

#### 8.3.1 COMPARATOR OUTPUT STATE

Each comparator state can always be read internally via the associated CxOUT bit of the CMCON0 register. The comparator outputs are directed to the CxOUT pins when CM<2:0> = 110. When this mode is selected, the TRIS bits for the associated CxOUT pins must be cleared to enable the output drivers.

#### 8.3.2 COMPARATOR OUTPUT POLARITY

Inverting the output of a comparator is functionally equivalent to swapping the comparator inputs. The polarity of a comparator output can be inverted by setting the CxINV bits of the CMCON0 register. Clearing CxINV results in a non-inverted output. A complete table showing the output state versus input conditions and the polarity bit is shown in Table 8-1.

### TABLE 8-1: OUTPUT STATE VS. INPUT CONDITIONS

| Input Conditions | CxINV | CxOUT |

|------------------|-------|-------|

| VIN- > VIN+      | 0     | 0     |

| VIN- < VIN+      | 0     | 1     |

| VIN- > VIN+      | 1     | 1     |

| VIN- < VIN+      | 1     | 0     |

**Note:** CxOUT refers to both the register bit and output pin.

#### 8.3.3 COMPARATOR INPUT SWITCH

The inverting input of the comparators may be switched between two analog pins or an analog input pin and and the fixed voltage reference in the following modes:

- CM<2:0> = 001 (Comparator C1 only)

- CM<2:0> = 010 (Comparators C1 and C2)

- CM<2:0> = 101 (Comparator C2 only)

In the above modes, both pins remain in Analog mode regardless of which pin is selected as the input. The CIS bit of the CMCON0 register controls the comparator input switch.

#### 8.4 Comparator Response Time

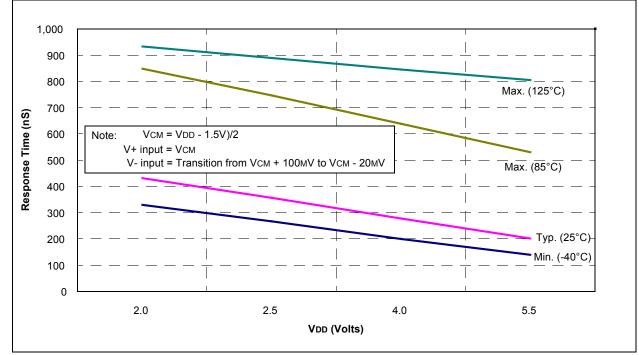

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Reference Specifications in **Section 19.0 "Electrical Specifications"** for more details.

#### 8.5 Comparator Interrupt Operation

The comparator interrupt flag is set whenever there is a change in the output value of the comparator. Changes are recognized by means of a mismatch circuit which consists of two latches and an exclusive-or gate (see Figure 8-2 and Figure 8-3). One latch is updated with the comparator output level when the CMCON0 register is read. This latch retains the value until the next read of the CMCON0 register or the occurrence of a Reset. The other latch of the mismatch circuit is updated on every Q1 system clock. A mismatch condition will occur when a comparator output change is clocked through the second latch on the Q1 clock cycle. The mismatch condition will persist, holding the CxIF bit of the PIR2 register true, until either the CMCON0 register is read or the comparator output returns to the previous state.

| Note: | A write operation to the CMCON0 register |  |  |  |

|-------|------------------------------------------|--|--|--|

|       | will also clear the mismatch condition   |  |  |  |

|       | because all writes include a read        |  |  |  |

|       | operation at the beginning of the write  |  |  |  |

|       | cycle.                                   |  |  |  |

Software will need to maintain information about the status of the comparator output to determine the actual change that has occurred.

The CxIF bit of the PIR2 register is the comparator interrupt flag. This bit must be reset in software by clearing it to '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CxIE bit of the PIE2 register and the PEIE and GIE bits of the INTCON register must all be set to enable comparator interrupts. If any of these bits are cleared, the interrupt is not enabled, although the CxIF bit of the PIR2 register will still be set if an interrupt condition occurs.

The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON0. This will end the mismatch condition. See Figures 8-6 and 8-7

- b) Clear the CxIF interrupt flag.

A persistent mismatch condition will preclude clearing the CxIF interrupt flag. Reading CMCON0 will end the mismatch condition and allow the CxIF bit to be cleared.

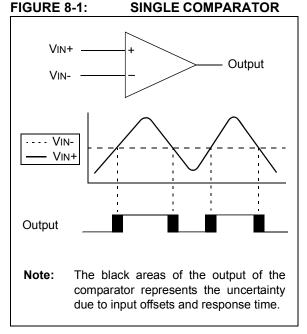

#### 9.3 AUSART Synchronous Mode

Synchronous serial communications are typically used in systems with a single master and one or more slaves. The master device contains the necessary circuitry for baud rate generation and supplies the clock for all devices in the system. Slave devices can take advantage of the master clock by eliminating the internal clock generation circuitry.

There are two signal lines in Synchronous mode: a bidirectional data line and a clock line. Slaves use the external clock supplied by the master to shift the serial data into and out of their respective receive and transmit shift registers. Since the data line is bidirectional, synchronous operation is half-duplex only. Half-duplex refers to the fact that master and slave devices can receive and transmit data but not both simultaneously. The AUSART can operate as either a master or slave device.

Start and Stop bits are not used in synchronous transmissions.

#### 9.3.1 SYNCHRONOUS MASTER MODE

The following bits are used to configure the AUSART for Synchronous Master operation:

- SYNC = 1

- CSRC = 1

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Setting the CSRC bit of the TXSTA register configures the device as a master. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the AUSART.

The LCD SEG8 and SEG9 functions must be disabled by clearing the SE8 and SE9 bits of the LCDSE1 register, if the RX/DT and TX/CK pins are shared with the LCD peripheral.

#### 9.3.1.1 Master Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a master transmits the clock on the TX/CK line. The TX/CK pin output driver is automatically enabled when the AUSART is configured for synchronous transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One clock cycle is generated for each data bit. Only as many clock cycles are generated as there are data bits.

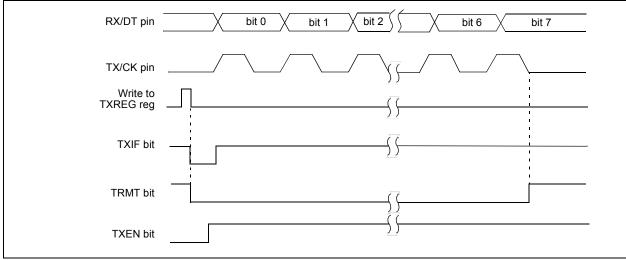

#### 9.3.1.2 Synchronous Master Transmission

Data is transferred out of the device on the RX/DT pin. The RX/DT and TX/CK pin output drivers are automatically enabled when the AUSART is configured for synchronous master transmit operation.

A transmission is initiated by writing a character to the TXREG register. If the TSR still contains all or part of a previous character the new character data is held in the TXREG until the last bit of the previous character has been transmitted. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR. The transmission of the character commences immediately following the transfer of the data to the TSR from the TXREG.

Each data bit changes on the leading edge of the master clock and remains valid until the subsequent leading clock edge.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

- 9.3.1.3 Synchronous Master Transmission Set-up:

- Initialize the SPBRG register and the BRGH bit to achieve the desired baud rate (see Section 9.2 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- 3. Disable Receive mode by clearing bits SREN and CREN.

- 4. Enable Transmit mode by setting the TXEN bit.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in the TX9D bit.

- 8. Start transmission by loading data to the TXREG register.

#### FIGURE 9-7: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

#### TABLE 9-6: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name   | Bit 7                             | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1     | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-----------------------------------|--------|--------|--------|--------|--------|-----------|-----------|----------------------|---------------------------------|

| INTCON | GIE                               | PEIE   | T0IE   | INTE   | RBIE   | T0IF   | INTF      | RBIF      | 0000 000x            | 0000 000x                       |

| LCDCON | LCDEN                             | SLPEN  | WERR   | VLCDEN | CS1    | CS0    | LMUX1     | LMUX0     | 0001 0011            | 0001 0011                       |

| LCDSE1 | SE15                              | SE14   | SE13   | SE12   | SE11   | SE10   | SE9       | SE8       | 0000 0000            | 0000 0000                       |

| PIE1   | EEIE                              | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE    | TMR1IE    | 0000 0000            | 0000 0000                       |

| PIR1   | EEIF                              | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF    | TMR1IF    | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN                              | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR      | RX9D      | x000 000x            | 0000 000x                       |

| SPBRG  | BRG7                              | BRG6   | BRG5   | BRG4   | BRG3   | BRG2   | BRG1      | BRG0      | 0000 0000            | 0000 0000                       |

| SSPCON | WCOL                              | SSPOV  | SSPEN  | CKP    | SSPM3  | SSPM2  | SSPM1     | SSPM0     | 0000 0000            | 0000 0000                       |

| TRISC  | TRISC7                            | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1    | TRISC0    | 1111 1111            | 1111 1111                       |

| TXREG  | REG AUSART Transmit Data Register |        |        |        |        |        | 0000 0000 | 0000 0000 |                      |                                 |

| TXSTA  | CSRC                              | TX9    | TXEN   | SYNC   | _      | BRGH   | TRMT      | TX9D      | 0000 -010            | 0000 -010                       |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Master Transmission.

#### 10.4 LCD Multiplex Types

The LCD driver module can be configured into one of four multiplex types:

- Static (only COM0 is used)

- 1/2 multiplex (COM<1:0> are used)

- 1/3 multiplex (COM<2:0> are used)

- 1/4 multiplex (COM<3:0> are used)

The LMUX<1:0> bit setting of the LCDCON register decides the function of RB5, RA2 or either RA3 or RD0 pins (see Table 10-2 for details).

If the pin is a digital I/O, the corresponding TRIS bit controls the data direction. If the pin is a COM drive, then the TRIS setting of that pin is overridden.

| Note: | On a Power-on Reset, the LMUX<1:0>    |

|-------|---------------------------------------|

|       | bits of the LCDCON register are '11'. |

#### TABLE 10-2: RA3/RD0, RA2, RB5 FUNCTION

| Multiplex | LMUX<br><1:0> | RA3/RD0 <sup>(1)</sup> | RA2           | RB5          |

|-----------|---------------|------------------------|---------------|--------------|

| Static    | 00            | Digital I/O            | Digital I/O   | Digital I/O  |

| 1/2       | 01            | Digital I/O            | Digital I/O   | COM1 Driver  |

| 1/3       | 10            | Digital I/O            | COM2 Driver   | COM1 Driver  |

| 1/4       | 11            | COM3 Driver            | COM2 Driver   | COM1 Driver  |

| Note 1    | RA3 for P     | IC16E913/916           | RD0 for PIC16 | F914/917 and |

Note 1: RA3 for PIC16F913/916, RD0 for PIC16F914/917 and PIC16F946

#### 10.5 Segment Enables

The LCDSEn registers are used to select the pin function for each segment pin. The selection allows each pin to operate as either an LCD segment driver or as one of the pin's alternate functions. To configure the pin as a segment pin, the corresponding bits in the LCDSEn registers must be set to '1'.

If the pin is a digital I/O, the corresponding TRIS bit controls the data direction. Any bit set in the LCDSEn registers overrides any bit settings in the corresponding TRIS register.

| Note: | On a Power-on Reset, these pins are |  |  |  |

|-------|-------------------------------------|--|--|--|

|       | configured as digital I/O.          |  |  |  |

#### 10.6 Pixel Control

The LCDDATAx registers contain bits which define the state of each pixel. Each bit defines one unique pixel.

Register 10-4 shows the correlation of each bit in the LCDDATAx registers to the respective common and segment signals.

Any LCD pixel location not being used for display can be used as general purpose RAM.

#### 10.7 LCD Frame Frequency

The rate at which the COM and SEG outputs change is called the LCD frame frequency.

#### TABLE 10-3: FRAME FREQUENCY FORMULAS

| Multiplex | Frame Frequency =                    |

|-----------|--------------------------------------|

| Static    | Clock source/(4 x 1 x (LP<3:0> + 1)) |

| 1/2       | Clock source/(2 x 2 x (LP<3:0> + 1)) |

| 1/3       | Clock source/(1 x 3 x (LP<3:0> + 1)) |

| 1/4       | Clock source/(1 x 4 x (LP<3:0> + 1)) |

| NL C      |                                      |

Note: Clock source is Fosc/8192, T1OSC/32 or LFINTOSC/32.

# TABLE 10-4:APPROXIMATE FRAME<br/>FREQUENCY (IN Hz) USING<br/>Fosc @ 8 MHz, TIMER1 @<br/>32.768 kHz OR LFINTOSC

| LP<3:0> | Static | 1/2 | 1/3 | 1/4 |

|---------|--------|-----|-----|-----|

| 2       | 85     | 85  | 114 | 85  |

| 3       | 64     | 64  | 85  | 64  |

| 4       | 51     | 51  | 68  | 51  |

| 5       | 43     | 43  | 57  | 43  |

| 6       | 37     | 37  | 49  | 37  |

| 7       | 32     | 32  | 43  | 32  |

#### **10.11 Configuring the LCD Module**

The following is the sequence of steps to configure the LCD module.

- 1. Select the frame clock prescale using bits LP<3:0> of the LCDPS register.

- 2. Configure the appropriate pins to function as segment drivers using the LCDSEn registers.

- 3. Configure the LCD module for the following using the LCDCON register:

- Multiplex and Bias mode, bits LMUX<1:0>

- Timing source, bits CS<1:0>

- Sleep mode, bit SLPEN

- 4. Write initial values to pixel data registers, LCDDATA0 through LCDDATA11 (LCDDATA23 on PIC16F946).

- 5. Clear LCD Interrupt Flag, LCDIF bit of the PIR2 register and if desired, enable the interrupt by setting bit LCDIE of the PIE2 register.

- 6. Enable bias voltage pins (VLCD<3:1>) by setting bit VLCDEN of the LCDCON register.

- 7. Enable the LCD module by setting bit LCDEN of the LCDCON register.

#### 10.12 Disabling the LCD Module

To disable the LCD module, write all '0's to the LCDCON register.

#### 10.13 LCD Current Consumption

When using the LCD module the current consumption consists of the following three factors:

- 1. The oscillator selected

- 2. The LCD bias source

- 3. The current required to charge the LCD segments

The current consumption of just the LCD module can be considered negligible compared to these other factors.

The oscillator selected:

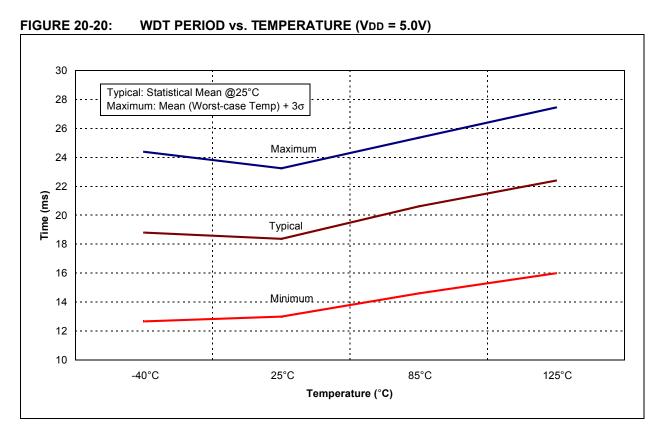

For LCD operation during Sleep either the T1oc or the LFINTOSC sources need to be used as the main system oscillator may be disabled during Sleep. During Sleep the LFINTOSC current consumption is given by electrical parameter D021, where the LFINTOSC use the same internal oscillator circuitry as the Watchdog Timer.

The LCD bias source:

The LCD bias source, typically an external resistor ladder which will have its own current draw.

The current required to charge the LCD segments:

The LCD segments which can be modeled as capacitors which must be both charged and discharged every frame. The size of the LCD segment and its technology determines the segment's capacitance.

#### 12.3 A/D Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 12-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 12-4. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed),

an A/D acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 12-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

#### EQUATION 12-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature = 50°C and external impedance of 10k Ω 5.0V VDD

$$\begin{aligned}

TACQ &= Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient \\

&= TAMP + TC + TCOFF \\

&= 2\mu s + TC + [(Temperature - 25°C)(0.05\mu s/°C)]

\end{aligned}$$

The value for TC can be approximated with the following equations:

$$\begin{aligned}

V_{APPLIED} \left( 1 - \frac{1}{(2^{n+1}) - 1} \right) &= V_{CHOLD} \qquad ;[1] V_{CHOLD} charged to within 1/2 lsb \\

V_{APPLIED} \left( 1 - e^{\frac{-TC}{RC}} \right) &= V_{CHOLD} \qquad ;[2] V_{CHOLD} charge response to V_{APPLIED} \\

V_{APPLIED} \left( 1 - e^{\frac{-TC}{RC}} \right) &= V_{APPLIED} \left( 1 - \frac{1}{(2^{n+1}) - 1} \right) \qquad ;combining [1] and [2] \\

Note: Where n = number of bits of the ADC. \\

Solving for TC: \\

TC &= -CHOLD(RIC + RSS + RS) ln(1/2047) \\

&= -10pF(1k\Omega + 7k\Omega + 10k\Omega) ln(0.0004885) \\

&= 1.37\mu s \\

Therefore: \\

TACQ &= 2\mu s + 1.37\mu s + [(50°C - 25°C)(0.05\mu s/°C)] \\

&= 4.67\mu s

\end{aligned}$$

**Note 1:** The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

#### 14.3 Enabling SPI I/O

To enable the serial port, SSP Enable bit SSPEN of the SSPCON register must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSPCON registers and then set the SSPEN bit. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, their data direction bits (in the TRISA and TRISC registers) should be set as follows:

- TRISC<7> bit must be set

- SDI is automatically controlled by the SPI module

- SDO must have TRISC<4> bit cleared

- SCK (Master mode) must have TRISC<6> bit cleared

- SCK (Slave mode) must have TRISC<6> bit set

- If enabled, SS must have TRISA<5> bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRISA and TRISC) registers to the opposite value.

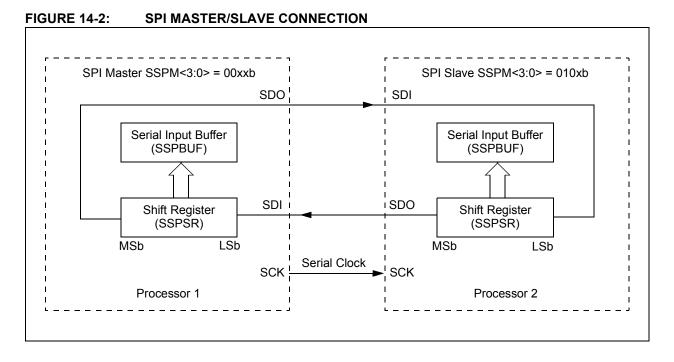

#### 14.4 Typical Connection

Figure 14-2 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge and latched on the opposite edge of the clock. Both processors should be programmed to the same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- · Master sends data Slave sends dummy data

- · Master sends data Slave sends data

- · Master sends dummy data Slave sends data

#### 15.3.1 PWM PERIOD

The PWM period is specified by the PR2 register of Timer2. The PWM period can be calculated using the formula of Equation 15-1.

#### EQUATION 15-1: PWM PERIOD

$PWM Period = [(PR2) + 1] \bullet 4 \bullet TOSC \bullet$ (TMR2 Prescale Value) Note: TOSC = 1/FOSC

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCPx pin is set. (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM duty cycle is latched from CCPRxL into CCPRxH.

| Note: | The Timer2 postscaler (see Section 7.1 |

|-------|----------------------------------------|

|       | "Timer2 Operation") is not used in the |

|       | determination of the PWM frequency.    |

#### 15.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to multiple registers: CCPRxL register and CCPx<1:0> bits of the CCPxCON register. The CCPRxL contains the eight MSbs and the CCPx<1:0> bits of the CCPxCON register contain the two LSbs. CCPRxL and CCPx<1:0> bits of the CCPxCON register can be written to at any time. The duty cycle value is not latched into CCPRxH until after the period completes (i.e., a match between PR2 and TMR2 registers occurs). While using the PWM, the CCPRxH register is read-only.

Equation 15-2 is used to calculate the PWM pulse width.

Equation 15-3 is used to calculate the PWM duty cycle ratio.

#### EQUATION 15-2: PULSE WIDTH

$Pulse Width = (CCPRxL:CCPxCON < 5:4>) \bullet$

TOSC • (TMR2 Prescale Value)

#### EQUATION 15-3: DUTY CYCLE RATIO

$$Duty Cycle Ratio = \frac{(CCPRxL:CCPxCON < 5:4>)}{4(PR2 + 1)}$$

The CCPRxH register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

The 8-bit timer TMR2 register is concatenated with either the 2-bit internal system clock (FOSC), or 2 bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

When the 10-bit time base matches the CCPRxH and 2-bit latch, then the CCPx pin is cleared (see Figure 15-3).

| SUBWF            | Subtract W from f                                                                                                                                                                          |                                       |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBWF f,d                                                                                                                                                                 |                                       |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                                          |                                       |  |  |  |

| Operation:       | (f) - (W) $\rightarrow$ (                                                                                                                                                                  | (f) - (W) $\rightarrow$ (destination) |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                   |                                       |  |  |  |

| Description:     | Subtract (2's complement method)<br>W register from register 'f'. If 'd' is<br>'0', the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f. |                                       |  |  |  |

|                  | C = 0                                                                                                                                                                                      | W > f                                 |  |  |  |

|                  | C = 1                                                                                                                                                                                      | $W \leq f$                            |  |  |  |

DC = 0

DC = 1

W<3:0> > f<3:0> W<3:0> ≤ f<3:0>

| XORLW            | Exclusive OR literal with W                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                                   |

| Operands:        | $0 \le k \le 255$                                                                                                          |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                              |

| Status Affected: | Z                                                                                                                          |

| Description:     | The contents of the W register<br>are XOR'ed with the eight-bit<br>literal 'k'. The result is placed in<br>the W register. |

| SWAPF            | Swap Nibbles in f                                                                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                        |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                |

| Status Affected: | None                                                                                                                                                                   |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in register 'f'. |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in \left[0,1\right] \end{array}$                                                                                                          |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |

| Status Affected: | Z                                                                                                                                                                               |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |

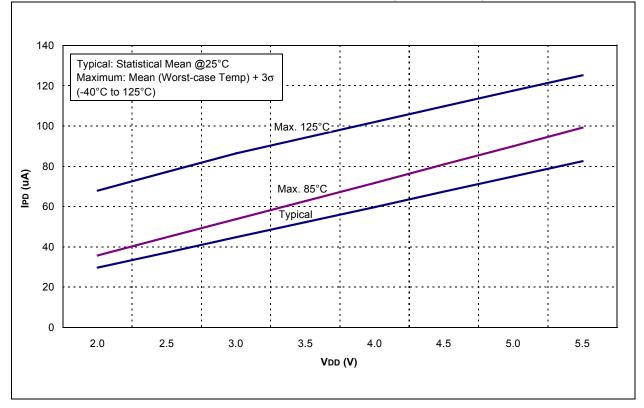

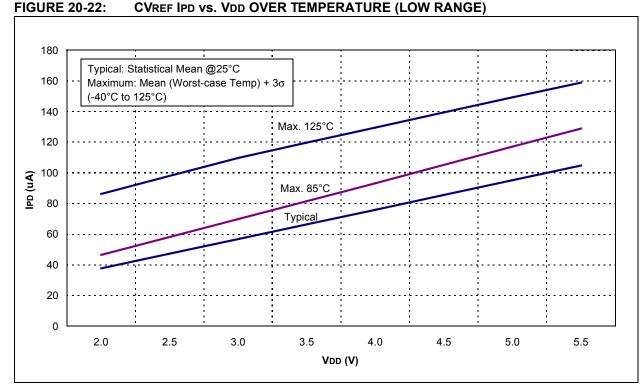

FIGURE 20-21: CVREF IPD vs. VDD OVER TEMPERATURE (HIGH RANGE)

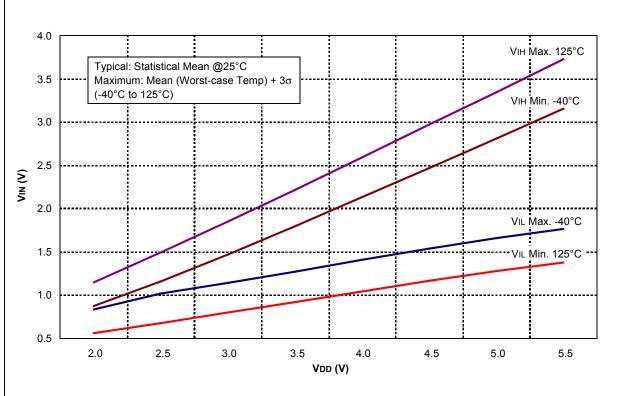

FIGURE 20-30: SCHMITT TRIGGER INPUT THRESHOLD VIN vs. VDD OVER TEMPERATURE

#### 21.0 PACKAGING INFORMATION

#### 21.1 Package Marking Information

28-Lead SPDIP

#### 40-Lead PDIP

### PIC16F913 -I/SP @3 0710017

#### Example

Example

#### 28-Lead QFN

Example

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |

|--------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | be carrie                                | nt the full Microchip part number cannot be marked on one line, it will d over to the next line, thus limiting the number of available s for customer-specific information.                                                                                                                                                                                                    |

\* Standard PIC<sup>®</sup> device marking consists of Microchip part number, year code, week code and traceability code. For PIC<sup>®</sup> device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

#### 21.2 Package Details

The following sections give the technical details of the packages.

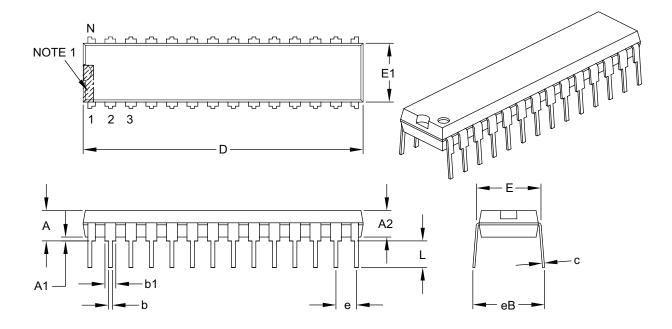

#### 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units          |          | INCHES |       |

|----------------------------|----------------|----------|--------|-------|

| Dir                        | mension Limits | MIN      | NOM    | MAX   |

| Number of Pins             | N              | 28       |        |       |

| Pitch                      | е              | .100 BSC |        |       |

| Top to Seating Plane       | А              | -        | -      | .200  |

| Molded Package Thickness   | A2             | .120     | .135   | .150  |

| Base to Seating Plane      | A1             | .015     | -      | -     |

| Shoulder to Shoulder Width | E              | .290     | .310   | .335  |

| Molded Package Width       | E1             | .240     | .285   | .295  |

| Overall Length             | D              | 1.345    | 1.365  | 1.400 |

| Tip to Seating Plane       | L              | .110     | .130   | .150  |

| Lead Thickness             | С              | .008     | .010   | .015  |

| Upper Lead Width           | b1             | .040     | .050   | .070  |

| Lower Lead Width           | b              | .014     | .018   | .022  |

| Overall Row Spacing §      | eB             | -        | -      | .430  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

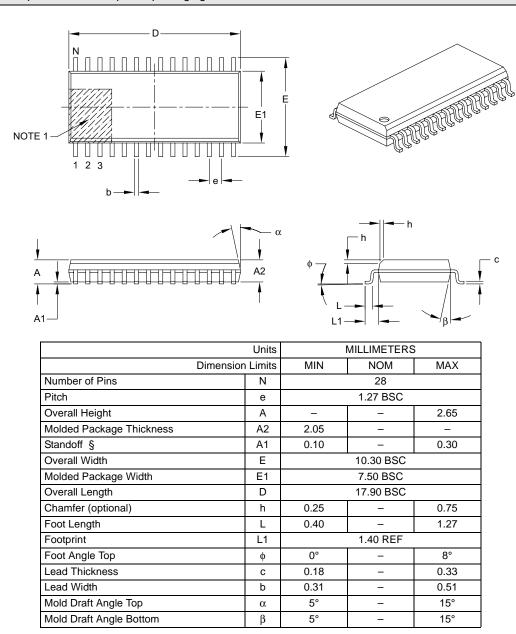

#### 28-Lead Plastic Small Outline (SO) – Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-052B

Associated Registers

#### INDEX

Α

| A/D                                                                 |

|---------------------------------------------------------------------|

| Specifications                                                      |

| Absolute Maximum Ratings                                            |

| AC Characteristics                                                  |

| Industrial and Extended                                             |

| Load Conditions                                                     |

| ACK pulse                                                           |

| ADC                                                                 |

| Associated registers                                                |

| Block Diagram                                                       |

| Calculating Acquisition Time                                        |

| Channel Selection 176                                               |

| Configuration176                                                    |

| Configuring Interrupt                                               |

| Conversion Clock                                                    |

| Conversion Procedure179<br>Internal Sampling Switch (Rss) Impedance |

| Interrupts                                                          |

| Operation                                                           |

| Operation During Sleep                                              |

| Port Configuration                                                  |

| Reference Voltage (VREF)176                                         |

| Result Formatting                                                   |

| Source Impedance                                                    |

| Special Event Trigger 178                                           |

| Starting an A/D Conversion178                                       |

| ADCON0 Register                                                     |

| ADCON1 Register                                                     |

| Addressable Universal Synchronous                                   |

| Asynchronous Receiver Transmitter (AUSART) 121                      |

| ADRESH Register (ADFM = 0)                                          |

| ADRESH Register (ADFM = 1)                                          |

| ADRESL Register (ADFM = 0)                                          |

| ADRESL Register (ADFM = 1)                                          |

| Analog-to-Digital Converter. See ADC                                |

| ANSEL Register                                                      |

| Assembler                                                           |

| MPASM Assembler                                                     |

| AUSART                                                              |

| Associated Registers                                                |

| Baud Rate Generator                                                 |

| Asynchronous Mode 123                                               |

| Associated Registers                                                |

| Receive                                                             |

| Transmit                                                            |

| Baud Rate Generator (BRG)                                           |

| Receiver                                                            |

| Setting up 9-bit Mode with Address Detect 128                       |

| Transmitter                                                         |

| Baud Rate Error, Calculating                                        |

| Baud Rates, Asynchronous Modes                                      |

| Formulas                                                            |

| High Baud Rate Select (BRGH Bit)                                    |

| Synchronous Master Mode                                             |

| Associated Registers                                                |

| Receive                                                             |

| Transmit136                                                         |

| Reception137                                                        |

| Transmission 135                                                    |

| Synchronous Slave Mode                                              |

| Receive 1                                 | 40 |

|-------------------------------------------|----|

| Transmit1                                 | 39 |

| Reception 1                               | 40 |

| Transmission 1                            | 39 |

| В                                         |    |

| -                                         |    |

| BF bit 1                                  |    |

| Block Diagram of RF                       | 83 |

| Block Diagrams                            |    |

| (CCP) Capture Mode Operation 2            |    |

| ADC 1                                     |    |

| ADC Transfer Function 1                   |    |

| Analog Input Model 111, 1                 |    |

| AUSART Receive 1                          |    |

| AUSART Transmit 1                         |    |

| CCP PWM                                   |    |

| Clock Source                              |    |

| Comparator 1 1                            |    |

| Comparator 21                             |    |

| Comparator Modes 1                        |    |

| Compare2                                  |    |

| Crystal Operation                         |    |

| External RC Mode                          |    |

| Fail-Safe Clock Monitor (FSCM)            |    |

| In-Circuit Serial Programming Connections |    |

| Interrupt Logic 2                         |    |

| LCD Clock Generation 1                    |    |

| LCD Driver Module 1                       |    |

| LCD Resistor Ladder Connection 1          |    |

| MCLR Circuit 2                            |    |

| On-Chip Reset Circuit                     |    |

| PIC16F913/916                             |    |

| PIC16F914/917                             |    |

| PIC16F946                                 |    |

| RA0 Pin                                   |    |

| RA1 Pin                                   |    |

| RA2 Pin                                   |    |

| RA3 Pin                                   |    |

| RA4 Pin                                   |    |

| RA5 Pin                                   |    |

| RA6 Pin                                   |    |

| RA7 Pin                                   |    |

| RB Pins                                   |    |

| RB4 Pin                                   |    |

| RB5 Pin                                   |    |

| RB6 Pin                                   |    |

| RB7 Pin                                   |    |

| RC0 Pin                                   |    |

| RC1 Pin                                   |    |

| RC2 Pin                                   |    |

| RC3 Pin                                   |    |

| RC4 Pin                                   |    |

| RC5 Pin                                   |    |

| RC6 Pin                                   |    |

| RC7 Pin                                   |    |

| RD Pins                                   |    |

| RD0 Pin                                   |    |

| RD1 Pin                                   |    |

| RD2 Pin                                   |    |

| RE Pins                                   |    |

| RE Pins                                   |    |

| Resonator Operation                       |    |

| RF Pins                                   | 83 |