Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                               |

| Number of I/O              | 24                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 352 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 5x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 28-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f916-i-so |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

#### 2.2.2.7 PIR2 Register

The PIR2 register contains the interrupt flag bits, as shown in Register 2-7.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### REGISTER 2-7: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | R/W-0 | U-0 | R/W-0                 |

|-------|-------|-------|-------|-----|-------|-----|-----------------------|

| OSFIF | C2IF  | C1IF  | LCDIF | —   | LVDIF | —   | CCP2IF <sup>(1)</sup> |

| bit 7 |       |       |       |     |       |     | bit 0                 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | OSFIF: Oscillator Fail Interrupt Flag bit                                                                                                                  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = System oscillator failed, clock input has changed to INTOSC (must be cleared in software)</li> <li>0 = System clock operating</li> </ul>      |

| bit 6   | C2IF: Comparator C2 Interrupt Flag bit                                                                                                                     |

|         | <ul> <li>1 = Comparator output (C2OUT bit) has changed (must be cleared in software)</li> <li>0 = Comparator output (C2OUT bit) has not changed</li> </ul> |

| bit 5   | C1IF: Comparator C1 Interrupt Flag bit                                                                                                                     |

|         | <ul> <li>1 = Comparator output (C1OUT bit) has changed (must be cleared in software)</li> <li>0 = Comparator output (C1OUT bit) has not changed</li> </ul> |

| bit 4   | LCDIF: LCD Module Interrupt bit                                                                                                                            |

|         | 1 = LCD has generated an interrupt                                                                                                                         |

|         | 0 = LCD has not generated an interrupt                                                                                                                     |

| bit 3   | Unimplemented: Read as '0'                                                                                                                                 |

| bit 2   | LVDIF: Low Voltage Detect Interrupt Flag bit                                                                                                               |

|         | 1 = LVD has generated an interrupt                                                                                                                         |

|         | 0 = LVD has not generated an interrupt                                                                                                                     |

| bit 1   | Unimplemented: Read as '0'                                                                                                                                 |

| bit 0   | CCP2IF: CCP2 Interrupt Flag bit <sup>(1)</sup>                                                                                                             |

|         | Capture Mode:                                                                                                                                              |

|         | <ul> <li>1 = A TMR1 register capture occurred (must be cleared in software)</li> <li>0 = No TMR1 register capture occurred</li> </ul>                      |

|         | Compare Mode:                                                                                                                                              |

|         | <ul> <li>1 = A TMR1 register compare match occurred (must be cleared in software)</li> <li>0 = No TMR1 register compare match occurred</li> </ul>          |

|         | PWM mode:                                                                                                                                                  |

|         | Unused in this mode                                                                                                                                        |

| Note 1: | PIC16F914/PIC16F917/PIC16F946 only.                                                                                                                        |

#### 3.6 **PORTD and TRISD Registers**

PORTD is an 8-bit port with Schmitt Trigger input buffers. Each pin is individually configured as an input or output. PORTD is only available on the PIC16F914/917 and PIC16F946.

#### EXAMPLE 3-4: INITIALIZING PORTD

| BANKSEL PORTD | ;                      |

|---------------|------------------------|

| CLRF PORTD    | ;Init PORTD            |

| BANKSEL TRISD | ;                      |

| MOVLW OFF     | ;Set RD<7:0> as inputs |

| MOVWF TRISD   | ;                      |

|               |                        |

### REGISTER 3-10: PORTD: PORTD REGISTER

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| RD7   | RD6   | RD5   | RD4   | RD3   | RD2   | RD1   | RD0   |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-0 RD<7:0>: PORTD I/O Pin bits

1 = Port pin is >VIH min.

0 = Port pin is <VIL max.

#### REGISTER 3-11: TRISD: PORTD TRI-STATE REGISTER

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-0 TRISD<7:0>: PORTD Tri-State Control bits

1 = PORTD pin configured as an input (tri-stated)

0 = PORTD pin configured as an output

#### 3.6.1 PIN DESCRIPTIONS AND DIAGRAMS

Each PORTD pin is multiplexed with other functions. The pins and their combined functions are briefly described here. For specific information about individual functions such as the Comparator or the ADC, refer to the appropriate section in this data sheet.

#### 3.6.1.1 RD0/COM3

Figure 3-22 shows the diagram for this pin. The RD0 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog output for the LCD

# 3.6.1.2 RD1

Figure 3-23 shows the diagram for this pin. The RD1 pin is configurable to function as one of the following:

a general purpose I/O

#### 3.6.1.3 RD2/CCP2

Figure 3-24 shows the diagram for this pin. The RD2 pin is configurable to function as one of the following:

- a general purpose I/O

- a Capture input, Compare output or PWM output

#### 3.6.1.4 RD3/SEG16

Figure 3-25 shows the diagram for this pin. The RD3 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog output for the LCD

#### 3.6.1.5 RD4/SEG17

Figure 3-25 shows the diagram for this pin. The RD4 pin is configurable to function as one of the following:

- · a general purpose I/O

- an analog output for the LCD

#### 3.6.1.6 RD5/SEG18

Figure 3-25 shows the diagram for this pin. The RD5 pin is configurable to function as one of the following:

- a general purpose I/O

- · an analog output for the LCD

# 3.6.1.7 RD6/SEG19

Figure 3-25 shows the diagram for this pin. The RD6 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog output for the LCD

#### 3.6.1.8 RD7/SEG20

Figure 3-25 shows the diagram for this pin. The RD7 pin is configurable to function as one of the following:

- a general purpose I/O

- · an analog output for the LCD

#### 4.5.2.1 OSCTUNE Register

The HFINTOSC is factory calibrated but can be adjusted in software by writing to the OSCTUNE register (Register 4-2).

The default value of the OSCTUNE register is '0'. The value is a 5-bit two's complement number.

When the OSCTUNE register is modified, the HFINTOSC frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

OSCTUNE does not affect the LFINTOSC frequency. Operation of features that depend on the LFINTOSC clock source frequency, such as the Power-up Timer (PWRT), Watchdog Timer (WDT), Fail-Safe Clock Monitor (FSCM) and peripherals, are *not* affected by the change in frequency.

# **REGISTER 4-2:** OSCTUNE: OSCILLATOR TUNING REGISTER

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | TUN4  | TUN3  | TUN2  | TUN1  | TUN0  |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:    |                                 |                              |                                 |                    |  |

|------------|---------------------------------|------------------------------|---------------------------------|--------------------|--|

| R = Reada  | ble bit                         | W = Writable bit             | U = Unimplemented bit           | , read as '0'      |  |

| -n = Value | at POR                          | '1' = Bit is set             | '0' = Bit is cleared            | x = Bit is unknown |  |

| bit 7-5    | Unimple                         | mented: Read as '0'          |                                 |                    |  |

| bit 4-0    | TUN<4:0>: Frequency Tuning bits |                              |                                 |                    |  |

|            | 01111 =                         | Maximum frequency            |                                 |                    |  |

|            | 01110 =                         |                              |                                 |                    |  |

|            | •                               |                              |                                 |                    |  |

|            | •                               |                              |                                 |                    |  |

|            | •                               |                              |                                 |                    |  |

|            | 00001 =                         |                              |                                 |                    |  |

|            | 00000 =                         | Oscillator module is running | at the factory-calibrated frequ | ency.              |  |

|            | 11111 =                         |                              |                                 |                    |  |

|            | •                               |                              |                                 |                    |  |

•

10000 = Minimum frequency

# 10.4 LCD Multiplex Types

The LCD driver module can be configured into one of four multiplex types:

- Static (only COM0 is used)

- 1/2 multiplex (COM<1:0> are used)

- 1/3 multiplex (COM<2:0> are used)

- 1/4 multiplex (COM<3:0> are used)

The LMUX<1:0> bit setting of the LCDCON register decides the function of RB5, RA2 or either RA3 or RD0 pins (see Table 10-2 for details).

If the pin is a digital I/O, the corresponding TRIS bit controls the data direction. If the pin is a COM drive, then the TRIS setting of that pin is overridden.

| Note: | On a Power-on Reset, the LMUX<1:0>    |

|-------|---------------------------------------|

|       | bits of the LCDCON register are '11'. |

#### TABLE 10-2: RA3/RD0, RA2, RB5 FUNCTION

| Multiplex | LMUX<br><1:0> | RA3/RD0 <sup>(1)</sup> | RA2           | RB5          |  |

|-----------|---------------|------------------------|---------------|--------------|--|

| Static    | 00            | Digital I/O            | Digital I/O   | Digital I/O  |  |

| 1/2       | 01            | Digital I/O            | Digital I/O   | COM1 Driver  |  |

| 1/3       | 10            | Digital I/O            | COM2 Driver   | COM1 Driver  |  |

| 1/4       | 11            | COM3 Driver            | COM2 Driver   | COM1 Driver  |  |

| Note 1    | RA3 for P     | IC16E913/916           | RD0 for PIC16 | F914/917 and |  |

Note 1: RA3 for PIC16F913/916, RD0 for PIC16F914/917 and PIC16F946

# 10.5 Segment Enables

The LCDSEn registers are used to select the pin function for each segment pin. The selection allows each pin to operate as either an LCD segment driver or as one of the pin's alternate functions. To configure the pin as a segment pin, the corresponding bits in the LCDSEn registers must be set to '1'.

If the pin is a digital I/O, the corresponding TRIS bit controls the data direction. Any bit set in the LCDSEn registers overrides any bit settings in the corresponding TRIS register.

| Note: | On a Power-on Reset, these pins are |  |

|-------|-------------------------------------|--|

|       | configured as digital I/O.          |  |

# 10.6 Pixel Control

The LCDDATAx registers contain bits which define the state of each pixel. Each bit defines one unique pixel.

Register 10-4 shows the correlation of each bit in the LCDDATAx registers to the respective common and segment signals.

Any LCD pixel location not being used for display can be used as general purpose RAM.

# 10.7 LCD Frame Frequency

The rate at which the COM and SEG outputs change is called the LCD frame frequency.

#### TABLE 10-3: FRAME FREQUENCY FORMULAS

| Multiplex | Frame Frequency =                    |

|-----------|--------------------------------------|

| Static    | Clock source/(4 x 1 x (LP<3:0> + 1)) |

| 1/2       | Clock source/(2 x 2 x (LP<3:0> + 1)) |

| 1/3       | Clock source/(1 x 3 x (LP<3:0> + 1)) |

| 1/4       | Clock source/(1 x 4 x (LP<3:0> + 1)) |

| NL C      |                                      |

Note: Clock source is Fosc/8192, T1OSC/32 or LFINTOSC/32.

# TABLE 10-4:APPROXIMATE FRAME<br/>FREQUENCY (IN Hz) USING<br/>Fosc @ 8 MHz, TIMER1 @<br/>32.768 kHz OR LFINTOSC

| LP<3:0> | Static | 1/2 | 1/3 | 1/4 |

|---------|--------|-----|-----|-----|

| 2       | 85     | 85  | 114 | 85  |

| 3       | 64     | 64  | 85  | 64  |

| 4       | 51     | 51  | 68  | 51  |

| 5       | 43     | 43  | 57  | 43  |

| 6       | 37     | 37  | 49  | 37  |

| 7       | 32     | 32  | 43  | 32  |

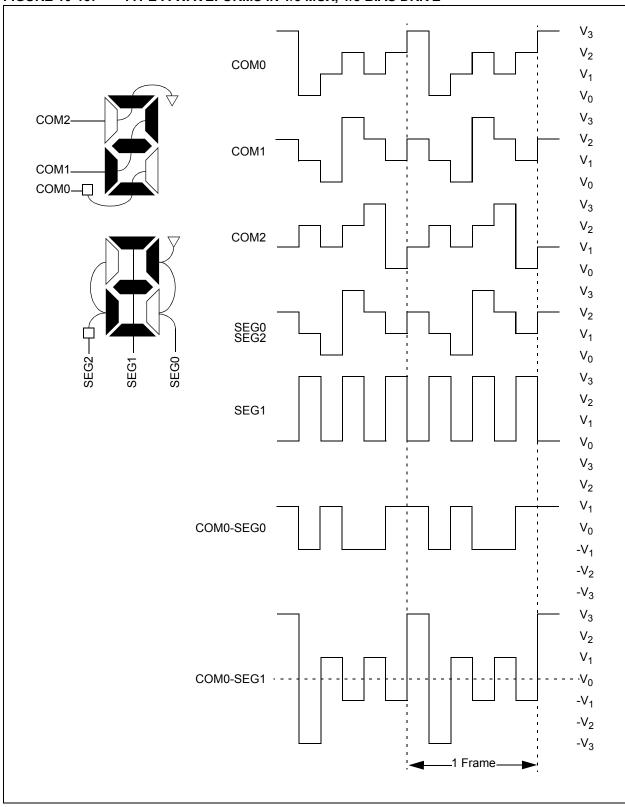

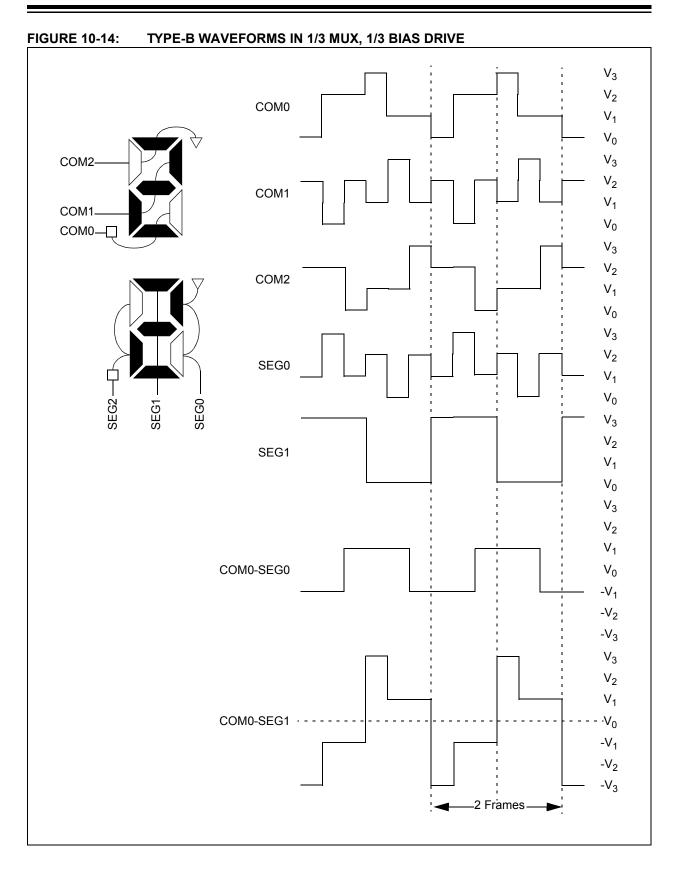

#### FIGURE 10-13: TYPE-A WAVEFORMS IN 1/3 MUX, 1/3 BIAS DRIVE

© 2007 Microchip Technology Inc.

#### 12.2.6 A/D CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- · Disable pin output driver (See TRIS register)

- · Configure pin as analog

- 2. Configure the ADC module:

- Select ADC conversion clock

- Configure voltage reference

- Select ADC input channel

- · Select result format

- Turn on ADC module

- 3. Configure ADC interrupt (optional):

- Clear ADC interrupt flag

- Enable ADC interrupt

- · Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO/DONE bit.

- 6. Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

- **Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

- 2: See Section 12.3 "A/D Acquisition Requirements".

#### EXAMPLE 12-1: A/D CONVERSION

;This code block configures the ADC ;for polling, Vdd reference, Frc clock ;and ANO input. ;

;Conversion start & polling for completion ; are included.

| ;       |             |                      |

|---------|-------------|----------------------|

| BANKSEL | ADCON1      | ;                    |

| MOVLW   | B'01110000' | ;ADC Frc clock       |

| MOVWF   | ADCON1      | ;                    |

| BANKSEL | TRISA       | ;                    |

| BSF     | TRISA,0     | ;Set RA0 to input    |

| BANKSEL | ANSEL       | ;                    |

| BSF     | ANSEL,0     | ;Set RA0 to analog   |

| BANKSEL | ADCON0      | ;                    |

| MOVLW   | B'10000001' | ;Right justify,      |

| MOVWF   | ADCON0      | ;Vdd Vref, ANO, On   |

| CALL    | SampleTime  | ;Acquisiton delay    |

| BSF     | ADCON0,GO   | ;Start conversion    |

| BTFSC   | ADCON0,GO   | ;Is conversion done? |

| GOTO    | \$-1        | ;No, test again      |

| BANKSEL | ADRESH      | ;                    |

| MOVF    | ADRESH,W    | ;Read upper 2 bits   |

| MOVWF   | RESULTHI    | ;store in GPR space  |

| BANKSEL | ADRESL      | ;                    |

| MOVF    | ADRESL,W    | ;Read lower 8 bits   |

| MOVWF   | RESULTLO    | ;Store in GPR space  |

|         |             |                      |

# 12.2.7 ADC REGISTER DEFINITIONS

The following registers are used to control the operation of the ADC.

| U-0             | R/W-0         | R/W-0            | R/W-0          | U-0                | U-0              | U-0             | U-0   |

|-----------------|---------------|------------------|----------------|--------------------|------------------|-----------------|-------|

|                 | ADCS2         | ADCS1            | ADCS0          | _                  |                  |                 | _     |

| bit 7           |               |                  |                |                    |                  |                 | bit 0 |

|                 |               |                  |                |                    |                  |                 |       |

| Legend:         |               |                  |                |                    |                  |                 |       |

| R = Readable    | bit           | W = Writable     | bit            | U = Unimpler       | nented bit, read | l as '0'        |       |

| -n = Value at F | POR           | '1' = Bit is set |                | '0' = Bit is cle   | ared             | x = Bit is unkr | nown  |

| bit 7           | Unimplemen    | ted: Read as '   | 0'             |                    |                  |                 |       |

|                 | -             |                  |                |                    |                  |                 |       |

| bit 6-4         | ADCS<2:0>:    | A/D Conversio    | n Clock Select | t bits             |                  |                 |       |

|                 | 000 = Fosc/2  | 2                |                |                    |                  |                 |       |

|                 | 001 = Fosc/8  | 3                |                |                    |                  |                 |       |

|                 | 010 = Fosc/3  | 32               |                |                    |                  |                 |       |

|                 | x11 = FRC (c) | ock derived fro  | m a dedicated  | l internal oscilla | ator = 500 kHz i | max.)           |       |

|                 | 100 = Fosc/4  |                  |                |                    |                  | - /             |       |

|                 | 101 = Fosc/1  | 6                |                |                    |                  |                 |       |

|                 | 110 = Fosc/6  |                  |                |                    |                  |                 |       |

| bit 3-0         | Unimplemen    | ted: Read as '   | 0'             |                    |                  |                 |       |

|                 |               |                  |                |                    |                  |                 |       |

#### REGISTER 12-2: ADCON1: A/D CONTROL REGISTER 1

#### REGISTER 14-1: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER

| R/W-0           | R/W-0                                                                                                                                                                    | R-0                                                                                                                                                                                | R-0                                                | R-0               | R-0                  | R-0                | R-0             |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------|----------------------|--------------------|-----------------|

| SMP             | CKE                                                                                                                                                                      | D/Ā                                                                                                                                                                                | Р                                                  | S                 | R/W                  | UA                 | BF              |

| bit 7           | -                                                                                                                                                                        |                                                                                                                                                                                    |                                                    |                   |                      |                    | bit 0           |

|                 |                                                                                                                                                                          |                                                                                                                                                                                    |                                                    |                   |                      |                    |                 |

| Legend:         | a:#                                                                                                                                                                      | M - Mritabla bit                                                                                                                                                                   |                                                    |                   | antad hit raad aa    | ·0'                |                 |

| R = Readable I  |                                                                                                                                                                          | W = Writable bit                                                                                                                                                                   |                                                    | •                 | ented bit, read as   |                    |                 |

| -n = Value at P | UR                                                                                                                                                                       | '1' = Bit is set                                                                                                                                                                   |                                                    | '0' = Bit is clea | ieu                  | x = Bit is unkno   | JWII            |

| bit 7           | SPI Master mo<br>1 = Input data s<br>0 = Input data s<br>SPI Slave mod<br>SMP must be o<br>$I^2C^{TM}$ mode:                                                             | sampled at end of sampled at middle                                                                                                                                                | data output ti<br>of data outpu<br>is used in Slav | t time (Microwire | )                    |                    |                 |

| bit 6           | CKE: SPI Cloc<br>SPI mode. CKI<br>1 = Data stable<br>0 = Data stable<br>SPI mode. CKI<br>1 = Data stable<br>0 = Data stable<br>I <sup>2</sup> C mode:<br>This bit must b | k Edge Select bit<br>$\frac{D}{2} = 0$ :<br>e on rising edge of<br>e on falling edge of<br>$\frac{D}{2} = 1$ :<br>e on falling edge of<br>e on rising edge of<br>e maintained clea | SCK (Microw<br>f SCK<br>f SCK (Microw<br>SCK       |                   |                      |                    |                 |

| bit 5           | 1 = Indicates th                                                                                                                                                         | DRESS bit (I <sup>2</sup> C m<br>nat the last byte re<br>nat the last byte re                                                                                                      | ceived or tran                                     |                   |                      |                    |                 |

| bit 4           | SSPEN is clea<br>1 = Indicates th                                                                                                                                        | ed when the SSP                                                                                                                                                                    | been detected                                      | ·                 |                      | cted last.         |                 |

| bit 3           | SSPEN is clea<br>1 = Indicates th                                                                                                                                        | ed when the SSP                                                                                                                                                                    | been detected                                      |                   |                      | cted last.         |                 |

| bit 2           | This bit holds th                                                                                                                                                        | RITE bit Information<br>ne R/W bit information<br>rt bit, Stop bit or A                                                                                                            | tion following t                                   |                   | natch. This bit is o | nly valid from the | e address match |

| bit 1           | 1 = Indicates th                                                                                                                                                         | ldress bit (10-bit l <sup>2</sup><br>nat the user needs<br>bes not need to be                                                                                                      | to update the                                      |                   | SPADD register       |                    |                 |

| bit O           | 1 = Receive co<br>0 = Receive no<br><u>Transmit (<math>l^2</math>C r</u><br>1 = Transmit in                                                                              | ind I <sup>2</sup> C modes):<br>omplete, SSPBUF<br>ot complete, SSPE                                                                                                               | UF is empty<br>JF is full                          |                   |                      |                    |                 |

#### REGISTER 14-2: SSPCON: SYNC SERIAL PORT CONTROL REGISTER

| R/W-0                     | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0                                                                                                                                                                                                           | R/W-0                                                                                                                            | R/W-0                                                                                  | R/W-0                                                                      | R/W-0                                  | R/W-0                               |  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------|-------------------------------------|--|

| WCOL                      | SSPOV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SSPEN                                                                                                                                                                                                           | CKP                                                                                                                              | SSPM3 <sup>(2)</sup>                                                                   | SSPM2 <sup>(2)</sup>                                                       | SSPM1 <sup>(2)</sup>                   | SSPM0 <sup>(2)</sup>                |  |

| bit 7                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                 |                                                                                                                                  |                                                                                        |                                                                            |                                        | bit (                               |  |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                 |                                                                                                                                  |                                                                                        |                                                                            |                                        |                                     |  |

| Legend:<br>R = Readable b | it                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | W = Writable bit                                                                                                                                                                                                |                                                                                                                                  | II = Unimplem                                                                          | ented bit, read as                                                         | ʻ <b>∩</b> '                           |                                     |  |

| -n = Value at PC          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | '1' = Bit is set                                                                                                                                                                                                |                                                                                                                                  | '0' = Bit is clea                                                                      |                                                                            | x = Bit is unkno                       |                                     |  |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                 |                                                                                                                                  |                                                                                        | leu                                                                        |                                        |                                     |  |

| bit 7                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Collision Detect bit<br>SUF register is writ                                                                                                                                                                    |                                                                                                                                  | till transmitting th                                                                   | e previous word (                                                          | must be cleared i                      | n software)                         |  |

| bit 6                     | In SPI mode:<br>1 = A new byt<br>data in SS<br>transmittin<br>tion (and t<br>0 = No overflo<br>In I <sup>2</sup> C™ mode:<br>1 = A byte is b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | received while the<br>node. SSPOV mu                                                                                                                                                                            | e the SSPBUI<br>flow can only o<br>etting overflow<br>itiated by writi<br>e SSPBUF reg                                           | occur in Slave mode<br>. In Master mode<br>ng to the SSPBU<br>gister is still hold     | ode. The user mu<br>e, the overflow bit<br>F register.<br>ing the previous | st read the SSPE<br>is not set since e | 3UF, even if only<br>each new recep |  |

| bit 5                     | SSPEN: Synchronous Serial Port Enable bit         In SPI mode:         1 = Enables serial port and configures SCK, SDO and SDI as serial port pins         0 = Disables serial port and configures these pins as I/O port pins         In I <sup>2</sup> C mode:         1 = Enables the serial port and configures the SDA and SCL pins as serial port pins         0 = Disables serial port and configures the SDA and SCL pins as serial port pins         0 = Disables serial port and configures these pins as I/O port pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                 |                                                                                                                                  |                                                                                        |                                                                            |                                        |                                     |  |

| bit 4                     | <b>CKP</b> : Clock Po<br>In SPI mode:<br>1 = Idle state fo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | or clock is a high le<br>or clock is a low le<br>ontrol                                                                                                                                                         | evel (Microwin                                                                                                                   | e default)                                                                             |                                                                            | , output                               |                                     |  |

| hit 2 0                   | 0 = Holds clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | k low (clock stretcl<br>ynchronous Seria                                                                                                                                                                        | , ,                                                                                                                              |                                                                                        | time.)                                                                     |                                        |                                     |  |

| bit 3-0                   | $\begin{array}{l} 0000 = {\rm SPI} \mbox{ Ma} \\ 0001 = {\rm SPI} \mbox{ Ma} \\ 0010 = {\rm SPI} \mbox{ Ma} \\ 0011 = {\rm SPI} \mbox{ Ma} \\ 0100 = {\rm SPI} \mbox{ SIa} \\ 0101 = {\rm SPI} \mbox{ SIa} \\ 0101 = {\rm I}^2 {\rm C} \mbox{ SIa} \\ 0111 = {\rm I}^2 {\rm C} \mbox{ SIa} \\ 1000 = {\rm Reserv} \\ 1001 = {\rm Reserv} \\ 1010 = {\rm Reserv} \\ 1011 = {\rm I}^2 {\rm C} \mbox{ Firm} \\ 1100 = {\rm Reserv} \\ 1101 = {\rm Reserv} \\ 1100 = {\rm SIa} \\ {\rm SIa} \mbox{ SIa} \mbox{ SIa} \mbox{ SIa} \mbox{ SIa} \\ {\rm SIa} \mbox{ SIa}  S$ | ster mode, clock<br>aster mode, clock<br>aster mode, clock<br>aster mode, clock<br>ave mode, clock =<br>ave mode, clock =<br>ve mode, 7-bit ad<br>ve mode, 10-bit a<br>ed<br>ed<br>ed<br>mware Controlled<br>ed | = Fosc/4<br>= Fosc/16<br>= Fosc/64<br>= TMR2 outpu<br>SCK pin. <u>SS</u><br>SCK pin. <u>SS</u><br>dress<br>ddress<br>Master mode | tt/2<br>pin control enable<br>pin control disabl<br>(slave IDLE)<br>rt and Stop bit in | ed. <del>SS</del> can be us<br>terrupts enabled                            |                                        |                                     |  |

#### 15.3.3 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is 10 bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 15-4.

#### EQUATION 15-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PR2 + 1)]}{\log(2)}$$

bits

Note: If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

| TABLE 15-3: | EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz) |

|-------------|---------------------------------------------------------|

|-------------|---------------------------------------------------------|

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

#### TABLE 15-4: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

### 15.3.4 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 15.3.5 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 4.0 "Oscillator Module (With Fail-Safe Clock Monitor)" for additional details.

#### 15.3.6 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

#### 15.3.7 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Disable the PWM pin (CCPx) output drivers by setting the associated TRIS bit.

- 2. Set the PWM period by loading the PR2 register.

- Configure the CCP module for the PWM mode by loading the CCPxCON register with the appropriate values.

- 4. Set the PWM duty cycle by loading the CCPRxL register and CCPx bits of the CCPxCON register.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR1 register.

- Set the Timer2 prescale value by loading the T2CKPS bits of the T2CON register.

- Enable Timer2 by setting the TMR2ON bit of the T2CON register.

- 6. Enable PWM output after a new PWM cycle has started:

- Wait until Timer2 overflows (TMR2IF bit of the PIR1 register is set).

- Enable the CCPx pin output driver by clearing the associated TRIS bit.

#### TABLE 15-5: SUMMARY OF REGISTERS ASSOCIATED WITH CAPTURE, COMPARE AND PWM

| Name                 | Bit 7                                                                      | Bit 6          | Bit 5        | Bit 4         | Bit 3           | Bit 2     | Bit 1   | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|----------------------|----------------------------------------------------------------------------|----------------|--------------|---------------|-----------------|-----------|---------|-----------|----------------------|---------------------------------|

| CCPxCON              | —                                                                          | _              | CCPxX        | CCPxY         | CCPxM3          | CCPxM2    | CCPxM1  | CCPxM0    | 00 0000              | 00 0000                         |

| CCPRxL               | Capture/Co                                                                 | mpare/PWN      | 1 Register X | Low Byte      |                 |           |         |           | xxxx xxxx            | uuuu uuuu                       |

| CCPRxH               | Capture/Co                                                                 | mpare/PWN      | 1 Register X | High Byte     |                 |           |         |           | xxxx xxxx            | uuuu uuuu                       |

| CMCON1               | —                                                                          | —              | —            | —             | —               | —         | T1GSS   | C2SYNC    | 10                   | 10                              |

| INTCON               | GIE                                                                        | PEIE           | T0IE         | INTE          | RBIE            | T0IF      | INTF    | RBIF      | 0000 000x            | 0000 000x                       |

| LCDCON               | LCDEN                                                                      | SLPEN          | WERR         | VLCDEN        | CS1             | CS0       | LMUX1   | LMUX0     | 0001 0011            | 0001 0011                       |

| LCDSE1               | SE15                                                                       | SE14           | SE13         | SE12          | SE11            | SE10      | SE9     | SE8       | 0000 0000            | 0000 0000                       |

| PIE1                 | EEIE                                                                       | ADIE           | RCIE         | TXIE          | SSPIE           | CCP1IE    | TMR2IE  | TMR1IE    | 0000 0000            | 0000 0000                       |

| PIE2                 | OSFIE                                                                      | C2IE           | C1IE         | LCDIE         | _               | LVDIE     | _       | CCP2IE    | 0000 -0-0            | 0000 -0-0                       |

| PIR1                 | EEIF                                                                       | ADIF           | RCIF         | TXIF          | SSPIF           | CCP1IF    | TMR2IF  | TMR1IF    | 0000 0000            | 0000 0000                       |

| PIR2                 | OSFIF                                                                      | C2IF           | C1IF         | LCDIF         | _               | LVDIF     | _       | CCP2IF    | 0000 -0-0            | 0000 -0-0                       |

| RCSTA                | SPEN                                                                       | RX9            | SREN         | CREN          | ADDEN           | FERR      | OERR    | RX9D      | 0000 000x            | 0000 000x                       |