#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                               |

| Number of I/O              | 24                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 352 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 5x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

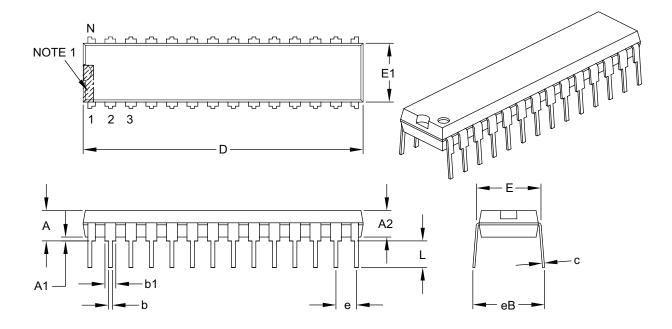

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 28-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f916-i-ss |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1-1: PIC16F91X/946 PINOUT DESCRIPTIONS (CONTINUED)

|         | Name                                                                                                                                                                                    | Function | Input<br>Type | Output<br>Type | t Description                         |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------|----------------|---------------------------------------|--|

| Vss     |                                                                                                                                                                                         | Vss      | Р             | _              | Ground reference for microcontroller. |  |

| Legend: | Legend:AN=Analog input or outputCMOS =CMOS compatible input or outputOD =Open DrainTTL=TTL compatible inputST=Schmitt Trigger input with CMOS levels P=PowerHV=High VoltageXTAL=Crystal |          |               |                |                                       |  |

| Noto 1  | • 1: COM3 is available on PA3 for the PIC16E013/016 and on PD0 for the PIC16E014/017 and PIC16E046                                                                                      |          |               |                |                                       |  |

Note 1: COM3 is available on RA3 for the PIC16F913/916 and on RD0 for the PIC16F914/917 and PIC16F946.

2: Pins available on PIC16F914/917 and PIC16F946 only.

**3:** Pins available on PIC16F946 only.

4: I<sup>2</sup>C Schmitt trigger inputs have special input levels.

### 2.3 PCL and PCLATH

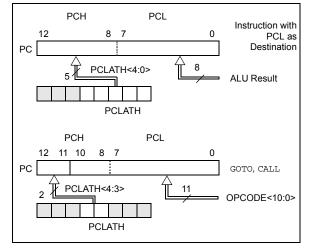

The Program Counter (PC) is 13 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 2-6 shows the two situations for the loading of the PC. The upper example in Figure 2-6 shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in Figure 2-6 shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

FIGURE 2-6: LOADING OF PC IN DIFFERENT SITUATIONS

#### 2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to the Application Note AN556, *"Implementing a Table Read"* (DS00556).

### 2.3.2 STACK

The PIC16F91X/946 family has an 8-level x 13-bit wide hardware stack (see Figures 2-1 and 2-2). The stack space is not part of either program or data space and the Stack Pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth PUSH overwrites the value that was stored from the first PUSH. The tenth PUSH overwrites the second PUSH (and so on).

- Note 1: There are no Status bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

### 2.4 Program Memory Paging

All PIC16F91X/946 devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper 2 bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is POPed off the stack. Therefore, manipulation of the PCLATH<4:3> bits is not required for the RETURN instructions (which POPs the address from the stack).

| Note: | The contents of the PCLATH register are<br>unchanged after a RETURN or RETFIE<br>instruction is executed. The user must<br>rewrite the contents of the PCLATH regis-<br>ter for any subsequent subroutine calls or<br>GOTO instructions. |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

Example 2-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that PCLATH is saved and restored by the Interrupt Service Routine (if interrupts are used).

#### EXAMPLE 2-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

|         | ORG 500h     |                                |

|---------|--------------|--------------------------------|

|         | BCF PCLATH,4 |                                |

|         | BSF PCLATH,3 | ;Select page 1<br>;(800h-FFFh) |

|         | CALL SUB1_P1 | ;Call subroutine in            |

|         | : –          | ;page 1 (800h-FFFh)            |

|         | :            |                                |

|         | ORG 900h     | ;page 1 (800h-FFFh)            |

| SUB1_P1 |              |                                |

|         | :            | ;called subroutine             |

|         |              | ;page 1 (800h-FFFh)            |

|         | :            |                                |

|         | RETURN       | ;return to                     |

|         |              | ;Call subroutine               |

|         |              | ;in page 0                     |

|         |              | ;(000h-7FFh)                   |

|         |              |                                |

| Name                  | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|-----------------------|-------|-------|--------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| LCDCON                | LCDEN | SLPEN | WERR   | VLCDEN | CS1    | CS0    | LMUX1  | LMUX0  | 0001 0011            | 0001 0011                       |

| LCDSE4 <sup>(1)</sup> | SE39  | SE38  | SE37   | SE36   | SE35   | SE34   | SE33   | SE32   | 0000 0000            | uuuu uuuu                       |

| LCDSE5 <sup>(1)</sup> | _     | _     | —      | _      | —      | —      | SE41   | SE40   | 00                   | uu                              |

| PORTG <sup>(1)</sup>  | _     | —     | RG5    | RG4    | RG3    | RG2    | RG1    | RG0    | xx xxxx              | uu uuuu                         |

| TRISG <sup>(1)</sup>  | _     | _     | TRISG5 | TRISG4 | TRISG3 | TRISG2 | TRISG1 | TRISG0 | 11 1111              | 11 1111                         |

### TABLE 3-7: SUMMARY OF REGISTERS ASSOCIATED WITH PORTG<sup>(1)</sup>

Legend:

x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTG.

Note

1:

PIC16F946 only.

#### 4.5.3 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is an uncalibrated 31 kHz internal clock source.

The output of the LFINTOSC connects to a postscaler and multiplexer (see Figure 4-1). Select 31 kHz, via software, using the IRCF<2:0> bits of the OSCCON register. See **Section 4.5.4 "Frequency Select Bits (IRCF)**" for more information. The LFINTOSC is also the frequency for the Power-up Timer (PWRT), Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The LFINTOSC is enabled by selecting 31 kHz (IRCF<2:0> bits of the OSCCON register = 000) as the system clock source (SCS bit of the OSCCON register = 1), or when any of the following are enabled:

- Two-Speed Start-up IESO bit of the Configuration Word register = 1 and IRCF<2:0> bits of the OSCCON register = 000

- Power-up Timer (PWRT)

- Watchdog Timer (WDT)

- Fail-Safe Clock Monitor (FSCM)

The LF Internal Oscillator (LTS) bit of the OSCCON register indicates whether the LFINTOSC is stable or not.

#### 4.5.4 FREQUENCY SELECT BITS (IRCF)

The output of the 8 MHz HFINTOSC and 31 kHz LFINTOSC connects to a postscaler and multiplexer (see Figure 4-1). The Internal Oscillator Frequency Select bits IRCF<2:0> of the OSCCON register select the frequency output of the internal oscillators. One of eight frequencies can be selected via software:

- 8 MHz

- 4 MHz (Default after Reset)

- 2 MHz

- 1 MHz

- 500 kHz

- 250 kHz

- 125 kHz

- 31 kHz (LFINTOSC)

| Note: | Following any Reset, the IRCF<2:0> bits of |

|-------|--------------------------------------------|

|       | the OSCCON register are set to '110' and   |

|       | the frequency selection is set to 4 MHz.   |

|       | The user can modify the IRCF bits to       |

|       | select a different frequency.              |

#### 4.5.5 HF AND LF INTOSC CLOCK SWITCH TIMING

When switching between the LFINTOSC and the HFINTOSC, the new oscillator may already be shut down to save power (see Figure 4-6). If this is the case, there is a delay after the IRCF<2:0> bits of the OSCCON register are modified before the frequency selection takes place. The LTS and HTS bits of the OSCCON register will reflect the current active status of the LFINTOSC and HFINTOSC oscillators. The timing of a frequency selection is as follows:

- 1. IRCF<2:0> bits of the OSCCON register are modified.

- 2. If the new clock is shut down, a clock start-up delay is started.

- 3. Clock switch circuitry waits for a falling edge of the current clock.

- 4. CLKOUT is held low and the clock switch circuitry waits for a rising edge in the new clock.

- CLKOUT is now connected with the new clock. LTS and HTS bits of the OSCCON register are updated as required.

- 6. Clock switch is complete.

See Figure 4-1 for more details.

If the internal oscillator speed selected is between 8 MHz and 125 kHz, there is no start-up delay before the new frequency is selected. This is because the old and new frequencies are derived from the HFINTOSC via the postscaler and multiplexer.

Start-up delay specifications are located under the oscillator parameters of **Section 19.0** "**Electrical Specifications**".

## 5.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A single software programmable prescaler is available for use with either Timer0 or the Watchdog Timer (WDT), but not both simultaneously. The prescaler assignment is controlled by the PSA bit of the Option register. To assign the prescaler to Timer0, the PSA bit must be cleared to a '0'.

There are 8 prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be assigned to the WDT module.

The prescaler is not readable or writable. When assigned to the Timer0 module, all instructions writing to the TMR0 register will clear the prescaler.

When the prescaler is assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT.

#### 5.1.3.1 Switching Prescaler Between Timer0 and WDT Modules

As a result of having the prescaler assigned to either Timer0 or the WDT, it is possible to generate an unintended device Reset when switching prescaler values. When changing the prescaler assignment from Timer0 to the WDT module, the instruction sequence shown in Example 5-1, must be executed.

## EXAMPLE 5-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

| BANKSEL | TMR 0           |                    |

|---------|-----------------|--------------------|

| CLRWDT  | IMICO           | ,<br>;Clear WDT    |

| CLRF    | TMR 0           | ;Clear TMR0 and    |

| CLIKF   | IMRO            |                    |

|         |                 | ;prescaler         |

| BANKSEL | OPTION_REG      | ;                  |

| BSF     | OPTION_REG, PSA | ;Select WDT        |

| CLRWDT  |                 | ;                  |

|         |                 | ;                  |

| MOVLW   | b'11111000'     | ;Mask prescaler    |

| ANDWF   | OPTION_REG,W    | ;bits              |

| IORLW   | b'00000101'     | ;Set WDT prescaler |

| MOVWF   | OPTION_REG      | ;to 1:32           |

|         |                 |                    |

When changing the prescaler assignment from the WDT to the Timer0 module, the following instruction sequence must be executed (see Example 5-2).

| EXAMPLE 5-2: | CHANGING PRESCALER         |

|--------------|----------------------------|

|              | (WDT $\rightarrow$ TIMER0) |

| CLRWDT  |              | ;Clear WDT and<br>;prescaler |

|---------|--------------|------------------------------|

| DANKGET | OPTION REG   | , presearer                  |

| DANKSEL | OFIION_REG   | i                            |

| MOVLW   | b'11110000'  | ;Mask TMR0 select and        |

| ANDWF   | OPTION_REG,W | ;prescaler bits              |

| IORLW   | b'00000011'  | ;Set prescale to 1:16        |

| MOVWF   | OPTION_REG   | i                            |

#### 5.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The T0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The T0IF bit must be cleared in software. The Timer0 interrupt enable is the T0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the    |

|-------|-----------------------------------------|

|       | processor from Sleep since the timer is |

|       | frozen during Sleep.                    |

## 5.1.5 USING TIMER0 WITH AN EXTERNAL CLOCK

When Timer0 is in Counter mode, the synchronization of the T0CKI input and the Timer0 register is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, the high and low periods of the external clock source must meet the timing requirements as shown in Section 19.0 "Electrical Specifications"

#### 6.7 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit of the PIR1 register is set. To enable the interrupt on rollover, you must set these bits:

- · Timer1 interrupt enable bit of the PIE1 register

- · PEIE bit of the INTCON register

- · GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

| Note: | The TMR1H:TMR1L register pair and th | е |

|-------|--------------------------------------|---|

|       | TMR1IF bit should be cleared befor   | e |

|       | enabling interrupts.                 |   |

#### 6.8 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMR1ON bit of the T1CON register must be set

- TMR1IE bit of the PIE1 register must be set

- · PEIE bit of the INTCON register must be set

The device will wake-up on an overflow and execute the next instruction. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine (0004h).

#### 6.9 Clock Source for LCD Module

The Timer1 oscillator can be used to provide a clock for the LCD module. This clock may be configured to remain running during Sleep.

For more information, see Section 10.0 "Liquid Crystal Display (LCD) Driver Module".

#### 8.2 Comparator Configuration

There are eight modes of operation for the comparator. The CM<2:0> bits of the CMCON0 register are used to select these modes as shown in Figure 8-5. I/O lines change as a function of the mode and are designated as follows:

- Analog function (A): digital input buffer is disabled

- Digital function (D): comparator digital output, overrides port function

- Normal port function (I/O): independent of comparator

The port pins denoted as "A" will read as a '0' regardless of the state of the I/O pin or the I/O control TRIS bit. Pins used as analog inputs should also have the corresponding TRIS bit set to '1' to disable the digital output driver. Pins denoted as "D" should have the corresponding TRIS bit set to '0' to enable the digital output driver.

| Note: | Comparator interrupts should be disabled |

|-------|------------------------------------------|

|       | during a Comparator mode change to       |

|       | prevent unintended interrupts.           |

#### TABLE 12-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES (VDD > 3.0V)

| ADC Clock        | Period (TAD) | Device Frequency (Fosc) |                         |                         |                         |  |  |

|------------------|--------------|-------------------------|-------------------------|-------------------------|-------------------------|--|--|

| ADC Clock Source | ADCS<2:0>    | 20 MHz                  | 8 MHz                   | 4 MHz                   | 1 MHz                   |  |  |

| Fosc/2           | 000          | 100 ns <sup>(2)</sup>   | 250 ns <sup>(2)</sup>   | 500 ns <sup>(2)</sup>   | 2.0 μs                  |  |  |

| Fosc/4           | 100          | 200 ns <sup>(2)</sup>   | 500 ns <sup>(2)</sup>   | 1.0 μs <sup>(2)</sup>   | 4.0 μs                  |  |  |

| Fosc/8           | 001          | 400 ns <sup>(2)</sup>   | 1.0 μs <sup>(2)</sup>   | 2.0 μs                  | 8.0 μs <sup>(3)</sup>   |  |  |

| Fosc/16          | 101          | 800 ns <sup>(2)</sup>   | 2.0 μs                  | 4.0 μs                  | 16.0 μs <sup>(3)</sup>  |  |  |

| Fosc/32          | 010          | 1.6 μs                  | 4.0 μs                  | 8.0 μs <sup>(3)</sup>   | 32.0 μs <sup>(3)</sup>  |  |  |

| Fosc/64          | 110          | 3.2 μs                  | 8.0 μs <sup>(3)</sup>   | 16.0 μs <sup>(3)</sup>  | 64.0 μs <sup>(3)</sup>  |  |  |

| Frc              | x11          | 2-6 μs <sup>(1,4)</sup> | 2-6 μs <sup>(1,4)</sup> | 2-6 μs <sup>(1,4)</sup> | 2-6 μs <sup>(1,4)</sup> |  |  |

**Legend:** Shaded cells are outside of recommended range.

**Note 1:** The FRC source has a typical TAD time of 4  $\mu$ s for VDD > 3.0V.

2: These values violate the minimum required TAD time.

- **3:** For faster conversion times, the selection of another clock source is recommended.

- 4: When the device frequency is greater than 1 MHz, the FRC clock source is only recommended if the conversion will be performed during Sleep.

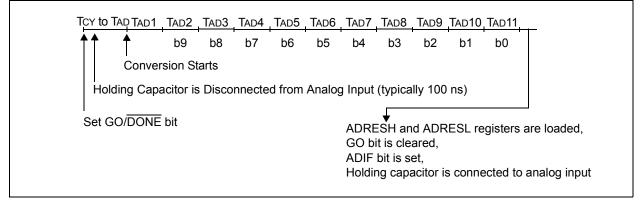

#### FIGURE 12-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

#### 12.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC interrupt flag is the ADIF bit in the PIR1 register. The ADC interrupt enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

| Note: | The ADIF bit is set at the completion of |

|-------|------------------------------------------|

|       | every conversion, regardless of whether  |

|       | or not the ADC interrupt is enabled.     |

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the global interrupt must be disabled. If the global interrupt is enabled, execution will switch to the Interrupt Service Routine.

Please see **Section 12.1.5** "Interrupts" for more information.

© 2007 Microchip Technology Inc.

| R/W-0         | R/W-0                                              | R/W-0                                                                                                                                                                                                | R/W-0         | R/W-0         | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |

|---------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|-----------------|-----------------|-------|--|--|--|--|

| ADFM          | VCFG1                                              | VCFG0                                                                                                                                                                                                | CHS2          | CHS1          | CHS0            | GO/DONE         | ADON  |  |  |  |  |

| bit 7         |                                                    |                                                                                                                                                                                                      |               | •             |                 |                 | bit   |  |  |  |  |

| Legend:       |                                                    |                                                                                                                                                                                                      |               |               |                 |                 |       |  |  |  |  |

| R = Readable  | a hit                                              | W = Writable                                                                                                                                                                                         | hit           | LI – Unimploy | mented bit, rea | ad aa 'O'       |       |  |  |  |  |

| -n = Value at |                                                    | '1' = Bit is set                                                                                                                                                                                     |               | 0 – Onimpier  |                 | x = Bit is unkn | 014/2 |  |  |  |  |

|               | PUR                                                | I = BILIS SEL                                                                                                                                                                                        |               |               | areu            |                 | JWII  |  |  |  |  |

| bit 7         | ADFM: A/D                                          | Conversion Res                                                                                                                                                                                       | ult Format Se | lect bit      |                 |                 |       |  |  |  |  |

|               | 1 = Right jus                                      |                                                                                                                                                                                                      |               |               |                 |                 |       |  |  |  |  |

|               | 0 = Left justi                                     | fied                                                                                                                                                                                                 |               |               |                 |                 |       |  |  |  |  |

| bit 6         | VCFG1: Vol                                         | tage Reference                                                                                                                                                                                       | bit           |               |                 |                 |       |  |  |  |  |

|               | 1 = VREF- pi                                       | n                                                                                                                                                                                                    |               |               |                 |                 |       |  |  |  |  |

|               | 0 <b>= V</b> SS                                    |                                                                                                                                                                                                      |               |               |                 |                 |       |  |  |  |  |

| bit 5         |                                                    | tage Reference                                                                                                                                                                                       | bit           |               |                 |                 |       |  |  |  |  |

|               | 1 = VREF+ p                                        | in                                                                                                                                                                                                   |               |               |                 |                 |       |  |  |  |  |

|               | 0 = Vss                                            |                                                                                                                                                                                                      |               |               |                 |                 |       |  |  |  |  |

| bit 4-2       |                                                    | Analog Channel                                                                                                                                                                                       | Select bits   |               |                 |                 |       |  |  |  |  |

|               | 000 = AN0<br>001 = AN1                             |                                                                                                                                                                                                      |               |               |                 |                 |       |  |  |  |  |

|               | 001 = AN1<br>010 = AN2                             |                                                                                                                                                                                                      |               |               |                 |                 |       |  |  |  |  |

|               | 011 = AN3                                          |                                                                                                                                                                                                      |               |               |                 |                 |       |  |  |  |  |

|               | 100 <b>= AN4</b>                                   |                                                                                                                                                                                                      |               |               |                 |                 |       |  |  |  |  |

|               | 101 <b>= AN5<sup>(1</sup></b>                      |                                                                                                                                                                                                      |               |               |                 |                 |       |  |  |  |  |

|               | 110 = AN6 <sup>(1</sup><br>111 = AN7 <sup>(1</sup> |                                                                                                                                                                                                      |               |               |                 |                 |       |  |  |  |  |

|               |                                                    |                                                                                                                                                                                                      | o             |               |                 |                 |       |  |  |  |  |

| bit 1         |                                                    | A/D Conversion                                                                                                                                                                                       |               |               |                 |                 |       |  |  |  |  |

|               |                                                    | <ol> <li>A/D conversion cycle in progress. Setting this bit starts an A/D conversion cycle.</li> <li>This bit is automatically cleared by hardware when the A/D conversion has completed.</li> </ol> |               |               |                 |                 |       |  |  |  |  |

|               |                                                    | version complete                                                                                                                                                                                     |               |               | e A/D convers   |                 | eu.   |  |  |  |  |

| bit 0         | ADON: ADO                                          | •                                                                                                                                                                                                    | samet in prog |               |                 |                 |       |  |  |  |  |

| ~             | 1 = ADC is e                                       |                                                                                                                                                                                                      |               |               |                 |                 |       |  |  |  |  |

|               | 0 = ADC is c                                       |                                                                                                                                                                                                      |               |               |                 |                 |       |  |  |  |  |

#### REGISTER 12-1: ADCON0: A/D CONTROL REGISTER 0

Note 1: Not available on 28-pin devices.

#### REGISTER 14-2: SSPCON: SYNC SERIAL PORT CONTROL REGISTER

| R/W-0                            | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0                                                                                                                             | R/W-0                                                                                                              | R/W-0                                                                                  | R/W-0                                                                      | R/W-0                                  | R/W-0                                   |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------|-----------------------------------------|

| WCOL                             | SSPOV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SSPEN                                                                                                                             | CKP                                                                                                                | SSPM3 <sup>(2)</sup>                                                                   | SSPM2 <sup>(2)</sup>                                                       | SSPM1 <sup>(2)</sup>                   | SSPM0 <sup>(2)</sup>                    |

| bit 7                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                   |                                                                                                                    |                                                                                        |                                                                            |                                        | bit (                                   |

| Logondy                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                   |                                                                                                                    |                                                                                        |                                                                            |                                        |                                         |

| <b>Legend:</b><br>R = Readable b | it                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | W = Writable bit                                                                                                                  |                                                                                                                    | U = Unimpleme                                                                          | ented bit, read as                                                         | ʻ0'                                    |                                         |

| -n = Value at PC                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | '1' = Bit is set                                                                                                                  |                                                                                                                    | '0' = Bit is clear                                                                     |                                                                            | x = Bit is unkno                       | מאונ                                    |

|                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                   |                                                                                                                    |                                                                                        |                                                                            |                                        | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

| bit 7                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Collision Detect bit<br>SUF register is writ                                                                                      |                                                                                                                    | till transmitting the                                                                  | e previous word (I                                                         | must be cleared i                      | n software)                             |

| bit 6                            | In SPI mode:<br>1 = A new byt<br>data in SS<br>transmittin<br>tion (and t<br>0 = No overflo<br>In I <sup>2</sup> C <sup>™</sup> mode:<br>1 = A byte is b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | received while the<br>node. SSPOV mu                                                                                              | e the SSPBUI<br>flow can only o<br>etting overflow<br>itiated by writin<br>e SSPBUF reg                            | occur in Slave mode<br>. In Master mode<br>ng to the SSPBU<br>gister is still holdi    | ode. The user mu<br>e, the overflow bit<br>F register.<br>Ing the previous | st read the SSPE<br>is not set since e | BUF, even if only<br>each new recep     |

| bit 5                            | In SPI mode:<br>1 = Enables se<br>0 = Disables se<br>In I <sup>2</sup> C mode:<br>1 = Enables the<br>0 = Disables se                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ronous Serial Por<br>rial port and confi<br>erial port and conf<br>e serial port and c<br>erial port and conf<br>when enabled, th | gures SCK, SI<br>igures these p<br>onfigures the s<br>igures these p                                               | ins as I/O port pi<br>SDA and SCL pir<br>ins as I/O port pi                            | ns<br>ns as serial port p<br>ns                                            |                                        |                                         |

| bit 4                            | <b>CKP</b> : Clock Po<br>In SPI mode:<br>1 = Idle state fo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | larity Select bit<br>or clock is a high le<br>or clock is a low le                                                                | evel (Microwire                                                                                                    | e default)                                                                             |                                                                            | i ouput.                               |                                         |

|                                  | 1 = Enable cloc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                   | n). (Used to er                                                                                                    | isure data setup                                                                       | time.)                                                                     |                                        |                                         |

| bit 3-0                          | $\begin{array}{l} 0000 = {\rm SPI} \mbox{ Ma} \\ 0001 = {\rm SPI} \mbox{ Ma} \\ 0010 = {\rm SPI} \mbox{ Ma} \\ 0011 = {\rm SPI} \mbox{ Ma} \\ 0100 = {\rm SPI} \mbox{ SIa} \\ 0101 = {\rm SPI} \mbox{ SIa} \\ 0101 = {\rm I}^2 {\rm C} \mbox{ SIa} \\ 0111 = {\rm I}^2 {\rm C} \mbox{ SIa} \\ 1000 = {\rm Reserv} \\ 1001 = {\rm Reserv} \\ 1010 = {\rm Reserv} \\ 1011 = {\rm I}^2 {\rm C} \mbox{ Firm} \\ 1100 = {\rm Reserv} \\ 1101 = {\rm Reserv} \\ 1100 = {\rm SIa} \\ {\rm SIa} \mbox{ SIa} \mbox{ SIa} \mbox{ SIa} \mbox{ SIa} \\ {\rm SIa} \mbox{ SIa}  S$ | ed<br>ed<br>nware Controlled<br>ed                                                                                                | = Fosc/4<br>= Fosc/16<br>= Fosc/64<br>= TMR2 outpu<br>SCK pin. SS<br>SCK pin. SS<br>dress<br>ddress<br>Master mode | t/2<br>pin control enable<br>pin control disabl<br>(slave IDLE)<br>rt and Stop bit int | ed. <del>SS</del> can be us<br>terrupts enabled                            |                                        |                                         |

#### 14.2 Operation

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- · Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- · Slave Select mode (Slave mode only)

The SSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready. Once the eight bits of data have been received, that byte is moved to the SSPBUF register. Then, the Buffer Full Status bit BF of the SSPSTAT register, and the interrupt flag bit SSPIF, are set. Any write to the SSPBUF register during transmission/reception of data will be ignored and the Write Collision Detect bit, WCOL of the SSPCON register, will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully.

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. Buffer Full bit BF of the SSPSTAT register indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the SSP interrupt is used to determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 14-1 shows the loading of the SSPBUF (SSPSR) for data transmission.

The SSPSR is not directly readable or writable and can only be accessed by addressing the SSPBUF register. Additionally, the SSP STATUS register (SSPSTAT) indicates the various status conditions.

#### EXAMPLE 14-1: LOADING THE SSPBUF (SSPSR) REGISTER

| LOOP | BANKSEL | SSPSTAT     | ;                                           |

|------|---------|-------------|---------------------------------------------|

|      | BTFSS   | SSPSTAT, BF | ;Has data been received(transmit complete)? |

|      | GOTO    | LOOP        | ;No                                         |

|      | BANKSEL | SSPBUF      | ;                                           |

|      | MOVF    | SSPBUF, W   | ;WREG reg = contents of SSPBUF              |

|      | MOVF    | RXDATA      | ;Save in user RAM, if data is meaningful    |

|      | MOVF    | TXDATA, W   | ;W reg = contents of TXDATA                 |

|      | MOVF    | SSPBUF      | ;New data to xmit                           |

#### 14.13 Master Mode

Master mode of operation is supported in firmware using interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the SSP module is disabled. The Stop (P) and Start (S) bits will toggle based on the Start and Stop conditions. Control of the  $I^2C$  bus may be taken when the P bit is set or the bus is idle and both the S and P bits are clear.

In Master mode, the SCL and SDA lines are manipulated by clearing the corresponding TRISC<7,6> bit(s). The output level is always low, irrespective of the value(s) in PORTC<7,6>. So when transmitting data, a '1' data bit must have the TRISC<6> bit set (input) and a '0' data bit must have the TRISC<7> bit cleared (output). The same scenario is true for the SCL line with the TRISC<6> bit. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the I<sup>2</sup>C module.

The following events will cause the SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt will occur if enabled):

- Start condition

- Stop condition

- Data transfer byte transmitted/received

Master mode of operation can be done with either the Slave mode idle (SSPM<3:0> = 1011), or with the Slave active. When both Master and Slave modes are enabled, the software needs to differentiate the source(s) of the interrupt.

#### 14.14 Multi-Master Mode

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions, allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the SSP module is disabled. The Stop (P) and Start (S) bits will toggle based on the Start and Stop conditions. Control of the  $I^2C$  bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is idle and both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the Stop condition occurs.

In Multi-Master operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISC<7,6>). There are two stages where this arbitration can be lost, these are:

- · Address Transfer

- Data Transfer

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed, an ACK pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to re-transfer the data at a later time.

## 14.14.1 CLOCK SYNCHRONIZATION AND THE CKP BIT

When the CKP bit is cleared, the SCL output is forced to '0'; however, setting the CKP bit will not assert the SCL output low until the SCL output is already sampled low. Therefore, the CKP bit will not assert the SCL line until an external  $l^2C$  master device has already asserted the SCL line. The SCL output will remain low until the CKP bit is set and all other devices on the  $l^2C$  bus have deasserted SCL. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCL (see Figure 14-12).

#### TABLE 16-4: INITIALIZATION CONDITION FOR REGISTERS (CONTINUED)