Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                              |

| Number of I/O              | 35                                                                      |

| Program Memory Size        | 14KB (8K x 14)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 352 x 8                                                                 |

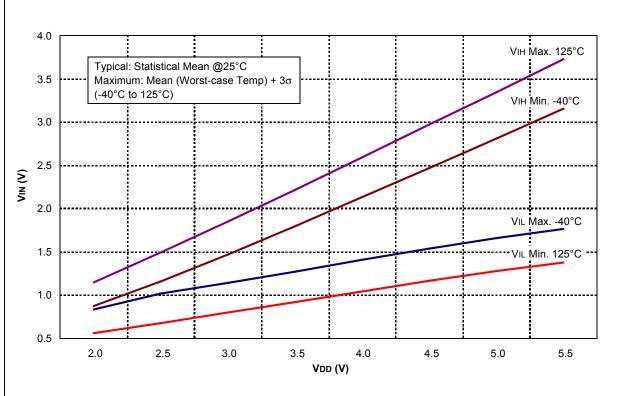

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                |

| Supplier Device Package    | 40-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f917-e-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, KEELOQ logo, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, PowerSmart, rfPIC, and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Linear Active Thermistor, Migratable Memory, MXDEV, MXLAB, PS logo, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, rfPICDEM, Select Mode, Smart Serial, SmartTel, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2007, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

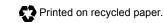

### Pin Diagrams - PIC16F913/916, 28-Pin

| Addr | Name                     | Bit 7         | Bit 6                                | Bit 5         | Bit 4         | Bit 3           | Bit 2          | Bit 1         | Bit 0         | Value on<br>POR, BOR | Page    |  |

|------|--------------------------|---------------|--------------------------------------|---------------|---------------|-----------------|----------------|---------------|---------------|----------------------|---------|--|

| Bank | 2                        |               |                                      |               |               |                 |                |               |               |                      |         |  |

| 100h | INDF                     | Addressing    | this location                        | uses conte    | nts of FSR to | address dat     | a memory (n    | ot a physical | register)     | xxxx xxxx            | 41,226  |  |

| 101h | TMR0                     | Timer0 Mo     | dule Registe                         | r             |               |                 |                |               |               | xxxx xxxx            | 99,226  |  |

| 102h | PCL                      | Program C     | ounter's (PC                         | ) Least Sign  | ificant Byte  |                 |                |               |               | 0000 0000            | 40,226  |  |

| 103h | STATUS                   | IRP           | RP1                                  | RP0           | TO            | PD              | Z              | DC            | С             | 0001 1xxx            | 32,226  |  |

| 104h | FSR                      | Indirect Da   | Indirect Data Memory Address Pointer |               |               |                 |                |               |               |                      |         |  |

| 105h | WDTCON                   | _             | _                                    | _             | WDTPS3        | WDTPS2          | WDTPS1         | WDTPS0        | SWDTEN        | 0 1000               | 235,227 |  |

| 106h | PORTB                    | RB7           | RB6                                  | RB5           | RB4           | RB3             | RB2            | RB1           | RB0           | xxxx xxxx            | 54,226  |  |

| 107h | LCDCON                   | LCDEN         | SLPEN                                | WERR          | VLCDEN        | CS1             | CS0            | LMUX1         | LMUX0         | 0001 0011            | 145,227 |  |

| 108h | LCDPS                    | WFT           | BIASMD                               | LCDA          | WA            | LP3             | LP2            | LP1           | LP0           | 0000 0000            | 146,227 |  |

| 109h | LVDCON                   | _             | _                                    | IRVST         | LVDEN         | —               | LVDL2          | LVDL1         | LVDL0         | 00 -100              | 145,228 |  |

| 10Ah | PCLATH                   | _             | _                                    | _             | Write Bu      | ffer for the up | oper 5 bits of | the Program   | Counter       | 0 0000               | 40,226  |  |

| 10Bh | INTCON                   | GIE           | PEIE                                 | T0IE          | INTE          | RBIE            | T0IF           | INTF          | RBIF          | 0000 000x            | 34,226  |  |

| 10Ch | EEDATL                   | EEDATL7       | EEDATL6                              | EEDATL5       | EEDATL4       | EEDATL3         | EEDATL2        | EEDATL1       | EEDATL0       | 0000 0000            | 188,228 |  |

| 10Dh | EEADRL                   | EEADRL7       | EEADRL6                              | EEADRL5       | EEADRL4       | EEADRL3         | EEADRL2        | EEADRL1       | EEADRL0       | 0000 0000            | 188,228 |  |

| 10Eh | EEDATH                   | _             | _                                    | EEDATH5       | EEDATH4       | EEDATH3         | EEDATH2        | EEDATH1       | EEDATH0       | 00 0000              | 188,228 |  |

| 10Fh | EEADRH                   | _             | _                                    | _             | EEADRH4       | EEADRH3         | EEADRH2        | EEADRH1       | EEADRH0       | 0 0000               | 188,228 |  |

| 110h | LCDDATA0                 | SEG7<br>COM0  | SEG6<br>COM0                         | SEG5<br>COM0  | SEG4<br>COM0  | SEG3<br>COM0    | SEG2<br>COM0   | SEG1<br>COM0  | SEG0<br>COM0  | XXXX XXXX            | 147,228 |  |

| 111h | LCDDATA1                 | SEG15<br>COM0 | SEG14<br>COM0                        | SEG13<br>COM0 | SEG12<br>COM0 | SEG11<br>COM0   | SEG10<br>COM0  | SEG9<br>COM0  | SEG8<br>COM0  | XXXX XXXX            | 147,228 |  |

| 112h | LCDDATA2 <sup>(2)</sup>  | SEG23<br>COM0 | SEG22<br>COM0                        | SEG21<br>COM0 | SEG20<br>COM0 | SEG19<br>COM0   | SEG18<br>COM0  | SEG17<br>COM0 | SEG16<br>COM0 | XXXX XXXX            | 147,228 |  |

| 113h | LCDDATA3                 | SEG7<br>COM1  | SEG6<br>COM1                         | SEG5<br>COM1  | SEG4<br>COM1  | SEG3<br>COM1    | SEG2<br>COM1   | SEG1<br>COM1  | SEG0<br>COM1  | XXXX XXXX            | 147,228 |  |

| 114h | LCDDATA4                 | SEG15<br>COM1 | SEG14<br>COM1                        | SEG13<br>COM1 | SEG12<br>COM1 | SEG11<br>COM1   | SEG10<br>COM1  | SEG9<br>COM1  | SEG8<br>COM1  | XXXX XXXX            | 147,228 |  |

| 115h | LCDDATA5 <sup>(2)</sup>  | SEG23<br>COM1 | SEG22<br>COM1                        | SEG21<br>COM1 | SEG20<br>COM1 | SEG19<br>COM1   | SEG18<br>COM1  | SEG17<br>COM1 | SEG16<br>COM1 | xxxx xxxx            | 147,228 |  |

| 116h | LCDDATA6                 | SEG7<br>COM2  | SEG6<br>COM2                         | SEG5<br>COM2  | SEG4<br>COM2  | SEG3<br>COM2    | SEG2<br>COM2   | SEG1<br>COM2  | SEG0<br>COM2  | XXXX XXXX            | 147,228 |  |

| 117h | LCDDATA7                 | SEG15<br>COM2 | SEG14<br>COM2                        | SEG13<br>COM2 | SEG12<br>COM2 | SEG11<br>COM2   | SEG10<br>COM2  | SEG9<br>COM2  | SEG8<br>COM2  | XXXX XXXX            | 147,228 |  |

| 118h | LCDDATA8 <sup>(2)</sup>  | SEG23<br>COM2 | SEG22<br>COM2                        | SEG21<br>COM2 | SEG20<br>COM2 | SEG19<br>COM2   | SEG18<br>COM2  | SEG17<br>COM2 | SEG16<br>COM2 | XXXX XXXX            | 147,228 |  |

| 119h | LCDDATA9                 | SEG7<br>COM3  | SEG6<br>COM3                         | SEG5<br>COM3  | SEG4<br>COM3  | SEG3<br>COM3    | SEG2<br>COM3   | SEG1<br>COM3  | SEG0<br>COM3  | XXXX XXXX            | 147,228 |  |

| I1Ah | LCDDATA10                | SEG15<br>COM3 | SEG14<br>COM3                        | SEG13<br>COM3 | SEG12<br>COM3 | SEG11<br>COM3   | SEG10<br>COM3  | SEG9<br>COM3  | SEG8<br>COM3  | XXXX XXXX            | 147,228 |  |

| 11Bh | LCDDATA11 <sup>(2)</sup> | SEG23<br>COM3 | SEG22<br>COM3                        | SEG21<br>COM3 | SEG20<br>COM3 | SEG19<br>COM3   | SEG18<br>COM3  | SEG17<br>COM3 | SEG16<br>COM3 | XXXX XXXX            | 147,228 |  |

| 11Ch | LCDSE0 <sup>(3)</sup>    | SE7           | SE6                                  | SE5           | SE4           | SE3             | SE2            | SE1           | SE0           | 0000 0000            | 147,228 |  |

| 11Dh | LCDSE1 <sup>(3)</sup>    | SE15          | SE14                                 | SE13          | SE12          | SE11            | SE10           | SE9           | SE8           | 0000 0000            | 147,228 |  |

| 11Eh | LCDSE2(2,3)              | SE23          | SE22                                 | SE21          | SE20          | SE19            | SE18           | SE17          | SE16          | 0000 0000            | 147,228 |  |

| 11Fh | —                        | Unimpleme     | ented                                |               |               |                 |                |               |               |                      | _       |  |

#### TABLE 2-3: PIC16F91X/946 SPECIAL FUNCTION REGISTERS SUMMARY BANK 2

Legend: -= Unimplemented locations read as '<u>o</u>', <u>u</u> = unchanged, <u>x</u> = unknown, <u>q</u> = value depends on condition, shaded = unimplemented

Note 1: Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

2: PIC16F914/917 and PIC16F946 only.

3: This register is only initialized by a POR or BOR reset and is unchanged by other Resets.

### 2.2.2.8 PCON Register

The Power Control (PCON) register contains flag bits (see Table 16-2) to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Watchdog Timer Reset (WDT)

- External MCLR Reset

The PCON register also controls the software enable of the BOR.

The PCON register bits are shown in Register 2-8.

### REGISTER 2-8: PCON: POWER CONTROL REGISTER

| U-0   | U-0 | U-0 | R/W-1  | U-0 | U-0 | R/W-0 | R/W-x |

|-------|-----|-----|--------|-----|-----|-------|-------|

| —     | —   | _   | SBOREN | _   | —   | POR   | BOR   |

| bit 7 |     |     |        |     |     |       | bit 0 |

| r            |                                                      |                           |                                  |                                  |  |  |  |  |  |  |

|--------------|------------------------------------------------------|---------------------------|----------------------------------|----------------------------------|--|--|--|--|--|--|

| Legend:      |                                                      |                           |                                  |                                  |  |  |  |  |  |  |

| R = Readal   | ole bit                                              | W = Writable bit          | U = Unimplemented bit,           | read as '0'                      |  |  |  |  |  |  |

| -n = Value a | at POR                                               | '1' = Bit is set          | '0' = Bit is cleared             | x = Bit is unknown               |  |  |  |  |  |  |

| bit 7-5      | Unimplem                                             | ented: Read as 'o'        |                                  |                                  |  |  |  |  |  |  |

|              | Unimplemented: Read as '0'                           |                           |                                  |                                  |  |  |  |  |  |  |

| bit 4        | bit 4 SBOREN: Software BOR Enable bit <sup>(1)</sup> |                           |                                  |                                  |  |  |  |  |  |  |

|              | 1 = BOR enabled                                      |                           |                                  |                                  |  |  |  |  |  |  |

|              | 0 <b>= BOR di</b>                                    | sabled                    |                                  |                                  |  |  |  |  |  |  |

| bit 3-2      | Unimplem                                             | ented: Read as '0'        |                                  |                                  |  |  |  |  |  |  |

| bit 1        | POR: Powe                                            | er-on Reset Status bit    |                                  |                                  |  |  |  |  |  |  |

|              | 1 = No Pov                                           | ver-on Reset occurred     |                                  |                                  |  |  |  |  |  |  |

|              | 0 = A Powe                                           | er-on Reset occurred (mus | t be set in software after a Po  | wer-on Reset occurs)             |  |  |  |  |  |  |

| bit 0        | BOR: Brow                                            | n-out Reset Status bit    |                                  |                                  |  |  |  |  |  |  |

|              | 1 = No Bro                                           | wn-out Reset occurred     |                                  |                                  |  |  |  |  |  |  |

|              | 0 = A Brow                                           | n-out Reset occurred (mus | st be set in software after a Po | ower-on Reset or Brown-out Reset |  |  |  |  |  |  |

|              | occurs                                               |                           |                                  |                                  |  |  |  |  |  |  |

|              |                                                      | ,                         |                                  |                                  |  |  |  |  |  |  |

**Note 1:** Set BOREN<1:0> = 01 in the Configuration Word register for this bit to control the  $\overline{\text{BOR}}$ .

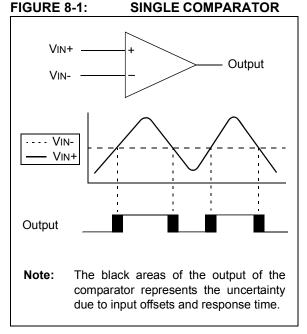

## 8.0 COMPARATOR MODULE

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. The comparators are very useful mixed signal building blocks because they provide analog functionality independent of the program execution. The Analog Comparator module includes the following features:

- Dual comparators

- Multiple comparator configurations

- Comparator outputs are available internally/externally

- Programmable output polarity

- · Interrupt-on-change

- · Wake-up from Sleep

- Timer1 gate (count enable)

- Output synchronization to Timer1 clock input

- Programmable voltage reference

#### 8.1 Comparator Overview

A comparator is shown in Figure 8-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

This device contains two comparators as shown in Figure 8-2 and Figure 8-3. The comparators are not independently configurable.

|                  | R/W-0                                                                                                                                                                 | R/C-0                                                                                                                                                                                              | R/W-1                             | R/W-0                      | 0 R/W-0                               | R/W-1                       | R/W-1                |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------|---------------------------------------|-----------------------------|----------------------|

| LCDEN            | SLPEN                                                                                                                                                                 | WERR                                                                                                                                                                                               | VLCDEN                            | CS1                        | CS0                                   | LMUX1                       | LMUX0                |

| bit 7            |                                                                                                                                                                       |                                                                                                                                                                                                    |                                   |                            |                                       |                             | bit                  |

|                  |                                                                                                                                                                       |                                                                                                                                                                                                    |                                   |                            |                                       |                             |                      |

| Legend:          |                                                                                                                                                                       |                                                                                                                                                                                                    |                                   |                            |                                       |                             |                      |

| R = Readab       |                                                                                                                                                                       | W = Writable b                                                                                                                                                                                     | it                                |                            | nplemented bit, r                     |                             |                      |

| C = Only cle     |                                                                                                                                                                       | '1' = Bit is set                                                                                                                                                                                   |                                   | '0' = Bit i                | s cleared                             | x = Bit is unkr             | nown                 |

| -n = Value a     | at POR                                                                                                                                                                |                                                                                                                                                                                                    |                                   |                            |                                       |                             |                      |

|                  |                                                                                                                                                                       |                                                                                                                                                                                                    | .,                                |                            |                                       |                             |                      |

| bit 7            |                                                                                                                                                                       | ) Driver Enable b                                                                                                                                                                                  |                                   |                            |                                       |                             |                      |

|                  |                                                                                                                                                                       | er module is ena<br>er module is disa                                                                                                                                                              |                                   |                            |                                       |                             |                      |

| bit 6            |                                                                                                                                                                       | Driver Enable i                                                                                                                                                                                    |                                   | e bit                      |                                       |                             |                      |

|                  |                                                                                                                                                                       | er module is disa                                                                                                                                                                                  | •                                 |                            |                                       |                             |                      |

|                  |                                                                                                                                                                       | er module is ena                                                                                                                                                                                   |                                   |                            |                                       |                             |                      |

| L:4 F            |                                                                                                                                                                       |                                                                                                                                                                                                    |                                   |                            |                                       |                             |                      |

| DIT 5            | WERR: LOD                                                                                                                                                             | Write Failed Err                                                                                                                                                                                   | זומיזכ                            |                            |                                       |                             |                      |

| bit 5            | 1 = LCDDAT                                                                                                                                                            | Ax register writ                                                                                                                                                                                   |                                   | e WA bit o                 | of the LCDPS re                       | egister = 0 (must           | be cleared i         |

| DIT 5            | 1 = LCDDAT<br>software                                                                                                                                                | Ax register writ                                                                                                                                                                                   |                                   | e WA bit o                 | of the LCDPS re                       | egister = 0 (must           | be cleared i         |

|                  | 1 = LCDDAT<br>software<br>0 = No LCD v                                                                                                                                | Ax register writ<br>)<br>write error                                                                                                                                                               | en while the                      |                            | of the LCDPS re                       | egister = 0 (must           | be cleared i         |

|                  | 1 = LCDDAT<br>software<br>0 = No LCD v<br>VLCDEN: LC                                                                                                                  | Ax register writ<br>)<br>write error<br>D Bias Voltage                                                                                                                                             | en while the                      |                            | of the LCDPS re                       | egister = 0 (must           | be cleared i         |

|                  | 1 = LCDDAT<br>software<br>0 = No LCD V<br>VLCDEN: LC<br>1 = VLCD pir                                                                                                  | Ax register writ<br>)<br>write error                                                                                                                                                               | en while the                      |                            | of the LCDPS re                       | egister = 0 (must           | be cleared i         |

| bit 4<br>bit 3-2 | 1 = LCDDAT<br>software<br>0 = No LCD v<br>VLCDEN: LC<br>1 = VLCD pir<br>0 = VLCD pir                                                                                  | Ax register writ<br>)<br>write error<br>D Bias Voltage I<br>is are enabled                                                                                                                         | en while the                      |                            | of the LCDPS re                       | egister = 0 (must           | be cleared i         |

| bit 4            | 1 = LCDDAT<br>software<br>0 = No LCD v<br>VLCDEN: LC<br>1 = VLCD pir<br>0 = VLCD pir<br>CS<1:0>: Clc<br>00 = Fosc/81                                                  | Ax register writ<br>)<br>write error<br>D Bias Voltage I<br>is are enabled<br>is are disabled<br>ock Source Selec<br>192                                                                           | en while the                      |                            | of the LCDPS re                       | egister = 0 (must           | be cleared i         |

| bit 4            | 1 = LCDDAT<br>software<br>0 = No LCD v<br>VLCDEN: LC<br>1 = VLCD pir<br>0 = VLCD pir<br>CS<1:0>: Clc<br>00 = Fosc/81<br>01 = T1OSC                                    | Ax register writ<br>write error<br>D Bias Voltage I<br>as are enabled<br>as are disabled<br>ock Source Selec<br>192<br>(Timer1)/32                                                                 | en while the                      |                            | of the LCDPS re                       | egister = 0 (must           | be cleared i         |

| bit 4<br>bit 3-2 | 1 = LCDDAT<br>software<br>0 = No LCD v<br>VLCDEN: LC<br>1 = VLCD pir<br>0 = VLCD pir<br>CS<1:0>: Clc<br>00 = Fosc/81<br>01 = T1OSC<br>1x = LFINTO                     | Ax register writ<br>write error<br>D Bias Voltage I<br>as are enabled<br>as are disabled<br>bock Source Selec<br>192<br>(Timer1)/32<br>SC (31 kHz)/32                                              | Pins Enable                       |                            | of the LCDPS re                       | egister = 0 (must           | be cleared i         |

| bit 4            | 1 = LCDDAT<br>software<br>0 = No LCD v<br>VLCDEN: LC<br>1 = VLCD pir<br>0 = VLCD pir<br>CS<1:0>: Clc<br>00 = Fosc/81<br>01 = T1OSC<br>1x = LFINTO                     | Ax register writ<br>write error<br>D Bias Voltage I<br>as are enabled<br>as are disabled<br>ock Source Selec<br>192<br>(Timer1)/32                                                                 | Pins Enable                       |                            | of the LCDPS re                       | egister = 0 (must           | be cleared i         |

| bit 4<br>bit 3-2 | 1 = LCDDAT<br>software<br>0 = No LCD v<br>VLCDEN: LC<br>1 = VLCD pir<br>0 = VLCD pir<br>CS<1:0>: Clc<br>00 = Fosc/81<br>01 = T1OSC<br>1x = LFINTO<br>LMUX<1:0>:       | Ax register writ<br>write error<br>D Bias Voltage<br>as are enabled<br>as are disabled<br>pock Source Selec<br>(92<br>(Timer1)/32<br>SC (31 kHz)/32<br>Commons Sele                                | Pins Enable                       | bit                        | of the LCDPS re<br>um Number of F     |                             |                      |

| bit 4<br>bit 3-2 | 1 = LCDDAT<br>software<br>0 = No LCD v<br>VLCDEN: LC<br>1 = VLCD pir<br>0 = VLCD pir<br>CS<1:0>: Clc<br>00 = Fosc/81<br>01 = T1OSC<br>1x = LFINTO                     | Ax register writ<br>write error<br>D Bias Voltage I<br>as are enabled<br>as are disabled<br>bock Source Selec<br>192<br>(Timer1)/32<br>SC (31 kHz)/32                                              | Pins Enable                       | bit<br>Maxim               |                                       | Pixels                      | be cleared i<br>Bias |

| bit 4<br>bit 3-2 | 1 = LCDDAT<br>software<br>0 = No LCD v<br>VLCDEN: LC<br>1 = VLCD pir<br>0 = VLCD pir<br>CS<1:0>: Clc<br>00 = Fosc/81<br>01 = T1OSC<br>1x = LFINTO<br>LMUX<1:0>:       | Ax register writ<br>write error<br>D Bias Voltage<br>as are enabled<br>as are disabled<br>pock Source Selec<br>(92<br>(Timer1)/32<br>SC (31 kHz)/32<br>Commons Sele                                | Pins Enable<br>Ct bits            | bit<br>Maxim<br>913/916    | um Number of F                        | Pixels                      |                      |

| bit 4<br>bit 3-2 | 1 = LCDDAT<br>software<br>0 = No LCD v<br>VLCDEN: LC<br>1 = VLCD pir<br>0 = VLCD pir<br>CS<1:0>: Clc<br>00 = FOSC/81<br>01 = T1OSC<br>1x = LFINTO<br>LMUX<1:0>:       | Ax register write<br>write error<br>D Bias Voltage<br>Ins are enabled<br>as are disabled<br>bock Source Select<br>192<br>(Timer1)/32<br>SC (31 kHz)/32<br>Commons Select<br>Multiplex              | Pins Enable<br>Ct bits            | Maxim<br>913/916<br>6      | um Number of F<br>PIC16F914/91        | Pixels<br>7 PIC16F946       | Bias                 |

| bit 4<br>bit 3-2 | 1 = LCDDAT<br>software<br>0 = No LCD v<br>VLCDEN: LC<br>1 = VLCD pir<br>0 = VLCD pir<br>CS<1:0>: Clc<br>00 = Fosc/81<br>01 = T1OSC<br>1x = LFINTO<br>LMUX<1:0>:<br>00 | Ax register writ<br>write error<br>D Bias Voltage I<br>as are enabled<br>as are disabled<br>ock Source Selec<br>(92<br>(Timer1)/32<br>SC (31 kHz)/32<br>Commons Sele<br>Multiplex<br>Static (COM0) | Pins Enable<br>of bits<br>PIC16FS | Maxim<br>913/916<br>6<br>2 | um Number of F<br>PIC16F914/917<br>24 | Pixels<br>7 PIC16F946<br>42 | Bias                 |

### REGISTER 10-1: LCDCON: LIQUID CRYSTAL DISPLAY CONTROL REGISTER

**Note 1:** On PIC16F913/916 devices, COM3 and SEG15 are shared on one pin, limiting the device from driving 64 pixels.

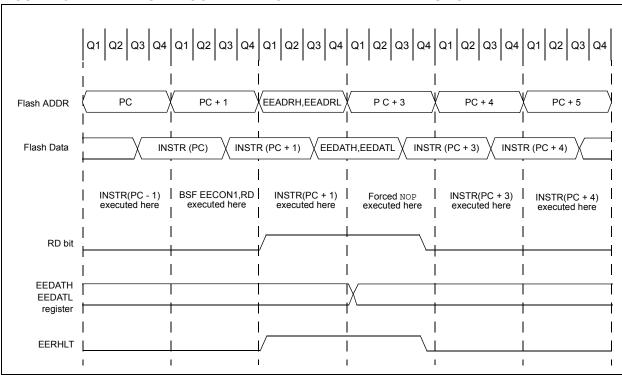

#### FIGURE 13-1: FLASH PROGRAM MEMORY READ CYCLE EXECUTION

#### TABLE 13-1: SUMMARY OF ASSOCIATED REGISTERS WITH DATA EEPROM

| Name   | Bit 7    | Bit 6         | Bit 5          | Bit 4           | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------|---------------|----------------|-----------------|---------|---------|---------|---------|----------------------|---------------------------------|

| INTCON | GIE      | PEIE          | T0IE           | INTE            | RBIE    | T0IF    | INTF    | RBIF    | 0000 000x            | 0000 000x                       |

| PIE1   | EEIE     | ADIE          | RCIE           | TXIE            | SSPIE   | CCP1IE  | TMR2IE  | TMR1IE  | 0000 0000            | 0000 0000                       |

| PIR1   | EEIF     | ADIF          | RCIF           | TXIF            | SSPIF   | CCP1IF  | TMR2IF  | TMR1IF  | 0000 0000            | 0000 0000                       |

| EEADRH | _        | _             | _              | EEADRH4         | EEADRH3 | EEADRH2 | EEADRH1 | EEADRH0 | 0 0000               | 0 0000                          |

| EEADRL | EEADRL7  | EEADRL6       | EEADRL5        | EEADRL4         | EEADRL3 | EEADRL2 | EEADRL1 | EEADRL0 | 0000 0000            | 0000 0000                       |

| EECON1 | EEPGD    | _             | —              |                 | WRERR   | WREN    | WR      | RD      | 0 x000               | q000                            |

| EECON2 | EEPROM C | ontrol Regist | er 2 (not a pł | nysical registe | er)     |         |         |         |                      |                                 |

| EEDATH | _        | -             | EEDATH5        | EEDATH4         | EEDATH3 | EEDATH2 | EEDATH1 | EEDATH0 | 00 0000              | 00 0000                         |

| EEDATL | EEDATL7  | EEDATL6       | EEDATL5        | EEDATL4         | EEDATL3 | EEDATL2 | EEDATL1 | EEDATL0 | 0000 0000            | 0000 0000                       |

$\label{eq:logarder} \begin{array}{ll} \mbox{Legend:} & x \mbox{=} unknown, \mbox{$u$} \mbox{=} unknown, \mbox{=} unknown, \mbox{=} unknown, \mbox{=} unknown, \mbox{=} unknown, \mbox{=} unknown, \mbox{$

### REGISTER 14-2: SSPCON: SYNC SERIAL PORT CONTROL REGISTER

| R/W-0                            | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W-0                                                                                                                                            | R/W-0                                                                                                | R/W-0                                                                      | R/W-0                                  | R/W-0                               |  |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------|-------------------------------------|--|

| WCOL                             | SSPOV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SSPEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CKP                                                                                                                                              | SSPM3 <sup>(2)</sup>                                                                                 | SSPM2 <sup>(2)</sup>                                                       | SSPM1 <sup>(2)</sup>                   | SSPM0 <sup>(2)</sup>                |  |

| bit 7                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                  |                                                                                                      |                                                                            |                                        | bit (                               |  |

| Logondy                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                  |                                                                                                      |                                                                            |                                        |                                     |  |

| <b>Legend:</b><br>R = Readable b | it                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | W = Writable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                  | U = Unimpleme                                                                                        | ented bit, read as                                                         | '0'                                    |                                     |  |

| -n = Value at PC                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                  | '0' = Bit is clear                                                                                   |                                                                            | x = Bit is unkno                       | wn                                  |  |