#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | 56800E                                                                |

| Core Size                  | 16-Bit                                                                |

| Speed                      | 32MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                            |

| Peripherals                | POR, PWM, WDT                                                         |

| Number of I/O              | 26                                                                    |

| Program Memory Size        | 16KB (8K x 16)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 2K x 16                                                               |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                             |

| Data Converters            | A/D 8x12b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    | 32-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc56f8014mfae |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

create a complete, scalable tools solution for easy, fast, and efficient development.

### 1.4 Architecture Block Diagram

The 56F8014's architecture is shown in **Figure 1-1**, **Figure 1-2**, and **Figure 1-3**. **Figure 1-1** illustrates how the 56800E system buses communicate with internal memories and the IPBus Bridge, as well as showing the internal connections between each unit of the 56800E core. **Figure 1-2** shows the peripherals and control blocks connected to the IPBus Bridge. **Figure 1-3** details how the device's I/O pins are muxed. The figures do not show the on-board regulator and power and ground signals. They also do not show the multiplexing between peripherals or the dedicated GPIOs. Please see **Part 2 Signal/Connection Descriptions** to see which signals are multiplexed with those of other peripherals.

### 1.5 Synchronize ADC with PWM

ADC conversion can be synchronized with the PWM module via Quad Timer channel 2 and 3 if needed. Internally, the PWM synch signal — which is generated at every PWM reload —can be connected to the timer channel 3 input, and the timer channel 2 and channel 3 outputs are connected to the ADC sync inputs. Timer channel 3 output is connected to SYNC0 and timer channel 2 is connected to SYNC1. The setting is controlled by the TC3\_INP bit in the SIM Control Register; see Section 6.3.1.

SYNC0 is the master ADC sync input, used to trigger both ADCA and ADCB in sequence and parallel mode. SYNC1 is used to trigger ADCB in parallel independent mode, while SYNC0 is used to trigger ADCA. See *MC56F8000RM*, the 56F801X Peripheral Reference Manual, for additional information.

### **1.6 Multiple Frequency PWM Output**

When both PWM channels of a complementary pair in software control mode and software control bits are set to 1, each complementary PWM signal pair — PWM 0 and 1; PWM 2 and 3; and PWM 4 and 5 — can select a PWM source from one of the following sources. This will enable each PWM pair and PWM2 to output PWM signals at different frequencies.

- External GPIO input:

- GPIOB2 input can be used to drive PWM 0 and 1

- GPIOB3 input can be used to drive PWM 2

- GPIOB4 input can be used to drive PWM 4 and 5

- Quad Timer output:

- Timer0 output can be used to drive PWM 0 and 1

- Timer2 output can be used to drive PWM 2

- Timer3 output can be used to drive PWM 4 and 5

- ADC conversion result:

- Signal of over/under limit of ADC sample 0 can be used to drive PWM 0 and 1

- Signal of over/under limit of ADC sample 1 can be used to drive PWM 2

# **Part 2 Signal/Connection Descriptions**

## 2.1 Introduction

The input and output signals of the 56F8014 are organized into functional groups, as detailed in **Table 2-1**. **Table 2-2** summarizes all device pins. In **Table 2-2**, each table row describes the signal or signals present on a pin, sorted by pin number.

| Functional Group                                         | Number of Pins |

|----------------------------------------------------------|----------------|

| Power (V <sub>DD</sub> or V <sub>DDA</sub> )             | 2              |

| Ground (V <sub>SS</sub> or V <sub>SSA</sub> )            | 3              |

| Supply Capacitors                                        | 1              |

| Reset                                                    | 1              |

| Pulse Width Modulator (PWM) Ports <sup>1</sup>           | 5              |

| Serial Peripheral Interface (SPI) Ports <sup>2</sup>     | 4              |

| Analog-to-Digital Converter (ADC) Ports                  | 8              |

| Timer Module Ports <sup>3</sup>                          | 2              |

| Serial Communications Interface (SCI) Ports <sup>4</sup> | 2              |

| JTAG/Enhanced On-Chip Emulation (EOnCE)                  | 4              |

#### **Table 2-1 Functional Group Pin Allocations**

1. Pins in this section can function as TMR and GPIO.

2. Pins in this section can function as TMR,  $\ensuremath{I^2C}\xspace$  , and GPIO.

3. Pins can function as PWM and GPIO.

4. Pins in this section can function as  $I^2C$  and GPIO.

# Part 3 OCCS

### 3.1 Overview

This module provides the system clock, which uses it to generate the various chip clocks. This module also produces the oscillator clock signals, plus the ADC clock and high-speed peripheral clock.

The on-chip clock synthesis module allows product design using an internal relaxation oscillator to run 56F801X family parts at user-selectable frequencies up to 32MHz.

## 3.2 Features

The On-Chip Clock Synthesis (OCCS) module interfaces to the oscillator and PLL. The OCCS module features:

- Internal relaxation oscillator

- Ability to power down the internal relaxation oscillator

- Ability to put the internal relaxation oscillator into a standby mode

- 3-bit postscaler provides control for the PLL output

- Ability to power down the internal PLL

- Provides 2X system clock frequency, which operates at twice the system clock, to the System Integration Module (SIM) that is used to generate the various device clocks

- Provides 3X system clock, which operates at three times the system clock, to PWM and Timer

- Safety shutdown feature is available in the event that the PLL reference clock disappears

- Can be driven from an external clock source

The clock generation module provides the programming interface for both the PLL and internal relaxation oscillator.

## 3.3 Operating Modes

In 56F801X family parts, either an internal oscillator or an external frequency source can be used to provide a reference clock to the SIM.

The 2X system clock source output from the OCCS can be described by one of the following equations:

2X system frequency = oscillator frequency

2X system frequency = (oscillator frequency X 8) / (postscaler)

where:

postscaler = 1, 2, 4, 8, 16, or 32 PLL output divider

The SIM is responsible for further dividing these frequencies by two, which will insure a 50% duty cycle in the system clock output.

### 4.4 Data Map

| Begin/End Address          | Memory Allocation                               |

|----------------------------|-------------------------------------------------|

| X:\$FF FFFF<br>X:\$FF FF00 | EOnCE<br>256 locations allocated                |

| X:\$FF FEFF<br>X:\$01 0000 | RESERVED                                        |

| X:\$00 FFFF<br>X:\$00 F000 | On-Chip Peripherals<br>4096 locations allocated |

| X:\$00 EFFF<br>X:\$00 8800 | RESERVED                                        |

| X:\$00 EFFF<br>X:\$00 0800 | Reserved                                        |

| X:\$00 7FFF<br>X:\$00 0040 | RESERVED                                        |

| X:\$00 07FF<br>X:\$00 0000 | On-Chip Data RAM <sup>2</sup><br>4KB            |

#### Table 4-4 Data Memory Map<sup>1</sup>

1. All addresses are 16-bit Word addresses.

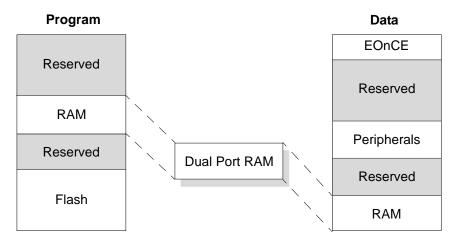

2. This RAM is shared with Program space starting at P: \$00 8000; see Figure 4-1.

Figure 4-1 Dual Port RAM

### 4.5 EOnCE Memory Map

Figure 4-5 lists all EOnCE registers necessary to access or control the EOnCE.

| Register Acronym | Address Offset | Register Description                 |

|------------------|----------------|--------------------------------------|

| PWM_CTRL         | \$0            | Control Register                     |

| PWM_FCTRL        | \$1            | Fault Control Register               |

| PWM_FLTACK       | \$2            | Fault Status Acknowledge Register    |

| PWM_OUT          | \$3            | Output Control Register              |

| PWM_CNTR         | \$4            | Counter Register                     |

| PWM_CMOD         | \$5            | Counter Modulo Register              |

| PWM_VAL0         | \$6            | Value Register 0                     |

| PWM_VAL1         | \$7            | Value Register 1                     |

| PWM_VAL2         | \$8            | Value Register 2                     |

| PWM_VAL3         | \$9            | Value Register 3                     |

| PWM_VAL4         | \$A            | Value Register 4                     |

| PWM_VAL5         | \$B            | Value Register 5                     |

| PWM_DTIM0        | \$C            | Dead Time Register 0                 |

| PWM_DTIM1        | \$D            | Dead Time Register 1                 |

| PWM_DMAP1        | \$E            | Disable Mapping Register 1           |

| PWM_DMAP2        | \$F            | Disable Mapping Register 2           |

| PWM_CNFG         | \$10           | Configure Register                   |

| PWM_CCTRL        | \$11           | Channel Control Register             |

| PWM_PORT         | \$12           | Port Register                        |

| PWM_ICCTRL       | \$13           | Internal Correction Control Register |

| PWM_SCTRL        | \$14           | Source Control Register              |

#### Table 4-8 Pulse Width Modulator Registers Address Map (PWM\_BASE = \$00 F040)

#### Table 4-9 Interrupt Control Registers Address Map (ITCN\_BASE = \$00 F060)

| Register Acronym | Address Offset | Register Description                          |

|------------------|----------------|-----------------------------------------------|

| ITCN_IPR0        | \$0            | Interrupt Priority Register 0                 |

| ITCN_IPR1        | \$1            | Interrupt Priority Register 1                 |

| ITCN_IPR2        | \$2            | Interrupt Priority Register 2                 |

| ITCN_IPR3        | \$3            | Interrupt Priority Register 3                 |

| ITCN_IPR4        | \$4            | Interrupt Priority Register 4                 |

| ITCN_VBA         | \$5            | Vector Base Address Register                  |

| ITCN_FIM0        | \$6            | Fast Interrupt Match 0 Register               |

| ITCN_FIVAL0      | \$7            | Fast Interrupt Vector Address Low 0 Register  |

| ITCN_FIVAH0      | \$8            | Fast Interrupt Vector Address High 0 Register |

#### 5.5.3.4 SCI Transmitter Idle Interrupt Priority Level (SCI\_TIDL IPL)— Bits 9–8

This field is used to set the interrupt priority level for IRQs. This IRQ is limited to priorities 0 through 2. It is disabled by default.

- 00 = IRQ disabled (default)

- 01 = IRQ is priority level 0

- 10 = IRQ is priority level 1

- 11 = IRQ is priority level 2

#### 5.5.3.5 SCI Transmitter Empty Interrupt Priority Level (SCI\_XMIT IPL)— Bits 7–6

This field is used to set the interrupt priority level for IRQs. This IRQ is limited to priorities 0 through 2. It is disabled by default.

- 00 = IRQ disabled (default)

- 01 = IRQ is priority level 0

- 10 = IRQ is priority level 1

- 11 = IRQ is priority level 2

#### 5.5.3.6 SPI Transmitter Empty Interrupt Priority Level (SPI\_XMIT IPL)— Bits 5–4

This field is used to set the interrupt priority level for IRQs. This IRQ is limited to priorities 0 through 2. It is disabled by default.

- 00 = IRQ disabled (default)

- 01 = IRQ is priority level 0

- 10 = IRQ is priority level 1

- 11 = IRQ is priority level 2

#### 5.5.3.7 SPI Receiver Full Interrupt Priority Level (SPI\_RCV IPL)— Bits 3–2

This field is used to set the interrupt priority level for IRQs. This IRQ is limited to priorities 0 through 2. It is disabled by default.

- 00 = IRQ disabled (default)

- 01 = IRQ is priority level 0

- 10 = IRQ is priority level 1

- 11 = IRQ is priority level 2

- SW Interrupt 0

- SW Interrupt LP

These interrupts are enabled at their fixed priority levels.

# Part 6 System Integration Module (SIM)

### 6.1 Introduction

The SIM module is a system catchall for the glue logic that ties together the system-on-chip. It controls distribution of resets and clocks and provides a number of control features. The System Integration Module is responsible for the following functions:

- Reset sequencing

- Clock control & distribution

- Stop/Wait control

- System status registers

- Registers for software access to the JTAG ID of the chip

- Test registers

- Power control

- I/O pad multiplexing

These are discussed in more detail in the sections that follow.

#### 6.2 Features

The SIM has the following features:

- Reset sequencing

- Core and Peripheral Clock control & distribution

- Stop/Wait mode control

- System status

- Power control

- Control I/O multiplexing

- System bus clocks with pipeline hold-off support

- System clocks for non-pipelined interfaces

- Peripheral clocks for Quad Timer and PWM with high-speed (3X) option

- Power-saving clock gating for peripherals

- Three power modes (Run, Wait, Stop) to control power utilization

- Stop mode shuts down the 56800E core, system clock, and peripheral clock

- Wait mode shuts down the 56800E core and unnecessary system clock operation

- Run mode supports full part operation

- Controls, with write protection, the enable/disable of 56800E core WAIT and STOP instructions

| Mode       | Core Clocks                                                                     | Peripheral Clocks                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|---------------------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wait       | Core and memory<br>clocks disabled                                              | Peripheral clocks<br>enabled        | Core executes WAIT instruction to enter this<br>mode.<br>Typically used for power-conscious applications.<br>Possible recoveries from Wait mode to Run<br>mode are:<br>1. Any interrupt<br>2. Executing a Debug mode entry command<br>during the 56800E core JTAG interface<br>2. Any reset (POR, external, software, COP)                                                                                                                            |

| Stop       | Master clock genera<br>remains operational,<br>the generation of sys<br>clocks. | but the SIM disables                | Core executes STOP instruction to enter this<br>mode. Possible recoveries from Stop mode to<br>Run mode are:<br>1. Interrupt from Timer channels that have been<br>configured to operate in Stop mode (TCx_SD)<br>2. Interrupt for SCI configured to operate in Stop<br>mode (SCI_SD)<br>3. Low-voltage interrupt<br>4. Executing a Debug mode entry command<br>using the 56800E core JTAG interface<br>5. Any reset (POR, external, software, COP)   |

| Standby    |                                                                                 | h-speed peripheral<br>e. System and | The user configures the OCCS and SIM to select<br>the relaxation oscillator clock source (PRECS),<br>shut down the PLL (PLLPD), put the relaxation<br>oscillator in Standby mode (ROSB), and put the<br>large regulator in Standby (LRSTDBY). The part<br>is fully operational, but operating at a minimum<br>frequency and power configuration. Recovery<br>requires reversing the sequence used to enter<br>this mode (allowing for PLL lock time). |

| Power-Down | Master clock genera<br>completely shut dow<br>peripheral clocks are             | n. All system and                   | The user configures the OCCS and SIM to enter<br>Standby mode as shown in the previous<br>description, followed by powering down the<br>oscillator (ROPD). The only possible recoveries<br>from this mode are:<br>1. External reset<br>2. Power-on reset                                                                                                                                                                                              |

#### Table 6-3 Clock Operation in Power-Down Modes (Continued)

The power modes provide additional means to disable clock domains, configure the voltage regulator, and configure clock generation to manage power utilization, as shown in **Table 6-3**. Run, Wait, and Stop modes provide means of enabling/disabling the peripheral and/or core clocking as a group. Stop disable controls are provided for selected peripherals in the control register so that these peripheral clocks can optionally continue to operate in Stop mode and generate interrupts which will return the part from Stop to Run mode. Standby mode provides normal operation but at very low speed and power utilization. It is possible to invoke Stop or Wait mode while in Standby mode for even greater levels of power reduction. A 200 kHz clock external clock can optionally be used in Standby mode to produce the required Standby 100 kHz system bus rate. Power-down mode, which selects the ROSC clock source but shuts it off, fully disables the part and minimizes its power utilization but is only recoverable via reset.

When the PLL is not selected and the system bus is operating at around 100 kHz, the large regulator can

be put into its Standby mode (LRSTDBY) to reduce the power utilization of that regulator.

All peripherals, except the COP/watchdog timer, run at the system clock (peripheral bus) frequency<sup>1</sup>, which is the same as the main processor frequency in this architecture. The COP timer runs at MSTR\_OSC / 1024. The maximum frequency of operation is SYS\_CLK = 32MHz. The only exception is the Quad Timer and PWM, which can be configured to operate at three times the system bus rate using TCR and PCR controls, provided the PLL is active and selected.

### 6.6 Resets

The SIM supports four sources of reset, as shown in **Figure 6-15**. The two asynchronous sources are the external reset pin and the Power-On Reset (POR). The two synchronous sources are the software reset, which is generated within the SIM itself by writing the SIM\_CTRL register in Section 6.3.1, and the COP reset. The SIM uses these to generate resets for the internal logic. These are outlined in Table 6-4. The first column lists the four primary resets which are calculated. The JTAG circuitry is reset by the Power-On Reset. Columns two through five indicate which reset sources trigger these reset signals. The last column provides additional detail.

|              |     | Reset S  | Sources  |     |                                                                                                     |

|--------------|-----|----------|----------|-----|-----------------------------------------------------------------------------------------------------|

| Reset Signal | POR | External | Software | СОР | Comments                                                                                            |

| EXTENDED_POR | Х   |          |          |     | Stretched version of POR. Relevant 64<br>Relaxation Oscillator Clock cycles after<br>POR deasserts. |

| CLKGEN_RST   | Х   | Х        | Х        | Х   | Released 32 Relaxation Oscillator Clock cycles after all reset sources have released.               |

| PERIP_RST    | Х   | Х        | Х        | Х   | Releases 32 Relaxation Oscillator Clock cycles after the CLKGEN_RST is released.                    |

| CORE_RST     | Х   | х        | х        | Х   | Releases 32 SYS_CLK periods after PERIP_RST is released.                                            |

**Table 6-4 Primary System Resets**

**Figure 6-15** provides a graphic illustration of the details in **Table 6-4**. Note that the POR\_Delay blocks use the Relaxation Oscillator Clock as their time base since other system clocks are inactive during this phase of reset.

<sup>1.</sup> The Quad Timer and PWM modules can be operated at three times the IPBus clock frequency.

in order to return to normal unsecured operation. Power-on reset will also reset both.

The user is responsible for directing the device to invoke the flash programming subroutine to reprogram the word \$0000 into program memory location \$00 1FF7. This is done by, for example, toggling a specific pin, or by downloading a user-defined key through serial interfaces.

**Note:** Flash contents can only be programmed for 1s to 0s.

## 7.3 Product Analysis

The recommended method of unsecuring a secured device for product analysis of field failures is via the method suggested in section 7.2.4. The customer would need to supply Technical Support with the details of the protocol to access the subroutines in flash. An alternative method for performing analysis on a secured device would be to mass-erase and reprogram the flash with the original code, but also either modify the security word or else not program the security word.

# Part 8 General Purpose Input/Output (GPIO)

## 8.1 Introduction

This section is intended to supplement the GPIO information found in the **56F801X Peripheral Reference Manual** and contains only chip-specific information. This information supercedes the generic information in the **56F801X Peripheral Reference Manual**.

## 8.2 Configuration

There are four GPIO ports defined on the 56F8014. The width of each port, the associated peripheral and reset functions are shown in **Table 8-1**. The specific mapping of GPIO port pins is shown in **Table 8-2**.

| GPIO Port | Available<br>Pins in<br>56F8014 | Peripheral Function | Reset Function      |

|-----------|---------------------------------|---------------------|---------------------|

| A         | 6                               | PWM, Reset          | GPIO, except GPIOA7 |

| В         | 8                               | SPI, SCI, Timer     | GPIO                |

| С         | 8                               | ADC                 | Analog              |

| D         | 4                               | JTAG                | JTAG                |

| GPIO Function | Peripheral Function      | LQFP<br>Package Pin | Notes                                                                                                                                                                          |

|---------------|--------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIOB6        | RXD / SDA / CLKIN        | 32                  | SIM register SIM_GPS is used to<br>select between RXD and SDA.<br>CLKIN functionality is enabled using<br>the PLL Control Register within the<br>OCCS block.<br>Defaults to B6 |

| GPIOB7        | TXD / SCL                | 2                   | SIM register SIM_GPS is used to<br>select between TXD and SCL<br>Defaults to B7                                                                                                |

| GPIOC0        | ANA0                     | 13                  | Defaults to ANA0                                                                                                                                                               |

| GPIOC1        | ANA1                     | 12                  | Defaults to ANA1                                                                                                                                                               |

| GPIOC2        | ANA2 / V <sub>REFH</sub> | 11                  | Defaults to ANA2                                                                                                                                                               |

| GPIOC3        | ANA3                     | 10                  | Defaults to ANA3                                                                                                                                                               |

| GPIOC4        | ANB0                     | 4                   | Defaults to ANB0                                                                                                                                                               |

| GPIOC5        | ANB1                     | 5                   | Defaults to ANB1                                                                                                                                                               |

| GPIOC6        | ANB2 / V <sub>REFL</sub> | 6                   | Defaults to ANB2                                                                                                                                                               |

| GPIOC7        | ANB3                     | 7                   | Defaults to ANB3                                                                                                                                                               |

| GPIOD0        | TDI                      | 29                  | Defaults to TDI                                                                                                                                                                |

| GPIOD1        | TDO                      | 31                  | Defaults to TDO                                                                                                                                                                |

| GPIOD2        | тск                      | 15                  | Defaults to TCK                                                                                                                                                                |

| GPIOD3        | TMS                      | 30                  | Defaults to TMS                                                                                                                                                                |

# Table 8-2 GPIO External Signals Map (Continued) Pins in shaded rows are not available in 56F8014

### 8.3 Reset Values

Tables 4-16 through 4-19 detail registers for the 56F8014; Figures 8-1 through 8-4 summarize register maps and reset values.

\_\_\_\_

| Add.<br>Offset | Register Acronym |              | 15     | 14     | 13     | 12     | 11     | 10     | 9      | 8      | 7      | 6      | 5      | 4      | 3 2 1 0          |

|----------------|------------------|--------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------------|

| \$0            | GPIOD_PUPEN      | R<br>W<br>RS | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | PU<br>1 1 1 1 1  |

| \$1            | GPIOD_DATA       | R<br>W<br>RS | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | D<br>0 0 0 0     |

| \$2            | GPIOD_DDIR       | R<br>W<br>RS | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | DD<br>0 0 0 0    |

| \$3            | GPIOD_PEREN      | R<br>W<br>RS | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | PE               |

| \$4            | GPIOD_IASSRT     | R<br>W<br>RS | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | IA<br>0 0 0 0    |

| \$5            | GPIOD_IEN        | R<br>W<br>RS | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | IEN<br>0 0 0 0   |

| \$6            | GPIOD_IEPOL      | R<br>W<br>RS | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | IEPOL            |

| \$7            | GPIOD_IPEND      | R<br>W<br>RS | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | IPR 0 0 0        |

| \$8            | GPIOD_IEDGE      | R<br>W<br>RS | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | IES<br>0 0 0 0   |

| \$9            | GPIOD_PPOUTM     | R<br>W<br>RS | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | OEN              |

| \$A            | GPIOD_RDATA      | R<br>W<br>RS | 0<br>X | RAW DATA         |

| \$В            | GPIOD_DRIVE      | R<br>W<br>RS | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | DRIVE<br>0 0 0 0 |

|                |                  | R            | 0      | Read   | l as 0 |        |        |        |        |        |        |        |        |        |                  |

Reserved

W

56F8014 Technical Data, Rev. 11

RS Reset

Figure 8-4 GPIOD Register Map Summary

## Part 9 Joint Test Action Group (JTAG)

#### 9.1 56F8014 Information

Please contact your Freescale sales representative or authorized distributor for device/package-specific BSDL information.

The  $\overline{\text{TRST}}$  pin is not available in this package. The pin is tied to  $V_{DD}$  in the package.

The JTAG state machine is reset during POR and can also be reset via a soft reset by holding TMS high for five rising edges of TCK, as described in the **56F8000 Peripheral User Manual**.

## Part 10 Specifications

### **10.1 General Characteristics**

The 56F8014 is fabricated in high-density CMOS with 5V-tolerant TTL-compatible digital inputs. The term "5V-tolerant" refers to the capability of an I/O pin, built on a 3.3V-compatible process technology, to withstand a voltage up to 5.5V without damaging the device. Many systems have a mixture of devices designed for 3.3V and 5V power supplies. In such systems, a bus may carry both 3.3V- and 5V-compatible I/O voltage levels (a standard 3.3V I/O is designed to receive a maximum voltage of  $3.3V \pm 10\%$  during normal operation without causing damage). This 5V-tolerant capability therefore offers the power savings of 3.3V I/O levels, combined with the ability to receive 5V levels without damage.

Absolute maximum ratings in **Table 10-1** are stress ratings only, and functional operation at the maximum is not guaranteed. Stress beyond these ratings may affect device reliability or cause permanent damage to the device.

Unless otherwise stated, all specifications within this chapter apply over the temperature range of -40°C to 125°C ambient temperature over the following supply ranges:

$V_{SS} = V_{SS}A = 0V, V_{DD} = V_{DDA} = 3.0-3.6V, CL \le 50pF, f_{OP} = 32MHz$

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 6. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

- 7. See Section 12.1 for more details on thermal design considerations.

#### **Table 10-4 Recommended Operating Conditions**

| $(V_{REFL} = 0V)$ | V <sub>SSA</sub> = | = 0V, ۱ | V <sub>SS</sub> = 0 | V) |

|-------------------|--------------------|---------|---------------------|----|

|-------------------|--------------------|---------|---------------------|----|

| Characteristic                                                                                                                            | Symbol             | Notes                              | Min    | Тур | Max              | Unit   |

|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------------------------|--------|-----|------------------|--------|

| Supply voltage                                                                                                                            | V <sub>DD</sub>    |                                    | 3      | 3.3 | 3.6              | V      |

| ADC Supply voltage                                                                                                                        | V <sub>DDA</sub>   |                                    | 3      | 3.3 | 3.6              | V      |

| ADC High Voltage Reference                                                                                                                | V <sub>REFH</sub>  |                                    | 3      | —   | V <sub>DDA</sub> | V      |

| Voltage difference $V_{DD\_IO}$ to $V_{DDA}$                                                                                              | $\Delta V_{DD}$    |                                    | -0.1   | 0   | 0.1              | V      |

| Voltage difference $V_{SS\_IO}$ to $V_{SSA}$                                                                                              | $\Delta V_{SS}$    |                                    | -0.1   | 0   | 0.1              | V      |

| Device Clock Frequency<br>Using relaxation oscillator<br>Using external clock source                                                      | FSYSCLK            |                                    | 8<br>0 | _   | 32<br>32         | MHz    |

| Input Voltage High (digital inputs)                                                                                                       | V <sub>IH</sub>    | Pin Groups 1, 2                    | 2      | —   | 5.5              | V      |

| Input Voltage Low (digital inputs)                                                                                                        | V <sub>IL</sub>    | Pin Groups 1, 2                    | -0.3   | —   | 0.8              | V      |

| Output Source Current High (at V <sub>OH</sub> min.)<br>When programmed for low drive strength<br>When programmed for high drive strength | I <sub>OH</sub>    | Pin Group 1<br>Pin Group 1         |        | _   | -4<br>-8         | mA     |

| Output Source Current Low (at V <sub>OL</sub> max.)<br>When programmed for low drive strength<br>When programmed for high drive strength  | I <sub>OL</sub>    | Pin Groups 1, 2<br>Pin Groups 1, 2 |        |     | 4<br>8           | mA     |

| Ambient Operating Temperature<br>(Automotive)                                                                                             | T <sub>A</sub>     |                                    | -40    |     | 125              | °C     |

| Ambient Operating Temperature (Industrial)                                                                                                | T <sub>A</sub>     |                                    | -40    | —   | 105              | °C     |

| Flash Endurance (Automotive)<br>(Program Erase Cycles)                                                                                    | N <sub>F</sub>     | T <sub>A</sub> = -40°C to<br>125°C | 10,000 | —   | —                | Cycles |

| Flash Endurance (Industrial)<br>(Program Erase Cycles)                                                                                    | N <sub>F</sub>     | T <sub>A</sub> = -40°C to<br>105°C | 10,000 | —   | _                | Cycles |

| Flash Data Retention                                                                                                                      | T <sub>R</sub>     | T <sub>J</sub> <= 85°C avg         | 15     | —   | —                | Years  |

| Flash Data Retention with <100<br>Program/Erase Cycles                                                                                    | t <sub>FLRET</sub> | T <sub>J</sub> <= 85°C avg         | 20     | —   |                  | Years  |

Note: Total chip source or sink current cannot exceed 50mA

#### **Default Mode**

Pin Group 1: GPIO, TDI, TDO, TMS, TCK Pin Group 2: RESET, GPIOA7 Pin Group 3: ADC analog inputs

## **10.12** Inter-Integrated Circuit Interface (I<sup>2</sup>C) Timing

|                                                                                                     | -                    |                |                   |                                   |                  |      |  |

|-----------------------------------------------------------------------------------------------------|----------------------|----------------|-------------------|-----------------------------------|------------------|------|--|

| Characteristic                                                                                      | Symbol               | Standard Mode  |                   | Fast Mode                         |                  | Unit |  |

|                                                                                                     | Symbol               | Minimum        | Maximum           | Minimum                           | Maximum          | Unit |  |

| SCL Clock Frequency                                                                                 | f <sub>SCL</sub>     | 0              | 100               | 0                                 | 400              | kHz  |  |

| Hold time (repeated ) START<br>condition. After this period, the<br>first clock pulse is generated. | t <sub>HD;</sub> STA | 4.0            |                   | 0.6                               |                  | μS   |  |

| LOW period of the SCL clock                                                                         | t <sub>LOW</sub>     | 4.7            |                   | 1.25                              |                  | μs   |  |

| HIGH period of the SCL clock                                                                        | t <sub>HIGH</sub>    | 4.0            |                   | 0.6                               |                  | μS   |  |

| Set-up time for a repeated START condition                                                          | t <sub>SU; STA</sub> | 4.7            |                   | 0.6                               |                  | μS   |  |

| Data hold time for I <sup>2</sup> C bus devices                                                     | t <sub>HD; DAT</sub> | 0 <sup>1</sup> | 3.45 <sup>2</sup> | 0 <sup>1</sup>                    | 0.9 <sup>2</sup> | μs   |  |

| Data set-up time                                                                                    | t <sub>SU; DAT</sub> | 250            |                   | 100 <sup>3</sup>                  |                  | ns   |  |

| Rise time of both SDA and SCL signals                                                               | t <sub>r</sub>       |                | 1000              | 2 +0.1C <sub>b</sub> <sup>4</sup> | 300              | ns   |  |

| Fall time of both SDA and SCL signals                                                               | t <sub>f</sub>       |                | 300               | 2 +0.1C <sub>b</sub> <sup>4</sup> | 300              | ns   |  |

| Set-up time for STOP condition                                                                      | t <sub>SU; STO</sub> | 4.0            |                   | 0.6                               |                  | μS   |  |

| Bus free time between STOP and START condition                                                      | t <sub>BUF</sub>     | 4.7            |                   | 1.3                               |                  | μS   |  |

| Pulse width of spikes that must be suppressed by the input filter                                   | t <sub>SP</sub>      | N/A            | N/A               | 0.0                               | 50               | ns   |  |

#### Table 10-17 I<sup>2</sup>C Timing

A device must internally provide a hold time of at least 300ns for the SDA signal (referred to the V<sub>IH</sub> min of the SCL signal) to bridge the undefined region of the falling edge of SCL.

2. The maximum  $t_{HD; DAT}$  has only to be met if the device does not stretch the LOW period ( $t_{LOW}$ ) of the SCL signal.

3. A Fast mode I<sup>2</sup>C bus device can be used in a Standard mode I<sup>2</sup>C bus system, but the requirement  $t_{SU; DAT} > = 250$ ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line  $t_{rmax} + t_{SU; DAT} = 1000 + 250 = 1250$ ns (according to the Standard mode I<sup>2</sup>C bus specification) before the SCL line is released.

4.  $C_b$  = total capacitance of the one bus line in pF.

## 10.14 Analog-to-Digital Converter (ADC) Parameters

| Parameter                                                        | Symbol              | Min               | Тур              | Max               | Unit                                 |  |  |

|------------------------------------------------------------------|---------------------|-------------------|------------------|-------------------|--------------------------------------|--|--|

| DC Specifications                                                | ÷                   |                   |                  | •                 |                                      |  |  |

| Resolution                                                       | R <sub>ES</sub>     | 12                | _                | 12                | Bits                                 |  |  |

| ADC internal clock                                               | f <sub>ADIC</sub>   | 0.1               | _                | 5.33              | MHz                                  |  |  |

| Conversion range                                                 | R <sub>AD</sub>     | V <sub>REFL</sub> | _                | V <sub>REFH</sub> | V                                    |  |  |

| ADC power-up time <sup>2</sup>                                   | t <sub>ADPU</sub>   | —                 | 6                | 13                | t <sub>AIC</sub> cycles <sup>3</sup> |  |  |

| Recovery from auto standby                                       | t <sub>REC</sub>    | —                 | 0                | 1                 | t <sub>AIC</sub> cycles <sup>3</sup> |  |  |

| Conversion time                                                  | t <sub>ADC</sub>    | —                 | 6                |                   | t <sub>AIC</sub> cycles <sup>3</sup> |  |  |

| Sample time                                                      | t <sub>ADS</sub>    | —                 | 1                |                   | t <sub>AIC</sub> cycles <sup>3</sup> |  |  |

| Accuracy                                                         |                     |                   |                  |                   |                                      |  |  |

| Integral non-linearity <sup>4</sup><br>(Full input signal range) | INL                 | —                 | +/- 3            | +/- 5             | LSB <sup>5</sup>                     |  |  |

| Differential non-linearity                                       | DNL                 | —                 | +/6              | +/- 1             | LSB <sup>5</sup>                     |  |  |

| Monotonicity                                                     |                     | GUARANTEED        |                  |                   |                                      |  |  |

| Offset Voltage Internal Ref                                      | V <sub>OFFSET</sub> | —                 | +/- 4            | +/- 9             | mV                                   |  |  |

| Offset Voltage External Ref                                      | V <sub>OFFSET</sub> | —                 | +/- 6            | +/- 12            | mV                                   |  |  |

| Gain Error (transfer gain)                                       | E <sub>GAIN</sub>   | —                 | .998 to 1.002    | 1.01 to .99       | -                                    |  |  |

| ADC Inputs <sup>6</sup> (Pin Group 3)                            |                     |                   |                  |                   |                                      |  |  |

| Input voltage (external reference)                               | V <sub>ADIN</sub>   | V <sub>REFL</sub> | —                | V <sub>REFH</sub> | V                                    |  |  |

| Input voltage (internal reference)                               | V <sub>ADIN</sub>   | V <sub>SSA</sub>  | _                | V <sub>DDA</sub>  | V                                    |  |  |

| Input leakage                                                    | I <sub>IA</sub>     | —                 | 0                | +/- 2             | μΑ                                   |  |  |

| V <sub>REFH</sub> current                                        | I <sub>VREFH</sub>  | —                 | 0                | _                 | μΑ                                   |  |  |

| Input injection current <sup>7</sup> , per pin                   | I <sub>ADI</sub>    | —                 | —                | 3                 | mA                                   |  |  |

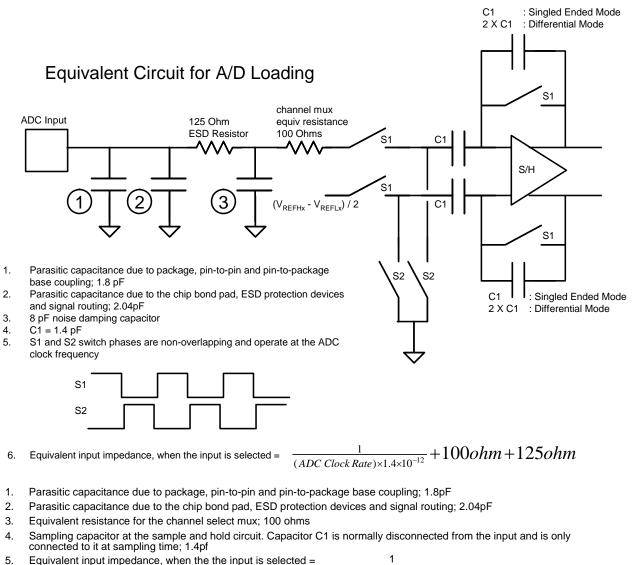

| Input capacitance                                                | C <sub>ADI</sub>    | —                 | See Figure 10-17 | _                 | pF                                   |  |  |

| Input impedance                                                  | X <sub>IN</sub>     | —                 | See Figure 10-17 |                   | Ohms                                 |  |  |

| AC Specifications                                                |                     | 11                |                  |                   |                                      |  |  |

| Signal-to-noise ratio                                            | SNR                 | 60                | 65               |                   | dB                                   |  |  |

| Total Harmonic Distortion                                        | THD                 | 60                | 64               | 1                 | dB                                   |  |  |

| Spurious Free Dynamic Range                                      | SFDR                | 61                | 66               | 1                 | dB                                   |  |  |

| Signal-to-noise plus distortion                                  | SINAD               | 58                | 62               |                   | dB                                   |  |  |

| Effective Number Of Bits                                         | ENOB                |                   | 10.0             | 1                 | Bits                                 |  |  |

#### Table 10-19 ADC Parameters<sup>1</sup>

1. All measurements were made at V<sub>DD</sub> = 3.3V, V<sub>REFH</sub> = 3.3V, and V<sub>REFL</sub> = ground

2. Includes power-up of ADC and  $\,V_{\mathsf{REF}}$

3. ADC clock cycles

4. INL measured from  $V_{IN} = V_{REFL}$  to  $V_{IN} = V_{REFH}$

- 5. LSB = Least Significant Bit = 0.806mV

- 6. Pin groups are detailed following **Table 10-1**.

- 7. The current that can be injected or sourced from an unselected ADC signal input without impacting the performance of the ADC.

#### **10.15 Equivalent Circuit for ADC Inputs**

**Figure 10-17** illustrates the ADC input circuit during sample and hold. S1 and S2 are always open/closed at the same time that S3 is closed/open. When S1/S2 are closed & S3 is open, one input of the sample and hold circuit moves to  $(V_{REFH}-V_{REFL})/2$ , while the other charges to the analog input voltage. When the switches are flipped, the charge on C1 and C2 are averaged via S3, with the result that a single-ended analog input is switched to a differential voltage centered about  $(V_{REFH}-V_{REFL})/2$ . The switches switch on every cycle of the ADC clock (open one-half ADC clock, closed one-half ADC clock). Note that there are additional capacitances associated with the analog input pad, routing, etc., but these do not filter into the S/H output voltage, as S1 provides isolation during the charge-sharing phase.

One aspect of this circuit is that there is an on-going input current, which is a function of the analog input voltage,  $V_{REF}$  and the ADC clock frequency.

(ADC Clock Rate) x 1.4 x 10<sup>-12</sup>

#### Figure 10-17 Equivalent Circuit for A/D Loading

### **10.16** Power Consumption

See Section 10.1 for a list of IDD requirements for the 56F8014. This section provides additional detail which can be used to optimize power consumption for a given application.

Power consumption is given by the following equation:

Total power = A: internal [static component]

+B: internal [state-dependent component] Please see http://www.freescale.com for the most current mechanical drawing.

## Part 11 Packaging

#### 11.1 56F8014 Package and Pin-Out Information

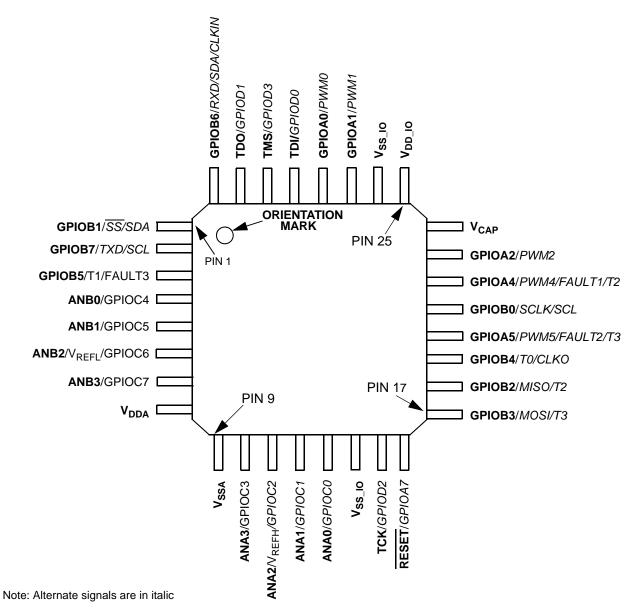

This section contains package and pin-out information for the 56F8014. This device comes in a 32-pin Low-profile Quad Flat Pack (LQFP). **Figure 11-1** shows the package outline for the 32-pin LQFP, **Figure 11-2** shows the mechanical parameters for this package, and **Table 11-1** lists the pin-out for the 32-pin LQFP.

Figure 11-1 Top View, 56F8014 32-Pin LQFP Package

56F8014 Technical Data, Rev. 11