# E·X Renesas Electronics America Inc - <u>UPD78F1177AGF-GAT-AX Datasheet</u>

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                |

| Core Processor             | 78K/0R                                                                                |

| Core Size                  | 16-Bit                                                                                |

| Speed                      | 20MHz                                                                                 |

| Connectivity               | 3-Wire SIO, EBI/EMI, I <sup>2</sup> C, LINbus, UART/USART                             |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                               |

| Number of I/O              | 111                                                                                   |

| Program Memory Size        | 384KB (384K x 8)                                                                      |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 24K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                           |

| Data Converters            | A/D 16x10b; D/A 2x8b                                                                  |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 128-LQFP                                                                              |

| Supplier Device Package    | -                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f1177agf-gat-ax |

|                            |                                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

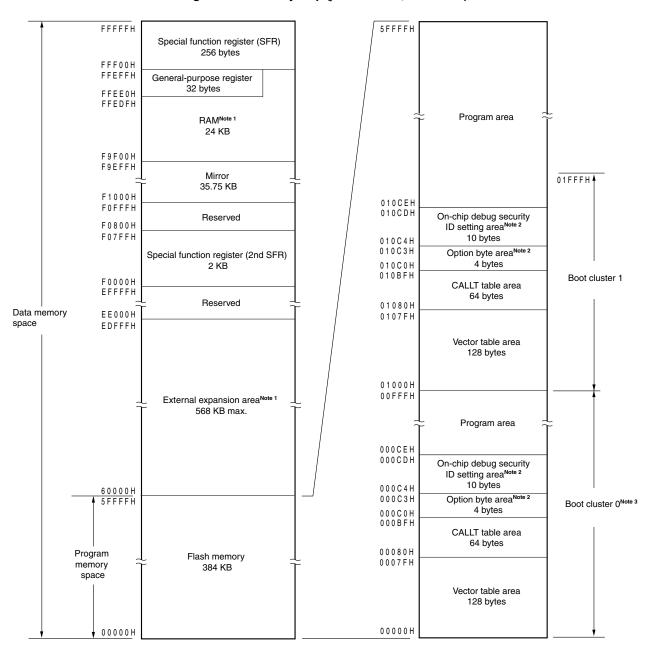

Figure 3-4. Memory Map (µPD78F1177, 78F1177A)

- **Notes 1.** Instructions can be executed from the RAM area excluding the general-purpose register area, and from the external expansion area.

- 2. When boot swap is not used: Set the option bytes to 000C0H to 000C3H, and the on-chip debug security IDs to 000C4H to 000CDH.

When boot swap is used: Set the option bytes to 000C0H to 000C3H and 010C0H to 010C3H, and the on-chip debug security IDs to 000C4H to 000CDH and 010C4H to 010CDH.

Writing boot cluster 0 can be prohibited depending on the setting of security (see 25.7 Security Setting).

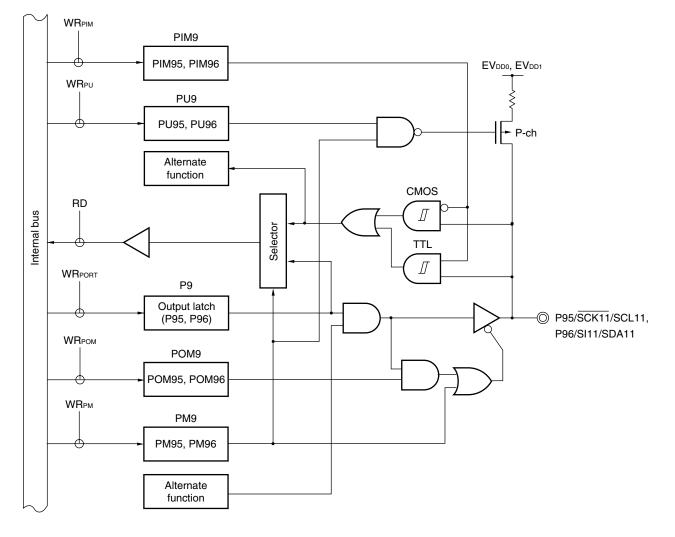

Figure 4-34. Block Diagram of P95 and P96

- P9: Port register 9

- PU9: Pull-up resistor option register 9

- PM9: Port mode register 9

- PIM9: Port input mode register 9

- POM9: Port output mode register 9

- RD: Read signal

- WR××: Write signal

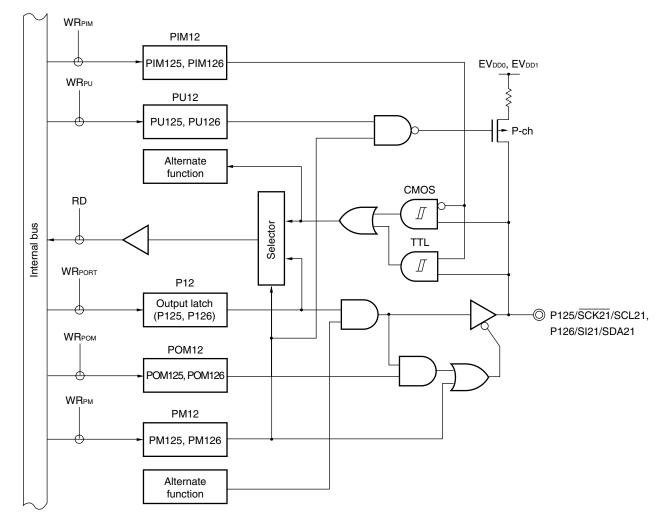

Figure 4-41. Block Diagram of P125 and P126

- P12: Port register 12

- PU12: Pull-up resistor option register 12

- PM12: Port mode register 12

- PIM12: Port input mode register 12

- POM12: Port output mode register 12

- RD: Read signal

- WR××: Write signal

#### (7) Operation speed mode control register (OSMC)

This register is used to control the step-up circuit of the flash memory for high-speed operation.

If the microcontroller operates at a low speed with a system clock of 10 MHz or less, the power consumption can be lowered by setting this register to the default value, 00H.

OSMC can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

#### Figure 6-8. Format of Operation Speed Mode Control Register (OSMC)

Address: F00F3H After reset: 00H R/W

| Symbol | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0    |

|--------|---|---|---|---|---|---|---|------|

| OSMC   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | FSEL |

| FSEL | fclk frequency selection                             |  |  |  |  |

|------|------------------------------------------------------|--|--|--|--|

| 0    | Dperates at a frequency of 10 MHz or less (default). |  |  |  |  |

| 1    | Operates at a frequency higher than 10 MHz.          |  |  |  |  |

Cautions 1. OSMC can be written only once after reset release, by an 8-bit memory manipulation instruction.

- 2. Write "1" to FSEL before the following two operations.

- Changing the clock prior to dividing fcLK to a clock other than fill.

- Operating the DMA controller.

- 3. The CPU waits when "1" is written to the FSEL flag.

Interrupt requests issued during a wait will be suspended.

The wait time is 16.6  $\mu$ s to 18.5  $\mu$ s when fclk = fiH, and 33.3  $\mu$ s to 36.9  $\mu$ s when fclk = fiH/2.

However, counting the oscillation stabilization time of fx can continue even while the CPU is waiting.

4. To increase fcLk to 10 MHz or higher, set FSEL to "1", then change fcLk after two or more clocks have elapsed. Use the external bus interface two clock cycles after setting FSEL to 1.

<R>

<R>

5. Flash memory can be used at a frequency of 10 MHz or lower if FSEL is 1.

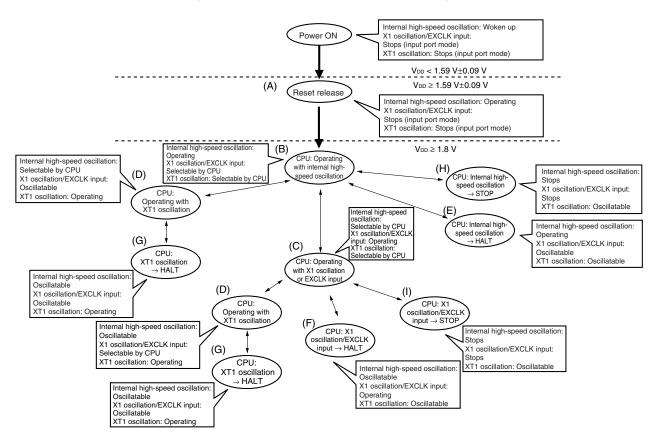

#### 6.6.5 CPU clock status transition diagram

Figure 6-15 shows the CPU clock status transition diagram of this product.

**Remark** If the low-power-supply detector (LVI) is set to ON by default by the option bytes, the reset will not be released until the power supply voltage (V<sub>DD</sub>) exceeds 2.07 V±0.2 V. After the reset operation, the status will shift to (B) in the above figure.

### Figure 7-24. Format of Noise Filter Enable Register 2 (NFEN2)

| Address: F00 | 62H After re | eset: 00H | R/W |   |         |         |         |         |

|--------------|--------------|-----------|-----|---|---------|---------|---------|---------|

| Symbol       | 7            | 6         | 5   | 4 | 3       | 2       | 1       | 0       |

| NFEN2        | 0            | 0         | 0   | 0 | TNFEN13 | TNFEN12 | TNFEN11 | TNFEN10 |

| TNFEN13 | Enable/disable using noise filter of TI13/TO13/P163 pin input signal |  |  |  |

|---------|----------------------------------------------------------------------|--|--|--|

| 0       | Noise filter OFF                                                     |  |  |  |

| 1       | Noise filter ON                                                      |  |  |  |

| TNFEN12 | Enable/disable using noise filter of TI12/TO12/P162 pin input signal |  |  |  |  |

|---------|----------------------------------------------------------------------|--|--|--|--|

| 0       | Noise filter OFF                                                     |  |  |  |  |

| 1       | Noise filter ON                                                      |  |  |  |  |

| TNFEN11 | Enable/disable using noise filter of TI11/TO11/P161 pin input signal |  |  |  |  |

|---------|----------------------------------------------------------------------|--|--|--|--|

| 0       | Noise filter OFF                                                     |  |  |  |  |

| 1       | Noise filter ON                                                      |  |  |  |  |

| TNFEN10 | Enable/disable using noise filter of TI10/TO10/P160 pin input signal |  |  |  |  |

|---------|----------------------------------------------------------------------|--|--|--|--|

| 0       | Noise filter OFF                                                     |  |  |  |  |

| 1       | Noise filter ON                                                      |  |  |  |  |

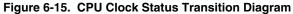

#### Figure 7-51. Example of Set Contents of Registers to Measure Input Pulse Interval

#### Figure 7-56. Operation Procedure When Input Signal High-/Low-Level Width Measurement Function Is Used

|                               | Software Operation                                                                                                                                                                                                         | Hardware Status                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TAU<br>default<br>setting     |                                                                                                                                                                                                                            | Power-off status<br>(Clock supply is stopped and writing to each register is<br>disabled.)                                                                                                                                                                                                                                                                                                                                                    |

|                               | Sets the TAU0EN bit, TAU1EN bit of the PER0 register to 1                                                                                                                                                                  | Power-on status. Each channel stops operating.<br>(Clock supply is started and writing to each register is<br>enabled.)                                                                                                                                                                                                                                                                                                                       |

|                               | Sets the TPSm register.<br>Determines clock frequencies of CKm0 and CKm1.                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Channel<br>default<br>setting | Sets the TMRmn register (determines operation mode of channel).<br>Clears TOEmn to 0 and stops operation of TOmn.                                                                                                          | Channel stops operating.<br>(Clock is supplied and some power is consumed.)                                                                                                                                                                                                                                                                                                                                                                   |

| Operation<br>start            | Sets the TSmn bit to 1.<br>The TSmn bit automatically returns to 0 because it is a<br>trigger bit.                                                                                                                         | TEmn = 1, and the TImn pin start edge detection wait status is set.                                                                                                                                                                                                                                                                                                                                                                           |

|                               | Detects TImn pin input count start valid edge.                                                                                                                                                                             | Clears TCRmn to 0000H and starts counting up.                                                                                                                                                                                                                                                                                                                                                                                                 |

| During<br>operation           | Set value of the TDRmn register can be changed.<br>The TCRmn register can always be read.<br>The TSRmn register is not used.<br>Set values of the TMRmn register, TOMmn, TOLmn,<br>TOmn, and TOEmn bits cannot be changed. | When the TImn pin start edge is detected, the counter<br>(TCRmn) counts up from 0000H. If a capture edge of the<br>TImn pin is detected, the count value is transferred to<br>TDRmn and INTTMmn is generated.<br>If an overflow occurs at this time, the OVF bit of the<br>TSRmn register is set; if an overflow does not occur, the<br>OVF bit is cleared. TCRmn stops the count operation unti<br>the next TImn pin start edge is detected. |

| Operation<br>stop             | The TTmn bit is set to 1.<br>TTmn bit automatically returns to 0 because it is a<br>trigger bit.                                                                                                                           | <ul> <li>TEmn = 0, and count operation stops.</li> <li>TCRmn holds count value and stops.</li> <li>The OVF bit of the TSRmn register is also held.</li> </ul>                                                                                                                                                                                                                                                                                 |

| TAU stop                      | The TAU0EN bit, TAU1EN bit of PER0 register is cleared to 0.                                                                                                                                                               | Power-off status<br>All circuits are initialized and SFR of each channel is<br>also initialized.                                                                                                                                                                                                                                                                                                                                              |

**Remark** m: Unit number (m = 0, 1), n: Channel number (n = 0 to 7), mn = 00 to 07, 10 to 13

|                               | Software Operation                                                                                                                                                                                                                                          | Hardware Status                                                                                                                                                    |  |  |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TAU<br>default<br>setting     |                                                                                                                                                                                                                                                             | Power-off status<br>(Clock supply is stopped and writing to each register is<br>disabled.)                                                                         |  |  |

|                               | Sets the TAU0EN bit, TAU0EN bit of the PER0 register to 1.                                                                                                                                                                                                  | Power-on status. Each channel stops operating.<br>(Clock supply is started and writing to each register is<br>enabled.)                                            |  |  |

|                               | Sets the TPSm register.<br>Determines clock frequencies of CKm0 and CKm1.                                                                                                                                                                                   |                                                                                                                                                                    |  |  |

| Channel<br>default<br>setting | Sets the TMRmn and TMRmp registers of two channels<br>to be used (determines operation mode of channels).<br>An output delay is set to the TDRmn register of the<br>master channel, and a pulse width is set to the TDRmp<br>register of the slave channel. | Channel stops operating.<br>(Clock is supplied and some power is consumed.)                                                                                        |  |  |

|                               | Sets slave channel.<br>The TOMmp bit of the TOMm register is set to 1<br>(combination-operation mode).<br>Sets the TOLmp bit.<br>Sets the TOmp bit and determines default level of the<br>TOmp output.                                                      | The TOmp pin goes into Hi-Z output state.<br>The TOmp default setting level is output when the port<br>mode register is in output mode and the port register is 0. |  |  |

|                               | Sets TOLINP to T and enables operation of TOMP.                                                                                                                                                                                                             | <ul> <li>TOmp does not change because channel stops operating.</li> <li>The TOmp pin outputs the TOmp set level.</li> </ul>                                        |  |  |

#### Figure 7-66. Operation Procedure of One-Shot Pulse Output Function (1/2)

**Remark** m: Unit number, n: Channel number, p: Slave channel number (p = n+1),

When m = 0: n = 0, 2, 4, 6When m = 1: n = 0, 2

#### (10) Week count register (WEEK)

The WEEK register is an 8-bit register that takes a value of 0 to 6 (decimal) and indicates the count value of weekdays.

It counts up in synchronization with the day counter.

When data is written to this register, it is written to a buffer and then to the counter up to 2 clocks (32.768 kHz) later. Set a decimal value of 00 to 06 to this register in BCD code. If a value outside the range is set, the register value returns to the normal value after 1 period.

WEEK can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

#### Figure 8-11. Format of Week Count Register (WEEK)

| Address: FFF | 95H After re | eset: 00H F | /W |   |   |       |       |       |

|--------------|--------------|-------------|----|---|---|-------|-------|-------|

| Symbol       | 7            | 6           | 5  | 4 | 3 | 2     | 1     | 0     |

| WEEK         | 0            | 0           | 0  | 0 | 0 | WEEK4 | WEEK2 | WEEK1 |

Caution The value corresponding to the month count register or the day count register is not stored in the week count register automatically. After reset release, set the week count register as follow.

| Day       | WEEK |  |  |

|-----------|------|--|--|

| Sunday    | 00H  |  |  |

| Monday    | 01H  |  |  |

| Tuesday   | 02H  |  |  |

| Wednesday | 03H  |  |  |

| Thursday  | 04H  |  |  |

| Friday    | 05H  |  |  |

| Saturday  | 06H  |  |  |

#### (3) 10-bit A/D conversion result register (ADCR)

This register is a 16-bit register that stores the A/D conversion result. The lower 6 bits are fixed to 0. Each time A/D conversion ends, the conversion result is loaded from the successive approximation register. The higher 8 bits of the conversion result are stored in FFF1FH and the lower 2 bits are stored in the higher 2 bits of FFF1EH. ADCR can be read by a 16-bit memory manipulation instruction.

Reset signal generation clears this register to 0000H.

#### Figure 11-7. Format of 10-Bit A/D Conversion Result Register (ADCR)

Address: FFF1FH, FFF1EH After reset: 0000H R

| Symbol | CFFF1FH |  |  |  |  |  | <br>FFF1EH |  |  |   |   |   |   |   |   |

|--------|---------|--|--|--|--|--|------------|--|--|---|---|---|---|---|---|

| ADCR   |         |  |  |  |  |  |            |  |  | 0 | 0 | 0 | 0 | 0 | 0 |

Caution When writing to the A/D converter mode register (ADM), analog input channel specification register (ADS), and A/D port configuration register (ADPC), the contents of ADCR may become undefined. Read the conversion result following conversion completion before writing to ADM, ADS, and ADPC. Using timing other than the above may cause an incorrect conversion result to be read.

#### (4) 8-bit A/D conversion result register (ADCRH)

This register is an 8-bit register that stores the A/D conversion result. The higher 8 bits of 10-bit resolution are stored.

ADCRH can be read by an 8-bit memory manipulation instruction. Reset signal generation clears this register to 00H.

#### Figure 11-8. Format of 8-Bit A/D Conversion Result Register (ADCRH)

| Address: F | FF1FH | After reset: | 00H R |   |   |   |   |   |  |

|------------|-------|--------------|-------|---|---|---|---|---|--|

| Symbol     | 7     | 6            | 5     | 4 | 3 | 2 | 1 | 0 |  |

| ADCRH      |       |              |       |   |   |   |   |   |  |

Caution When writing to the A/D converter mode register (ADM), analog input channel specification register (ADS), and A/D port configuration register (ADPC), the contents of ADCRH may become undefined. Read the conversion result following conversion completion before writing to ADM, ADS, and ADPC. Using timing other than the above may cause an incorrect conversion result to be read.

The D/A converter includes the following hardware.

Table 12-1. Configuration of D/A Converter

| Item              | Configuration                                                                                                                                |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Control registers | Peripheral enable register 0 (PER0)<br>D/A converter mode register (DAM)<br>8-bit D/A conversion value setting registers 0, 1 (DACS0, DACS1) |

#### (1) AVREF1 pin

This is the D/A converter reference voltage input pin and the positive power supply pin of P110, P111, and the D/A converter.

The voltage that can be supplied to AV<sub>REF1</sub> varies as follows, depending on whether the P110/ANO0 and P111/ANO1 pins are used as digital I/Os or analog outputs.

| Analog/Digital                                                                    | VDD Condition                         | AV <sub>REF1</sub> Voltage                                                                   |  |  |

|-----------------------------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------|--|--|

| Using at least one pin as an analog output and using all pins not as digital I/Os | $1.8~V \leq V_{\text{DD}} \leq 5.5~V$ | $1.8 \ V \leq AV_{\text{REF1}} \leq V_{\text{DD}} = EV_{\text{DD0}} = EV_{\text{DD1}}$       |  |  |

| Pins used as analog outputs and digital I/Os are                                  | $2.7~V \leq V_{\text{DD}} \leq 5.5~V$ | $2.7 \text{ V} \leq AV_{\text{REF1}} \leq V_{\text{DD}} = EV_{\text{DD0}} = EV_{\text{DD1}}$ |  |  |

| mixed <sup>Note</sup>                                                             | $1.8~V \leq V_{\text{DD}} < 2.7~V$    | AVREF1 has same potential as EVDD0,<br>EVDD1, and VDD                                        |  |  |

| Using at least one pin as a digital I/O and using all pins                        | $2.7~V \leq V_{\text{DD}} \leq 5.5~V$ | $2.7 \text{ V} \leq AV_{\text{REF1}} \leq V_{\text{DD}} = EV_{\text{DD0}} = EV_{\text{DD1}}$ |  |  |

| not as analog outputs <sup>№te</sup>                                              | $1.8~V \leq V_{\text{DD}} < 2.7~V$    | AVREF1 has same potential as EVDD0,<br>EVDD1, and VDD                                        |  |  |

**Note** AVREF1 is the reference for the I/O voltage of a port to be used as a digital port.

• High-/low-level input voltage (VIH5/VIL5)

• High-/low-level output voltage (VOH2/VOL2)

#### 12.4.3 Cautions

Observe the following cautions when using the D/A converter of the 78K0R/KH3.

(1) The digital port I/O function, which is the alternate function of the ANO0 and ANO1 pins, does not operate during D/A conversion.

During D/A conversion, 0 is read from the P11 register in input mode.

- (2) Do not read/write the P11 register and do not change the setting of the PM11 register during D/A conversion (otherwise the conversion accuracy may decrease).

- (3) It is recommended that both the ANO0 and ANO1 pins be used as analog output pins or digital I/O pins, that is, use these two channels for the same application (if these pins are used for the different applications, the conversion accuracy may decrease).

- (4) In the real-time output mode, set the DACSn register value before the timer trigger is generated. In addition, do not change the set value of the DACSn register while the trigger signal is output.

- (5) Before changing the operation mode, be sure to clear the DACEn bit of the DAM register to 0 (D/A conversion stop).

- (6) When using the port that functions alternately as the ANO0 or ANO1 pin, use it as the port input with few level changes.

<R>

<R>

- (7) Stop the conversion performed by the D/A converter when supplying AV<sub>REF1</sub> or AV<sub>REF0</sub> (the reference voltages for the A/D converter) starts or stops.

- (8) Because the D/A converter stops operation in the STOP mode, the ANO0 and ANO1 pins go into a high-impedance state, and the power consumption can be reduced.

In the standby modes other than the STOP mode, however, the operation continues. To lower the power consumption, therefore, clear the DACEn bit of the DAM register to 0 (D/A conversion stop).

- (9) Since the output impedance of the D/A converter is high, the current cannot be obtained from the ANOn pin (n = 0, 1). When the input impedance of the load is low, insert a follower amplifier between the load and ANOn pin keeping the wiring length as short as possible (for high impedance). If the wiring becomes too long, take necessary actions such as surrounding with a ground pattern.

#### (2) Operation procedure

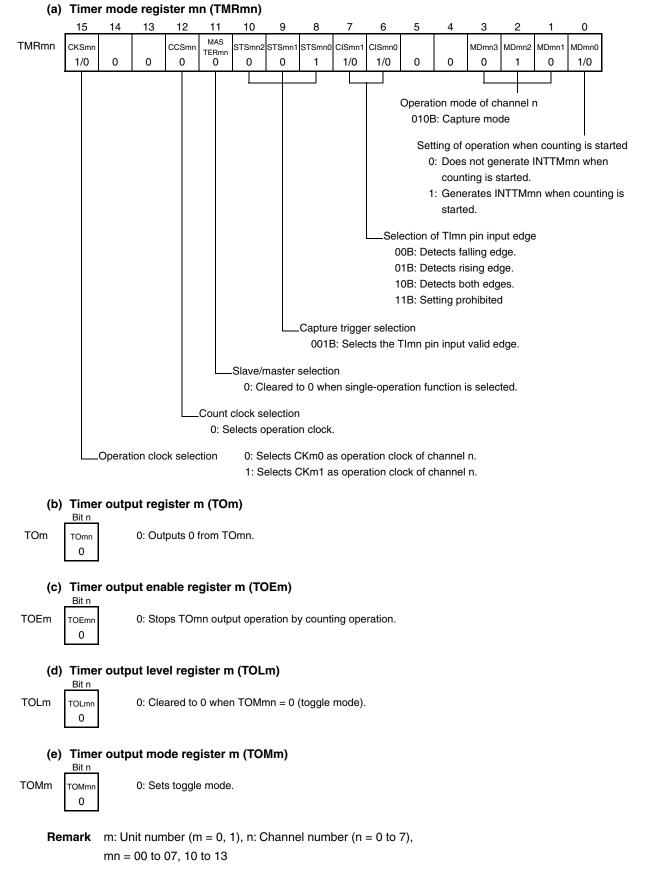

#### Figure 13-94. Initial Setting Procedure for Address Field Transmission

Caution After setting the PER0 register to 1, be sure to set the SPSm register after 4 or more clocks have elapsed.

## 13.7.6 Procedure for processing errors that occurred during simplified I<sup>2</sup>C (IIC10, IIC11, IIC20, IIC21) communication

The procedure for processing errors that occurred during simplified I<sup>2</sup>C (IIC10, IIC11, IIC20, IIC21) communication is described in Figures 13-105 and 13-106.

| Figure 13-105. | Processing | Procedure in     | Case of Parity | Error or ( | Overrun Error |

|----------------|------------|------------------|----------------|------------|---------------|

| rigate to too. | riccoonig  | i i oocaai o iii | oute of func   |            |               |

<R>

| Software Manipulation  | Hardware Status                                    | Remark                                                                                                                                                                 |

|------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reads SDRmn register.  | BFF = 0, and channel n is enabled to receive data. | This is to prevent an overrun error if<br>the next reception is completed<br>during error processing.                                                                  |

| Reads SSRmn register.  |                                                    | Error type is identified and the read value is used to clear error flag.                                                                                               |

| Writes SIRmn register. | <ul> <li>Error flag is cleared.</li> </ul>         | Only error generated at the point of<br>reading can be cleared, by writing<br>the value read from the SSRmn<br>register to the SIRmn register<br>without modification. |

#### Figure 13-106. Processing Procedure in Case of Parity Error (ACK error) in Simplified I<sup>2</sup>C Mode

| Software Manipulation    | Hardware Status                                    | Remark                                                                                                                                                                                                               |

|--------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reads SDRmn register.    | BFF = 0, and channel n is enabled to receive data. | This is to prevent an overrun error if<br>the next reception is completed<br>during error processing.                                                                                                                |

| Reads SSRmn register.    |                                                    | Error type is identified and the read value is used to clear error flag.                                                                                                                                             |

| Writes SIRmn register.   | ► Error flag is cleared.                           | Only error generated at the point of<br>reading can be cleared, by writing<br>the value read from the SSRmn<br>register to the SIRmn register<br>without modification.                                               |

| Sets STmn bit to 1.      | ► SEmn = 0, and channel n stops operation.         | Slave is not ready for reception<br>because ACK is not returned.<br>Therefore, a stop condition is<br>created, the bus is released, and<br>communication is started again from<br>the start condition. Or, a restart |

| Creates stop condition.  |                                                    | condition is generated and<br>transmission can be redone from                                                                                                                                                        |

| Creates start condition. |                                                    | address transmission.                                                                                                                                                                                                |

| Sets SSmn bit to 1.      | SEmn = 1, and channel n is enabled to operate.     |                                                                                                                                                                                                                      |

**Remark** m: Unit number (m = 0, 1), n: Channel number (n = 0 to 3), mn = 02, 03, 10, 11

#### **Operation example 2: When used as interrupt**

Interrupt requests may be generated frequently. Take the following action.

#### <Action>

Confirm that "supply voltage (V<sub>DD</sub>)  $\geq$  detection voltage (V<sub>LVI</sub>)" when detecting the falling edge of V<sub>DD</sub>, or "supply voltage (V<sub>DD</sub>) < detection voltage (V<sub>LVI</sub>)" when detecting the rising edge of V<sub>DD</sub>, in the servicing routine of the LVI interrupt by using bit 0 (LVIF) of the low-voltage detection register (LVIM). Clear bit 1 (LVIIF) of interrupt request flag register 0L (IF0L) to 0.

For a system with a long supply voltage fluctuation period near the LVI detection voltage, take the above action after waiting for the supply voltage fluctuation time.

- **Remark** If bit 2 (LVISEL) of the low voltage detection register (LVIM) is set to "1", the meanings of the above words change as follows.

- Supply voltage (V<sub>DD</sub>)  $\rightarrow$  Input voltage from external input pin (EXLVI)

- Detection voltage (VLVI)  $\rightarrow$  Detection voltage (VEXLVI = 1.21 V)

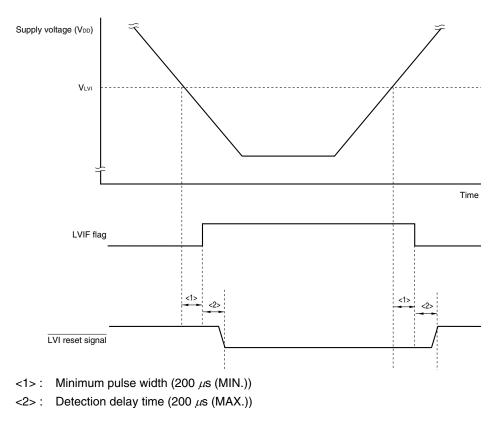

- (2) Delay from the time LVI reset source is generated until the time LVI reset has been generated or released There is some delay from the time supply voltage (VDD) < LVI detection voltage (VLVI) until the time LVI reset has been generated.

In the same way, there is also some delay from the time LVI detection voltage (V<sub>LVI</sub>)  $\leq$  supply voltage (V<sub>DD</sub>) until the time LVI reset has been released (see **Figure 22-12**).

See the timing in Figure 21-2 (2) When LVI is ON upon power application (option byte: LVIOFF = 0) for the reset processing time until the normal operation is entered after the LVI reset is released.

#### 25.8 Processing Time of Each Command When Using PG-FP4 or PG-FP5 (Reference Values)

The processing time of each command (reference values) when using PG-FP4 or PG-FP5 as the dedicated flash memory programmer is shown below.

| PG-FP4     |                   | Port: UART  |             |             |             |               |             |             |             |             |

|------------|-------------------|-------------|-------------|-------------|-------------|---------------|-------------|-------------|-------------|-------------|

| Command    | Speed: 115200 bps |             |             |             |             | Speed: 1 Mbps |             |             |             |             |

|            | μΡD78F1174,       | μΡD78F1175, | μΡD78F1176, | μΡD78F1177, | μΡD78F1178, | μΡD78F1174,   | μΡD78F1175, | μΡD78F1176, | μΡD78F1177, | μΡD78F1178, |

|            | μΡD78F1174A       | μΡD78F1175A | μΡD78F1176A | μΡD78F1177A | μΡD78F1178A | μΡD78F1174A   | μΡD78F1175A | μΡD78F1176A | μΡD78F1177A | μΡD78F1178A |

| Signature  | 1 s               | 1 s         | 1 s         | 1 s         | 1 s         | 0.5 s         | 0.5 s       | 0.5 s       | 1 s         | 1 s         |

|            | (TYP.)            | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)        | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      |

| Blankcheck | 1 s               | 1.5 s       | 1.5 s       | 2 s         | 2.5 s       | 1 s           | 1 s         | 1.5 s       | 2 s         | 2.5 s       |

|            | (TYP.)            | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)        | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      |

| Erase      | 1 s               | 1.5 s       | 1.5 s       | 2 s         | 2.5 s       | 1 s           | 1.5 s       | 1.5 s       | 2 s         | 2.5 s       |

|            | (TYP.)            | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)        | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      |

| Program    | 19 s              | 26.5 s      | 35 s        | 51.5 s      | 68.5 s      | 6.5 s         | 9 s         | 12 s        | 17.5 s      | 23 s        |

|            | (TYP.)            | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)        | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      |

| Verify     | 16 s              | 23.5 s      | 31 s        | 46 s        | 61 s        | 4.5 s         | 6 s         | 8 s         | 11.5 s      | 15.5 s      |

|            | (TYP.)            | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)        | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      |

| E.P.V      | 20 s              | 28 s        | 36.5 s      | 53.5 s      | 71 s        | 7.5 s         | 10.5 s      | 13.5 s      | 19.5 s      | 25.5 s      |

|            | (TYP.)            | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)        | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      |

| Checksum   | 1 s               | 1.5 s       | 1.5 s       | 2 s         | 2.5 s       | 1 s           | 1.5 s       | 1.5 s       | 2 s         | 2.5 s       |

|            | (TYP.)            | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)        | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      |

| Security   | 1 s               | 1 s         | 1 s         | 1 s         | 1 s         | 0.5 s         | 0.5 s       | 0.5 s       | 1 s         | 1 s         |

|            | (TYP.)            | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)        | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      |

Table 25-9. Processing Time of Each Command When Using PG-FP4 (Reference Values)

Table 25-10.

Processing Time of Each Command When Using PG-FP5 (Reference Values)

| PG-FP5    |                   | Port: UART  |             |             |             |               |             |             |             |             |

|-----------|-------------------|-------------|-------------|-------------|-------------|---------------|-------------|-------------|-------------|-------------|

| Command   | Speed: 115200 bps |             |             |             |             | Speed: 1 Mbps |             |             |             |             |

|           | μΡD78F1174,       | μΡD78F1175, | μΡD78F1176, | μΡD78F1177, | μΡD78F1178, | μΡD78F1174,   | μΡD78F1175, | μΡD78F1176, | μΡD78F1177, | μΡD78F1178, |

|           | μΡD78F1174A       | μΡD78F1175A | μΡD78F1176A | μΡD78F1177A | μΡD78F1178A | μΡD78F1174A   | μΡD78F1175A | μΡD78F1176A | μΡD78F1177A | μΡD78F1178A |

| Signature | 0.5 s             | 0.5 s       | 0.5 s       | 0.5 s       | 0.5 s       | 0.5 s         | 0.5 s       | 0.5 s       | 0.5 s       | 0.5 s       |

| read      | (TYP.)            | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)        | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      |

| Blank     | 1 s               | 1 s         | 1 s         | 2 s         | 2.5 s       | 1 s           | 1 s         | 1 s         | 2 s         | 2.5 s       |

| check     | (TYP.)            | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)        | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      |

| Erase     | 1 s               | 1 s         | 1.5 s       | 2 s         | 2.5 s       | 1 s           | 1 s         | 1.5 s       | 2 s         | 2.5 s       |

|           | (TYP.)            | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)        | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      |

| Program   | 17.5 s            | 26 s        | 34 s        | 51 s        | 67.5 s      | 6 s           | 8.5 s       | 11 s        | 16.5 s      | 22 s        |

|           | (TYP.)            | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)        | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      |

| Verify    | 15.5 s            | 23 s        | 30.5 s      | 45.5 s      | 60 s        | 4 s           | 5.5 s       | 7.5 s       | 11 s        | 14 s        |

|           | (TYP.)            | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)        | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      |

| Auto-     | 18 s              | 26.5 s      | 35 s        | 52 s        | 69 s        | 6 s           | 9 s         | 12 s        | 18 s        | 23.5 s      |

| procedure | (TYP.)            | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)        | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      |

| Checksum  | 1 s               | 1.5 s       | 1.5 s       | 2 s         | 2.5 s       | 1 s           | 1.5 s       | 1.5 s       | 2 s         | 2.5 s       |

|           | (TYP.)            | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)        | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      |

| Security  | 0.5 s             | 0.5 s       | 0.5 s       | 0.5 s       | 0.5 s       | 0.5 s         | 0.5 s       | 0.5 s       | 0.5 s       | 0.5 s       |

|           | (TYP.)            | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)        | (TYP.)      | (TYP.)      | (TYP.)      | (TYP.)      |

| Communication<br>Mode | Flash Memory<br>Programming<br>Function | Debugging Function                                        |

|-----------------------|-----------------------------------------|-----------------------------------------------------------|

| 1-line mode           | Available                               | Pseudo real-time RAM monitor (RRM) function not supported |

| 2-line mode           | None                                    | Pseudo real-time RAM monitor (RRM) function supported     |

**Remark** 2-line mode is not used for flash programming, however, even if TOOL1 pin is connected with CLK\_IN of QB-MINI2, writing is performed normally with no problem.

#### 26.2 On-Chip Debug Security ID

The 78K0R/KH3 has an on-chip debug operation control bit in the flash memory at 000C3H (see **CHAPTER 24 OPTION BYTE**) and an on-chip debug security ID setting area at 000C4H to 000CDH, to prevent third parties from reading memory content.

When the boot swap function is used, also set a value that is the same as that of 010C3H and 010C4H to 010CDH in advance, because 000C3H, 000C4H to 000CDH and 010C3H, and 010C4H to 010CDH are switched.

For details on the on-chip debug security ID, refer to the QB-MINI2 On-Chip Debug Emulator with Programming Function User's Manual (U18371E).

#### Table 26-2. On-Chip Debug Security ID

| Address          | On-Chip Debug Security ID |  |  |  |

|------------------|---------------------------|--|--|--|

| 000C4H to 000CDH | Any ID code of 10 bytes   |  |  |  |

| 010C4H to 010CDH |                           |  |  |  |

#### 26.3 Securing of user resources

To perform communication between the 78K0R/KH3 and QB-MINI2, as well as each debug function, the securing of memory space must be done beforehand.

If NEC Electronics assembler RA78K0R or compiler CC78K0R is used, the items can be set by using linker options.

#### (1) Securement of memory space

The shaded portions in Figure 26-2 are the areas reserved for placing the debug monitor program, so user programs or data cannot be allocated in these spaces. When using the on-chip debug function, these spaces must be secured so as not to be used by the user program. Moreover, this area must not be rewritten by the user program.

#### Flash Memory Programming Characteristics

#### $(T_{A} = -40 \text{ to } +85^{\circ}\text{C}, 2.7 \text{ V} \le \text{V}_{DD} = \text{EV}_{DD0} = \text{EV}_{DD1} \le 5.5 \text{ V}, \text{V}_{SS} = \text{EV}_{SS0} = \text{EV}_{SS1} = 0 \text{ V})$

| Parameter                                        | Symbol | Conditions                                                                                                                          |                         | MIN.   | TYP. | MAX. | Unit  |

|--------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------|------|------|-------|

| VDD supply current                               | IDD    | TYP. = 10 MHz, MAX. = 20 MHz                                                                                                        |                         | 4.5    | 15   | mA   |       |

| CPU/peripheral hardware<br>clock frequency       | fс∟к   |                                                                                                                                     |                         | 2      |      | 20   | MHz   |

| Number of rewrites (number of deletes per block) | Cwrt   | Used for updating programs<br>When using flash memory programmer<br>and NEC Electronics self programming<br>library                 |                         | 100    |      |      | Times |

|                                                  |        | Used for updating data<br>When using NEC Electronics EEPROM<br>emulation library (usable ROM size: 6<br>KB of 3 consecutive blocks) | Retained<br>for 3 years | 10,000 |      |      | Times |

#### (a) Conventional-specification products (µPD78F117x)

Remark When updating data multiple times, use the flash memory as one for updating data.

#### Symbol MIN. TYP. MAX. Parameter Conditions Unit VDD supply current ldd TYP. = 10 MHz, MAX. = 20 MHz 4.5 15 mΑ CPU/peripheral hardware 2 MHz **f**clk 20 clock frequency <R> CWRT Number of rewrites (number Used for updating programs Retained 1000 Times of deletes per block) When using flash memory programmer for 15 and NEC Electronics self programming years library 10,000 Used for updating data Retained Times When using NEC Electronics EEPROM for 5 years emulation library (usable ROM size: 6 KB of 3 consecutive blocks)

#### (b) Expanded-specification products ( $\mu$ PD78F117xA)

**Remark** When updating data multiple times, use the flash memory as one for updating data.

(A) Grade Products

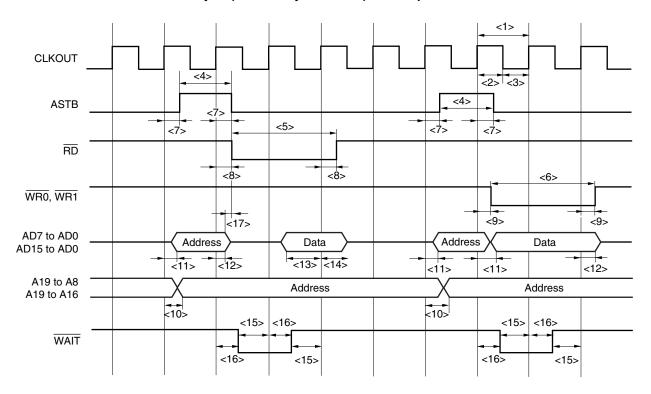

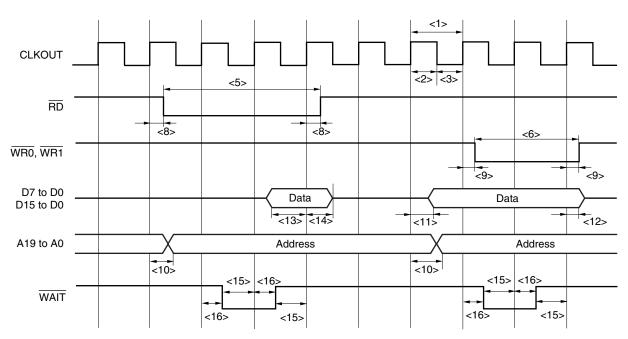

#### (2) External bus interface (2/4)

Read/write cycle (CLKOUT synchronous): In separate bus mode

Read/write cycle (CLKOUT synchronous): In multiplexed bus mode