#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 40                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1.375K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                                |

| Data Converters            | A/D 7x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89lp51rc2-20au |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

] P1.2 (ECI) ] P1.1 (T2 EX/<u>SS</u>) ] P1.0 (T2/XTAL1B‡)

З 2 ō 44 43 42 41

🗖 P4.2 (XTAL2B‡)

<sup>29</sup> <sup>20</sup> <sup>20</sup> <sup>21</sup> <sup>22</sup> <sup>23</sup> <sup>23</sup> <sup>23</sup> <sup>24</sup>

(DDA) P4.3

(XTAL1A) P4.6 □ 2 VSS □ 2

(XTAL2A) P4.7

] P0.1 (AD1) ] P0.2 (AD2) ] P0.3 (AD3) □ P0.0 (AD0)

40<sup>4</sup> 39

38

36

35 🗆 POL

🗆 P0.4 (AD4)

P0.5 (AD5)

D P0.7 (AD7)

37 P0.6 (AD6)

34 P4.0 (SCL)

33 P4.4 (ALE)

32 2 P4.5 (PSEN)

31 P2.7 (A15/AIN3) 30 P2.6 (A14/AIN2)

P2.5 (A13/AIN1)

P1.4 (CEX1/SS1)

P1.3 (CEX0)

4 П

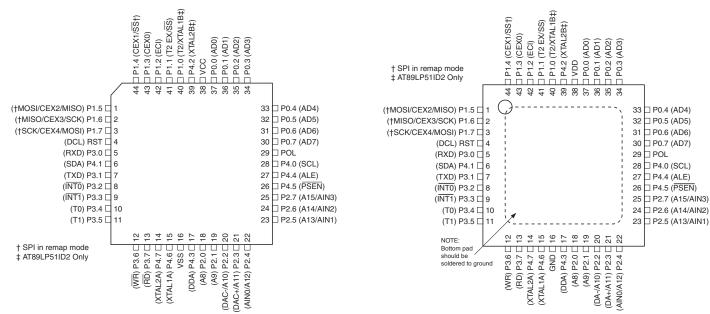

**Pin Configurations**

44-lead VQFP

1.

1.1

#### 1.4 40-pin PDIP

|                                |      | -                   |

|--------------------------------|------|---------------------|

| (T2) P1.0 🗆                    | 1 4  |                     |

| (SS/T2EX) P1.1                 | 2 3  | 9 - P0.0 (AD0)      |

| (ECI) P1.2 🗆                   | 3 3  | . ,                 |

| (CEX0) P1.3 [                  | 4 3  |                     |

| († <del>SS</del> /CEX1) P1.4 🗆 | 5 3  | 6 🗆 P0.3 (AD3)      |

| (†MOSI/CEX2/MISO) P1.5 🗆       | 6 3  | 5 🗆 P0.4 (AD4)      |

| (†MISO/CEX3/SCL) P1.6 🗆        | 7 3  | 4 🗆 P0.5 (AD5)      |

| (†SCK/CEX4/MOSI) P1.7 🗆        | 8 3  | 3 🗆 P0.6 (AD6)      |

| RST 🗆                          | 9 3  | 2 🗆 P0.7 (AD7)      |

| (RXD) P3.0 🗆                   | 10 3 | 1 🗆 POL             |

| (TXD) P3.1 🗆                   | 11 3 | 0 🗆 P4.4 (ALE)      |

| (ĪNT0) P3.2 🗆                  | 12 2 | 9 🗆 P4.5 (PSEN)     |

| (INT1) P3.3 🗆                  | 13 2 | 8 🗆 P2.7 (A15/AIN3) |

| (T0) P3.4 🗆                    | 14 2 | 7 🗆 P2.6 (A14/AIN2) |

| (T1) P3.5 🗆                    | 15 2 | 6 🗆 P2.5 (A13/AIN1) |

| (WR) P3.6 🗆                    | 16 2 | 5 🗆 P2.4 (A12/AIN0) |

| (RD) P3.7 🗆                    | 17 2 | 4 🗆 P2.3 (A11/DAC+) |

| (XTAL2A) P4.7 🗆                | 18 2 | 3 🗆 P2.2 (A10/DAC-) |

| (XTAL1A) P4.6 🗆                | 19 2 | 2 🗆 P2.1 (A9)       |

| GND 🗆                          | 20 2 | 1 🗆 P2.0 (A8)       |

|                                |      |                     |

†SPI in remap mode

#### 1.2 44-lead PLCC

(†MOSI/CEX2/MISO) P1.5

† SPI in remap mode

‡ AT89LP51ID2 Only

(†MISO/CEX3/SCK) P1.6 28

(†SCK/CEX4/MOSI) P1.7 2 9

(DCL) RST [ 10

(RXD) P3.0 [11]

(SDA) P4.1 [ 12

(TXD) P3.1 [ 13

(INTO) P3.2 14

(INT1) P3.3 [ 15

16 17 17

(<u>WR</u>) P3.6 □ 1 (<u>RD</u>) P3.7 □ 1

(T0) P3.4 🗆

(T1) P3.5 🗆

(A8) P2.0 [ 2 (A9) P2.1 [ 2 (A9) P2.1 [ 2 (DAC-/A10) P2.2 [ 2 (DAC-/A11) P2.3 [ 2 (AIN0/A12) P2.4 [ 24

#### 44-pad VQFN/QFN/MLF 1.3

# 1.5 Pin Description

| Table 1-1. Atme | I AT89LP51RB2/RC2/IC2 Pin Description |

|-----------------|---------------------------------------|

|-----------------|---------------------------------------|

| P            | Pin Numbe | er   |        |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------|-----------|------|--------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VQFP<br>VQFN | PLCC      | PDIP | Symbol | Туре                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1            | 7         | 6    | P1.5   | I/O<br>I/O<br>I/O        | <ul> <li>P1.5: User-configurable I/O Port 1 bit 5.</li> <li>MISO: SPI master-in/slave-out. When configured as master, this pin is an input. When configured as slave, this pin is an output.</li> <li>MOSI: SPI master-out/slave-in (Remap mode). When configured as master, this pin is an output. When configured as slave, this pin is an input. During In-System Programming, this pin is an input.</li> <li>CEX2: Capture/Compare external I/O for PCA module 2.</li> </ul> |

| 2            | 8         | 7    | P1.6   | I/O<br>I/O<br>I/O        | <ul> <li>P1.6: User-configurable I/O Port 1 bit 6.</li> <li>SCK: SPI Clock. When configured as master, this pin is an output. When configured as slave, this pin is an input.</li> <li>MISO: SPI master-in/slave-out (Remap mode). When configured as master, this pin is an input. When configured as slave, this pin is an output. During In-System Programming, this pin is an output.</li> <li>CEX3: Capture/Compare external I/O for PCA module 3.</li> </ul>               |

| 3            | 9         | 8    | P1.7   | I/O<br>I/O<br>I/O<br>I/O | <ul> <li>P1.7: User-configurable I/O Port 1 bit 7.</li> <li>MOSI: SPI master-out/slave-in. When configured as master, this pin is an output. When configured as slave, this pin is an input.</li> <li>SCK: SPI Clock (Remap mode). When configured as master, this pin is an output. When configured as slave, this pin is an input. During In-System Programming, this pin is an input.</li> <li>CEX4: Capture/Compare external I/O for PCA module 4.</li> </ul>                |

| 4            | 10        | 9    | RST    | I/O<br>I                 | RST: External Reset input (Reset polarity depends on POL pin). The RST pin can output a pulse when the internal Watchdog reset or POR is active.<br>DCL: Serial Debug Clock input for On-Chip Debug Interface when OCD is enabled.                                                                                                                                                                                                                                               |

| 5            | 11        | 10   | P3.0   | I/O<br>I                 | P3.0: User-configurable I/O Port 3 bit 0.<br>RXD: Serial Port Receiver Input.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6            | 12        |      | P4.1   | I/O<br>I/O               | P4.1: User-configurable I/O Port 4bit 1.<br>SDA: TWI bidirectional Serial Data line.                                                                                                                                                                                                                                                                                                                                                                                             |

| 7            | 13        | 11   | P3.1   | I/O<br>O                 | P3.1: User-configurable I/O Port 3 bit 1.<br>TXD: Serial Port Transmitter Output.                                                                                                                                                                                                                                                                                                                                                                                                |

| 8            | 14        | 12   | P3.2   | I/O<br>I                 | P3.2: User-configurable I/O Port 3 bit 2.<br>INT0: External Interrupt 0 Input or Timer 0 Gate Input.                                                                                                                                                                                                                                                                                                                                                                             |

| 9            | 15        | 13   | P3.3   | I/O<br>I                 | P3.3: User-configurable I/O Port 3 bit 3.<br>INT1: External Interrupt 1 Input or Timer 1 Gate Input                                                                                                                                                                                                                                                                                                                                                                              |

| 10           | 16        | 14   | P3.4   | I/O<br>I/O               | <ul><li>P3.4: User-configurable I/O Port 3 bit 4.</li><li>T1: Timer/Counter 0 External input or output.</li></ul>                                                                                                                                                                                                                                                                                                                                                                |

| 11           | 17        | 15   | P3.5   | I/O<br>I/O               | <ul><li>P3.5: User-configurable I/O Port 3 bit 5.</li><li>T1: Timer/Counter 1 External input or output.</li></ul>                                                                                                                                                                                                                                                                                                                                                                |

| 12           | 18        | 16   | P3.6   | I/O<br>O                 | <b>P3.6</b> : User-configurable I/O Port 3 bit 6.<br><b>WR</b> : External memory interface Write Strobe (active-low).                                                                                                                                                                                                                                                                                                                                                            |

| 13           | 19        | 17   | P3.7   | I/O<br>O                 | <b>P3.7</b> : User-configurable I/O Port 3 bit 7.<br><b>RD</b> : External memory interface Read Strobe (active-low).                                                                                                                                                                                                                                                                                                                                                             |

| 14           | 20        | 18   | P4.7   | I/O<br>O                 | <b>P4.7</b> : User-configurable I/O Port 4 bit 7.<br><b>XTAL2A</b> : Output from inverting oscillator amplifier A. It may be used as a port pin if the internal RC oscillator or external clock is selected as the clock source A.                                                                                                                                                                                                                                               |

| 15           | 21        | 19   | P4.6   | I/O<br>I                 | <b>P4.6</b> : User-configurable I/O Port 4 bit 6.<br><b>XTAL1A</b> : Input to the inverting oscillator amplifier A and internal clock generation circuits. It may be used as a port pin if the internal RC oscillator is selected as the clock source A.                                                                                                                                                                                                                         |

#### Table 1-1. Atmel AT89LP51RB2/RC2/IC2 Pin Description

| P            | in Numbe | er   |        |                                         |                                                                                                                                                                        |  |  |  |  |

|--------------|----------|------|--------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| VQFP<br>VQFN | PLCC     | PDIP | Symbol | Туре                                    | Description                                                                                                                                                            |  |  |  |  |

| 16           | 22       | 20   | GND    | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | Ground                                                                                                                                                                 |  |  |  |  |

| 17           | 23       |      | P4.3   | I/O<br>I/O                              | <b>P4.3</b> : User-configurable I/O Port 4bit 3.<br><b>DDA</b> : Bidirectional Debug Data line for the On-Chip Debug Interface when OCD is enabled.                    |  |  |  |  |

| 18           | 24       | 21   | P2.0   | I/O<br>O                                | <ul><li>P2.0: User-configurable I/O Port 2 bit 0.</li><li>A8: External memory interface Address bit 8.</li></ul>                                                       |  |  |  |  |

| 19           | 25       | 22   | P2.1   | I/O<br>O                                | <b>22.1</b> : User-configurable I/O Port 2 bit 1.<br><b>A9</b> : External memory interface Address bit 9.                                                              |  |  |  |  |

| 20           | 26       | 23   | P2.1   | I/O<br>O<br>O                           | <ul> <li>P2.2: User-configurable I/O Port 2 bit 2.</li> <li>DA-: DAC negative differential output.</li> <li>A10: External memory interface Address bit 10.</li> </ul>  |  |  |  |  |

| 21           | 27       | 24   | P2.3   | I/O<br>O<br>O                           | <ul> <li>P2.3: User-configurable I/O Port 2 bit 3.</li> <li>DA+-: DAC positive differential output.</li> <li>A11: External memory interface Address bit 11.</li> </ul> |  |  |  |  |

| 22           | 28       | 25   | P2.4   | I/O<br>I<br>O                           | <ul><li>P2.4: User-configurable I/O Port 2 bit 5.</li><li>AIN0: Analog Comparator Input 0.</li><li>A12: External memory interface Address bit 12.</li></ul>            |  |  |  |  |

| 23           | 29       | 26   | P2.5   | I/O<br>I<br>O                           | <ul><li>P2.5: User-configurable I/O Port 2 bit 5.</li><li>AIN1: Analog Comparator Input 1.</li><li>A13: External memory interface Address bit 13.</li></ul>            |  |  |  |  |

| 24           | 30       | 27   | P2.6   | I/O<br>I<br>O                           | <ul><li>P2.6: User-configurable I/O Port 2 bit 6.</li><li>AIN2: Analog Comparator Input 2.</li><li>A14: External memory interface Address bit 14.</li></ul>            |  |  |  |  |

| 25           | 31       | 28   | P2.7   | I/O<br>I<br>O                           | <ul><li>P2.7: User-configurable I/O Port 2 bit 7.</li><li>AIN3: Analog Comparator Input 3.</li><li>A15: External memory interface Address bit 15.</li></ul>            |  |  |  |  |

| 26           | 32       | 29   | P4.5   | I/O<br>O                                | <b>P4.5</b> : User-configurable I/O Port 4 bit 5.<br><b>PSEN</b> : External memory interface Program Store Enable (active-low).                                        |  |  |  |  |

| 27           | 33       | 30   | P4.4   | I/O<br>I/O                              | <b>P4.4</b> : User-configurable I/O Port 4 bit 4.<br><b>ALE</b> : External memory interface Address Latch Enable.                                                      |  |  |  |  |

| 28           | 34       |      | P4.0   | I/O                                     | <b>P4.0</b> : User-configurable I/O Port 4 bit 0.<br><b>SCL</b> : TWI Serial Clock line. This line is an output in mater mode and an input in slave mode.              |  |  |  |  |

| 29           | 35       | 31   | POL    | I                                       | POL: Reset polarity                                                                                                                                                    |  |  |  |  |

| 30           | 36       | 32   | P0.7   | I/O<br>I/O                              | <b>P0.7</b> : User-configurable I/O Port 0 bit 7.<br><b>AD7</b> : External memory interface Address/Data bit 7.                                                        |  |  |  |  |

| 31           | 37       | 33   | P0.6   | I/O<br>I/O<br>I                         | <b>P0.6</b> : User-configurable I/O Port 0 bit 6.<br><b>AD6</b> : External memory interface Address/Data bit 6.<br><b>ADC6</b> : ADC analog input 6.                   |  |  |  |  |

| 32           | 38       | 34   | P0.5   | I/O<br>I/O<br>I                         | P0.5: User-configurable I/O Port 0 bit 5.<br>AD5: External memory interface Address/Data bit 5.<br>ADC5: ADC analog input 5.                                           |  |  |  |  |

| 33           | 39       | 35   | P0.4   | I/O<br>I/O<br>I                         | P0.4: User-configurable I/O Port 0 bit 4.<br>AD4: External memory interface Address/Data bit 4.<br>ADC4: ADC analog input 4.                                           |  |  |  |  |

| 34           | 40       | 36   | P0.3   | I/O<br>I/O<br>I                         | P0.3: User-configurable I/O Port 0 bit 3.<br>AD3: External memory interface Address/Data bit 3.<br>ADC3: ADC analog input 3.                                           |  |  |  |  |

4 AT89LP51RB2/RC2/IC2 Summary

| Pin Number   |      |      |        |                 |                                                                                                                                                                                                                                                                                                                                       |

|--------------|------|------|--------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VQFP<br>VQFN | PLCC | PDIP | Symbol | Туре            | Description                                                                                                                                                                                                                                                                                                                           |

| 35           | 41   | 37   | P0.2   | I/O<br>I/O<br>I | <ul> <li>P0.2: User-configurable I/O Port 0 bit 2.</li> <li>AD2: External memory interface Address/Data bit 2.</li> <li>ADC2: ADC analog input 2.</li> </ul>                                                                                                                                                                          |

| 36           | 42   | 38   | P0.1   | I/O<br>I/O<br>I | <ul> <li>P0.1: User-configurable I/O Port 0 bit 1.</li> <li>AD1: External memory interface Address/Data bit 1.</li> <li>ADC1: ADC analog input 1.</li> </ul>                                                                                                                                                                          |

| 37           | 43   | 39   | P0.0   | I/O<br>I/O<br>I | <ul><li>P0.0: User-configurable I/O Port 0 bit 0.</li><li>AD0: External memory interface Address/Data bit 0.</li><li>ADC0: ADC analog input 0.</li></ul>                                                                                                                                                                              |

| 38           | 44   | 40   | VDD    | I               | Supply Voltage                                                                                                                                                                                                                                                                                                                        |

| 39           | 1    |      | P4.2   | I/O             | <b>P4.2</b> : User-configurable I/O Port 4bit 2.<br><b>XTAL2B</b> : Output from low-frequency inverting oscillator amplifier B (AT89LP51IC2 only). It may be used as a port pin if the internal RC oscillator or external clock is selected as the clock source B.                                                                    |

| 40           | 2    | 1    | P1.0   | I/O<br>I/O      | <ul> <li>P1.0: User-configurable I/O Port 1 bit 0.</li> <li>T2: Timer 2 External Input or Clock Output.</li> <li>XTAL1B: Input to the low-frequency inverting oscillator amplifier B and internal clock generation circuits. It may be used as a port pin if the internal RC oscillator is selected as the clock source B.</li> </ul> |

| 41           | 3    | 2    | P1.1   | I/O<br>I<br>I   | P1.1: User-configurable I/O Port 1 bit 1.<br>T2EX: Timer 2 External Capture/Reload Input.<br>SS: SPI Slave-Select.                                                                                                                                                                                                                    |

| 42           | 4    | 3    | P1.2   | I/O             | P1.2: User-configurable I/O Port 1 bit 2.                                                                                                                                                                                                                                                                                             |

| 43           | 5    | 4    | P1.3   | I/O<br>I/O      | P1.3: User-configurable I/O Port 1 bit 3.<br>CEX0: Capture/Compare external I/O for PCA module 0.                                                                                                                                                                                                                                     |

| 44           | 6    | 5    | P1.4   | I/O<br>I<br>I/O | P1.4: User-configurable I/O Port 1 bit 4.<br>SS: SPI Slave-Select (Remap Mode). This pin is an input for In-System Programming<br>CEX1: Capture/Compare external I/O for PCA module 1.                                                                                                                                                |

#### Table 1-1. Atmel AT89LP51RB2/RC2/IC2 Pin Description

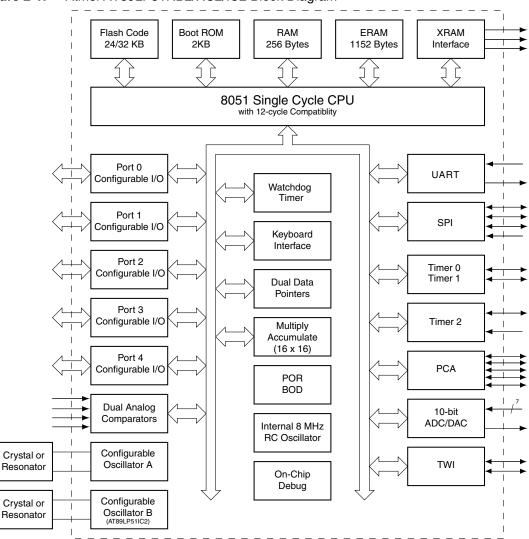

# 2. Overview

The Atmel<sup>®</sup> AT89LP51RB2/RC2/IC2 is a low-power, high-performance CMOS 8-bit 8051 microcontroller with 64KB of In-System Programmable Flash program memory. The devices are manufactured using Atmel's high-density nonvolatile memory technology and are compatible with the industry-standard 80C51 instruction set.

The AT89LP51RB2/RC2/IC2 is built around an enhanced CPU core that can fetch a single byte from memory every clock cycle. In the classic 8051 architecture, each fetch requires 6 clock cycles, forcing instructions to execute in 12, 24 or 48 clock cycles. In the AT89LP51RB2/RC2/IC2 CPU, standard instructions need only one to four clock cycles providing six to twelve times more throughput than the standard 8051. Seventy percent of instructions need only as many clock cycles as they have bytes to execute, and most of the remaining instructions require only one additional clock. The enhanced CPU core is capable of 20 MIPS throughput whereas the classic 8051 CPU can deliver only 4 MIPS at the same current consumption. Conversely, at the same throughput as the classic 8051, the new CPU core runs at a much lower speed and thereby greatly reducing power consumption and EMI. The AT89LP51RB2/RC2/IC2 also includes a compatibility mode that will enable classic 12 clock per machine cycle operation for true timing compatibility with the Atmel AT89C51RB2/RC2.

The AT89LP51RB2/RC2/IC2 retains all of the standard features of the AT89C51RB2/RC2, including: 64KB of In-System Programmable Flash program memory, 256 bytes of RAM, 1152 bytes of expanded RAM, up to 40 I/O lines, three 16-bit timer/counters, a Programmable Counter Array, a programmable hardware watchdog timer, a keyboard interface, a full-duplex enhanced serial port, a serial peripheral interface (SPI), on-chip crystal oscillator, and a four-level, ten-vector interrupt system. A block diagram is shown in Figure 2-1.

In addition, the Atmel<sup>®</sup> AT89LP51RB2/RC2/IC2 provides a Two-Wire Interface (TWI) for up to 400KB/s serial transfer; a 10-bit, 8-channel Analog-to-Digital Converter (ADC) with temperature sensor and digital-to-analog (DAC) mode; two analog comparators; and an 8MHz internal oscillator.

Some standard features on the AT89LP51RB2/RC2/IC2 are enhanced with new modes or operations. Mode 0 of Timer 0 or Timer 1 acts as a variable 9–16 bit timer/counter and Mode 1 acts as a 16-bit auto-reload timer/counter. In addition, each timer/counter may independently drive an 8-bit precision pulse width modulation output. Mode 0 (synchronous mode) of the serial port allows flexibility in the phase/polarity relationship between clock and data.

The I/O ports of the AT89LP51RB2/RC2/IC2 can be independently configured in one of four operating modes. In quasi-bidirectional mode, the ports operate as in the classic 8051. In inputonly mode, the ports are tristated. Push-pull output mode provides full CMOS drivers and opendrain mode provides just a pull-down. Unlike other 8051s, this allows Port 0 to operate with onchip pull-ups if desired.

The AT89LP51RB2/RC2/IC2 includes an On-Chip Debug (OCD) interface that allows read-modify-write capabilities of the system state and program flow control, and programming of the internal memories. The on-chip Flash may also be programmed through the UART-based bootloader or the SPI-based In-System programming interface (ISP).

The TWI and OCD features are not available on the PDIP package. The AT89LP51IC2 is also not available in PDIP.

The features of the AT89LP51RB2/RC2/IC2 make it a powerful choice for applications that need pulse width modulation, high speed I/O, and counting capabilities such as alarms, motor control, corded phones, and smart card readers.

## 2.1 Block Diagram

Figure 2-1. Atmel AT89LP51RB2/RC2/IC2 Block Diagram

### 2.2 System Configuration

The AT89LP51RB2/RC2/IC2 supports several system configuration options. Nonvolatile options are set through user fuses that must be programmed through the flash programming interface. Volatile options are controlled by software through individual bits of special function registers (SFRs). The AT89LP51RB2/RC2/IC2 must be properly configured before correct operation can occur.

#### 2.2.1 Fuse Options

Table 2-1 lists the fusible options for the AT89LP51RB2/RC2/IC2. These options maintain their state even when the device is powered off. Some may be changed through the FLash API but others can only be changed with an external device programmer. For more information, see datasheet.

| Fuse Name                         | Description                                                                                                                                                                                                 |  |  |  |  |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Clock Source A                    | Selects between the High Speed Crystal Oscillator, Low Power<br>Crystal Oscillator, External Clock on XTAL1A or Internal RC Oscillator<br>for the source of the system clock when oscillator A is selected. |  |  |  |  |

| Clock Source B                    | Selects between the 32 kHzCrystal Oscillator, External Clock on XTAL1B or Internal RC Oscillator for the source of the system clock when oscillator B is selected (AT89LP51IC2 Only).                       |  |  |  |  |

| Oscillator Select                 | Selects whether oscillator A or B is enabled to boot the device. (AT89LP51IC2 Only)                                                                                                                         |  |  |  |  |

| X2 Mode                           | Selects the default state of whether the clock source is divided by two (X1) or not (X2) to generate the system clock.                                                                                      |  |  |  |  |

| Start-up Time                     | Selects time-out delay for the POR/BOD/PWD wake-up period.                                                                                                                                                  |  |  |  |  |

| Compatibility Mode                | Configures the CPU in 12-clock compatibility or single-cycle fast execution mode.                                                                                                                           |  |  |  |  |

| XRAM Configuration                | Configures if access to on-chip memories that are mapped to the external data memory address space is enabled/disabled by default.                                                                          |  |  |  |  |

| Bootloader Jump Bit               | Enables or disables the on-ship bootloader.                                                                                                                                                                 |  |  |  |  |

| On-Chip Debug Enable              | Enables or disables On-Chip Debug. OCD must be enabled prior to using an in-circuit debugger with the device.                                                                                               |  |  |  |  |

| In-System Programming Enable      | Enables or disables In-System Programming.                                                                                                                                                                  |  |  |  |  |

| User Signature Programming Enable | Enables or disables programming of User Signature array.                                                                                                                                                    |  |  |  |  |

| Default Port State                | Configures the default port state as input-only mode (tristated) or quasi-bidirectional mode (weakly pulled high).                                                                                          |  |  |  |  |

| Low Power Mode                    | Enables or disables power reduction features for lower system frequencies.                                                                                                                                  |  |  |  |  |

| nfiguration Fuses |

|-------------------|

| ſ                 |

#### 2.2.2 Software Options

Table 2-2 lists some important software configuration bits that affect operation at the system level. These can be changed by the application software but are set to their default values upon any reset. Most peripherals also have multiple configuration bits that are not listed here.

Table 2-2.

Important Software Configuration Bits

|                    | important Contraro Co                                            | 3                                                                                                                                                                                                 |

|--------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit(s)             | SFR Location                                                     | Description                                                                                                                                                                                       |

| PxM0.y<br>PxM1.y   | P0M0, P0M1, P1M0, P1M1,<br>P2M0, P2M1, P3M0, P3M1,<br>P4M0, P4M1 | Configures the I/O mode of Port x Pin y to be one of input-only, quasi-<br>bidirectional, push-pull output or open-drain. The default state is<br>controlled by the Default Port State fuse above |

| CKRL               | CKRL                                                             | Selects the division ratio between the oscillator and the system clock                                                                                                                            |

| TPS <sub>3-0</sub> | CLKREG.7-4                                                       | Selects the division ratio between the system clock and the timers                                                                                                                                |

| ALES               | AUXR.0                                                           | Enables/disables toggling of ALE                                                                                                                                                                  |

| EXRAM              | AUXR.1                                                           | Enables/disables access to on-chip memories that are mapped to the external data memory address space                                                                                             |

| WS <sub>1-0</sub>  | AUXR.6-5                                                         | Selects the number of wait states when accessing external data memory                                                                                                                             |

| XSTK               | AUXR1.4                                                          | Configures the hardware stack to be in RAM or extra RAM                                                                                                                                           |

| ENBOOT             | AUXR1.5                                                          | Enables/disables access to the on-chip Flash API                                                                                                                                                  |

## 2.3 Comparison to the Atmel AT89C51RB2/RC2/IC2

The Atmel<sup>®</sup> AT89LP51RB2/RC2/IC2 is part of a family of devices with enhanced features that are fully binary compatible with the 8051 instruction set. The AT89LP51RB2/RC2/IC2 has two modes of operations, Compatibility mode and Fast mode. In Compatibility mode the instruction timing, peripheral behavior, SFR addresses, bit assignments and pin functions are identical to the existing Atmel AT89C51RB2/RC2/IC2 product. Additional enhancements are transparent to the user and can be used if desired. Fast mode allows greater performance, but with some differences in behavior. The major enhancements from the AT89C51RB2/RC2/IC2 are outlined in the following paragraphs and may be useful to users migrating to the AT89LP51RB2/RC2/IC2 from older devices. A summary of the differences between Compatibility and Fast modes is given in Table 2-3 on page 11. See also the Application note "Migrating from AT89C51RB2/RC2/IC2 to AT89LP51RB2/RC2/IC2."

#### 2.3.1 Instruction Execution

In Compatibility mode the Atmel<sup>®</sup> AT89LP51RB2/RC2/IC2 CPU uses the six-state machine cycle of the standard 8051 where instruction bytes are fetched every three system clock cycles. Execution times in this mode are identical to the Atmel AT89C51RB2/RC2/IC2. For greater performance the user can enable Fast mode by disabling the Compatibility fuse. In Fast mode the CPU fetches one code byte from memory every clock cycle instead of every three clock cycles. This greatly increases the throughput of the CPU. Each standard instruction executes in only one to four clock cycles. See datasheet for more details. Any software delay loops or instruction-based timing operations may need to be retuned to achieve the desired results in Fast mode.

#### 2.3.2 System Clock

The system clock source is not limited to a crystal or external clock. The system clock source is selectable between the crystal oscillator, an externally driven clock and an internal 8.0MHz RC oscillator for AT89LP51RB2/RC2 and clock source A of AT89LP51IC2. Clock source B of AT89LP51IC2 is not limited to a 32 kHz crystal. The clock source B is selectable between the 32 kHz crystal oscillator, an externally driven clock and an internal 8.0MHz RC oscillator. Unlike AT89C51IC2, the X2 and CKRL features will also affect the OSCB source.

By default in Compatibility mode the system clock frequency is divided by 2 from the externally supplied XTAL1 frequency for compatibility with standard 8051s (12 clocks per machine cycle). The System Clock Divider can scale the system clock versus the oscillator source. The divideby-2 can be disabled to operate in X2 mode (6 clocks per machine cycle) or the clock may be further divided to reduce the operating frequency. In Fast mode the clock divider defaults to divide by 1.

#### 2.3.3 Reset

The RST pin of the AT89LP51RB2/RC2/IC2 has selectable polarity using the POL pin (formerly  $\overline{EA}$ ). When POL is high the RST pin is active high with a pull-down resistor and when POL is low the RST pin is active low with a pull-up resistor. For existing AT89C51RB2/RC2/IC2 sockets where  $\overline{EA}$  is tied to VDD, replacing AT89C51RB2/RC2 with AT89LP51RB2/RC2/IC2 will maintain the active high reset. Note that forcing external execution by tying  $\overline{EA}$  low is not supported.

The AT89LP51RB2/RC2/IC2 includes an on-chip Power-On Reset and Brown-out Detector circuit that ensures that the device is reset from system power up. In most cases a RC startup circuit is not required on the RST pin, reducing system cost, and the RST pin may be left unconnected if a board-level reset is not present.

#### 2.3.4 Timer/Counters

A common prescaler is available to divide the time base for Timer 0, Timer 1, Timer 2 and the WDT. The TPS<sub>3-0</sub> bits in the CLKREG SFR control the prescaler. In Compatibility mode TPS<sub>3-0</sub> defaults to 0101B, which causes the timers to count once every machine cycle. The counting rate can be adjusted linearly from the system clock rate to 1/16 of the system clock rate by changing TPS<sub>3-0</sub>. In Fast mode TPS<sub>3-0</sub> defaults to 0000B, or the system clock rate. TPS does not affect Timer 2 in Clock Out or Baud Generator modes.

In Compatibility mode the sampling of the external Timer/Counter pins: T0, T1, T2 and T2EX; and the external interrupt pins,  $\overline{INT0}$  and  $\overline{INT1}$ , is also controlled by the prescaler. In Fast mode these pins are always sampled at the system clock rate.

Both Timer 0 and Timer 1 can toggle their respective counter pins, T0 and T1, when they overflow by setting the output enable bits in TCONB.

#### 2.3.5 Interrupt Handling

Fast mode allows for faster interrupt response due to the shorter instruction execution times.

#### 2.3.6 Keyboard Interface

The AT89LP51RB2/RC2/IC2 does not clear the keyboard flag register (KBF) after a read. Each bit must be cleared in software. This allows the interrupt to be generate once per flag when multiple flags are set, if desired. To mimic the old behavior the service routine must clear the whole register.

The keyboard can also support general edge-triggered interrupts with the addition of the KBMOD register.

#### 2.3.7 Serial Port

The timer prescaler increases the range of achievable baud rates when using Timer 1 to generate the baud rate in UART Modes 1 or 3, including an increase in the maximum baud rate available in Compatibility mode. Additional features include automatic address recognition and framing error detection.

The shift register mode (Mode 0) has been enhanced with more control of the polarity, phase and frequency of the clock and full-duplex operation. This allows emulation of master serial peripheral (SPI) and two-wire (TWI) interfaces.

#### 2.3.8 I/O Ports

The P0, P1, P2 and P3 I/O ports of the AT89LP51RB2/RC2/IC2 may be configured in four different modes. The default setting depends on the Tristate-Port User Fuse. When the fuse is set all the I/O ports revert to input-only (tristated) mode at power-up or reset. When the fuse is not active, ports P1, P2 and P3 start in quasi-bidirectional mode and P0 starts in open-drain mode. P4 always operates in quasi-bidirectional mode. P0 can be configured to have internal pull-ups by placing it in quasi-bidirectional or output modes. This can reduce system cost by removing the need for external pull-ups on Port 0.

The P4.4–P4.7 pins are additional I/Os that replace the normally dedicated ALE, PSEN, XTAL1 and XTAL2 pins of the AT89C51RB2/RC2/IC2. These pins can be used as additional I/Os depending on the configuration of the clock and external memory.

#### 2.3.9 Security

The AT89LP51RB2/RC2/IC2 does not support the external access pin ( $\overline{EA}$ ). Therefore it is not possible to execute from external program memory in address range 0000H–1FFFH. When the third Lockbit is enabled (Lock Mode 4) external program execution is disabled for all addresses above 1FFFH. This differs from AT89C51RB2/RC2/IC2 where Lock Mode 4 prevents  $\overline{EA}$  from being sampled low, but may still allow external execution at addresses outside the 8K internal space.

#### 2.3.10 Programming

The AT89LP51RB2/RC2/IC2 supports a richer command set for In-System Programming (ISP). Existing AT89C51RB2/RC2 programmers should be able to program the AT89LP51RB2/RC2/IC2 in byte mode. In page mode the AT89LP51RB2/RC2/IC2 only supports programming of a half-page of 64 bytes and therefore requires an extra address byte as compared to AT89C51RB2/RC2. Furthermore the device signature is located at addresses 0000H, 0001H and 0003H instead of 0000H, 0100H and 0200H.

| Feature                                          | Compatibility   | Fast            |

|--------------------------------------------------|-----------------|-----------------|

| Instruction Fetch in System Clocks               | 3               | 1               |

| Instruction Execution Time in System Clocks      | 6, 12, 18 or 24 | 1, 2, 3, 4 or 5 |

| Default System Clock Divisor                     | 2               | 1               |

| Default Timer Prescaler Divisor                  | 6               | 1               |

| Pin Sampling Rate (INT0, INT1, T0, T1, T2, T2EX) | Prescaler Rate  | System Clock    |

| Minimum RST input pulse in System Clocks         | 12              | 2               |

#### **Table 2-3.** Compatibility Mode versus Fast Mode Summary

# 3. Special Function Registers

A map of the on-chip memory area called the Special Function Register (SFR) space is shown in Table 3-1.

Note that not all of the addresses are occupied, and unoccupied addresses may not be implemented on the chip. Read accesses to these addresses will in general return random data, and write accesses will have an indeterminate effect. User software should not write to these unlisted locations, since they may be used in future products to invoke new features.

| Table 5- | Aunen              | A TOUL JINL        | 52/1102/102 0       | n map anu           | neset value         | 3                   |                        |                     | _    |

|----------|--------------------|--------------------|---------------------|---------------------|---------------------|---------------------|------------------------|---------------------|------|

|          | 8                  | 9                  | А                   | В                   | С                   | D                   | Е                      | F                   |      |

| 0F8H     |                    | CH<br>0000 0000    | CCAP0H<br>0000 0000 | CCAP1H<br>0000 0000 | CCAP2H<br>0000 0000 | CCAP3H<br>0000 0000 | CCAP4H<br>0000 0000    |                     | 0FFH |

| 0F0H     | B<br>0000 0000     |                    | RL0<br>0000 0000    | RL1<br>0000 0000    | RH0<br>0000 0000    | RH1<br>0000 0000    | PAGE<br>0000 0000      | BX<br>0000 0000     | 0F7H |

| 0E8H     |                    | CL<br>0000 0000    | CCAP0L<br>0000 0000 | CCAP1L<br>0000 0000 | CCAP2L<br>0000 0000 | CCAP3L<br>0000 0000 | CCAP4L<br>0000 0000    | SPX<br>xxxx x000    | 0EFH |

| 0E0H     | ACC<br>0000 0000   | AX<br>0000 0000    | DSPR<br>0000 0000   | FIRD<br>0000 0000   | MACL<br>0000 0000   | MACH<br>0000 0000   | P0M0<br>(2)            | P0M1<br>0000 0000   | 0E7H |

| 0D8H     | CCON<br>00x0 0000  | CMOD<br>00xx x000  | CCAPM0<br>x000 0000 | CCAPM1<br>x000 0000 | CCAPM2<br>x000 0000 | CCAPM3<br>x000 0000 | CCAPM4<br>x000 0000    |                     | 0DFH |

| 0D0H     | PSW<br>0000 0000   | FCON<br>xxxx 0000  |                     |                     | DPLB<br>0000 0000   | DPHB<br>0000 0000   | P1M0<br>(2)            | P1M1<br>0000 0000   | 0D7H |

| 0C8H     | T2CON<br>0000 0000 | T2MOD<br>0000 0000 | RCAP2L<br>0000 000  | RCAP2H<br>0000 0000 | TL2<br>0000 000     | TH2<br>0000 0000    | P2M0<br>(2)            | P2M1<br>0000 0000   | 0CFH |

| 0C0H     | P4<br>1111 1111    |                    |                     | SPCON<br>0001 0100  | SPSTA<br>0000 0000  | SPDAT<br>xxxx xxxx  | P3M0<br>(2)            | P3M1<br>0000 0000   | 0C7H |

| 0B8H     | IPL0<br>xx00 0000  | SADEN<br>0000 0000 |                     |                     |                     | AREF<br>0000 0000   | P4M0<br>(2)            | P4M1<br>0000 0000   | 0BFH |

| 0B0H     | P3<br>1111 1111    | IEN1<br>xxxx 0000  | IPL1<br>xxxx 0000   | IPH1<br>xxxx 0000   |                     |                     |                        | IPH0<br>xx00 0000   | 0B7H |

| 0A8H     | IEN0<br>0x00 0000  | SADDR<br>0000 0000 |                     | ACSRB<br>0000 0000  | DADL<br>0000 0000   | DADH<br>0000 0000   | CLKREG<br>0101 xxxx    | CKCON1<br>xxxx xxx0 | 0AFH |

| 0A0H     | P2<br>1111 1111    | DPCF<br>0000 0000  | AUXR1<br>0000 00x0  | ACSRA<br>0000 0000  | DADC<br>0000 0000   | DADI<br>0000 0000   | WDTRST<br>(write-only) | WDTPRG<br>0000 0xx0 | 0A7H |

| 98H      | SCON<br>0000 0000  | SBUF<br>xxxx xxxx  | BRL<br>0000 0000    | BDRCON<br>xxx0 0000 | KBLS<br>0000 0000   | KBE<br>0000 0000    | KBF<br>0000 0000       | KBMOD<br>0000 0000  | 9FH  |

| 90H      | P1<br>1111 1111    | TCONB<br>0010 0100 | BMSEL<br>xxxx xxx0  | SSCON<br>0000 0000  | SSCS<br>1111 1000   | SSDAT<br>1111 1111  | SSADR<br>1111 1110     | CKRL<br>1111 1111   | 97H  |

| 88H      | TCON<br>0000 0000  | TMOD<br>0000 0000  | TL0<br>0000 0000    | TL1<br>0000 0000    | TH0<br>0000 0000    | TH1<br>0000 0000    | AUXR<br>0000 0000      | CKCON0<br>0000 0000 | 8FH  |

| 80H      | P0<br>1111 1111    | SP<br>0000 0111    | DPL<br>0000 0000    | DPH<br>0000 0000    |                     | CKSEL<br>xxxx xxx0  | OSCCON<br>xxxx x001    | PCON<br>000x 0000   | 87H  |

|          | 0                  | 1                  | 2                   | 3                   | 4                   | 5                   | 6                      | 7                   |      |

| Nataa    |                    | the left meet      | olumn ara hit       | addraaabla          |                     |                     |                        |                     | -    |

Notes: 1. All SFRs in the left-most column are bit-addressable.

2. Reset value is 1111 1111B when Tristate-Port Fuse is enabled and 0000 0000B when disabled.

3. Reset value is 0101 0010B when Compatibility mode is enabled and 0000 0000B when disabled.

#### Table 3-2.C51 Core SFRs

| Mnemonic | Add | Name                             | 7  | 6  | 5  | 4   | 3    | 2    | 1   | 0   |

|----------|-----|----------------------------------|----|----|----|-----|------|------|-----|-----|

| ACC      | E0h | Accumulator                      |    |    |    |     |      |      |     |     |

| В        | F0h | B Register                       |    |    |    |     |      |      |     |     |

| PSW      | D0h | Program Status Word              | CY | AC | F0 | RS1 | RS0  | OV   | F1  | Р   |

| SP       | 81h | Stack Pointer                    |    |    |    |     |      |      |     |     |

| SPX      | EFh | Extended Stack Pointer           | _  | -  | _  | -   | SP11 | SP10 | SP9 | SP8 |

| DPL      | 82h | Data Pointer Low Byte            |    |    |    |     |      |      |     |     |

| DPH      | 83h | Data Pointer High Byte           |    |    |    |     |      |      |     |     |

| DPLB     | D4h | Alternate Data Pointer Low Byte  |    |    |    |     |      |      |     |     |

| DPHB     | D5h | Alternate Data Pointer High Byte |    |    |    |     |      |      |     |     |

| PAGE     | F6h | ERAM Page Register               | -  | -  | -  | -   |      |      |     |     |

#### Table 3-3.Digital Signal Processing SFRs

| Mnemonic | Add | Name                 | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|----------|-----|----------------------|------|------|------|------|------|------|------|------|

| AX       | E1h | Extended Accumulator |      |      |      |      |      |      |      |      |

| BX       | F7h | Extended B Register  |      |      |      |      |      |      |      |      |

| DSPR     | E2h | DSP Control Register | MRW1 | MRW0 | SMLB | SMLA | CBE1 | CBE0 | MVCD | DPRB |

| FIRD     | E3h | FIFO Depth           |      |      |      |      |      |      |      |      |

| MACL     | E4h | MAC Low Byte         |      |      |      |      |      |      |      |      |

| MACH     | E5h | MAC High Byte        |      |      |      |      |      |      |      |      |

# Table 3-4.System Management SFRs

| Mnemonic              | Add | Name                        | 7     | 6     | 5      | 4    | 3    | 2      | 1      | 0      |

|-----------------------|-----|-----------------------------|-------|-------|--------|------|------|--------|--------|--------|

| PCON                  | 87h | Power Control               | SMOD1 | SMOD0 | PWDEX  | POF  | GF1  | GF0    | PD     | IDL    |

| AUXR                  | 8Eh | Auxiliary Register 0        | DPU   | WS1   | WS0/M0 | XRS2 | XRS1 | XRS0   | EXTRAM | AO     |

| AUXR1                 | A2h | Auxiliary Register 1        | -     | -     | ENBOOT | XSTK | GF3  | 0      | -      | DPS    |

| DPCR                  | A3h | Datapointer Config Register | DPU1  | DPU0  | DPD1   | DPD0 | -    | -      | -      | -      |

| CKRL                  | 97h | Clock Reload Register       |       |       |        |      |      |        |        |        |

| CKCKON0               | 8Fh | Clock Control Register 0    | TWIX2 | WDTX2 | PCAX2  | SIX2 | T2X2 | T1X2   | T0X2   | X2     |

| CKCKON1               | AFh | Clock Control Register 1    | -     | -     | -      | -    | -    | -      | -      | SPIX2  |

| CKSEL <sup>(1)</sup>  | 85h | Clock Selection Register    | -     | -     | -      | _    | -    | -      | -      | CKS    |

| CLKREG                | AEh | Clock Register              | TPS3  | TPS2  | TPS1   | TPS0 | -    | -      | -      | -      |

| OSCCON <sup>(1)</sup> | 85h | Oscillator Control Register | -     | -     | _      | _    | -    | SCLKT0 | OscBEn | OscAEn |

Note: 1. Present on AT89LP51IC2 Only

### Table 3-5.Interrupt SFRs

| Mnemonic | Add | Name                              | 7    | 6    | 5    | 4     | 3    | 2    | 1    | 0    |

|----------|-----|-----------------------------------|------|------|------|-------|------|------|------|------|

| IEN0     | A8h | Interrupt Enable Control 0        | EA   | EC   | ET2  | ES    | ET1  | EX1  | ET0  | EX0  |

| IEN1     | B1h | Interrupt Enable Control 1        | -    | -    | EADC | ECMP  | -    | ESPI | ETWI | EKB  |

| IPH0     | B7h | Interrupt Priority Control High 0 | IP1D | PPCH | PT2H | PHS   | PT1H | PX1H | РТОН | PX0H |

| IPL0     | B8h | Interrupt Priority Control Low 0  | IP0D | PPCL | PT2L | PLS   | PT1L | PX1L | PTOL | PX0L |

| IPH1     | B3h | Interrupt Priority Control High 1 | IP3D | -    | PADL | PCMPL | -    | SPIH | PTWL | РКВН |

| IPL1     | B2h | Interrupt Priority Control Low 1  | IP2D | Ι    | PADH | PCMPH | -    | SPIL | PTWH | PKBL |

#### Table 3-6. Port SFRs

| Mnemonic | Add | Name          | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------|-----|---------------|---|---|---|---|---|---|---|---|

| P0       | 80h | 8-bit Port 0  |   |   |   |   |   |   |   |   |

| P1       | 90h | 8-bit Port 1  |   |   |   |   |   |   |   |   |

| P2       | A0h | 8-bit Port 2  |   |   |   |   |   |   |   |   |

| P3       | B0h | 8-bit Port 3  |   |   |   |   |   |   |   |   |

| P4       | C0h | 8-bit Port 4  |   |   |   |   |   |   |   |   |

| P0M0     | E6h | Port 0 Mode 0 |   |   |   |   |   |   |   |   |

| P0M1     | E7h | Port 0 Mode 1 |   |   |   |   |   |   |   |   |

| P1M0     | D6h | Port 1 Mode 0 |   |   |   |   |   |   |   |   |

| P1M1     | D7h | Port 1 Mode 1 |   |   |   |   |   |   |   |   |

| P2M0     | CEh | Port 2 Mode 0 |   |   |   |   |   |   |   |   |

| P2M1     | CFh | Port 2 Mode 1 |   |   |   |   |   |   |   |   |

| P3M0     | C6h | Port 3 Mode 0 |   |   |   |   |   |   |   |   |

| P3M1     | C7h | Port 3 Mode 1 |   |   |   |   |   |   |   |   |

| P4M0     | BEh | Port 4 Mode 0 |   |   |   |   |   |   |   |   |

| P4M1     | BFh | Port 4 Mode 1 |   |   |   |   |   |   |   |   |

### Table 3-7.Serial I/O Port SFRs

| Mnemonic | Add | Name               | 7      | 6   | 5   | 4   | 3    | 2    | 1   | 0   |

|----------|-----|--------------------|--------|-----|-----|-----|------|------|-----|-----|

| SCON     | 98h | Serial Control     | FE/SM0 | SM1 | SM2 | REN | TB8  | RB8  | ТІ  | RI  |

| SBUF     | 99h | Serial Data Buffer |        |     |     |     |      |      |     |     |

| SADEN    | B9h | Slave Address Mask |        |     |     |     |      |      |     |     |

| SADDR    | A9h | Slave Address      |        |     |     |     |      |      |     |     |

| BDRCON   | 9Bh | Baud Rate Control  | -      | -   | -   | BRR | TBCK | RBCK | SPD | SRC |

| BRL      | 9Ah | Baud Rate Reload   |        |     |     |     |      |      |     |     |

| Table 3-8. | Tim | er SFRs                                     |       |      |      |      |       |      |      |        |

|------------|-----|---------------------------------------------|-------|------|------|------|-------|------|------|--------|

| Mnemonic   | Add | Name                                        | 7     | 6    | 5    | 4    | 3     | 2    | 1    | 0      |

| TCON       | 88h | Timer/Counter 0 and 1 Control               | TF1   | TR1  | TF0  | TR0  | IE1   | IT1  | IE0  | ITO    |

| TMOD       | 89h | Timer/Counter 0 and 1 Modes                 | GATE1 | C/T1 | M11  | M01  | GATE0 | C/T0 | M10  | M00    |

| TCONB      | 91h | Timer/Counter 0 and 1 Mode B                |       |      |      |      |       |      |      |        |

| TL0        | 8Ah | Timer/Counter 0 Low Byte                    |       |      |      |      |       |      |      |        |

| TH0        | 8Ch | Timer/Counter 0 High Byte                   |       |      |      |      |       |      |      |        |

| TL1        | 8Bh | Timer/Counter 1 Low Byte                    |       |      |      |      |       |      |      |        |

| TH1        | 8Dh | Timer/Counter 1 High Byte                   |       |      |      |      |       |      |      |        |

| RL0        | F2h | Timer/Counter 0 Reload Low                  |       |      |      |      |       |      |      |        |

| RH0        | F3h | Timer/Counter 0 Reload High                 |       |      |      |      |       |      |      |        |

| RTL1       | F4h | Timer/Counter 1 Reload Low                  |       |      |      |      |       |      |      |        |

| RH1        | F5h | Timer/Counter 1 Reload High                 |       |      |      |      |       |      |      |        |

| WDTRST     | A6h | WatchDog Timer Reset                        |       |      |      |      |       |      |      |        |

| WDTPRG     | A7h | WatchDog Timer Program                      |       |      |      |      |       | WTO2 | WTO1 | WTO0   |

| T2CON      | C8h | Timer/Counter 2 control                     | TF2   | EXF2 | RCLK | TCLK | EXEN2 | TR2  | C/T2 | CP/RL2 |

| T2MOD      | C9h | Timer/Counter 2 Mode                        | _     | -    | -    | -    | -     | -    | T2OE | DCEN   |

| RCAP2H     | CBh | Timer/Counter 2 Reload/Capture<br>High Byte |       |      |      |      |       |      |      |        |

| RCAP2L     | CAh | Timer/Counter 2 Reload/Capture<br>Low Byte  |       |      |      |      |       |      |      |        |

| TH2        | CDh | Timer/Counter 2 High Byte                   |       |      |      |      |       |      |      |        |

| TL2        | CCh | Timer/Counter 2 Low Byte                    |       |      |      |      |       |      |      |        |

### Table 3-9.SPI Controller SFRs

| Mnemonic | Add | Name        | 7    | 6    | 5     | 4    | 3    | 2    | 1    | 0    |

|----------|-----|-------------|------|------|-------|------|------|------|------|------|

| SPCON    | C3h | SPI Control | SPR2 | SPEN | SSDIS | MSTR | CPOL | CPHA | SPR1 | SPR0 |

| SPSTA    | C4h | SPI Status  | SPIF | WCOL | SSERR | MODF |      |      |      |      |

| SPDAT    | C5h | SPI Data    | SPD7 | SPD6 | SPD5  | SPD4 | SPD3 | SPD2 | SPD1 | SPD0 |

## Table 3-10. TWI Controller SFRs

| Mnemonic | Add | Name                       | 7     | 6    | 5     | 4     | 3    | 2    | 1     | 0     |

|----------|-----|----------------------------|-------|------|-------|-------|------|------|-------|-------|

| SSCON    | 93h | Synchronous Serial Control | SSCR2 | SSPE | SSSTA | SSSTO | SSI  | SSAA | SSCR1 | SSCR0 |

| SSCS     | 94h | Synchronous Serial Status  | SSC4  | SSC3 | SSC2  | SSC1  | SSC0 | 0    | 0     | 0     |

| SSDAT    | 95h | Synchronous Serial Data    |       |      |       |       |      |      |       |       |

| SSADR    | 96h | Synchronous Serial Address | SSA7  | SSA6 | SSA5  | SSA4  | SSA3 | SSA2 | SSA1  | SSGC  |

Table 3-11. Keyboard Interface SFRs

| Mnemonic | Add | Name                    | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|----------|-----|-------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| KBLS     | 9Ch | Keyboard Level Selector | KBLS7 | KBLS6 | KBLS5 | KBLS4 | KBLS3 | KBLS2 | KBLS1 | KBLS0 |

| KBE      | 9Dh | Keyboard Input Enable   | KBE7  | KBE6  | KBE5  | KBE4  | KBE3  | KBE2  | KBE1  | KBE0  |

| KBF      | 9Eh | Keyboard Flag Register  | KBF7  | KBF6  | KBF5  | KBF4  | KBF3  | KBF2  | KBF1  | KBF0  |

| KBMOD    | 9Fh | Keyboard Mode Register  | KBM7  | KBM6  | KBM5  | KBM4  | КВМЗ  | KBM2  | KBM1  | KBM0  |

#### Table 3-12. Flash Memory SFR

| Mnemonic | Add | Name                      | 7     | 6     | 5     | 4     | 3   | 2     | 1     | 0     |

|----------|-----|---------------------------|-------|-------|-------|-------|-----|-------|-------|-------|

| BMSEL    | 92h | Bank Mode Select Register | -     | -     | -     | _     | -   | _     | _     | FBS   |

| FCON     | D2h | Flash Control Register    | FPSL3 | FPSL2 | FPSL1 | FPSL0 | FPS | FMOD1 | FMOD0 | FBUSY |

#### Table 3-13. Analog Comparator SFRs

| Mnemonic | Add | Name                          | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------|-----|-------------------------------|---|---|---|---|---|---|---|---|

| ACSRA    | A3h | Comparator A Control Register |   |   |   |   |   |   |   |   |

| ACSRB    | ABh | Comparator B Control Register |   |   |   |   |   |   |   |   |

| AREF     | BDh | Comparator Reference Register |   |   |   |   |   |   |   |   |

#### Table 3-14. ADC Controller SFRs

| Mnemonic | Add | Name                       | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------|-----|----------------------------|---|---|---|---|---|---|---|---|

| DADC     | A4h | DAC/ADC Control Register   |   |   |   |   |   |   |   |   |

| DADI     | A5h | DAC/ADC Input Register     |   |   |   |   |   |   |   |   |

| DADL     | ACh | DAC/ADC Data Low Register  |   |   |   |   |   |   |   |   |

| DADH     | ADh | DAC/ADC Data High Register |   |   |   |   |   |   |   |   |

### Table 3-15. PCA SFRs

| Mnemo<br>-nic | Add | Name                        | 7    | 6     | 5     | 4     | 3    | 2    | 1    | 0     |

|---------------|-----|-----------------------------|------|-------|-------|-------|------|------|------|-------|

| CCON          | D8h | PCA Timer/Counter Control   | CF   | CR    |       | CCF4  | CCF3 | CCF2 | CCF1 | CCF0  |

| CMOD          | D9h | PCA Timer/Counter Mode      | CIDL | WDTE  |       |       |      | CPS1 | CPS0 | ECF   |

| CL            | E9h | PCA Timer/Counter Low Byte  |      |       |       |       |      |      |      |       |

| СН            | F9h | PCA Timer/Counter High Byte |      |       |       |       |      |      |      |       |

| CCAPM0        | DAh | PCA Timer/Counter Mode 0    |      | ECOM0 | CAPP0 | CAPN0 | MAT0 | TOG0 | PWM0 | ECCF0 |

| CCAPM1        | DBh | PCA Timer/Counter Mode 1    |      | ECOM1 | CAPP1 | CAPN1 | MAT1 | TOG1 | PWM1 | ECCF1 |

| CCAPM2        | DCh | PCA Timer/Counter Mode 2    |      | ECOM2 | CAPP2 | CAPN2 | MAT2 | TOG2 | PWM2 | ECCF2 |

| CCAPM3        | DDh | PCA Timer/Counter Mode 3    |      | ECOM3 | CAPP3 | CAPN3 | MAT3 | TOG3 | PWM3 | ECCF3 |

# 4.2 Cross Reference with AT89C51RB2/RC2/IC2

| Device Migration          | Package | Packing | Previous Ordering Code | New Ordering Code         |

|---------------------------|---------|---------|------------------------|---------------------------|

|                           | PLCC44  | Stick   | AT89C51RB2-SLSUM       | AT89LP51RB2-20JU          |

|                           |         | Reel    | AT89C51RB2-SLRUM       | AT89LP51RB2-20JU + SL383  |

| AT89C51RB2 to AT89LP51RB2 | VQFP44  | Tray    | AT89C51RB2-RLTUM       | AT89LP51RB2-20AAU         |

|                           |         | Reel    | AT89C51RB2-RLRUM       | AT89LP51RB2-20AAU + SL383 |

|                           | PLCC44  | Stick   | AT89C51RC2-SLSUM       | AT89LP51RC2-20JU          |

|                           |         | Reel    | AT89C51RC2-SLRUM       | AT89LP51RC2-20JU + SL383  |

| AT89C51RC2 to AT89LP51RC2 | VQFP44  | Tray    | AT89C51RC2-RLTUM       | AT89LP51RC2-20AAU         |

|                           |         | Reel    | AT89C51RC2-RLRUM       | AT89LP51RC2-20AAU + SL383 |

|                           | PLCC44  | Stick   | AT89C51IC2-SLSUM       | AT89LP51IC2-20JU          |

|                           |         | Reel    | AT89C51IC2-SLRUM       | AT89LP51IC2-20JU + SL383  |

| AT89C51IC2 to AT89LP51IC2 | VQFP44  | Tray    | AT89C51IC2-RLTUM       | AT89LP51IC2-20AAU         |

|                           |         | Reel    | AT89C51IC2-RLRUM       | AT89LP51IC2-20AAU + SL383 |

### Table 4-1. Ordering Cross Reference AT89C51RB2/RC2/IC2 to AT89LP51RB2/RC2/IC2

# Table 4-2.Packages Not Found in AT89C51RB2/RC2/IC2

| Device                      | Package  | Packing | Ordering Code     |  |  |

|-----------------------------|----------|---------|-------------------|--|--|

|                             | TQFP44   | Tray    | AT89LP51RD2-20AU  |  |  |

| AT89C51BB2 to AT89LP51BB2   | IQFF44   | Reel    | AT89LP51RD2-20AUR |  |  |

| AT 69C5TRD2 to AT 69LP5TRD2 |          | Tray    | AT89LP51RD2-20MU  |  |  |

|                             | VQFN44   | Reel    | AT89LP51RD2-20MUR |  |  |

|                             | TQFP44   | Tray    | AT89LP51ED2-20AU  |  |  |

| AT89C51BC2 to AT89LP51BC2   |          | Reel    | AT89LP51ED2-20AUR |  |  |

|                             | VQFN44   | Tray    | AT89LP51ED2-20MU  |  |  |

|                             |          | Reel    | AT89LP51ED2-20MUR |  |  |

|                             | TOED44   | Tray    | AT89LP51ID2-20AU  |  |  |

| AT89C51IC2 to AT89LP51IC2   | TQFP44   | Reel    | AT89LP51ID2-20AUR |  |  |

| A109031102 10 A1091P31102   | VQFN44   | Tray    | AT89LP51ID2-20MU  |  |  |

|                             | V QF1144 | Reel    | AT89LP51ID2-20MUR |  |  |

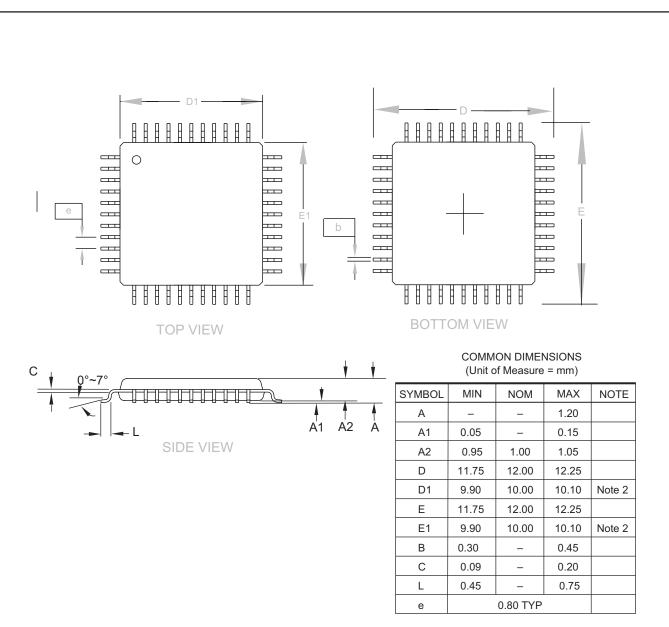

5.2 44A – TQFP

- Notes: 1. This package conforms to JEDEC reference MS-026, Variation ACB.

- 2. Dimensions D1 and E1 do not include mold protrusion. Allowable protrusion is 0.25 mm per side. Dimensions D1 and E1 are maximum plastic body size dimensions including mold mismatch.

- 3. Lead coplanarity is 0.10 mm maximum.

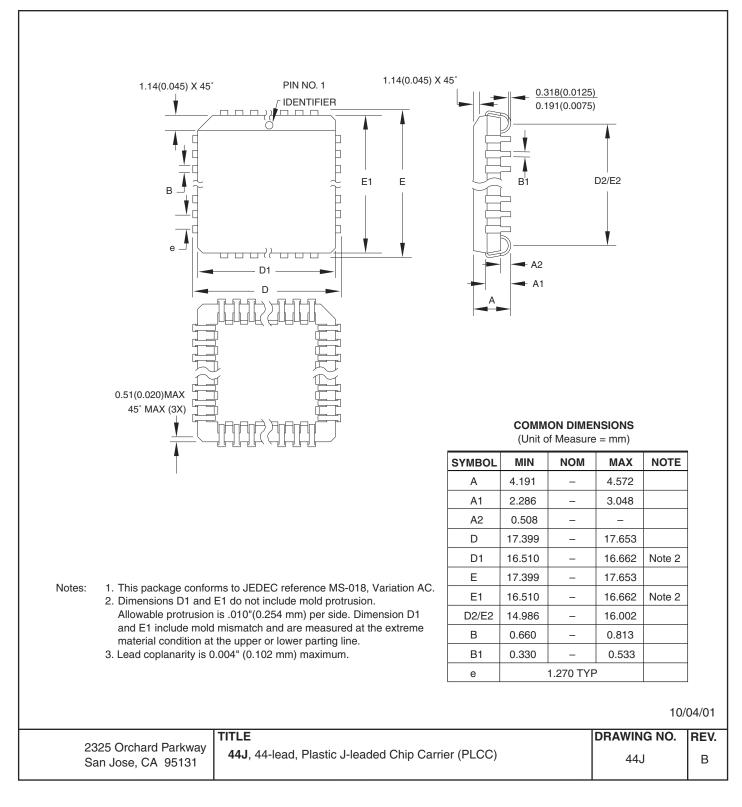

# 5.3 44J – PLCC

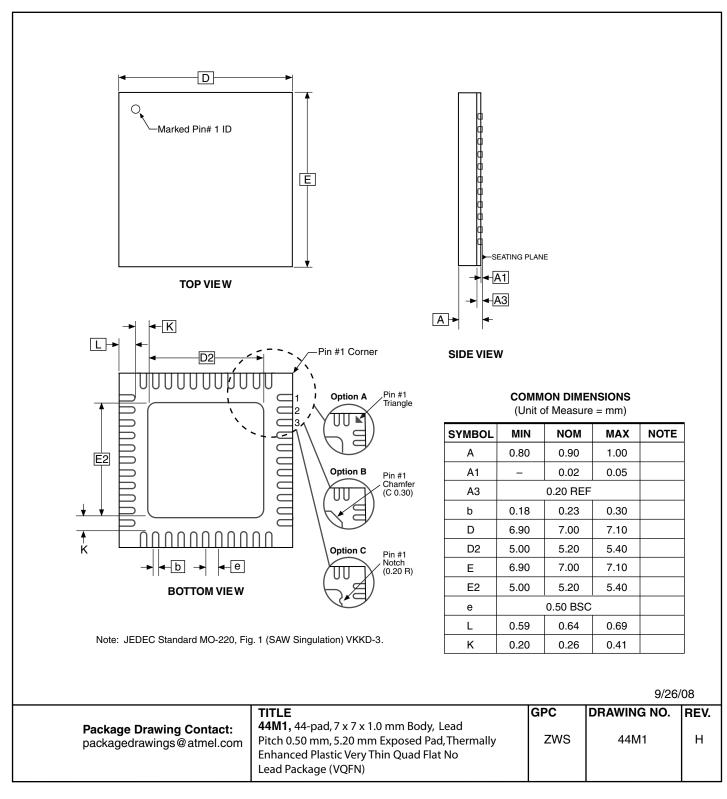

### 5.4 44M1 – VQFN/MLF

Atmel Corporation 2325 Orchard Parkway San Jose, CA 95131 USA Tel: (+1) (408) 441-0311 Fax: (+1) (408) 487-2600 www.atmel.com 8051@atmel.com Atmel Asia Limited Unit 01-5 & 16, 19F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong, Kowloon HONG KONG Tel: (+852) 2245-6100 Fax: (+852) 2722-1369

#### Atmel Munich GmbH

Business Campus Packring 4 D-85748 Garching b. Munich GERMANY Tel: (+49) 89-31970-0 Fax: (+49) 89-3194621

#### Atmel Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 JAPAN Tel: (+81) (3) 3523-3551 Fax: (+81)( 3) 3523-7581

© 2011 Atmel Corporation. All rights reserved.

Atmel<sup>®</sup>, Atmel logo and combinations thereof, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDITIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel applications. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.