# E·XFL

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                 |

|--------------------------------|-----------------------------------------------------------------|

| Product Status                 | Obsolete                                                        |

| Number of LABs/CLBs            | 5968                                                            |

| Number of Logic Elements/Cells | 53712                                                           |

| Total RAM Bits                 | 2322432                                                         |

| Number of I/O                  | 309                                                             |

| Number of Gates                | 3400000                                                         |

| Voltage - Supply               | 1.14V ~ 1.26V                                                   |

| Mounting Type                  | Surface Mount                                                   |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                              |

| Package / Case                 | 484-FBGA, CSPBGA                                                |

| Supplier Device Package        | 484-CSPBGA (19x19)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xa3sd3400a-4csg484i |

|                                |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

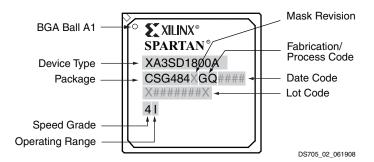

# **Package Marking**

Figure 2 shows the top marking for XA Spartan-3A DSP FPGAs in BGA packages.

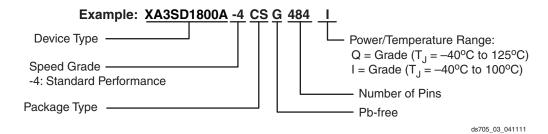

# **Ordering Information**

XA Spartan-3A DSP FPGAs are available in Pb-free packaging only for all device/package combinations.

# **Pb-Free Packaging**

| Device     |    | Speed Grade             | Package Type / Number of Pins |                                             | Temperature Range (T <sub>J</sub> ) |                          |  |

|------------|----|-------------------------|-------------------------------|---------------------------------------------|-------------------------------------|--------------------------|--|

| XA3SD1800A | -4 | Standard<br>Performance | CSG484                        | 484-ball Chip-Scale Ball Grid Array (CSBGA) | I                                   | I-Grade (-40°C to 100°C) |  |

| XA3SD3400A |    | +                       | FGG676                        | 676-ball Fine-Pitch Ball Grid Array (FBGA)  | Q                                   | Q-Grade (-40°C to 125°C) |  |

### Notes:

1. The XA Spartan-3A DSP FPGA product line is available in -4 speed grade only.

2. The XA3SD3400A is available in I-Grade only.

# **Power Supply Specifications**

| Table 5: Supply Voltage Thresholds for Power-On Reset |

|-------------------------------------------------------|

|-------------------------------------------------------|

| Symbol              | Description                                 | Min | Max | Units |

|---------------------|---------------------------------------------|-----|-----|-------|

| V <sub>CCINTT</sub> | Threshold for the V <sub>CCINT</sub> supply | 0.4 | 1.0 | V     |

| V <sub>CCAUXT</sub> | Threshold for the V <sub>CCAUX</sub> supply | 0.8 | 2.0 | V     |

| V <sub>CCO2T</sub>  | Threshold for the $V_{CCO}$ Bank 2 supply   | 0.8 | 2.0 | V     |

### Notes:

2. To ensure successful power-on, V<sub>CCINT</sub>, V<sub>CCO</sub> Bank 2, and V<sub>CCAUX</sub> supplies must rise through their respective threshold-voltage ranges with no dips at any point.

### Table 6: Supply Voltage Ramp Rate

| Symbol              | Description                                               | Min | Мах | Units |

|---------------------|-----------------------------------------------------------|-----|-----|-------|

| V <sub>CCINTR</sub> | Ramp rate from GND to valid $V_{CCINT}$ supply level      | 0.2 | 100 | ms    |

| V <sub>CCAUXR</sub> | Ramp rate from GND to valid $V_{CCAUX}$ supply level      | 0.2 | 100 | ms    |

| V <sub>CCO2R</sub>  | Ramp rate from GND to valid $V_{CCO}$ Bank 2 supply level | 0.2 | 100 | ms    |

### Notes:

1. V<sub>CCINT</sub>, V<sub>CCAUX</sub>, and V<sub>CCO</sub> supplies to the FPGA can be applied in any order. However, the FPGA's configuration source (SPI Flash, parallel NOR Flash, microcontroller) might have specific requirements. Check the data sheet for the attached configuration source. Apply V<sub>CCINT</sub> last for lowest overall power consumption (see <u>UG331</u> chapter "Powering Spartan-3 Generation FPGAs" for more information).

2. To ensure successful power-on, V<sub>CCINT</sub>, V<sub>CCO</sub> Bank 2, and V<sub>CCAUX</sub> supplies must rise through their respective threshold-voltage ranges with no dips at any point.

### Table 7: Supply Voltage Levels Necessary for Preserving CMOS Configuration Latch (CCL) Contents and RAM Data

| Symbol             | Description                                                                      | Min | Units |

|--------------------|----------------------------------------------------------------------------------|-----|-------|

| V <sub>DRINT</sub> | $V_{CCINT}$ level required to retain CMOS Configuration Latch (CCL) and RAM data | 1.0 | V     |

| V <sub>DRAUX</sub> | $V_{CCAUX}$ level required to retain CMOS Configuration Latch (CCL) and RAM data | 2.0 | V     |

<sup>1.</sup> V<sub>CCINT</sub>, V<sub>CCAUX</sub>, and V<sub>CCO</sub> supplies to the FPGA can be applied in any order. However, the FPGA's configuration source (SPI Flash, parallel NOR Flash, microcontroller) might have specific requirements. Check the data sheet for the attached configuration source. Apply V<sub>CCINT</sub> last for lowest overall power consumption (see <u>UG331</u> chapter "Powering Spartan-3 Generation FPGAs" for more information).

# **Quiescent Current Requirements**

Table 10: Quiescent Supply Current Characteristics

| Symbol              | Description                                 | Device     | Typical <sup>(2)</sup> | l-Grade<br>Maximum <sup>(2)</sup> | Q-Grade<br>Maximum <sup>(2)</sup> | Units |

|---------------------|---------------------------------------------|------------|------------------------|-----------------------------------|-----------------------------------|-------|

| I <sub>CCINTQ</sub> | Quiescent V <sub>CCINT</sub> supply current | XA3SD1800A | 41                     | 500                               | 900                               | mA    |

|                     |                                             | XA3SD3400A | 64                     | 725                               | -                                 | mA    |

| Iccoq               | Quiescent V <sub>CCO</sub> supply current   | XA3SD1800A | 0.4                    | 5                                 | 5                                 | mA    |

|                     |                                             | XA3SD3400A | 0.4                    | 5                                 | -                                 | mA    |

| I <sub>CCAUXQ</sub> | Quiescent V <sub>CCAUX</sub> supply current | XA3SD1800A | 25                     | 110                               | 145                               | mA    |

|                     |                                             | XA3SD3400A | 39                     | 160                               | -                                 | mA    |

### Notes:

- 1. The numbers in this table are based on the conditions set forth in Table 8.

- 2. Quiescent supply current is measured with all I/O drivers in a high-impedance state and with all pull-up/pull-down resistors at the I/O pads disabled. Typical values are characterized using typical devices at room temperature (T<sub>J</sub> of 25°C at V<sub>CCINT</sub> = 1.2V, V<sub>CCO</sub> = 3.3V, and V<sub>CCAUX</sub> = 2.5V). The maximum limits are tested for each device at the respective maximum specified junction temperature and at maximum voltage limits with V<sub>CCINT</sub> = 1.26V, V<sub>CCO</sub> = 3.6V, and V<sub>CCAUX</sub> = 3.6V. The FPGA is programmed with a "blank" configuration data file (that is, a design with no functional elements instantiated). For conditions other than those described above (for example, a design including functional elements), measured quiescent current levels will be different than the values in the table.

There are two recommended ways to estimate the total power consumption (quiescent plus dynamic) for a specific design: a) The <u>Spartan-3A DSP FPGA XPower Estimator</u> provides quick, approximate, typical estimates, and does not require a netlist of the design. b) XPower Analyzer uses a netlist as input to provide maximum estimates as well as more accurate typical estimates.

4. The maximum numbers in this table indicate the minimum current each power rail requires in order for the FPGA to power-on successfully.

5. For information on the power-saving Suspend mode, see XAPP480, Using Suspend Mode in Spartan-3 Generation FPGAs. Suspend mode typically saves 40% total power consumption compared to quiescent current.

|                         |                   |                         | nditions                | Logic Level Characteristics |                            |  |

|-------------------------|-------------------|-------------------------|-------------------------|-----------------------------|----------------------------|--|

| IOSTANDAR               | ID Attribute      | l <sub>OL</sub><br>(mA) | I <sub>ОН</sub><br>(mA) | V <sub>OL</sub><br>Max (V)  | V <sub>OH</sub><br>Min (V) |  |

| LVTTL <sup>(3)</sup>    | 2                 | 2                       | -2                      | 0.4                         | 2.4                        |  |

|                         | 4                 | 4                       | -4                      |                             |                            |  |

|                         | 6                 | 6                       | 6                       |                             |                            |  |

|                         | 8                 | 8                       | -8                      |                             |                            |  |

|                         | 12                | 12                      | -12                     |                             |                            |  |

|                         | 16                | 16                      | -16                     |                             |                            |  |

|                         | 24                | 24 <sup>(6)</sup>       | -24                     |                             |                            |  |

| LVCMOS33 <sup>(3)</sup> | 2                 | 2                       | -2                      | 0.4                         | V <sub>CCO</sub> – 0.4     |  |

|                         | 4                 | 4                       | -4                      |                             |                            |  |

|                         | 6                 | 6                       | -6                      |                             |                            |  |

|                         | 8                 | 8                       | -8                      | ]                           |                            |  |

|                         | 12                | 12                      | -12                     |                             |                            |  |

|                         | 16                | 16                      | -16 <sup>(6)</sup>      |                             |                            |  |

|                         | 24 <sup>(4)</sup> | 24                      | -24 <sup>(6)</sup>      |                             |                            |  |

| LVCMOS25 <sup>(3)</sup> | 2                 | 2                       | -2                      | 0.4                         | V <sub>CCO</sub> – 0.4     |  |

|                         | 4                 | 4                       | -4                      |                             |                            |  |

|                         | 6                 | 6                       | -6                      |                             |                            |  |

|                         | 8                 | 8                       | -8                      |                             |                            |  |

|                         | 12                | 12                      | -12                     |                             |                            |  |

|                         | 16 <sup>(4)</sup> | 16                      | -16 <sup>(6)</sup>      |                             |                            |  |

|                         | 24 <sup>(4)</sup> | 24 <sup>(6)</sup>       | -24 <sup>(6)</sup>      |                             |                            |  |

| LVCMOS18 <sup>(3)</sup> | 2                 | 2                       | -2                      | 0.4                         | V <sub>CCO</sub> – 0.4     |  |

|                         | 4                 | 4                       | -4                      |                             |                            |  |

|                         | 6                 | 6                       | -6 <sup>(6)</sup>       |                             |                            |  |

|                         | 8                 | 8                       | -8                      |                             |                            |  |

|                         | 12 <sup>(4)</sup> | 12                      | -12 <sup>(6)</sup>      |                             |                            |  |

|                         | 16 <sup>(4)</sup> | 16                      | -16                     |                             |                            |  |

| LVCMOS15 <sup>(3)</sup> | 2                 | 2                       | -2                      | 0.4                         | V <sub>CCO</sub> – 0.4     |  |

|                         | 4                 | 4                       | -4                      |                             |                            |  |

|                         | 6                 | 6                       | -6                      |                             |                            |  |

|                         | 8(4)              | 8                       | -8                      |                             |                            |  |

|                         | 12 <sup>(4)</sup> | 12                      | -12                     |                             |                            |  |

| LVCMOS12 <sup>(3)</sup> | 2                 | 2                       | -2                      | 0.4                         | V <sub>CCO</sub> – 0.4     |  |

|                         | 4(4)              | 4                       | -4                      |                             |                            |  |

|                         | 6 <sup>(4)</sup>  | 6                       | -6                      |                             |                            |  |

| PCI33_3 <sup>(5)</sup>  |                   | 1.5                     | -0.5                    | 10% V <sub>CCO</sub>        | 90% V <sub>CCO</sub>       |  |

### Table 12: DC Characteristics of User I/Os Using Single-Ended Standards

|                                | V <sub>CCO</sub> for Drivers <sup>(1)</sup> |             |         | V <sub>ID</sub> |          |          | V <sub>ICM</sub> <sup>(2)</sup> |         |                    |

|--------------------------------|---------------------------------------------|-------------|---------|-----------------|----------|----------|---------------------------------|---------|--------------------|

| IOSTANDARD Attribute           | Min (V)                                     | Nom (V)     | Max (V) | Min (mV)        | Nom (mV) | Max (mV) | Min (V)                         | Nom (V) | Max (V)            |

| LVDS_25 <sup>(3)</sup>         | 2.25                                        | 2.5         | 2.75    | 100             | 350      | 600      | 0.3                             | 1.25    | 2.35               |

| LVDS_33 <sup>(3)</sup>         | 3.0                                         | 3.3         | 3.6     | 100             | 350      | 600      | 0.3                             | 1.25    | 2.35               |

| BLVDS_25 <sup>(4)</sup>        | 2.25                                        | 2.5         | 2.75    | 100             | 300      | -        | 0.3                             | 1.3     | 2.35               |

| MINI_LVDS_25 <sup>(3)</sup>    | 2.25                                        | 2.5         | 2.75    | 200             | -        | 600      | 0.3                             | 1.2     | 1.95               |

| MINI_LVDS_33 <sup>(3)</sup>    | 3.0                                         | 3.3         | 3.6     | 200             | -        | 600      | 0.3                             | 1.2     | 1.95               |

| LVPECL_25 <sup>(5)</sup>       |                                             | Inputs Only |         | 100             | 800      | 1000     | 0.3                             | 1.2     | 1.95               |

| LVPECL_33 <sup>(5)</sup>       |                                             | Inputs Only |         | 100             | 800      | 1000     | 0.3                             | 1.2     | 2.8 <sup>(6)</sup> |

| RSDS_25 <sup>(3)</sup>         | 2.25                                        | 2.5         | 2.75    | 100             | 200      | -        | 0.3                             | 1.2     | 1.5                |

| RSDS_33 <sup>(3)</sup>         | 3.0                                         | 3.3         | 3.6     | 100             | 200      | -        | 0.3                             | 1.2     | 1.5                |

| TMDS_33 <sup>(3,4,7)</sup>     | 3.14                                        | 3.3         | 3.47    | 150             | -        | 1200     | 2.7                             | -       | 3.23               |

| PPDS_25 <sup>(3)</sup>         | 2.25                                        | 2.5         | 2.75    | 100             | -        | 400      | 0.2                             | -       | 2.3                |

| PPDS_33 <sup>(3)</sup>         | 3.0                                         | 3.3         | 3.6     | 100             | -        | 400      | 0.2                             | -       | 2.3                |

| DIFF_HSTL_I_18                 | 1.7                                         | 1.8         | 1.9     | 100             | -        | -        | 0.8                             | -       | 1.1                |

| DIFF_HSTL_II_18 <sup>(8)</sup> | 1.7                                         | 1.8         | 1.9     | 100             | -        | -        | 0.8                             | -       | 1.1                |

| DIFF_HSTL_III_18               | 1.7                                         | 1.8         | 1.9     | 100             | -        | -        | 0.8                             | -       | 1.1                |

| DIFF_HSTL_I                    | 1.4                                         | 1.5         | 1.6     | 100             | -        | -        | 0.68                            |         | 0.9                |

| DIFF_HSTL_III                  | 1.4                                         | 1.5         | 1.6     | 100             | -        | -        | -                               | 0.9     | -                  |

| DIFF_SSTL18_I                  | 1.7                                         | 1.8         | 1.9     | 100             | -        | -        | 0.7                             | -       | 1.1                |

| DIFF_SSTL18_II <sup>(8)</sup>  | 1.7                                         | 1.8         | 1.9     | 100             | -        | -        | 0.7                             | -       | 1.1                |

| DIFF_SSTL2_I                   | 2.3                                         | 2.5         | 2.7     | 100             | -        | -        | 1.0                             | -       | 1.5                |

| DIFF_SSTL2_II <sup>(8)</sup>   | 2.3                                         | 2.5         | 2.7     | 100             | -        | -        | 1.0                             | -       | 1.5                |

| DIFF_SSTL3_I                   | 3.0                                         | 3.3         | 3.6     | 100             | -        | -        | 1.1                             | -       | 1.9                |

| DIFF_SSTL3_II                  | 3.0                                         | 3.3         | 3.6     | 100             | -        | -        | 1.1                             | -       | 1.9                |

### Table 13: Recommended Operating Conditions for User I/Os Using Differential Signal Standards

#### Notes:

1. The V<sub>CCO</sub> rails supply only differential output drivers, not input circuits.

2.

$V_{ICM}$  must be less than  $V_{CCAUX}$ . These true differential output standards are supported only on FPGA banks 0 and 2. Inputs are unrestricted. See the chapter "Using I/O Resources" in UG331. 3.

See External Termination Requirements for Differential I/O, page 16. 4.

LVPECL is supported on inputs only, not outputs. LVPECL\_33 requires V<sub>CCAUX</sub> = 3.3V ± 10%. 5.

6.

7.

8.

EVPECL as supported on inputs only, not outputs. EVPECL\_33 requires  $V_{CCAUX} = 0.37 \pm 10\%$ . EVPECL\_33 maximum  $V_{ICM}$  = the lower of 2.8V or  $V_{CCAUX} - (V_{ID}/2)$ . Requires  $V_{CCAUX} = 3.3V \pm 10\%$  for inputs. ( $V_{CCAUX} - 300 \text{ mV}$ )  $\leq V_{ICM} \leq (V_{CCAUX} - 37 \text{ mV})$ These higher-drive output standards are supported only on FPGA banks 1 and 3. Inputs are unrestricted. See the chapter "Using I/O Resources" in UG331.  $V_{REF}$  inputs are used for the DIFF\_SSTL and DIFF\_HSTL standards. The  $V_{REF}$  settings are the same as for the single-ended versions in Table 11. Other differential 9. standards do not use V<sub>REF</sub>

www.xilinx.com

# I/O Timing

### Pin-to-Pin Clock-to-Output Times

### Table 18: Pin-to-Pin Clock-to-Output Times for the IOB Output Path

| Symbol                | Department                                                           | Conditions                                                                                                              | Device     | Speed Grade: -4 | Units |

|-----------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------|-----------------|-------|

|                       | Description                                                          | Conditions                                                                                                              | Device     | Max             | Units |

| Clock-to-Out          | put Times                                                            |                                                                                                                         |            |                 |       |

| T <sub>ICKOFDCM</sub> |                                                                      | ctive transition on the Global output drive, Fast slew ppearing at the Output pin. rate, with DCM <sup>(3)</sup> XA3SD3 | XA3SD1800A | 3.51            | ns    |

|                       | Clock pin to data appearing at the Output pin.<br>The DCM is in use. |                                                                                                                         | XA3SD3400A | 3.82            | ns    |

| T <sub>ICKOF</sub>    |                                                                      | LVCMOS25 <sup>(2)</sup> , 12mA output drive, Fast slew                                                                  | XA3SD1800A | 5.58            | ns    |

|                       | appearing at the Output pin. The DCM is not in use.                  | rate, without DCM                                                                                                       | XA3SD3400A | 6.13            | ns    |

### Notes:

1. The numbers in this table are tested using the methodology presented in Table 27 and are based on the operating conditions set forth in Table 8 and Table 11.

2. This clock-to-output time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the Global Clock Input or a standard other than LVCMOS25 with 12 mA drive and Fast slew rate is assigned to the data Output. If the former is true, *add* the appropriate Input adjustment from Table 23. If the latter is true, *add* the appropriate Output adjustment from Table 26.

3. DCM output jitter is included in all measurements.

### **Pin-to-Pin Setup and Hold Times**

### Table 19: Pin-to-Pin Setup and Hold Times for the IOB Input Path (System Synchronous)

| Symbol             | Description                                                                                      | Conditions                                                                | Device     | Speed Grade: -4 | L lucito |  |

|--------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------|-----------------|----------|--|

| Symbol             | Description                                                                                      | Conditions                                                                | Device     | Min             | Units    |  |

| Setup Times        |                                                                                                  |                                                                           |            |                 |          |  |

| T <sub>PSDCM</sub> | When writing to the Input Flip-Flop (IFF), the time from the setup of data at the Input pin to   | LVCMOS25 <sup>(2)</sup> ,<br>IFD_DELAY_VALUE=0,                           | XA3SD1800A | 3.11            | ns       |  |

|                    | the active transition at a Global Clock pin. The DCM is in use. No Input Delay is programmed.    | with DCM <sup>(4)</sup>                                                   | XA3SD3400A | 2.49            | ns       |  |

| T <sub>PSFD</sub>  | When writing to IFF, the time from the setup of data at the Input pin to an active transition at | pin to an active transition at IFD_DELAY_VALUE = 0                        | XA3SD1800A | 3.39            | ns       |  |

|                    | the Global Clock pin. The DCM is not in use.<br>The Input Delay is programmed.                   | without DCM                                                               | XA3SD3400A | 3.08            | ns       |  |

| Hold Times         |                                                                                                  | 1                                                                         |            |                 |          |  |

| T <sub>PHDCM</sub> | When writing to IFF, the time from the active transition at the Global Clock pin to the point    | n to the point IFD_DELAY_VALUE = 0, with DCM <sup>(4)</sup> XA3SD3400A -0 | XA3SD1800A | -0.38           | ns       |  |

|                    | when data must be held at the Input pin. The DCM is in use. No Input Delay is programmed.        |                                                                           | -0.26      | ns              |          |  |

| T <sub>PHFD</sub>  | When writing to IFF, the time from the active transition at the Global Clock pin to the point    | LVCMOS25 <sup>(3)</sup> ,<br>IFD_DELAY_VALUE=6,                           | XA3SD1800A | -0.71           | ns       |  |

|                    | when data must be held at the Input pin. The DCM is not in use. The Input Delay is programmed.   | without DCM                                                               | XA3SD3400A | -0.65           | ns       |  |

Notes:

2. This setup time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the Global Clock Input or the data Input. If this is true of the Global Clock Input, subtract the appropriate adjustment from Table 23. If this is true of the data Input, add the appropriate Input adjustment from the same table.

3. This hold time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the Global Clock Input or the data Input. If this is true of the Global Clock Input, add the appropriate Input adjustment from Table 23. If this is true of the data Input, subtract the appropriate Input adjustment from the same table. When the hold time is negative, it is possible to change the data before the clock's active edge.

4. DCM output jitter is included in all measurements.

<sup>1.</sup> The numbers in this table are tested using the methodology presented in Table 27 and are based on the operating conditions set forth in Table 8 and Table 11.

# Input Setup and Hold Times

# Table 20: Setup and Hold Times for the IOB Input Path

| Symbol               | Description                                                                                               | Conditions              | IFD_DELAY | Device     | Speed Grade: -4 | Units |

|----------------------|-----------------------------------------------------------------------------------------------------------|-------------------------|-----------|------------|-----------------|-------|

| Cymbol               | Decemption                                                                                                | Conditione              | _VALUE    | Min        | Min             | onito |

| Setup Tim            | es                                                                                                        |                         |           |            |                 |       |

| T <sub>IOPICK</sub>  | Time from the setup of data at the Input pin to                                                           | LVCMOS25 <sup>(2)</sup> | 0         | XA3SD1800A | 1.81            | ns    |

|                      | the active transition at the ICLK input of the<br>Input Flip-Flop (IFF). No Input Delay is<br>programmed. |                         |           | XA3SD3400A | 1.88            | ns    |

| T <sub>IOPICKD</sub> | Time from the setup of data at the Input pin to                                                           | LVCMOS25 <sup>(2)</sup> | 1         | XA3SD1800A | 2.24            | ns    |

|                      | the active transition at the ICLK input of the<br>Input Flip-Flop (IFF). The Input Delay is               |                         | 2         |            | 2.83            | ns    |

|                      | programmed.                                                                                               |                         | 3         | XA3SD3400A | 3.64            | ns    |

|                      |                                                                                                           |                         | 4         |            | 4.20            | ns    |

|                      |                                                                                                           |                         | 5         |            | 4.16            | ns    |

|                      |                                                                                                           |                         | 6         |            | 5.09            | ns    |

|                      |                                                                                                           |                         | 7         |            | 6.02            | ns    |

|                      |                                                                                                           |                         | 8         |            | 6.63            | ns    |

|                      |                                                                                                           |                         | 1         |            | 2.44            | ns    |

|                      |                                                                                                           |                         | 2         |            | 3.02            | ns    |

|                      |                                                                                                           |                         | 3         |            | 3.81            | ns    |

|                      |                                                                                                           |                         | 4         |            | 4.39            | ns    |

|                      |                                                                                                           |                         | 5         | -          | 4.26            | ns    |

|                      |                                                                                                           |                         | 6         |            | 5.08            | ns    |

|                      |                                                                                                           |                         | 7         |            | 5.95            | ns    |

|                      |                                                                                                           |                         | 8         | ]          | 6.55            | ns    |

| Convert Output Time from LV |                          |       | Add the Adjustment Below | Unite |  |

|-----------------------------|--------------------------|-------|--------------------------|-------|--|

|                             | Signal Standard (IOSTAND |       | Speed Grade: -4          |       |  |

| LVCMOS33                    | Slow                     | 2 mA  | 5.58                     | ns    |  |

|                             |                          | 4 mA  | 3.30                     | ns    |  |

|                             |                          | 6 mA  | 3.30                     | ns    |  |

|                             |                          | 8 mA  | 2.26                     | ns    |  |

|                             |                          | 12 mA | 1.29                     | ns    |  |

|                             |                          | 16 mA | 1.21                     | ns    |  |

|                             |                          | 24 mA | 2.79                     | ns    |  |

|                             | Fast                     | 2 mA  | 3.72                     | ns    |  |

|                             |                          | 4 mA  | 2.04                     | ns    |  |

|                             |                          | 6 mA  | 2.08                     | ns    |  |

|                             |                          | 8 mA  | 0.53                     | ns    |  |

|                             |                          | 12 mA | 0.59                     | ns    |  |

|                             |                          | 16 mA | 0.59                     | ns    |  |

|                             |                          | 24 mA | 0.51                     | ns    |  |

|                             | QuietIO                  | 2 mA  | 27.67                    | ns    |  |

|                             |                          | 4 mA  | 27.67                    | ns    |  |

|                             |                          | 6 mA  | 27.67                    | ns    |  |

|                             |                          | 8 mA  | 16.71                    | ns    |  |

|                             |                          | 12 mA | 16.29                    | ns    |  |

|                             |                          | 16 mA | 16.18                    | ns    |  |

|                             |                          | 24 mA | 12.11                    | ns    |  |

### Table 26: Output Timing Adjustments for IOB (Cont'd)

| Convert Output Time from LVCM  | IOS25 with 12mA Drive a | nd Fast | Add the Adjustment Below | Units |

|--------------------------------|-------------------------|---------|--------------------------|-------|

| Slew Rate to the Following Sig | gnal Standard (IOSTAND  | ARD)    | Speed Grade: -4          | Units |

| LVCMOS15                       | Slow                    | 2 mA    | 6.41                     | ns    |

|                                |                         | 4 mA    | 3.97                     | ns    |

|                                |                         | 6 mA    | 3.21                     | ns    |

|                                |                         | 8 mA    | 2.53                     | ns    |

|                                |                         | 12 mA   | 2.06                     | ns    |

|                                | Fast                    | 2 mA    | 5.83                     | ns    |

|                                |                         | 4 mA    | 3.05                     | ns    |

|                                |                         | 6 mA    | 1.95                     | ns    |

|                                |                         | 8 mA    | 1.60                     | ns    |

|                                |                         | 12 mA   | 1.30                     | ns    |

|                                | QuietIO                 | 2 mA    | 34.11                    | ns    |

|                                |                         | 4 mA    | 25.66                    | ns    |

|                                |                         | 6 mA    | 24.64                    | ns    |

|                                |                         | 8 mA    | 22.06                    | ns    |

|                                |                         | 12 mA   | 20.64                    | ns    |

| LVCMOS12                       | Slow                    | 2 mA    | 7.14                     | ns    |

|                                |                         | 4 mA    | 4.87                     | ns    |

|                                |                         | 6 mA    | 5.67                     | ns    |

|                                | Fast                    | 2 mA    | 6.77                     | ns    |

|                                |                         | 4 mA    | 5.02                     | ns    |

|                                |                         | 6 mA    | 4.09                     | ns    |

|                                | QuietIO                 | 2 mA    | 50.76                    | ns    |

|                                |                         | 4 mA    | 43.17                    | ns    |

|                                |                         | 6 mA    | 37.31                    | ns    |

| PCI33_3                        | · · · ·                 |         | 0.34                     | ns    |

| HSTL_I                         |                         |         | 0.85                     | ns    |

| HSTL_III                       |                         |         | 1.16                     | ns    |

| HSTL_I_18                      |                         |         | 0.35                     | ns    |

| HSTL_II_18                     |                         |         | 0.30                     | ns    |

| HSTL_III_18                    |                         |         | 0.47                     | ns    |

| SSTL18_I                       |                         |         | 0.40                     | ns    |

| SSTL18_II                      |                         |         | 0.30                     | ns    |

| SSTL2_I                        |                         |         | 0.00                     | ns    |

| SSTL2_II                       |                         |         | -0.05                    | ns    |

| SSTL3_I                        |                         |         | 0.00                     | ns    |

| SSTL3_II                       |                         |         | 0.17                     | ns    |

### Table 26: Output Timing Adjustments for IOB (Cont'd)

| Convert Output Time from LVCMOS25 with 12mA Drive and Fast | Add the Adjustment Below | Units |

|------------------------------------------------------------|--------------------------|-------|

| Slew Rate to the Following Signal Standard (IOSTANDARD)    | Speed Grade: -4          | Units |

| Differential Standards                                     |                          |       |

| LVDS_25                                                    | 1.49                     | ns    |

| LVDS_33                                                    | 0.46                     | ns    |

| BLVDS_25                                                   | 0.11                     | ns    |

| MINI_LVDS_25                                               | 1.11                     | ns    |

| MINI_LVDS_33                                               | 0.41                     | ns    |

| LVPECL_25                                                  | Input Only               |       |

| LVPECL_33                                                  |                          |       |

| RSDS_25                                                    | 1.72                     | ns    |

| RSDS_33                                                    | 0.64                     | ns    |

| TMDS_33                                                    | 0.46                     | ns    |

| PPDS_25                                                    | 1.28                     | ns    |

| PPDS_33                                                    | 0.88                     | ns    |

| DIFF_HSTL_I_18                                             | 0.43                     | ns    |

| DIFF_HSTL_II_18                                            | 0.41                     | ns    |

| DIFF_HSTL_III_18                                           | 0.36                     | ns    |

| DIFF_HSTL_I                                                | 1.01                     | ns    |

| DIFF_HSTL_III                                              | 1.16                     | ns    |

| DIFF_SSTL18_I                                              | 0.49                     | ns    |

| DIFF_SSTL18_II                                             | 0.41                     | ns    |

| DIFF_SSTL2_I                                               | 0.91                     | ns    |

| DIFF_SSTL2_II                                              | 0.10                     | ns    |

| DIFF_SSTL3_I                                               | 1.18                     | ns    |

| DIFF_SSTL3_II                                              | 0.28                     | ns    |

|                                                            | 1                        |       |

### Table 26: Output Timing Adjustments for IOB (Cont'd)

Notes:

1. The numbers in this table are tested using the methodology presented in Table 27 and are based on the operating conditions set forth in Table 8, Table 11, and Table 13.

2. These adjustments are used to convert output- and three-state-path times originally specified for the LVCMOS25 standard with 12 mA drive and Fast slew rate to times that correspond to other signal standards. Do not adjust times that measure when outputs go into a high-impedance state.

| Signal Standard  |                      | Inputs                   |                          | Out                               | puts               | Inputs and<br>Outputs |

|------------------|----------------------|--------------------------|--------------------------|-----------------------------------|--------------------|-----------------------|

| (IŎSTANDARD)     | V <sub>REF</sub> (V) | V <sub>L</sub> (V)       | V <sub>H</sub> (V)       | <b>R<sub>T</sub> (</b> Ω <b>)</b> | V <sub>T</sub> (V) | V <sub>M</sub> (V)    |

| SSTL2_II         | 1.25                 | V <sub>REF</sub> – 0.75  | V <sub>REF</sub> + 0.75  | 25                                | 1.25               | V <sub>REF</sub>      |

| SSTL3_I          | 1.5                  | V <sub>REF</sub> – 0.75  | V <sub>REF</sub> + 0.75  | 50                                | 1.5                | V <sub>REF</sub>      |

| SSTL3_II         | 1.5                  | V <sub>REF</sub> – 0.75  | V <sub>REF</sub> + 0.75  | 25                                | 1.5                | V <sub>REF</sub>      |

| Differential     | I                    |                          | · · ·                    |                                   |                    |                       |

| LVDS_25          | -                    | V <sub>ICM</sub> - 0.125 | V <sub>ICM</sub> + 0.125 | 50                                | 1.2                | V <sub>ICM</sub>      |

| LVDS_33          | _                    | V <sub>ICM</sub> – 0.125 | V <sub>ICM</sub> + 0.125 | 50                                | 1.2                | V <sub>ICM</sub>      |

| BLVDS_25         | -                    | V <sub>ICM</sub> – 0.125 | V <sub>ICM</sub> + 0.125 | 1M                                | 0                  | V <sub>ICM</sub>      |

| MINI_LVDS_25     | -                    | V <sub>ICM</sub> – 0.125 | V <sub>ICM</sub> + 0.125 | 50                                | 1.2                | V <sub>ICM</sub>      |

| MINI_LVDS_33     | -                    | V <sub>ICM</sub> – 0.125 | V <sub>ICM</sub> + 0.125 | 50                                | 1.2                | V <sub>ICM</sub>      |

| LVPECL_25        | -                    | V <sub>ICM</sub> - 0.3   | V <sub>ICM</sub> + 0.3   | N/A                               | N/A                | V <sub>ICM</sub>      |

| LVPECL_33        | _                    | V <sub>ICM</sub> - 0.3   | V <sub>ICM</sub> + 0.3   | N/A                               | N/A                | V <sub>ICM</sub>      |

| RSDS_25          | _                    | V <sub>ICM</sub> - 0.1   | V <sub>ICM</sub> + 0.1   | 50                                | 1.2                | V <sub>ICM</sub>      |

| RSDS_33          | -                    | V <sub>ICM</sub> - 0.1   | V <sub>ICM</sub> + 0.1   | 50                                | 1.2                | V <sub>ICM</sub>      |

| TMDS_33          | -                    | V <sub>ICM</sub> - 0.1   | V <sub>ICM</sub> + 0.1   | 50                                | 3.3                | V <sub>ICM</sub>      |

| PPDS_25          | _                    | V <sub>ICM</sub> - 0.1   | V <sub>ICM</sub> + 0.1   | 50                                | 0.8                | V <sub>ICM</sub>      |

| PPDS_33          | -                    | V <sub>ICM</sub> - 0.1   | V <sub>ICM</sub> + 0.1   | 50                                | 0.8                | V <sub>ICM</sub>      |

| DIFF_HSTL_I      | 0.9                  | V <sub>REF</sub> – 0.5   | V <sub>REF</sub> + 0.5   | 50                                | 0.9                | V <sub>REF</sub>      |

| DIFF_HSTL_III    | 0.9                  | V <sub>REF</sub> – 0.5   | V <sub>REF</sub> + 0.5   | 50                                | 0.9                | V <sub>REF</sub>      |

| DIFF_HSTL_I_18   | 0.9                  | V <sub>REF</sub> – 0.5   | V <sub>REF</sub> + 0.5   | 50                                | 0.9                | V <sub>REF</sub>      |

| DIFF_HSTL_II_18  | 0.9                  | V <sub>REF</sub> – 0.5   | V <sub>REF</sub> + 0.5   | 50                                | 0.9                | V <sub>REF</sub>      |

| DIFF_HSTL_III_18 | 1.1                  | V <sub>REF</sub> – 0.5   | V <sub>REF</sub> + 0.5   | 50                                | 1.8                | V <sub>REF</sub>      |

| DIFF_SSTL18_I    | 0.9                  | V <sub>REF</sub> – 0.5   | V <sub>REF</sub> + 0.5   | 50                                | 0.9                | V <sub>REF</sub>      |

| DIFF_SSTL18_II   | 0.9                  | V <sub>REF</sub> – 0.5   | V <sub>REF</sub> + 0.5   | 50                                | 0.9                | V <sub>REF</sub>      |

| DIFF_SSTL2_I     | 1.25                 | V <sub>REF</sub> – 0.5   | V <sub>REF</sub> + 0.5   | 50                                | 1.25               | V <sub>REF</sub>      |

| DIFF_SSTL2_II    | 1.25                 | V <sub>REF</sub> – 0.5   | V <sub>REF</sub> + 0.5   | 50                                | 1.25               | V <sub>REF</sub>      |

| DIFF_SSTL3_I     | 1.5                  | V <sub>REF</sub> – 0.5   | V <sub>REF</sub> + 0.5   | 50                                | 1.5                | V <sub>REF</sub>      |

| DIFF_SSTL3_II    | 1.5                  | V <sub>REF</sub> – 0.5   | V <sub>REF</sub> + 0.5   | 50                                | 1.5                | V <sub>REF</sub>      |

### Table 27: Test Methods for Timing Measurement at I/Os (Cont'd)

### Notes:

- 1. Descriptions of the relevant symbols are as follows:

- $V_{REF}$  The reference voltage for setting the input switching threshold  $V_{ICM}$  The common mode input voltage  $V_M$  Voltage of measurement point on signal transition  $V_L$  Low-level test voltage at Input pin

- $R_T$  Effective termination resistance, which takes on a value of 1  $M\Omega$  when no parallel termination is required  $V_T$  Termination voltage

- The load capacitance (C<sub>I</sub>) at the Output pin is 0 pF for all signal standards. 2.

- З. According to the PCI specification.

The capacitive load (C<sub>1</sub>) is connected between the output and GND. The Output timing for all standards, as published in the speed files and the data sheet, is always based on a C<sub>L</sub> value of zero. High-impedance probes (less than 1 pF) are used for all measurements. Any delay that the test fixture might contribute to test measurements is subtracted from those measurements to produce the final timing numbers as published in the speed files and data sheet.

| 0:       |                       |    | Package Type: CS        | G484 and FGG676         |

|----------|-----------------------|----|-------------------------|-------------------------|

| Signal   | Standard (IOSTANDARD) |    | Top, Bottom (Banks 0,2) | Left, Right (Banks 1,3) |

| LVCMOS33 | Slow                  | 2  | 76                      | 76                      |

|          |                       | 4  | 46                      | 46                      |

|          |                       | 6  | 27                      | 27                      |

|          |                       | 8  | 20                      | 20                      |

|          |                       | 12 | 13                      | 13                      |

|          |                       | 16 | 10                      | 10                      |

|          |                       | 24 | -                       | 9                       |

|          | Fast                  | 2  | 10                      | 10                      |

|          |                       | 4  | 8                       | 8                       |

|          |                       | 6  | 5                       | 5                       |

|          |                       | 8  | 4                       | 4                       |

|          |                       | 12 | 4                       | 4                       |

|          |                       | 16 | 2                       | 2                       |

|          |                       | 24 | -                       | 2                       |

|          | QuietIO               | 2  | 76                      | 76                      |

|          |                       | 4  | 46                      | 46                      |

|          |                       | 6  | 32                      | 32                      |

|          |                       | 8  | 26                      | 26                      |

|          |                       | 12 | 18                      | 18                      |

|          |                       | 16 | 14                      | 14                      |

|          |                       | 24 | -                       | 10                      |

# Table 29: Recommended Number of Simultaneously Switching Outputs per V<sub>CCO</sub>/GND Pair (V<sub>CCAUX</sub>=3.3V) (Cont'd)

www.xilinx.com

# **Configurable Logic Block Timing**

# Table 30: CLB (SLICEM) Timing

| Symbol               | Deservition                                                                                                                             | Speed Grade: -4 |      | Units |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|-------|

| Symbol               | Description                                                                                                                             | Min             | Мах  | Units |

| Clock-to-Output      | Times                                                                                                                                   |                 |      | I     |

| Т <sub>СКО</sub>     | When reading from the FFX (FFY) Flip-Flop, the time from the active transition at the CLK input to data appearing at the XQ (YQ) output | -               | 0.68 | ns    |

| Setup Times          |                                                                                                                                         |                 | 1    | I     |

| T <sub>AS</sub>      | Time from the setup of data at the F or G input to the active transition at the CLK input of the CLB                                    | 0.36            | -    | ns    |

| T <sub>DICK</sub>    | Time from the setup of data at the BX or BY input to the active transition at the CLK input of the CLB                                  | 1.88            | -    | ns    |

| Hold Times           |                                                                                                                                         |                 |      |       |

| T <sub>AH</sub>      | Time from the active transition at the CLK input to the point where data is last held at the F or G input                               | 0.00            | -    | ns    |

| T <sub>CKDI</sub>    | Time from the active transition at the CLK input to the point where data is last held at the BX or BY input                             | 0.00            | -    | ns    |

| Clock Timing         |                                                                                                                                         |                 |      | I     |

| Т <sub>СН</sub>      | The High pulse width of the CLB's CLK signal                                                                                            | 0.75            | -    | ns    |

| T <sub>CL</sub>      | The Low pulse width of the CLK signal                                                                                                   | 0.75            | -    | ns    |

| F <sub>TOG</sub>     | Toggle frequency (for export control)                                                                                                   | 0               | 667  | MHz   |

| Propagation Time     | es                                                                                                                                      |                 |      |       |

| T <sub>ILO</sub>     | The time it takes for data to travel from the CLB's F (G) input to the X (Y) output                                                     | -               | 0.71 | ns    |

| Set/Reset Pulse      | Width                                                                                                                                   |                 |      | 1     |

| T <sub>RPW_CLB</sub> | The minimum allowable pulse width, High or Low, to the CLB's SR input                                                                   | 1.61            | -    | ns    |

### Notes:

1. The numbers in this table are based on the operating conditions set forth in Table 8.

| Cumbal                              | Deservition                                                                                                                       |       | Grade: -4 | Unito |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------|-----------|-------|

| Symbol                              | Description                                                                                                                       | Min   | Max       | Units |

| Clock-to-Output Tir                 | nes                                                                                                                               |       |           |       |

| Т <sub>SHCKO</sub>                  | Time from the active edge at the CLK input to data appearing on the distributed RAM output                                        | _     | 1.72      | ns    |

| Setup Times                         |                                                                                                                                   |       |           |       |

| T <sub>DS</sub>                     | Setup time of data at the BX or BY input before the active transition at the CLK input of the distributed RAM                     | -0.02 | -         | ns    |

| T <sub>AS</sub>                     | Setup time of the F/G address inputs before the active transition at the CLK input of the distributed RAM                         | 0.36  | -         | ns    |

| T <sub>WS</sub>                     | Setup time of the write enable input before the active transition at the CLK input of the distributed RAM                         | 0.59  | -         | ns    |

| Hold Times                          |                                                                                                                                   |       |           | L     |

| T <sub>DH</sub>                     | Hold time of the BX and BY data inputs after the active transition at the CLK input of the distributed RAM                        | 0.13  | -         | ns    |

| T <sub>AH,</sub> T <sub>WH</sub>    | Hold time of the F/G address inputs or the write enable input after the active transition at the CLK input of the distributed RAM | 0.01  | -         | ns    |

| Clock Pulse Width                   |                                                                                                                                   | 1     | 1         | 1     |

| T <sub>WPH</sub> , T <sub>WPL</sub> | Minimum High or Low pulse width at CLK input                                                                                      | 1.01  | _         | ns    |

### Table 32: CLB Shift Register Switching Characteristics

| Symbol                              | Description                                                                                                  |      | Speed Grade: -4 |       |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------|------|-----------------|-------|

| Symbol                              | Description                                                                                                  | Min  | Max             | Units |

| Clock-to-Output Tir                 | nes                                                                                                          |      |                 |       |

| T <sub>REG</sub>                    | Time from the active edge at the CLK input to data appearing on the shift register output                    | -    | 4.82            | ns    |

| Setup Times                         |                                                                                                              |      |                 |       |

| T <sub>SRLDS</sub>                  | Setup time of data at the BX or BY input before the active transition at the CLK input of the shift register | 0.18 | -               | ns    |

| Hold Times                          |                                                                                                              |      |                 |       |

| T <sub>SRLDH</sub>                  | Hold time of the BX or BY data input after the active transition at the CLK input of the shift register      | 0.16 | -               | ns    |

| Clock Pulse Width                   |                                                                                                              |      | ł               | L     |

| T <sub>WPH</sub> , T <sub>WPL</sub> | Minimum High or Low pulse width at CLK input                                                                 | 1.01 | -               | ns    |

# **Clock Buffer/Multiplexer Switching Characteristics**

### Table 33: Clock Distribution Switching Characteristics

| Description                                                                                                    | Symbol            | Minimum | Maximum | Units |

|----------------------------------------------------------------------------------------------------------------|-------------------|---------|---------|-------|

| Global clock buffer (BUFG, BUFGMUX, BUFGCE) I input to O-output delay                                          | T <sub>GIO</sub>  | -       | 0.23    | ns    |

| Global clock multiplexer (BUFGMUX) select S-input setup to I0 and I1 inputs.<br>Same as BUFGCE enable CE-input | T <sub>GSI</sub>  | _       | 0.63    | ns    |

| Frequency of signals distributed on global buffers (all sides)                                                 | F <sub>BUFG</sub> | 0       | 334     | MHz   |

### Notes:

1. The numbers in this table are based on the operating conditions set forth in Table 8.

# **Block RAM Timing**

### Table 34: Block RAM Timing

| Querra ha a l            | Description                                                                                                             |      | Speed Grade: -4 |       |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------|------|-----------------|-------|

| Symbol                   | Description                                                                                                             | Min  | Max             | Units |

| Clock-to-Output 1        | Times                                                                                                                   |      |                 |       |

| T <sub>RCKO_DOA_NC</sub> | When reading from block RAM, the delay from the active transition at the CLK input to data appearing at the DOUT output | -    | 2.80            | ns    |

| T <sub>RCKO_DOA</sub>    | Clock CLK to DOUT output (with output register)                                                                         | _    | 1.45            | ns    |

| Setup Times              |                                                                                                                         |      |                 |       |

| T <sub>RCCK_ADDR</sub>   | Setup time for the ADDR inputs before the active transition at the CLK input of the block RAM                           | 0.46 | _               | ns    |

| T <sub>RDCK_DIB</sub>    | Setup time for data at the DIN inputs before the active transition at the CLK input of the block RAM                    | 0.33 | -               | ns    |

| T <sub>RCCK_ENB</sub>    | Setup time for the EN input before the active transition at the CLK input of the block RAM                              | 0.60 | _               | ns    |

| T <sub>RCCK_WEB</sub>    | Setup time for the WE input before the active transition at the CLK input of the block RAM                              | 0.75 | -               | ns    |

| T <sub>RCCK_REGCE</sub>  | Setup time for the CE input before the active transition at the CLK input of the block RAM                              | 0.40 | -               | ns    |

| T <sub>RCCK_RST</sub>    | Setup time for the RST input before the active transition at the CLK input of the block RAM                             | 0.25 | -               | ns    |

| Hold Times               |                                                                                                                         |      |                 | ,     |

| T <sub>RCKC_ADDR</sub>   | Hold time on the ADDR inputs after the active transition at the CLK input                                               | 0.10 | _               | ns    |

| T <sub>RDCK_DIB</sub>    | Hold time on the DIN inputs after the active transition at the CLK input                                                | 0.10 | -               | ns    |

| T <sub>RCKC_ENB</sub>    | Hold time on the EN input after the active transition at the CLK input                                                  | 0.10 | -               | ns    |

| T <sub>RCKC_WEB</sub>    | Hold time on the WE input after the active transition at the CLK input                                                  | 0.10 | _               | ns    |

| T <sub>RCKC_REGCE</sub>  | Hold time on the CE input after the active transition at the CLK input                                                  | 0.10 | -               | ns    |

| T <sub>RCKC_RST</sub>    | Hold time on the RST input after the active transition at the CLK input                                                 | 0.10 | -               | ns    |

| Clock Timing             |                                                                                                                         |      |                 |       |

| T <sub>BPWH</sub>        | High pulse width of the CLK signal                                                                                      | 1.79 | -               | ns    |

| T <sub>BPWL</sub>        | Low pulse width of the CLK signal                                                                                       | 1.79 | -               | ns    |

| Clock Frequency          | · · · · · · · · · · · · · · · · · · ·                                                                                   |      |                 |       |

| F <sub>BRAM</sub>        | Block RAM clock frequency                                                                                               | 0    | 280             | MHz   |

Notes:

1. The numbers in this table are based on the operating conditions set forth in Table 8.

### **Digital Frequency Synthesizer**

### Table 39: Recommended Operating Conditions for the DFS

|                    | Symbol                             | Description                               | Description Speed Grade:        |       | Speed Grade: -4 |       |

|--------------------|------------------------------------|-------------------------------------------|---------------------------------|-------|-----------------|-------|

|                    | Symbol                             | Min Ma                                    |                                 |       |                 | Units |

| Input Fre          | quency Ranges <sup>(2)</sup>       |                                           |                                 |       |                 | ·     |

| F <sub>CLKIN</sub> | CLKIN_FREQ_FX                      | Frequency for the CLKIN input             |                                 | 0.200 | 333             | MHz   |

| Input Clo          | ck Jitter Tolerance <sup>(3)</sup> | •                                         |                                 |       | <u>.</u>        |       |

| CLKIN_C            | YC_JITT_FX_LF                      | Cycle-to-cycle jitter at the CLKIN input, | $F_{CLKFX} \le 150 \text{ MHz}$ | -     | ±300            | ps    |

| CLKIN_C            | YC_JITT_FX_HF                      | based on CLKFX output frequency           | F <sub>CLKFX</sub> > 150 MHz    | -     | ±150            | ps    |

| CLKIN_PE           | ER_JITT_FX                         | Period jitter at the CLKIN input          |                                 | -     | ±1              | ns    |

### Notes:

- 1. DFS specifications apply when either of the DFS outputs (CLKFX or CLKFX180) is used.

- 2. If both DFS and DLL outputs are used on the same DCM, follow the more restrictive CLKIN\_FREQ\_DLL specifications in Table 37.

- 3. CLKIN input jitter beyond these limits may cause the DCM to lose lock.

- 4. The DCM specifications are guaranteed when both adjacent DCMs are locked.

### Table 40: Switching Characteristics for the DFS

| Symbol                               | Description                                                                                                         |                | Device | Speed Grade: -4                                                                                                          |                                      | Units |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------|--------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------|

| Symbol                               |                                                                                                                     |                |        | Min                                                                                                                      | Max                                  | Units |

| Output Frequency Ranges              |                                                                                                                     |                |        |                                                                                                                          |                                      |       |

| CLKOUT_FREQ_FX <sup>(2)</sup>        | Frequency for the CLKFX and CLKFX180                                                                                | outputs        | All    | 5                                                                                                                        | 311                                  | MHz   |

| Output Clock Jitter <sup>(3,4)</sup> |                                                                                                                     |                |        |                                                                                                                          |                                      |       |

| CLKOUT_PER_JITT_FX                   | Period jitter at the CLKFX and CLKFX180                                                                             |                |        | Тур                                                                                                                      | Max                                  |       |

|                                      | outputs.                                                                                                            | CLKIN ≤ 20 MHz | All    | Use the Spartan-3A<br>Jitter Calculator:<br>www.xilinx.com/support/<br>documentation/data_she<br>ets/s3a_jitter_calc.zip |                                      | ps    |

|                                      |                                                                                                                     | CLKIN > 20 MHz |        | ±[1% of<br>CLKFX<br>period<br>+ 100]                                                                                     | ±[1% of<br>CLKFX<br>period<br>+ 200] | ps    |

| Duty Cycle <sup>(5,6)</sup>          |                                                                                                                     | •              |        |                                                                                                                          |                                      |       |

| CLKOUT_DUTY_CYCLE_FX                 | Duty cycle precision for the CLKFX and CLKFX180 outputs, including the BUFGMUX and clock tree duty-cycle distortion |                | All    | -                                                                                                                        | ±[1% of<br>CLKFX period<br>+ 350]    | ps    |

| Phase Alignment <sup>(6)</sup>       |                                                                                                                     |                |        |                                                                                                                          |                                      |       |

| CLKOUT_PHASE_FX                      | Phase offset between the DFS CLKFX ou<br>CLK0 output when both the DFS and DLI                                      |                | All    | -                                                                                                                        | ±200                                 | ps    |

| CLKOUT_PHASE_FX180                   | Phase offset between the DFS CLKFX180 output and the DLL CLK0 output when both the DFS and DLL are used             |                | All    | -                                                                                                                        | ±[1% of<br>CLKFX period<br>+ 200]    | ps    |

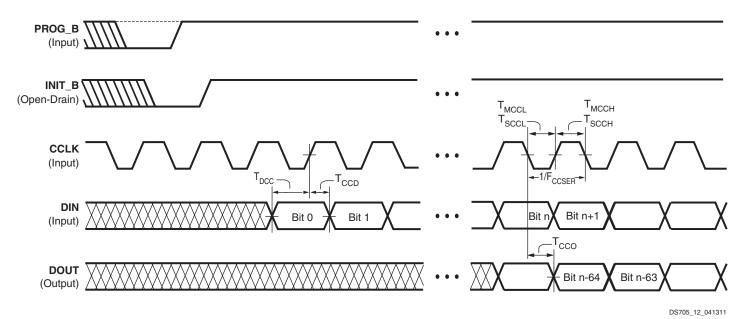

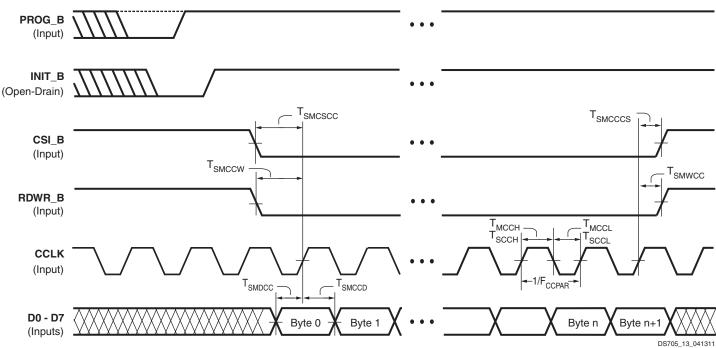

# **Slave Serial Mode Timing**

Figure 12: Waveforms for Slave Serial Configuration

### Table 51: Timing for the Slave Serial Configuration Modes

| Symbol             | Description                                                                                            |                            |              | Max | Units |

|--------------------|--------------------------------------------------------------------------------------------------------|----------------------------|--------------|-----|-------|

| Clock-to-O         | utput Times                                                                                            |                            |              |     |       |

| T <sub>CCO</sub>   | The time from the falling transition on the CCLK pin to data appearing at the DOUT pin                 |                            | 1.5          | 10  | ns    |

| Setup Time         | es                                                                                                     |                            |              | 1   |       |

| T <sub>DCC</sub>   | The time from the setup of data at the DIN pin to the rising transition at the CCLK pin                |                            |              | -   | ns    |

| Hold Time          | S                                                                                                      |                            |              |     |       |

| T <sub>CCD</sub>   | The time from the rising transition at the CCLK pin to the point when data is last held at the DIN pin |                            | 1.0          | -   | ns    |