Welcome to **E-XFL.COM**

**Understanding Embedded - DSP (Digital Signal Processors)**

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

Applications of <u>Embedded - DSP (Digital Signal Processors)</u>

| Details                 |                                                                     |

|-------------------------|---------------------------------------------------------------------|

| Product Status          | Obsolete                                                            |

| Туре                    | Fixed Point                                                         |

| Interface               | CAN, EBI/EMI, I <sup>2</sup> C, IrDA, PPI, SPI, SPORT, UART/USART   |

| Clock Rate              | 400MHz                                                              |

| Non-Volatile Memory     | External                                                            |

| On-Chip RAM             | 68kB                                                                |

| Voltage - I/O           | 1.8V, 2.5V, 3.3V                                                    |

| Voltage - Core          | 1.29V                                                               |

| Operating Temperature   | -40°C ~ 105°C (TA)                                                  |

| Mounting Type           | Surface Mount                                                       |

| Package / Case          | 88-VFQFN Exposed Pad, CSP                                           |

| Supplier Device Package | 88-LFCSP-VQ (12x12)                                                 |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adbf504wycpz401 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **TABLE OF CONTENTS**

| Peatures                                                                 | Additional Information                                | 21    |

|--------------------------------------------------------------------------|-------------------------------------------------------|-------|

| Memory 1                                                                 | Related Signal Chains                                 | 21    |

| Peripherals                                                              | Signal Descriptions                                   | 22    |

| General Description                                                      | Specifications                                        | 26    |

| Portable Low-Power Architecture                                          | Operating Conditions                                  | 26    |

| System Integration                                                       | Electrical Characteristics                            | 28    |

| Processor Peripherals                                                    | Processor—Absolute Maximum Ratings                    | 31    |

| Blackfin Processor Core                                                  | ESD Sensitivity                                       | 32    |

| Memory Architecture                                                      | Package Information                                   | 32    |

| Flash Memory                                                             | Processor—Timing Specifications                       | 33    |

| DMA Controllers                                                          | Processor—Output Drive Currents                       | 50    |

| Watchdog Timer                                                           | Processor—Test Conditions                             | 51    |

| Timers                                                                   | Processor—Environmental Conditions                    | 53    |

| Up/Down Counters and Thumbwheel Interfaces 10                            | Flash—Specifications                                  | 54    |

| 3-Phase PWM Units                                                        | Flash—Program and Erase Times and Endurance           |       |

| Serial Ports                                                             | Cycles                                                | 54    |

| Serial Peripheral Interface (SPI) Ports                                  | Flash—Absolute Maximum Ratings                        | 54    |

| UART Ports (UARTs)                                                       | ADC—Specifications                                    |       |

| Parallel Peripheral Interface (PPI) 11                                   | ADC—Operating Conditions                              | 55    |

| RSI Interface                                                            | ADC—Timing Specifications                             | 58    |

| Controller Area Network (CAN) Interface                                  | ADC—Absolute Maximum Ratings                          | 58    |

| TWI Controller Interface                                                 | ADC—Typical Performance Characteristics               | 59    |

| Ports                                                                    | ADC—Terminology                                       | 61    |

| Dynamic Power Management                                                 | ADC—Theory of Operation                               | 62    |

| ADSP-BF50x Voltage Regulation                                            | ADC—Modes of Operation                                | 68    |

| Clock Signals                                                            | ADC—Serial Interface                                  | 71    |

| Booting Modes                                                            | 120-Lead LQFP Lead Assignment                         | 73    |

| Instruction Set Description                                              | 88-Lead LFCSP Lead Assignment                         | 76    |

| Development Tools                                                        | Outline Dimensions                                    | 79    |

| ADC and ACM Interface                                                    | Automotive Products                                   | 81    |

| Internal ADC                                                             | Ordering Guide                                        | 81    |

| ADC Application Hints                                                    |                                                       |       |

| REVISION HISTORY                                                         |                                                       |       |

| 04/14—Rev. A to Rev. B                                                   | Revised package diagram (Figure 93) to include U-Groo | ve in |

| Jpdated Development Tools                                                | Outline Dimensions                                    |       |

| Corrected RCKFE bit setting and description in                           | Package thickness changed from 0.75/0.80/0.85 to      |       |

| Table 9, The SPORTx Receive Configuration 1 Register                     | 0.75/0.85/0.90 in Figure 94 in Outline Dimensions     | 79    |

| SPORTx_RCR1)                                                             |                                                       |       |

| Jpdated footnote 6 in Operating Conditions                               |                                                       |       |

| Updated Table 18 with revised data for static Current—IDD-DEEPSLEEP (mA) |                                                       |       |

Table 3. System Interrupt Controller (SIC)

| Peripheral Interrupt Source | General-Purpose<br>Interrupt (at Reset) | Peripheral<br>Interrupt ID | Default Core<br>Interrupt ID |      | SIC Registers      |

|-----------------------------|-----------------------------------------|----------------------------|------------------------------|------|--------------------|

| PLL Wakeup Interrupt        | IVG7                                    | 0                          | 0                            | IAR0 | IMASKO, ISRO, IWRO |

| DMA Error (generic)         | IVG7                                    | 1                          | 0                            | IAR0 | IMASKO, ISRO, IWRO |

| PPI Status                  | IVG7                                    | 2                          | 0                            | IAR0 | IMASKO, ISRO, IWRO |

| SPORT0 Status               | IVG7                                    | 3                          | 0                            | IAR0 | IMASKO, ISRO, IWRO |

| SPORT1 Status               | IVG7                                    | 4                          | 0                            | IAR0 | IMASKO, ISRO, IWRO |

| UARTO Status                | IVG7                                    | 5                          | 0                            | IAR0 | IMASKO, ISRO, IWRO |

| UART1 Status                | IVG7                                    | 6                          | 0                            | IAR0 | IMASKO, ISRO, IWRO |

| SPI0 Status                 | IVG7                                    | 7                          | 0                            | IAR0 | IMASKO, ISRO, IWRO |

| SPI1 Status                 | IVG7                                    | 8                          | 0                            | IAR1 | IMASKO, ISRO, IWRO |

| CAN Status                  | IVG7                                    | 9                          | 0                            | IAR1 | IMASKO, ISRO, IWRO |

| RSI Mask 0 Interrupt        | IVG7                                    | 10                         | 0                            | IAR1 | IMASKO, ISRO, IWRO |

| Reserved                    | _                                       | 11                         | _                            | IAR1 | IMASKO, ISRO, IWRO |

| CNT0 Interrupt              | IVG8                                    | 12                         | 1                            | IAR1 | IMASKO, ISRO, IWRO |

| CNT1 Interrupt              | IVG8                                    | 13                         | 1                            | IAR1 | IMASKO, ISRO, IWRO |

| DMA Channel 0 (PPI Rx/Tx)   | IVG9                                    | 14                         | 2                            | IAR1 | IMASKO, ISRO, IWRO |

| DMA Channel 1 (RSI Rx/Tx)   | IVG9                                    | 15                         | 2                            | IAR1 | IMASKO, ISRO, IWRO |

| DMA Channel 2 (SPORT0 Rx)   | IVG9                                    | 16                         | 2                            | IAR2 | IMASKO, ISRO, IWRO |

| DMA Channel 3 (SPORT0 Tx)   | IVG9                                    | 17                         | 2                            | IAR2 | IMASKO, ISRO, IWRO |

| DMA Channel 4 (SPORT1 Rx)   | IVG9                                    | 18                         | 2                            | IAR2 | IMASKO, ISRO, IWRO |

| DMA Channel 5 (SPORT1 Tx)   | IVG9                                    | 19                         | 2                            | IAR2 | IMASKO, ISRO, IWRO |

| DMA Channel 6 (SPI0 Rx/Tx)  | IVG10                                   | 20                         | 3                            | IAR2 | IMASKO, ISRO, IWRO |

| DMA Channel 7 (SPI1 Rx/Tx)  | IVG10                                   | 21                         | 3                            | IAR2 | IMASKO, ISRO, IWRO |

| DMA Channel 8 (UARTO Rx)    | IVG10                                   | 22                         | 3                            | IAR2 | IMASKO, ISRO, IWRO |

| DMA Channel 9 (UART0 Tx)    | IVG10                                   | 23                         | 3                            | IAR2 | IMASKO, ISRO, IWRO |

| DMA Channel 10 (UART1 Rx)   | IVG10                                   | 24                         | 3                            | IAR3 | IMASKO, ISRO, IWRO |

| DMA Channel 11 (UART1 Tx)   | IVG10                                   | 25                         | 3                            | IAR3 | IMASKO, ISRO, IWRO |

| CAN Receive                 | IVG11                                   | 26                         | 4                            | IAR3 | IMASKO, ISRO, IWRO |

| CAN Transmit                | IVG11                                   | 27                         | 4                            | IAR3 | IMASKO, ISRO, IWRO |

| TWI                         | IVG11                                   | 28                         | 4                            | IAR3 | IMASKO, ISRO, IWRO |

| Port F Interrupt A          | IVG11                                   | 29                         | 4                            | IAR3 | IMASKO, ISRO, IWRO |

| Port F Interrupt B          | IVG11                                   | 30                         | 4                            | IAR3 | IMASKO, ISRO, IWRO |

| Reserved                    | _                                       | 31                         | _                            | IAR3 | IMASKO, ISRO, IWRO |

| Timer 0                     | IVG12                                   | 32                         | 5                            | IAR4 | IMASK1, ISR1, IWR1 |

| Timer 1                     | IVG12                                   | 33                         | 5                            | IAR4 | IMASK1, ISR1, IWR1 |

| Timer 2                     | IVG12                                   | 34                         | 5                            | IAR4 | IMASK1, ISR1, IWR1 |

| Timer 3                     | IVG12                                   | 35                         | 5                            | IAR4 | IMASK1, ISR1, IWR1 |

| Timer 4                     | IVG12                                   | 36                         | 5                            | IAR4 | IMASK1, ISR1, IWR1 |

| Timer 5                     | IVG12                                   | 37                         | 5                            | IAR4 | IMASK1, ISR1, IWR1 |

| Timer 6                     | IVG12                                   | 38                         | 5                            | IAR4 | IMASK1, ISR1, IWR1 |

| Timer 7                     | IVG12                                   | 39                         | 5                            | IAR4 | IMASK1, ISR1, IWR1 |

| Port G Interrupt A          | IVG12                                   | 40                         | 5                            | IAR5 | IMASK1, ISR1, IWR1 |

| Port G Interrupt B          | IVG12                                   | 41                         | 5                            | IAR5 | IMASK1, ISR1, IWR1 |

| MDMA Stream 0               | IVG13                                   | 42                         | 6                            | IAR5 | IMASK1, ISR1, IWR1 |

The timers can generate interrupts to the processor core providing periodic events for synchronization, either to the system clock or to a count of external signals.

In addition to the eight general-purpose programmable timers, a ninth timer is also provided. This extra timer is clocked by the internal processor clock and is typically used as a system tick clock for generation of operating system periodic interrupts.

# UP/DOWN COUNTERS AND THUMBWHEEL INTERFACES

Two 32-bit up/down counters are provided that can sense 2-bit quadrature or binary codes as typically emitted by industrial drives or manual thumbwheels. The counters can also operate in general-purpose up/down count modes. Then, count direction is either controlled by a level-sensitive input pin or by two edge detectors.

A third counter input can provide flexible zero marker support and can alternatively be used to input the push-button signal of thumb wheels. All three pins have a programmable debouncing circuit.

Internal signals forwarded to each timer unit enable these timers to measure the intervals between count events. Boundary registers enable auto-zero operation or simple system warning by interrupts when programmable count values are exceeded.

#### **3-PHASE PWM UNITS**

The two/dual 3-phase PWM generation units each feature:

- · 16-bit center-based PWM generation unit

- Programmable PWM pulse width

- Single/double update modes

- Programmable dead time and switching frequency

- Twos-complement implementation which permits smooth transition to full ON and full OFF states

- Possibility to synchronize the PWM generation to either externally-generated or internally-generated synchronization pulses

- Special provisions for BDCM operation (crossover and output enable functions)

- Wide variety of special switched reluctance (SR) operating modes

- Output polarity and clock gating control

- Dedicated asynchronous PWM shutdown signal

Each PWM block integrates a flexible and programmable 3-phase PWM waveform generator that can be programmed to generate the required switching patterns to drive a 3-phase voltage source inverter for ac induction motor (ACIM) or permanent magnet synchronous motor (PMSM) control. In addition, the PWM block contains special functions that considerably simplify the generation of the required PWM switching patterns for control of the electronically commutated motor (ECM) or brushless dc motor (BDCM). Software can enable a special mode for switched reluctance motors (SRM).

The six PWM output signals (per PWM unit) consist of three high-side drive signals (PWMx\_AH, PWMx\_BH, and PWMx\_CH) and three low-side drive signals (PWMx\_AL, PWMx\_BL, and PWMx\_CL). The polarity of the generated PWM signal can be set with software, so that either active HI or active LO PWM patterns can be produced.

The switching frequency of the generated PWM pattern is programmable using the 16-bit PWM\_TM register. The PWM generator can operate in single update mode or double update mode. In single update mode, the duty cycle values are programmable only once per PWM period, so that the resultant PWM patterns are symmetrical about the midpoint of the PWM period. In the double update mode, a second updating of the PWM registers is implemented at the midpoint of the PWM period. In this mode, it is possible to produce asymmetrical PWM patterns that produce lower harmonic distortion in 3-phase PWM inverters.

Pulses synchronous to the switching frequency can be generated internally and output on the PWMx\_SYNC pin. The PWM unit can also accept externally generated synchronization pulses through PWMx\_SYNC.

Each PWM unit features a dedicated asynchronous shutdown pin, PWMx\_TRIP, which (when brought low) instantaneously places all six PWM outputs in the OFF state.

#### **SERIAL PORTS**

The processors incorporate two dual-channel synchronous serial ports (SPORT0 and SPORT1) for serial and multiprocessor communications. The SPORTs support the following features:

- I<sup>2</sup>S capable operation.

- Bidirectional operation—Each SPORT has two sets of independent transmit and receive pins, enabling eight channels of I<sup>2</sup>S stereo audio.

- Buffered (8-deep) transmit and receive ports—Each port has a data register for transferring data words to and from other processor components and shift registers for shifting data in and out of the data registers.

- Clocking—Each transmit and receive port can either use an external serial clock or generate its own, in frequencies ranging from (f<sub>SCLK</sub>/131,070) Hz to (f<sub>SCLK</sub>/2) Hz.

- Word length—Each SPORT supports serial data words from 3 to 32 bits in length, transferred most significant bit first or least significant bit first.

- Framing—Each transmit and receive port can run with or without frame sync signals for each data word. Frame sync signals can be generated internally or externally, active high or low, and with either of two pulse widths and early or late frame sync.

- Companding in hardware—Each SPORT can perform

A-law or μ-law companding according to ITU recommendation G.711. Companding can be selected on the transmit and/or receive channel of the SPORT without additional latencies.

where the variables in the equations are:

$f_{CCLKNOM}$  is the nominal core clock frequency

$f_{CCLKRED}$  is the reduced core clock frequency

$V_{DDINTNOM}$  is the nominal internal supply voltage

$V_{DDINTRED}$  is the reduced internal supply voltage

$T_{NOM}$  is the duration running at  $f_{CCLKNOM}$

$T_{RED}$  is the duration running at  $f_{CCLKRED}$

#### ADSP-BF50x VOLTAGE REGULATION

The ADSP-BF50x processors require an external voltage regulator to power the  $V_{\rm DDINT}$  domain. To reduce standby power consumption, the external voltage regulator can be signaled through EXT\_WAKE to remove power from the processor core. This signal is high-true for power-up and may be connected directly to the low-true shut-down input of many common regulators.

While in the hibernate state, all external supplies ( $V_{\rm DDEXT}$ ,  $V_{\rm DDFLASH}$ ) can still be applied, eliminating the need for external buffers. The external voltage regulator can be activated from this power down state by asserting the  $\overline{\rm RESET}$  pin, which then initiates a boot sequence. EXT\_WAKE indicates a wakeup to the external voltage regulator.

The power good  $(\overline{PG})$  input signal allows the processor to start only after the internal voltage has reached a chosen level. In this way, the startup time of the external regulator is detected after hibernation. For a complete description of the power good functionality, refer to the ADSP-BF50x Blackfin Processor Hardware Reference.

#### **CLOCK SIGNALS**

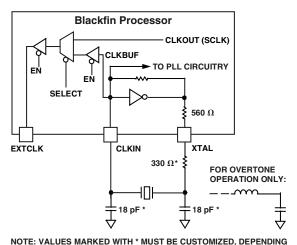

The processor can be clocked by an external crystal, a sine wave input, or a buffered, shaped clock derived from an external clock oscillator.

If an external clock is used, it should be a TTL-compatible signal and must not be halted, changed, or operated below the specified frequency during normal operation. This signal is connected to the processor's CLKIN pin. When an external clock is used, the XTAL pin must be left unconnected.

Alternatively, because the processor includes an on-chip oscillator circuit, an external crystal may be used. For fundamental frequency operation, use the circuit shown in Figure 4. A parallel-resonant, fundamental frequency, microprocessor-grade crystal is connected across the CLKIN and XTAL pins. The on-chip resistance between CLKIN and the XTAL pin is in the 500 k $\Omega$  range. Further parallel resistors are typically not recommended. The two capacitors and the series resistor shown in Figure 4 fine tune phase and amplitude of the sine frequency.

The capacitor and resistor values shown in Figure 4 are typical values only. The capacitor values are dependent upon the crystal manufacturers' load capacitance recommendations and the PCB physical layout. The resistor value depends on the drive level specified by the crystal manufacturer. The user should verify the customized values based on careful investigations on multiple devices over temperature range.

A third-overtone crystal can be used for frequencies above 25 MHz. The circuit is then modified to ensure crystal operation only at the third overtone by adding a tuned inductor circuit as shown in Figure 4. A design procedure for third-overtone operation is discussed in detail in (EE-168) Using Third Overtone Crystals with the ADSP-218x DSP on the Analog Devices website (www.analog.com)—use site search on "EE-168."

The Blackfin core runs at a different clock rate than the on-chip peripherals. As shown in Figure 5, the core clock (CCLK) and system peripheral clock (SCLK) are derived from the input clock (CLKIN) signal. An on-chip PLL is capable of multiplying the CLKIN signal by a programmable multiplication factor (bounded by specified minimum and maximum VCO frequencies). The default multiplier is 6×, but it can be modified by a software instruction sequence.

NOTE: VALUES MARKED WITH \* MUST BE CUSTOMIZED, DEPENDING ON THE CRYSTAL AND LAYOUT. PLEASE ANALYZE CAREFULLY. FOR FREQUENCIES ABOVE 33 MHz, THE SUGGESTED CAPACITOR VALUE OF 18 pF SHOULD BE TREATED AS A MAXIMUM, AND THE SUGGESTED RESISTOR VALUE SHOULD BE REDUCED TO 0  $\Omega$ .

Figure 4. External Crystal Connections

On-the-fly frequency changes can be effected by simply writing to the PLL\_DIV register. The maximum allowed CCLK and SCLK rates depend on the applied voltages  $V_{\rm DDINT}$  and  $V_{\rm DDEXT}$ ; the VCO is always permitted to run up to the CCLK frequency specified by the part's speed grade. The EXTCLK pin can be configured to output either the SCLK frequency or the input buffered CLKIN frequency, called CLKBUF. When configured to output SCLK (CLKOUT), the EXTCLK pin acts as a reference signal in many timing specifications. While active by default, it can be disabled using the EBIU\_AMGCTL register.

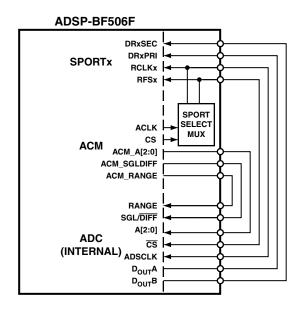

The ACM synchronizes the ADC conversion process; generating the ADC controls, the ADC conversion start signal, and other signals. The actual data acquisition from the ADC is done by the SPORT peripherals.

The serial interface on the ADC allows the part to be directly connected to the ADSP-BF504, ADSP-BF504F, and ADSP-BF506F processors using serial interface protocols.

Figure 6 shows how to connect an external ADC to the ACM and one of the two SPORTs on the ADSP-BF504 or ADSP-BF504F processors.

#### ADSP-BF504/ADSP-BF504F DRxSEC DRxPRI **SPORTX** RCLKx -RFSx SPORT SELECT ACLK MUX CS ACM\_A[2:0] ACM SGLDIFF ACM\_RANGE RANGE SGL/DIFF A[2:0] **ADC** $\overline{\mathsf{cs}}$ (EXTERNAL) **ADSCLK** $\mathbf{D}_{\mathbf{OUT}}\mathbf{A}$ $D_{OUT}B$

Figure 6. ADC (External), ACM, and SPORT Connections

The ADC is integrated into the ADSP-BF506F product. Figure 7 shows how to connect the internal ADC to the ACM and to one of the two SPORTs on the ADSP-BF506F processor.

Figure 7. ADC (Internal), ACM, and SPORT Connections

The ADSP-BF504, ADSP-BF504F, and ADSP-BF506F processors interface directly to the ADC without any glue logic required. The availability of secondary receive registers on the serial ports of the Blackfin processors means only one serial port is necessary to read from both  $D_{\rm OUT}$  pins simultaneously. Figure 7 (ADC (Internal), ACM, and SPORT Connections) shows both  $D_{\rm OUT}A$  and  $D_{\rm OUT}B$  of the ADC connected to one of the processor's serial ports. The SPORTx Receive Configuration 1 register and SPORTx Receive Configuration 2 register should be set up as outlined in Table 9 (The SPORTx Receive Configuration 1 Register (SPORTx\_RCR1)) and Table 10 (The SPORTx Receive Configuration 2 Register (SPORTx\_RCR2)).

Table 9. The SPORTx Receive Configuration 1 Register (SPORTx\_RCR1)

| Setting         | Description                            |

|-----------------|----------------------------------------|

| RCKFE = 0       | Sample data with falling edge of RSCLK |

| LRFS = 1        | Active low frame signal                |

| RFSR = 1        | Frame every word                       |

| IRFS = 0        | External RFS used                      |

| RLSBIT = 0      | Receive MSB first                      |

| RDTYPE = 00     | Zero fill                              |

| IRCLK = 0       | External receive clock                 |

| RSPEN = 1       | Receive enabled                        |

| TFSR = RFSR = 1 |                                        |

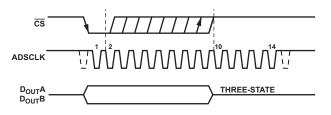

Table 12. ADC—Signal Descriptions (ADSP-BF506F Processor Only) (Continued)

| Signal Name                            | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D <sub>OUT</sub> A, D <sub>OUT</sub> B | 0    | Serial Data Outputs. The data output is supplied to each pin as a serial data stream. The bits are clocked out on the falling edge of the ADSCLK input and 14 ADSCLKs are required to access the data. The data simultaneously appears on both pins from the simultaneous conversions of both ADCs. The data stream consists of two leading zeros followed by the 12 bits of conversion data. The data is provided MSB first. If $\overline{CS}$ is held low for 16 ADSCLK cycles rather than 14, then two trailing zeros will appear after the 12 bits of data. If $\overline{CS}$ is held low for a further 16 ADSCLK cycles on either $D_{OUT}A$ or $D_{OUT}B$ , the data from the other ADC follows on the $D_{OUT}$ pin. This allows data from a simultaneous conversion on both ADCs to be gathered in serial format on either $D_{OUT}A$ or $D_{OUT}B$ using only one serial port. For more information, see the ADC—Serial Interface section. |

| V <sub>DRIVE</sub>                     | Р    | Logic Power Supply Input. The voltage supplied at this pin determines at what voltage the digital I/O interface operates. This pin should be decoupled to DGND. The voltage at this pin may be different than that at $AV_{DD}$ and $DV_{DD}$ but should never exceed either by more than 0.3 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| $DV_DD$                                | Р    | Digital Supply Voltage, 2.7 V to 5.25 V. This is the supply voltage for all digital circuitry on the internal ADC. The DV <sub>DD</sub> and AV <sub>DD</sub> voltages should ideally be at the same potential and must not be more than 0.3 V apart even on a transient basis. This supply should be decoupled to DGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

### ADSP-BF50x Clock Related Operating Conditions

Table 14 describes the core clock timing requirements for the ADSP-BF50x processors. Take care in selecting MSEL, SSEL, and CSEL ratios so as not to exceed the maximum core clock and system clock (see Table 16). Table 15 describes phase-locked loop operating conditions.

Table 14. Core Clock (CCLK) Requirements—ADSP-BF50x Processors—All Speed Grades

|            |                                                     |                        |                        | Max CCLK  |      |

|------------|-----------------------------------------------------|------------------------|------------------------|-----------|------|

| Paramete   | •                                                   | Min V <sub>DDINT</sub> | Nom V <sub>DDINT</sub> | Frequency | Unit |

| $f_{CCLK}$ | Core Clock Frequency (All Models)                   | 1.33 V                 | 1.400 V                | 400       | MHz  |

|            | Core Clock Frequency (Industrial/Commercial Models) | 1.16 V                 | 1.225 V                | 300       | MHz  |

|            | Core Clock Frequency (Industrial Models Only)       | 1.14 V                 | 1.200 V                | 200       | MHz  |

|            | Core Clock Frequency (Commercial Models Only)       | 1.10 V                 | 1.150 V                | 200       | MHz  |

Table 15. Phase-Locked Loop Operating Conditions

| Parameter        |                                                                                 | Min | Max                           | Unit |

|------------------|---------------------------------------------------------------------------------|-----|-------------------------------|------|

| f <sub>VCO</sub> | Voltage Controlled Oscillator (VCO) Frequency<br>(Commercial/Industrial Models) | 72  | Instruction Rate <sup>1</sup> | MHz  |

|                  | Voltage Controlled Oscillator (VCO) Frequency<br>(Automotive Models)            | 84  | Instruction Rate <sup>1</sup> | MHz  |

<sup>&</sup>lt;sup>1</sup> For more information, see Ordering Guide on Page 81.

Table 16. Maximum SCLK Conditions for ADSP-BF50x Processors

| Parameter         |                                                     | V <sub>DDEXT</sub> = 1.8 V/2.5 V/3.3 V Nominal | Unit |

|-------------------|-----------------------------------------------------|------------------------------------------------|------|

| $f_{\text{SCLK}}$ | CLKOUT/SCLK Frequency (V <sub>DDINT</sub> ≥ 1.16 V) | 100                                            | MHz  |

|                   | CLKOUT/SCLK Frequency (V <sub>DDINT</sub> < 1.16 V) | 80                                             | MHz  |

### **ELECTRICAL CHARACTERISTICS**

| Parameter                             |                                                                                 | Test Conditions                                                                                                                               | Min  | Typical | Max                                                                         | Unit             |

|---------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------|---------|-----------------------------------------------------------------------------|------------------|

| V <sub>OH</sub>                       | High Level Output Voltage                                                       | $V_{DDEXT} = 1.7 \text{ V, } I_{OH} = -0.5 \text{ mA}$                                                                                        | 1.35 |         |                                                                             | ٧                |

|                                       | High Level Output Voltage                                                       | $V_{DDEXT} = 2.25 \text{ V, } I_{OH} = -0.5 \text{ mA}$                                                                                       | 2.0  |         |                                                                             | V                |

|                                       | High Level Output Voltage                                                       | $V_{DDEXT} = 3.0 \text{ V, } I_{OH} = -0.5 \text{ mA}$                                                                                        | 2.4  |         |                                                                             | V                |

| $V_{OL}$                              | Low Level Output Voltage                                                        | $V_{DDEXT} = 1.7 \text{ V/2.25 V/3.0 V},$<br>$I_{OL} = 2.0 \text{ mA}$                                                                        |      |         | 0.4                                                                         | V                |

| I <sub>IH</sub>                       | High Level Input Current <sup>1</sup>                                           | $V_{DDEXT} = 3.6 \text{ V}, V_{IN} = 3.6 \text{ V}$                                                                                           |      |         | 10.0                                                                        | μΑ               |

| I <sub>IL</sub>                       | Low Level Input Current <sup>1</sup>                                            | $V_{DDEXT} = 3.6 \text{ V}, V_{IN} = 0 \text{ V}$                                                                                             |      |         | 10.0                                                                        | μΑ               |

| $I_{IHP}$                             | High Level Input Current JTAG <sup>2</sup>                                      | $V_{DDEXT} = 3.6 \text{ V}, V_{IN} = 3.6 \text{ V}$                                                                                           |      |         | 75.0                                                                        | μΑ               |

| I <sub>OZH</sub>                      | Three-State Leakage Current <sup>3</sup>                                        | $V_{DDEXT} = 3.6 \text{ V}, V_{IN} = 3.6 \text{ V}$                                                                                           |      |         | 10.0                                                                        | μΑ               |

| I <sub>OZHTWI</sub>                   | Three-State Leakage Current <sup>4</sup>                                        | $V_{DDEXT} = 3.0 \text{ V}, V_{IN} = 5.5 \text{ V}$                                                                                           |      |         | 10.0                                                                        | μΑ               |

| I <sub>OZL</sub>                      | Three-State Leakage Current <sup>3</sup>                                        | $V_{DDEXT} = 3.6 \text{ V}, V_{IN} = 0 \text{ V}$                                                                                             |      |         | 10.0                                                                        | μΑ               |

| $C_IN$                                | Input Capacitance <sup>5,6</sup>                                                | $ \begin{aligned} f_{\text{IN}} &= 1 \text{ MHz, } T_{\text{AMBIENT}} = 25^{\circ}\text{C,} \\ V_{\text{IN}} &= 2.5 \text{ V} \end{aligned} $ |      | 5       | 8                                                                           | pF               |

| $C_{\text{INTWI}}$                    | Input Capacitance <sup>4,6</sup>                                                | $f_{IN} = 1 \text{ MHz}, T_{AMBIENT} = 25^{\circ}\text{C},$ $V_{IN} = 2.5 \text{ V}$                                                          |      |         | 10                                                                          | pF               |

| I <sub>DDDEEPSLEEP</sub> <sup>7</sup> | V <sub>DDINT</sub> Current in Deep Sleep Mode                                   | $V_{DDINT} = 1.2 \text{ V}, f_{CCLK} = 0 \text{ MHz}, \\ f_{SCLK} = 0 \text{ MHz}, T_{J} = 25^{\circ}\text{C}, \\ ASF = 0.00$                 |      | 1.85    |                                                                             | mA               |

| I <sub>DDSLEEP</sub>                  | V <sub>DDINT</sub> Current in Sleep Mode                                        | $V_{DDINT} = 1.2 \text{ V, } f_{SCLK} = 25 \text{ MHz,} $<br>$T_{J} = 25^{\circ}\text{C}$                                                     |      | 2.1     |                                                                             | mA               |

| I <sub>DD-IDLE</sub>                  | V <sub>DDINT</sub> Current in Idle                                              | $V_{DDINT} = 1.2 \text{ V, } f_{CCLK} = 50 \text{ MHz,}$<br>$T_J = 25^{\circ}\text{C, ASF} = 0.42$                                            |      | 18      |                                                                             | mA               |

| I <sub>DD-TYP</sub>                   | V <sub>DDINT</sub> Current                                                      | $V_{DDINT} = 1.40 \text{ V}, f_{CCLK} = 400 \text{ MHz}, $<br>$T_{J} = 25 ^{\circ}\text{C}, \text{ ASF} = 1.00$                               |      | 104     |                                                                             | mA               |

|                                       | V <sub>DDINT</sub> Current                                                      | $V_{DDINT} = 1.225 \text{ V}, f_{CCLK} = 300 \text{ MHz}, $<br>$T_J = 25^{\circ}\text{C}, \text{ ASF} = 1.00$                                 |      | 69      |                                                                             | mA               |

|                                       | V <sub>DDINT</sub> Current                                                      | $V_{DDINT} = 1.2 \text{ V, } f_{CCLK} = 200 \text{ MHz,}$<br>$T_J = 25 ^{\circ}\text{C, ASF} = 1.00$                                          |      | 51      |                                                                             | mA               |

| I <sub>DDHIBERNATE</sub> <sup>8</sup> | Hibernate State Current                                                         | $\begin{split} &V_{DDEXT}\!=3.30 \text{ V,} \\ &V_{DDFLASH}\!=\!1.8 \text{ V,}        $                                                       |      | 40      |                                                                             | μΑ               |

| I <sub>DDSLEEP</sub> <sup>9</sup>     | V <sub>DDINIT</sub> Current in Sleep Mode                                       | $f_{CCLK} = 0 \text{ MHz}, f_{SCLK} > 0 \text{ MHz}$                                                                                          |      |         | Table 18 + $(.16 \times V_{DDINT} \times f_{SCLK})$                         | mA <sup>10</sup> |

| I <sub>DDDEEPSLEEP</sub> 9            | V <sub>DDINT</sub> Current in Deep Sleep Mode                                   | $f_{CCLK} = 0 \text{ MHz}, f_{SCLK} = 0 \text{ MHz}$                                                                                          |      |         | Table 18                                                                    | mA               |

| I <sub>DDINT</sub> <sup>9</sup>       | V <sub>DDINT</sub> Current                                                      | $f_{CCLK} > 0 \text{ MHz}, f_{SCLK} \ge 0 \text{ MHz}$                                                                                        |      |         | Table 18 + $(Table 19 \times ASF) + (.16 \times V_{DDINT} \times f_{SCLK})$ | mA               |

| I <sub>DDFLASH1</sub>                 | Flash Memory Supply Current 1 — Asynchronous Read (5 MHz NORCLK <sup>11</sup> ) |                                                                                                                                               |      | 10      | 20                                                                          | mA               |

|                                       | Flash Memory Supply Current 1                                                   | 4 Word                                                                                                                                        |      | 18      | 20                                                                          | mA               |

|                                       | — Synchronous Read (50 MHz                                                      | 8 Word                                                                                                                                        |      | 20      | 22                                                                          | mA               |

|                                       | NORCLK <sup>11</sup> )                                                          | 16 Word                                                                                                                                       |      | 25      | 27                                                                          | mA               |

|                                       |                                                                                 | Continuous                                                                                                                                    |      | 28      | 30                                                                          | mA               |

| Parameter             | r                                                                       | <b>Test Conditions</b>                                       | Min | Typical | Max | Unit |

|-----------------------|-------------------------------------------------------------------------|--------------------------------------------------------------|-----|---------|-----|------|

| I <sub>DDFLASH2</sub> | Flash Memory Supply Current 2 — Reset/Powerdown                         |                                                              |     | 15      | 50  | μΑ   |

| I <sub>DDFLASH3</sub> | Flash Memory Supply Current 3 — Standby                                 |                                                              |     | 15      | 50  | μΑ   |

| I <sub>DDFLASH4</sub> | Flash Memory Supply Current 4 — Automatic Standby                       |                                                              |     | 15      | 50  | μΑ   |

| I <sub>DDFLASH5</sub> | Flash Memory Supply Current 5<br>— Program                              |                                                              |     | 15      | 40  | mA   |

|                       | Flash Memory Supply Current 5<br>— Erase                                |                                                              |     | 15      | 40  | mA   |

| I <sub>DDFLASH6</sub> | Flash Memory Supply Current 6 — Dual Operations                         | Program/Erase in one bank, asynchronous read in another bank |     | 25      | 60  | mA   |

|                       |                                                                         | Program/Erase in one bank, synchronous read in another bank  |     | 43      | 70  | mA   |

| I <sub>DDFLASH7</sub> | Flash Memory Supply Current 7<br>— Program/Erase Suspended<br>(Standby) |                                                              |     | 15      | 50  | μΑ   |

<sup>&</sup>lt;sup>1</sup> Applies to input pins.

$<sup>^2</sup>$  Applies to JTAG input pins (TCK, TDI, TMS,  $\overline{\text{TRST}}\text{)}.$

<sup>&</sup>lt;sup>3</sup> Applies to three-statable pins.

<sup>&</sup>lt;sup>4</sup> Applies to bidirectional pins SCL and SDA.

<sup>&</sup>lt;sup>5</sup> Applies to all signal pins, except SCL and SDA.

<sup>&</sup>lt;sup>6</sup>Guaranteed, but not tested.

<sup>&</sup>lt;sup>7</sup> See the ADSP-BF50x Blackfin Processor Hardware Reference Manual for definition of sleep, deep sleep, and hibernate operating modes.

$<sup>^8</sup>$  Applies to  $V_{\mbox{\scriptsize DDEXT}}$  supply only. Clock inputs are tied high or low.

<sup>&</sup>lt;sup>9</sup>Guaranteed maximum specifications.

$<sup>^{10}</sup>$ Unit for  $V_{DDINT}$  is V (Volts). Unit for  $f_{SCLK}$  is MHz. Example: 1.4 V, 75 MHz would be  $0.16 \times 1.4 \times 75 = 16.8$  mA adder.

$<sup>^{11}\</sup>mbox{See}$  the ADSP-BF50x Blackfin Processor Hardware Reference Manual for definition of NORCLK.

#### **ESD SENSITIVITY**

### ESD (electrostatic discharge) sensitive device.

Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

#### **PACKAGE INFORMATION**

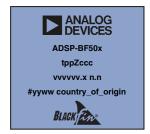

The information presented in Figure 9 and Table 23 provides details about the package branding for the ADSP-BF50x processors.

Figure 9. Product Information on Package

Table 23. Package Brand Information<sup>1</sup>

| Brand Key  | Field Description          |

|------------|----------------------------|

| ADSP-BF50x | Product Name <sup>2</sup>  |

| t          | Temperature Range          |

| рр         | Package Type               |

| Z          | RoHS Compliant Designation |

| ccc        | See Ordering Guide         |

| VVVVV.X    | Assembly Lot Code          |

| n.n        | Silicon Revision           |

| #          | RoHS Compliance Designator |

| yyww       | Date Code                  |

<sup>&</sup>lt;sup>1</sup> Nonautomotive only. For branding information specific to Automotive products, contact Analog Devices Inc.

<sup>&</sup>lt;sup>2</sup> See product names in the Ordering Guide on Page 81.

### **Parallel Peripheral Interface Timing**

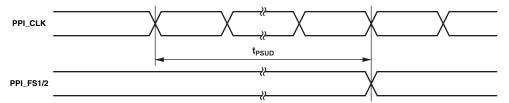

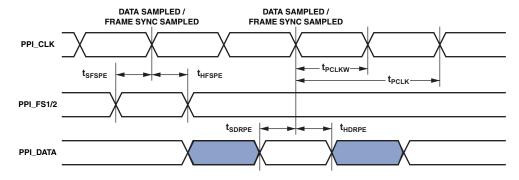

Table 27 and Figure 14 on Page 35, Figure 20 on Page 40, and Figure 22 on Page 41 describe parallel peripheral interface operations.

Table 27. Parallel Peripheral Interface Timing

|                     |                                                                                          |                         | $I_{\text{DDEXT}} = 1.8 \text{ V}$ | <b>V</b> <sub>DDE</sub> | $_{\rm EXT} = 2.5 \text{ V}/3.3 \text{ V}$ |      |

|---------------------|------------------------------------------------------------------------------------------|-------------------------|------------------------------------|-------------------------|--------------------------------------------|------|

| Paramete            | r                                                                                        | Min                     | Max                                | Min                     | Max                                        | Unit |

| Timing Red          | quirements                                                                               |                         |                                    |                         |                                            |      |

| $t_{PCLKW}$         | PPI_CLK Width <sup>1</sup>                                                               | t <sub>SCLK</sub> – 1.5 | 5                                  | t <sub>SCLK</sub> – 1.5 | 5                                          | ns   |

| $t_{PCLK}$          | PPI_CLK Period <sup>1</sup>                                                              | $2 \times t_{SCLK}$     | -1.5                               | $2 \times t_{SCLK}$     | -1.5                                       | ns   |

| Timing Red          | quirements—GP Input and Frame Capture Modes                                              |                         |                                    |                         |                                            |      |

| $t_{PSUD}$          | External Frame Sync Startup Delay <sup>2</sup>                                           | $4 \times t_{PCLK}$     |                                    | $4 \times t_{PCLK}$     |                                            | ns   |

| t <sub>SFSPE</sub>  | External Frame Sync Setup Before PPI_CLK (Nonsampling Edge for Rx, Sampling Edge for Tx) | 6.7                     |                                    | 6.7                     |                                            | ns   |

| t <sub>HFSPE</sub>  | External Frame Sync Hold After PPI_CLK                                                   | 1.5                     |                                    | 1.5                     |                                            | ns   |

| $t_{\text{SDRPE}}$  | Receive Data Setup Before PPI_CLK                                                        | 4.1                     |                                    | 3.5                     |                                            | ns   |

| $t_{\text{HDRPE}}$  | Receive Data Hold After PPI_CLK                                                          | 2                       |                                    | 1.6                     |                                            | ns   |

| Switching           | Characteristics—GP Output and Frame Capture Modes                                        |                         |                                    |                         |                                            |      |

| t <sub>DFSPE</sub>  | Internal Frame Sync Delay After PPI_CLK                                                  |                         | 8.7                                |                         | 8.0                                        | ns   |

| t <sub>HOFSPE</sub> | Internal Frame Sync Hold After PPI_CLK                                                   | 1.7                     |                                    | 1.7                     |                                            | ns   |

| t <sub>DDTPE</sub>  | Transmit Data Delay After PPI_CLK                                                        |                         | 8.7                                |                         | 8.0                                        | ns   |

| t <sub>HDTPE</sub>  | Transmit Data Hold After PPI_CLK                                                         | 2.3                     |                                    | 1.9                     |                                            | ns   |

<sup>&</sup>lt;sup>1</sup> PPI\_CLK frequency cannot exceed f<sub>SCLK</sub>/2

<sup>&</sup>lt;sup>2</sup> The PPI port is fully enabled 4 PPI clock cycles after the PAB write to the PPI port enable bit. Only after the PPI port is fully enabled are external frame syncs and data words guaranteed to be received correctly by the PPI peripheral.

Figure 13. PPI with External Frame Sync Timing

Figure 14. PPI GP Rx Mode with External Frame Sync Timing

### **RSI Controller Timing**

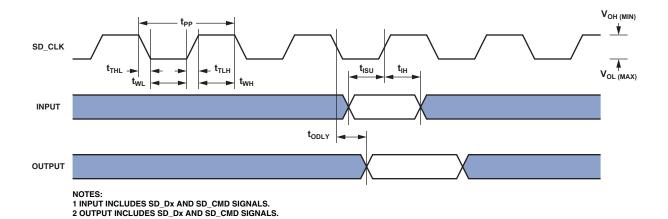

Table 28 and Figure 18 describe RSI Controller Timing. Table 29 and Figure 19 describe RSI controller (high speed) timing.

### Table 28. RSI Controller Timing

| Parar             | meter                                        | Min              | Max | Unit |

|-------------------|----------------------------------------------|------------------|-----|------|

| Timin             | Timing Requirements                          |                  |     |      |

| $t_{ISU}$         | Input Setup Time                             | 5.75             |     | ns   |

| $t_IH$            | Input Hold Time                              | 2                |     | ns   |

| Switc             | hing Characteristics                         |                  |     |      |

| $f_{PP}^{-1}$     | Clock Frequency Data Transfer Mode           | 0                | 25  | MHz  |

| $f_{OD}$          | Clock Frequency Identification Mode          | 100 <sup>2</sup> | 400 | kHz  |

| $t_WL$            | Clock Low Time                               | 10               |     | ns   |

| $t_{WH}$          | Clock High Time                              | 10               |     | ns   |

| $t_{TLH}$         | Clock Rise Time                              |                  | 10  | ns   |

| $t_{THL}$         | Clock Fall Time                              |                  | 10  | ns   |

| $t_{ODLY}$        | Output Delay Time During Data Transfer Mode  |                  | 14  | ns   |

| t <sub>ODLY</sub> | Output Delay Time During Identification Mode |                  | 50  | ns   |

$<sup>^{1}\,</sup>t_{_{PP}}=1/f_{_{PP}}.$

<sup>&</sup>lt;sup>2</sup> Specification can be 0 kHz, which means to stop the clock. The given minimum frequency range is for cases where a continuous clock is required.

Figure 18. RSI Controller Timing

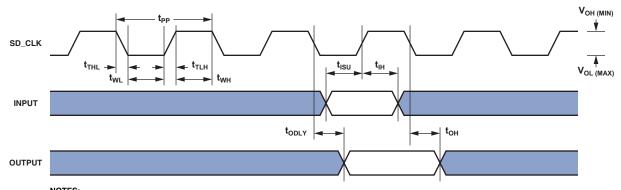

Table 29. RSI Controller Timing (High Speed Mode)

| Parar             | Parameter                                   |      | Max | Unit |

|-------------------|---------------------------------------------|------|-----|------|

| Timin             | g Requirements                              |      |     |      |

| $t_{ISU}$         | Input Setup Time                            | 5.75 |     | ns   |

| $t_{\text{IH}}$   | Input Hold Time                             | 2    |     | ns   |

| Switch            | ning Characteristics                        |      |     |      |

| $f_{PP}^{-1}$     | Clock Frequency Data Transfer Mode          | 0    | 50  | MHz  |

| $t_WL$            | Clock Low Time                              | 7    |     | ns   |

| $t_{WH}$          | Clock High Time                             | 7    |     | ns   |

| $t_{TLH}$         | Clock Rise Time                             |      | 3   | ns   |

| $t_{THL}$         | Clock Fall Time                             |      | 3   | ns   |

| $t_{\text{ODLY}}$ | Output Delay Time During Data Transfer Mode |      | 2.5 | ns   |

| t <sub>OH</sub>   | Output Hold Time                            | 2.5  |     | ns   |

$<sup>^{1}</sup>$   $t_{pp} = 1/f_{pp}$ .

NOTES: 1 INPUT INCLUDES SD\_Dx AND SD\_CMD SIGNALS. 2 OUTPUT INCLUDES SD\_Dx AND SD\_CMD SIGNALS.

Figure 19. RSI Controller Timing (High-Speed Mode)

#### **Serial Ports**

Table 30 through Table 33 on Page 41 and Figure 20 on Page 40 through Figure 22 on Page 41 describe serial port operations.

Table 30. Serial Ports—External Clock

|                     |                                                                                   | V                   | 7 <sub>DDEXT</sub> = 1.8 V | V <sub>DDEX</sub>   | <sub>T</sub> = 2.5 V/3.3 V |      |

|---------------------|-----------------------------------------------------------------------------------|---------------------|----------------------------|---------------------|----------------------------|------|

| Parameter           |                                                                                   | Min                 | Max                        | Min                 | Max                        | Unit |

| Timing Re           | quirements                                                                        |                     |                            |                     |                            |      |

| t <sub>SFSE</sub>   | TFSx/RFSx Setup Before TSCLKx/RSCLKx <sup>1</sup>                                 | 3.0                 |                            | 3.0                 |                            | ns   |

| t <sub>HFSE</sub>   | TFSx/RFSx Hold After TSCLKx/RSCLKx <sup>1</sup>                                   | 3.0                 |                            | 3.0                 |                            | ns   |

| t <sub>SDRE</sub>   | Receive Data Setup Before RSCLKx <sup>1,2</sup>                                   | 3.0                 |                            | 3.0                 |                            | ns   |

| $t_{\text{HDRE}}$   | Receive Data Hold After RSCLKx <sup>1,2</sup>                                     | 3.5                 |                            | 3.0                 |                            | ns   |

| t <sub>SCLKEW</sub> | TSCLKx/RSCLKx Width                                                               | 4.5                 |                            | 4.5                 |                            | ns   |

| t <sub>SCLKE</sub>  | TSCLKx/RSCLKx Period                                                              | $2 \times t_{SCLK}$ |                            | $2 \times t_{SCLK}$ |                            | ns   |

| Switching           | Characteristics                                                                   |                     |                            |                     |                            |      |

| t <sub>DFSE</sub>   | TFSx/RFSx Delay After TSCLKx/RSCLKx (Internally Generated TFSx/RFSx) <sup>3</sup> |                     | 10.0                       |                     | 10.0                       | ns   |

| t <sub>HOFSE</sub>  | TFSx/RFSx Hold After TSCLKx/RSCLKx (Internally Generated TFSx/RFSx) <sup>3</sup>  | 0.0                 |                            | 0.0                 |                            | ns   |

| t <sub>DDTE</sub>   | Transmit Data Delay After TSCLKx <sup>3</sup>                                     |                     | 11.0                       |                     | 10.0                       | ns   |

| t <sub>HDTE</sub>   | Transmit Data Hold After TSCLKx <sup>3</sup>                                      | 0.0                 |                            | 0.0                 |                            | ns   |

<sup>&</sup>lt;sup>1</sup> Referenced to sample edge.

Table 31. Serial Ports—Internal Clock

|                     |                                                                                   | v    | $V_{\text{DDEXT}} = 1.8 \text{ V}$ | $V_{\text{ddex}}$ | $_{T}$ = 2.5 V/3.3 V |      |

|---------------------|-----------------------------------------------------------------------------------|------|------------------------------------|-------------------|----------------------|------|

| Parameter           |                                                                                   | Min  | Max                                | Min               | Max                  | Unit |

| Timing Red          | quirements                                                                        |      |                                    |                   |                      |      |

| $t_{SFSI}$          | TFSx/RFSx Setup Before TSCLKx/RSCLKx <sup>1</sup>                                 | 11.0 |                                    | 9.6               |                      | ns   |

| t <sub>HFSI</sub>   | TFSx/RFSx Hold After TSCLKx/RSCLKx <sup>1</sup>                                   | -1.5 |                                    | -1.5              |                      | ns   |

| $t_{\text{SDRI}}$   | Receive Data Setup Before RSCLKx <sup>1,2</sup>                                   | 11.5 |                                    | 10.0              |                      | ns   |

| $t_{HDRI}$          | Receive Data Hold After RSCLKx <sup>1,2</sup>                                     | -1.5 |                                    | -1.5              |                      | ns   |

| Switching           | Characteristics                                                                   |      |                                    |                   |                      |      |

| t <sub>SCLKIW</sub> | TSCLKx/RSCLKx Width                                                               | 7.0  |                                    | 8.0               |                      | ns   |

| t <sub>DFSI</sub>   | TFSx/RFSx Delay After TSCLKx/RSCLKx (Internally Generated TFSx/RFSx) <sup>3</sup> |      | 4.0                                |                   | 3.0                  | ns   |

| t <sub>HOFSI</sub>  | TFSx/RFSx Hold After TSCLKx/RSCLKx (Internally Generated TFSx/RFSx) <sup>3</sup>  | -2.0 |                                    | -1.0              |                      | ns   |

| t <sub>DDTI</sub>   | Transmit Data Delay After TSCLKx <sup>3</sup>                                     |      | 4.0                                |                   | 3.0                  | ns   |

| t <sub>HDTI</sub>   | Transmit Data Hold After TSCLKx <sup>3</sup>                                      | -1.8 |                                    | -1.5              |                      | ns   |

$<sup>^{\</sup>rm 1}$  Referenced to sample edge.

<sup>&</sup>lt;sup>2</sup>When SPORT is used in conjunction with the ACM, refer to the timing requirements in Table 41 (ACM Timing).

<sup>&</sup>lt;sup>3</sup> Referenced to drive edge.

<sup>&</sup>lt;sup>2</sup>When SPORT is used in conjunction with the ACM, refer to the timing requirements in Table 41 (ACM Timing).

$<sup>^{\</sup>rm 3}\,\text{Referenced}$  to drive edge.

# Universal Asynchronous Receiver-Transmitter (UART) Ports—Receive and Transmit Timing

The UART ports receive and transmit operations are described in the *ADSP-BF50x Hardware Reference Manual*.

### **General-Purpose Port Timing**

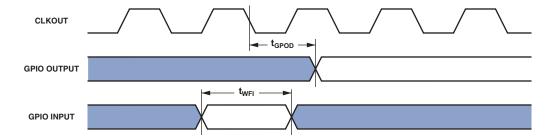

Table 36 and Figure 25 describe general-purpose port operations.

Table 36. General-Purpose Port Timing

|                                                             |                                                        | $V_{DDEXT} = 1.8 V$   |      | $V_{DDEXT} = 2.5 \text{ V}/3.3 \text{ V}$ |     |      |

|-------------------------------------------------------------|--------------------------------------------------------|-----------------------|------|-------------------------------------------|-----|------|

| Parameter                                                   |                                                        | Min                   | Max  | Min                                       | Max | Unit |

| Timing Requirement                                          |                                                        |                       |      |                                           |     |      |

| t <sub>WFI</sub> General-Purpose Port Pin Input Pulse Width |                                                        | t <sub>SCLK</sub> + 1 |      | t <sub>SCLK</sub> + 1                     |     | ns   |

| Switching Characteristic                                    |                                                        |                       |      |                                           |     |      |

| $t_{GPOD}$                                                  | General-Purpose Port Pin Output Delay from CLKOUT High | 0                     | 11.0 | 0                                         | 8.9 | ns   |

Figure 25. General-Purpose Port Timing

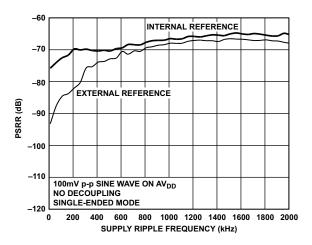

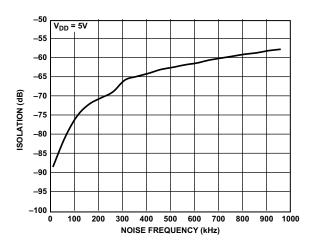

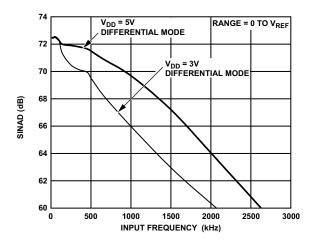

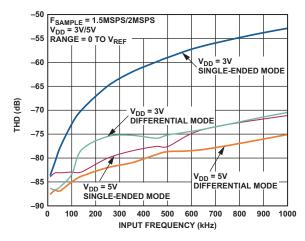

#### **ADC—TYPICAL PERFORMANCE CHARACTERISTICS**

$T_A = 25$ °C, unless otherwise noted.

Figure 50. PSRR vs. Supply Ripple Frequency Without Supply Decoupling

Figure 51. Channel-to-Channel Isolation

Figure 52. SINAD vs. Analog Input Frequency for Various Supply Voltages

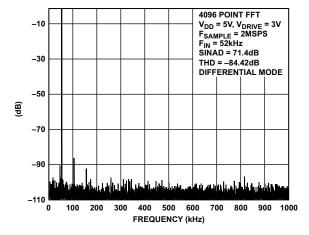

Figure 53. Typical FFT

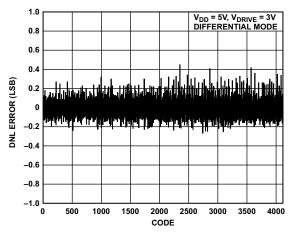

Figure 54. Typical DNL

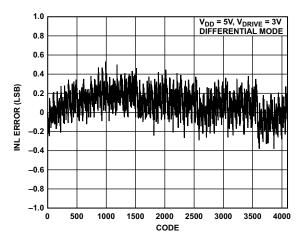

Figure 55. Typical INL

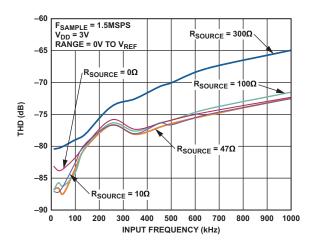

Figure 66. THD vs. Analog Input Frequency for Various Source Impedances, Differential Mode

Figure 67. THD vs. Analog Input Frequency for Various Supply Voltages

#### **Analog Inputs**

The ADC has a total of 12 analog inputs. Each on-board ADC has six analog inputs that can be configured as six single-ended channels, three pseudo differential channels, or three fully differential channels. These may be selected as described in the Analog Input Selection section.

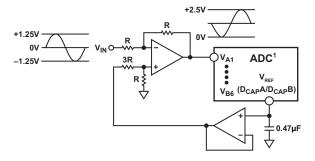

#### Single-Ended Mode

The ADC can have a total of 12 single-ended analog input channels. In applications where the signal source has high impedance, it is recommended to buffer the analog input before applying it to the ADC. The analog input range can be programmed to be either 0 to  $V_{\text{REF}}$  or 0 to 2  $\times$   $V_{\text{REF}}.$

If the analog input signal to be sampled is bipolar, the internal reference of the ADC can be used to externally bias up this signal to make it correctly formatted for the ADC. Figure 68 shows a typical connection diagram when operating the ADC in single-ended mode.

<sup>1</sup>ADDITIONAL PINS OMITTED FOR CLARITY.

Figure 68. Single-Ended Mode Connection Diagram

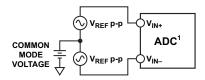

#### **Differential Mode**

The ADC can have a total of six differential analog input pairs.

Differential signals have some benefits over single-ended signals, including noise immunity based on the device's common-mode rejection and improvements in distortion performance. Figure 69 (Differential Input Definition) defines the fully differential analog input of the ADC.

<sup>1</sup>ADDITIONAL PINS OMITTED FOR CLARITY.

Figure 69. Differential Input Definition

The amplitude of the differential signal is the difference between the signals applied to the  $V_{\rm IN+}$  and  $V_{\rm IN-}$  pins in each differential pair  $(V_{\rm IN+}\,V_{\rm IN-}).\,V_{\rm IN+}$  and  $V_{\rm IN-}$  should be simultaneously driven by two signals each of amplitude  $V_{\rm REF}$  (or  $2\times V_{\rm REF}$ , depending on the range chosen) that are 180° out of phase. The amplitude of the differential signal is, therefore (assuming the 0 to  $V_{\rm REF}$  range is selected)  $-V_{\rm REF}$  to  $+V_{\rm REF}$  peak-to-peak  $(2\times V_{\rm REF})$ , regardless of the common mode (CM).

The common mode is the average of the two signals

$$(V_{IN+} + V_{IN-})/2$$

and is, therefore, the voltage on which the two inputs are centered.

This results in the span of each input being CM  $\pm$  V<sub>REF</sub>/2. This voltage has to be set up externally and its range varies with the reference value, V<sub>REF</sub>. As the value of V<sub>REF</sub> increases, the common-mode range decreases. When driving the inputs with an amplifier, the actual common-mode range is determined by the amplifier's output voltage swing.

Figure 70 (Input Common-Mode Range vs. VREF (0 to VREF Range, VDD = 5 V)) and Figure 71 (Input Common-Mode Range vs. VREF ( $2 \times VREF$  Range, VDD = 5 V)) show how the common-mode range typically varies with  $V_{REF}$  for a 5 V power

down for a relatively long duration between these bursts of several conversions. When the ADC is in partial power-down, all analog circuitry is powered down except for the on-chip reference and reference buffer.

To enter partial power-down mode, the conversion process must be interrupted by bringing  $\overline{CS}$  high anywhere after the second falling edge of ADSCLK and before the  $10^{th}$  falling edge of ADSCLK, as shown in Figure 81 (Entering Partial Power-Down Mode). Once  $\overline{CS}$  is brought high in this window of ADSCLKs, the part enters partial power-down, the conversion that was initiated by the falling edge of  $\overline{CS}$  is terminated, and  $D_{OUT}A$  and  $D_{OUT}B$  go back into three-state. If  $\overline{CS}$  is brought high before the second ADSCLK falling edge, the part remains in normal mode and does not power down. This avoids accidental power-down due to glitches on the  $\overline{CS}$  line.

Figure 81. Entering Partial Power-Down Mode

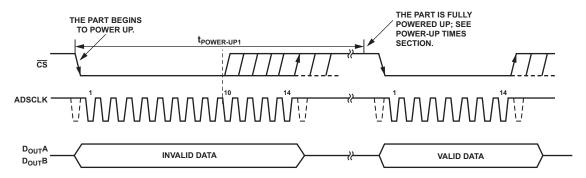

To exit this mode of operation and power up the ADC again, a dummy conversion is performed. On the falling edge of  $\overline{CS}$ , the device begins to power up and continues to power up as long as  $\overline{CS}$  is held low until after the falling edge of the  $10^{th}$  ADSCLK. The device is fully powered up after approximately 1  $\mu$ s has elapsed, and valid data results from the next conversion, as shown in Figure 82 (Exiting Partial Power-Down Mode). If  $\overline{CS}$  is brought high before the second falling edge of ADSCLK, the ADC again goes into partial power-down. This avoids accidental power-up due to glitches on the  $\overline{CS}$  line. Although the device may begin to power up on the falling edge of  $\overline{CS}$ , it powers down

again on the rising edge of  $\overline{\text{CS}}$ . If the ADC is already in partial power-down mode and  $\overline{\text{CS}}$  is brought high between the second and 10<sup>th</sup> falling edges of ADSCLK, the device enters full power-down mode.

#### Full Power-Down Mode

This mode is intended for use in applications where throughput rates slower than those in the partial power-down mode are required, as power-up from a full power-down takes substantially longer than that from partial power-down. This mode is more suited to applications where a series of conversions performed at a relatively high throughput rate are followed by a long period of inactivity and thus power-down. When the ADC is in full power-down, all analog circuitry is powered down. Full power-down is entered in a similar way as partial power-down, except the timing sequence shown in Figure 81 (Entering Partial Power-Down Mode) must be executed twice. The conversion process must be interrupted in a similar fashion by bringing  $\overline{CS}$ high anywhere after the second falling edge of ADSCLK and before the 10<sup>th</sup> falling edge of ADSCLK. The device enters partial power-down at this point. To reach full power-down, the next conversion cycle must be interrupted in the same way, as shown in Figure 83 (Entering Full Power-Down Mode). Once CS is brought high in this window of ADSCLKs, the part completely powers down.

Note that it is not necessary to complete the 14 ADSCLKs once  $\overline{CS}$  is brought high to enter a power-down mode.

To exit full power-down and power up the ADC, a dummy conversion is performed, as when powering up from partial power-down. On the falling edge of  $\overline{CS}$ , the device begins to power up and continues to power up, as long as  $\overline{CS}$  is held low until after the falling edge of the  $10^{th}$  ADSCLK. The required power-up time must elapse before a conversion can be initiated, as shown in Figure 84 (Exiting Full Power-Down Mode). See the Power-Up Times section for the power-up times associated with the ADC.

Figure 82. Exiting Partial Power-Down Mode

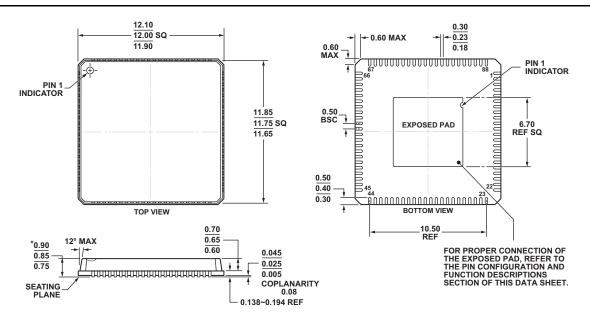

\*COMPLIANT TO JEDEC STANDARDS MO-220-VRRD EXCEPT FOR MINIMUM THICKNESS AND LEAD COUNT.

Figure 94. 88-Lead Lead Frame Chip Scale Package [LFCSP\_VQ]<sup>1</sup>

12 x 12 mm Body, Very Thin Quad

(CP-88-5)

Dimensions shown in millimeters

<sup>&</sup>lt;sup>1</sup> For information relating to the CP-88-5 package's exposed pad, see the table endnote on Page 76.

#### **AUTOMOTIVE PRODUCTS**

The ADBF504W model is available with controlled manufacturing to support the quality and reliability requirements of automotive applications. Note that these automotive models may have specifications that differ from the commercial models and designers should review the Specifications section of this

data sheet carefully. Only the automotive grade products shown in Table 58 are available for use in automotive applications. Contact your local ADI account representative for specific product ordering information and to obtain the specific Automotive Reliability reports for these models.

**Table 58. Automotive Products**

| Automotive Models <sup>1,2</sup> | Temperature<br>Range <sup>3</sup> | Processor Instruction Rate (Maximum) |     | , <b>.</b> .     | Package<br>Option |

|----------------------------------|-----------------------------------|--------------------------------------|-----|------------------|-------------------|

| ADBF504WYCPZ4XX                  | -40°C to +105°C                   | 400 MHz                              | N/A | 88-Lead LFCSP_VQ | CP-88-5           |

<sup>&</sup>lt;sup>1</sup> Z = RoHS compliant part.

### **ORDERING GUIDE**

| Model <sup>1,2</sup> | Temperature<br>Range <sup>3,4</sup> | Processor Instruction Rate (Maximum) | Flash<br>Memory | Package<br>Description | Package<br>Option |

|----------------------|-------------------------------------|--------------------------------------|-----------------|------------------------|-------------------|

| ADSP-BF504BCPZ-3F    | -40°C to +85°C                      | 300 MHz                              | 32M bit         | 88-Lead LFCSP_VQ       | CP-88-5           |

| ADSP-BF504BCPZ-4     | -40°C to +85°C                      | 400 MHz                              | N/A             | 88-Lead LFCSP_VQ       | CP-88-5           |

| ADSP-BF504BCPZ-4F    | -40°C to +85°C                      | 400 MHz                              | 32M bit         | 88-Lead LFCSP_VQ       | CP-88-5           |