Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Not For New Designs                                                              |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | R8C                                                                              |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 20MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, LINbus, SIO, SSU, UART/USART                                   |

| Peripherals                | POR, PWM, Voltage Detect, WDT                                                    |

| Number of I/O              | 15                                                                               |

| Program Memory Size        | 4KB (4K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 1K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                      |

| Data Converters            | A/D 4x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 20-LSSOP (0.173", 4.40mm Width)                                                  |

| Supplier Device Package    | 20-LSSOP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f21321ddsp-u0 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Current of Feb. 2010

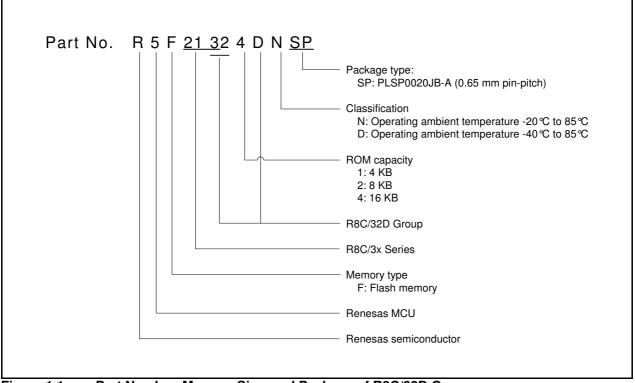

## 1.2 Product List

Table 1.3 lists Product List for R8C/32D Group, and Figure 1.1 shows a Part Number, Memory Size, and Package of R8C/32D Group.

| Part No.         | ROM Capacity | RAM Capacity | Package Type | Remarks   |

|------------------|--------------|--------------|--------------|-----------|

| R5F21321DNSP     | 4 Kbytes     | 1 Kbyte      | PLSP0020JB-A | N version |

| R5F21322DNSP     | 8 Kbytes     | 1 Kbyte      | PLSP0020JB-A |           |

| R5F21324DNSP     | 16 Kbytes    | 1 Kbyte      | PLSP0020JB-A |           |

| R5F21321DDSP (D) | 4 Kbytes     | 1 Kbyte      | PLSP0020JB-A | D version |

| R5F21322DDSP (D) | 8 Kbytes     | 1 Kbyte      | PLSP0020JB-A |           |

| R5F21324DDSP (D) | 16 Kbytes    | 1 Kbyte      | PLSP0020JB-A |           |

### Table 1.3 Product List for R8C/32D Group

(D): Under development

R/W

R/W

## 6.2.2 Voltage Monitor Circuit Edge Select Register (VCAC)

| Ado     | dress 0 | 031h      | h                                                                  |             |             |           |      |             |            |    |  |  |

|---------|---------|-----------|--------------------------------------------------------------------|-------------|-------------|-----------|------|-------------|------------|----|--|--|

|         | Bit     | Bit b7 b6 |                                                                    | b5          | b4          | b3        | 3    | b2          | b1         | b0 |  |  |

| Sy      | mbol    |           |                                                                    | _           | —           |           | -    | VCAC2       | VCAC1      |    |  |  |

| After F | Reset   | 0         | 0                                                                  | 0           | 0           | 0         |      | 0           | 0          | 0  |  |  |

|         |         |           |                                                                    |             |             |           |      |             |            |    |  |  |

| Bit     | Symbo   | ol        |                                                                    | Bit Name    |             |           |      |             | Functio    | on |  |  |

| b0      |         | No        | othing is assig                                                    | ned. If nec | essary, set | : to 0. \ | Wher | n read, the | content is | 0. |  |  |

| b1      | VCAC    | C1 VC     | Voltage monitor 1 circuit edge select bit (1) 0: One edge          |             |             |           |      |             |            |    |  |  |

|         |         |           | 1: Both edges                                                      |             |             |           |      |             |            |    |  |  |

| b2      | VCAC    | 2 Vo      | Itage monitor 2 circuit edge select bit <sup>(2)</sup> 0: One edge |             |             |           |      |             |            |    |  |  |

| b2 | VCAC2 | Voltage monitor 2 circuit edge select bit <sup>(2)</sup> 0: One edge<br>1: Both edges | R/W |   |

|----|-------|---------------------------------------------------------------------------------------|-----|---|

| b3 | —     | Nothing is assigned. If necessary, set to 0. When read, the content is 0.             | —   |   |

| b4 | —     |                                                                                       |     | ĺ |

| b5 | —     |                                                                                       |     | ĺ |

| b6 | —     |                                                                                       |     | l |

| b7 | —     |                                                                                       |     | l |

Notes:

- 1. When the VCAC1 bit is set to 0 (one edge), the VW1C7 bit in the VW1C register is enabled. Set the VW1C7 bit after setting the VCAC1 bit to 0.

- 2. When the VCAC2 bit is set to 0 (one edge), the VW2C7 bit in the VW2C register is enabled. Set the VW2C7 bit after setting the VCAC2 bit to 0.

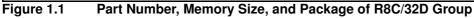

### 6.2.3 Voltage Detect Register 1 (VCA1)

| Bit | Symbol | Bit Name                                               | Function                                                                    | R/W |

|-----|--------|--------------------------------------------------------|-----------------------------------------------------------------------------|-----|

| b0  | —      | Reserved bits                                          | Set to 0.                                                                   | R/W |

| b1  |        |                                                        |                                                                             |     |

| b2  | —      |                                                        |                                                                             |     |

| b3  | VCA13  | Voltage detection 2 signal monitor flag <sup>(1)</sup> | 0: VCC < Vdet2<br>1: VCC ≥ Vdet2<br>or voltage detection 2 circuit disabled | R   |

| b4  | —      | Reserved bits                                          | Set to 0.                                                                   | R/W |

| b5  | —      |                                                        |                                                                             |     |

| b6  | —      |                                                        |                                                                             |     |

| b7  | _      |                                                        |                                                                             |     |

Note:

1. When the VCA27 bit in the VCA2 register is set to 1 (voltage detection 2 circuit enabled), the VCA13 bit is enabled.

When the VCA27 bit in the VCA2 register is set to 0 (voltage detection 2 circuit disabled), the VCA13 bit is set to 1 (VCC  $\geq$  Vdet2).

### 9.8.1 How to Use Oscillation Stop Detection Function

• The oscillation stop detection interrupt shares a vector with the voltage monitor 1 interrupt, the voltage monitor 2 interrupt, and the watchdog timer interrupt. To use the oscillation stop detection interrupt and watchdog timer interrupt, the interrupt source needs to be determined.

Table 9.6 lists the Determination of Interrupt Sources for Oscillation Stop Detection, Watchdog Timer, Voltage Monitor 1, or Voltage Monitor 2 Interrupt. Figure 9.11 shows an Example of Determining Interrupt Sources for Oscillation Stop Detection, Watchdog Timer, Voltage Monitor 1, or Voltage Monitor 2 Interrupt.

- When the XIN clock restarts after oscillation stop, switch the XIN clock to the clock source for the CPU clock and the peripheral functions by a program.

Figure 9.10 shows the Procedure for Switching Clock Source from Low-Speed On-Chip Oscillator to XIN Clock.

- To enter wait mode while the oscillation stop detection function is used, set the CM02 bit to 0 (peripheral function clock does not stop in wait mode).

- Since the oscillation stop detection function is a function for cases where the XIN clock is stopped by an external cause, set bits OCD1 to OCD0 to 00b to stop or start the XIN clock by a program (select stop mode or change the CM05 bit).

- This function cannot be used when the XIN clock frequency is below 2 MHz. In this case, set bits OCD1 to OCD0 to 00b.

- To use the low-speed on-chip oscillator clock as the clock source for the CPU clock and the peripheral functions after detecting the oscillation stop, set the FRA01 bit in the FRA0 register to 0 (low-speed on-chip oscillator selected) and bits OCD1 to OCD0 to 11b.

To use the high-speed on-chip oscillator clock as the clock source for the CPU clock and the peripheral functions after detecting the oscillation stop, first set the FRA00 bit to 1 (high-speed on-chip oscillator oscillator) and the FRA01 bit to 1 (high-speed on-chip oscillator selected). Then set bits OCD1 to OCD0 to 11b.

# 11.2.2 Interrupt Control Register (FMRDYIC, TRCIC)

| Address 0041h (FMRDYIC), 0047h (TRCIC) |                                   |                                                                            |                                              |                    |          |                                                                                 |                             |                         |       |                          |

|----------------------------------------|-----------------------------------|----------------------------------------------------------------------------|----------------------------------------------|--------------------|----------|---------------------------------------------------------------------------------|-----------------------------|-------------------------|-------|--------------------------|

|                                        | Bit I                             | o7                                                                         | b6                                           | b5                 | b4       | b3                                                                              | b2                          | b1                      | b0    |                          |

| Sy                                     | mbol ·                            | _                                                                          |                                              |                    |          | IR                                                                              | ILVL2                       | ILVL1                   | ILVL0 |                          |

| After F                                | Reset                             | Х                                                                          | Х                                            | Х                  | Х        | Х                                                                               | 0                           | 0                       | 0     |                          |

| Bit<br>b0<br>b1<br>b2                  | Symbol<br>ILVL0<br>ILVL1<br>ILVL2 | Interru                                                                    | Bit<br>pt priority                           | Name<br>level sele | ect bit  | <sup>b2 b1 b0</sup><br>0 0 0: Leve<br>0 0 1: Leve<br>0 1 0: Leve<br>0 1 1: Leve | I 0 (interrup<br>I 1<br>I 2 | Function<br>t disabled) |       | R/W<br>R/W<br>R/W<br>R/W |

|                                        |                                   |                                                                            |                                              |                    |          | 1 0 1 1: Leve<br>1 0 0: Leve<br>1 0 1: Leve<br>1 1 0: Leve<br>1 1 1: Leve       | 4<br>  5<br>  6             |                         |       |                          |

| b3                                     | IR                                | Interrupt request bit 0: No interrupt request bit 1: Interrupt request bit |                                              |                    |          |                                                                                 | • •                         | ed                      |       | R                        |

| b4                                     | —                                 |                                                                            | Nothing is assigned. If necessary, set to 0. |                    |          |                                                                                 |                             |                         |       | —                        |

| b5                                     |                                   | When                                                                       | read, the                                    | content is         | undefine | d.                                                                              |                             |                         |       |                          |

| b6                                     | —                                 |                                                                            |                                              |                    |          |                                                                                 |                             |                         |       |                          |

| b7                                     | —                                 |                                                                            |                                              |                    |          |                                                                                 |                             |                         |       |                          |

Rewrite the interrupt control register when an interrupt request corresponding to the register is not generated. Refer to **11.8.5 Rewriting Interrupt Control Register**.

# 11.5.1 Key Input Enable Register 0 (KIEN)

| Address 01FEh |         |        |              |                |       |            |        |          |       |     |       |

|---------------|---------|--------|--------------|----------------|-------|------------|--------|----------|-------|-----|-------|

|               | Bit I   | o7     | b6           | b5             | b4    | b3         | b2     | b1       | b0    |     |       |

| Sy            | mbol Kl | 3PL    | KI3EN        | KI2PL          | KI2EN | KI1PL      | KI1EN  | KI0PL    | KI0EN |     |       |

| After F       | Reset   | 0      | 0            | 0              | 0     | 0          | 0      | 0        | 0     |     |       |

|               |         |        |              |                |       |            |        |          |       | DAA |       |

| Bit           | Symbol  |        | BI           | t Name         |       |            |        | Function |       |     | R/W   |

| b0            | KI0EN   | KI0 in | put enable   | bit            |       | 0: Disab   | led    |          |       |     | R/W   |

|               |         |        |              |                |       | 1: Enable  | ed     |          |       |     |       |

| b1            | KI0PL   | KI0 in | put polarity | select bit     |       | 0: Falling | g edge |          |       |     | R/W   |

|               |         |        |              |                |       | 1: Rising  | edge   |          |       |     |       |

| b2            | KI1EN   | KI1 in | put enable   | bit            |       | 0: Disab   | led    |          |       |     | R/W   |

|               |         |        |              |                |       | 1: Enable  | ed     |          |       |     |       |

| b3            | KI1PL   | KI1 in | put polarity | select bit     |       | 0: Falling | g edge |          |       |     | R/W   |

|               |         |        |              |                |       | 1: Rising  | edge   |          |       |     |       |

| b4            | KI2EN   | KI2 in | put enable   | bit            |       | 0: Disab   | led    |          |       |     | R/W   |

|               |         |        | •            |                |       | 1: Enable  | ed     |          |       |     |       |

| b5            | KI2PL   | KI2 in | put polarity | select bit     |       | 0: Falling | n edae |          |       |     | R/W   |

|               |         |        | parpolant    | 00.000.000     |       | 1: Rising  |        |          |       |     | ,     |

| b6            | KI3EN   | KI3 in | put enable   | hit            |       | 0: Disab   |        |          |       |     | R/W   |

|               |         |        |              | on             |       | 1: Enable  |        |          |       |     | 10,00 |

| h7            | KIODI   |        | nut poloriti | , a ala at hit |       |            |        |          |       |     |       |

| b7            | KI3PL   | K13 In | put polarity | Select Dit     |       | 0: Falling |        |          |       |     | R/W   |

|               |         |        |              |                |       | 1: Rising  | l edge |          |       |     |       |

The IR bit in the KUPIC register may be set to 1 (interrupt requested) when the KIEN register is rewritten. Refer to **11.8.4 Changing Interrupt Sources**.

#### **Option Function Select Register (OFS)** 14.2.6

| Address     | )FFFFh   |       |        |             |             |       |    |       |  |

|-------------|----------|-------|--------|-------------|-------------|-------|----|-------|--|

| Bit         | b7       | b6    | b5     | b4          | b3          | b2    | b1 | b0    |  |

| Symbol      | CSPROINI | LVDAS | VDSEL1 | VDSEL0      | ROMCP1      | ROMCR | —  | WDTON |  |

| After Reset |          |       |        | Iser Settin | a Value (1) |       |    |       |  |

User Setting value

| Bit      | Symbol           | Bit Name                                               | Function                                                                                                                                                 | R/W        |

|----------|------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| b0       | WDTON            | Watchdog timer start select bit                        | <ul><li>0: Watchdog timer automatically starts after reset.</li><li>1: Watchdog timer is stopped after reset.</li></ul>                                  | R/W        |

| b1       | —                | Reserved bit                                           | Set to 1.                                                                                                                                                | R/W        |

| b2       | ROMCR            | ROM code protect disable bit                           | 0: ROM code protect disabled<br>1: ROMCP1 bit enabled                                                                                                    | R/W        |

| b3       |                  | ROM code protect bit                                   | 0: ROM code protect enabled<br>1: ROM code protect disabled                                                                                              | R/W        |

| b4<br>b5 | VDSEL0<br>VDSEL1 | Voltage detection 0 level select bit <sup>(2)</sup>    | <sup>b5 b4</sup><br>0 0: 3.80 V selected (Vdet0_3)<br>0 1: 2.85 V selected (Vdet0_2)<br>1 0: 2.35 V selected (Vdet0_1)<br>1 1: 1.90 V selected (Vdet0_0) | R/W<br>R/W |

| b6       | LVDAS            | Voltage detection 0 circuit start bit <sup>(3)</sup>   | 0: Voltage monitor 0 reset enabled after reset<br>1: Voltage monitor 0 reset disabled after reset                                                        | R/W        |

| b7       | CSPROINI         | Count source protection mode<br>after reset select bit | 0: Count source protect mode enabled after reset<br>1: Count source protect mode disabled after reset                                                    | R/W        |

Notes:

1. The OFS register is allocated in the flash memory, not in the SFRs. Set appropriate values as ROM data by a program.

Do not write additions to the OFS register. If the block including the OFS register is erased, the OFS register is set to FFh.

When blank products are shipped, the OFS register is set to FFh. It is set to the written value after written by the user.

When factory-programming products are shipped, the value of the OFS register is the value programmed by the user.

2. The same level of the voltage detection 0 level selected by bits VDSEL0 and VDESL1 is set in both functions of voltage monitor 0 reset and power-on reset.

3. To use power-on reset and voltage monitor 0 reset, set the LVDAS bit to 0 (voltage monitor 0 reset enabled after reset).

For a setting example of the OFS register, refer to 13.3.1 Setting Example of Option Function Select Area.

### LVDAS Bit (Voltage Detection 0 Circuit Start Bit)

The Vdet0 voltage to be monitored by the voltage detection 0 circuit is selected by bits VDSEL0 and VDSEL1.

R/W

#### Timer RA I/O Control Register (TRAIOC) in Event Counter Mode 16.5.1

|   | Ado     | dress ( | 0101h | 1   |               |               |                                                               |                                                                                                                                                                                                             |              |          |         |              |  |

|---|---------|---------|-------|-----|---------------|---------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------|---------|--------------|--|

|   |         | Bit     | b7    | 7   | b6            | b5            | b4                                                            | b3                                                                                                                                                                                                          | b2           | b1       | b0      |              |  |

|   | Sy      | mbol    | TIOC  | T1  | TIOGT0        | TIPF1         | TIPF0                                                         | —                                                                                                                                                                                                           | TOENA        | TOPCR    | TEDGSEL |              |  |

|   | After F | Reset   | 0     |     | 0             | 0             | 0                                                             | 0                                                                                                                                                                                                           | 0            | 0        | 0       |              |  |

| г | D:+     | 0.00    | hal   | 1   | D:+           | Marra         | 1                                                             |                                                                                                                                                                                                             |              |          |         |              |  |

|   | Bit     | Sym     |       |     | BIL           | Name          |                                                               |                                                                                                                                                                                                             |              | Function |         | R/W<br>t R/W |  |

|   | b0      | TEDG    | SEL   | TRA | AIO polarity  | switch bit    |                                                               | <ul> <li>0: Starts counting at rising edge of the TRAIO input<br/>and TRAO starts output at "L"</li> <li>1: Starts counting at falling edge of the TRAIO input<br/>and TRAO starts output at "H"</li> </ul> |              |          |         |              |  |

| t | b1      | TOP     | CR    | TRA | AIO output    | control bit   |                                                               | Set to 0 in event counter mode.                                                                                                                                                                             |              |          |         |              |  |

| t | b2      | TOE     | NA    | TRA | AO output e   | enable bit    |                                                               | 0: TRAO output disabled                                                                                                                                                                                     |              |          |         |              |  |

|   |         |         |       |     |               |               |                                                               | 1: TRAO output                                                                                                                                                                                              |              |          |         |              |  |

| Γ | b3      |         | _     | Res | erved bit     |               |                                                               | Set to 0.                                                                                                                                                                                                   |              |          |         |              |  |

| Γ | b4      | TIP     | 'F0   | TRA | AIO input fil | lter select b | oit (1)                                                       | <sup>b5 b4</sup><br>0 0: No filte                                                                                                                                                                           |              |          |         | R/W          |  |

|   | b5      | TIP     | 'F1   |     |               |               |                                                               |                                                                                                                                                                                                             | vith f1 samp | lina     |         | R/W          |  |

|   |         |         |       |     |               |               |                                                               |                                                                                                                                                                                                             | •            | •        |         |              |  |

|   |         |         |       |     |               |               | 1 0: Filter with f8 sampling<br>1 1: Filter with f32 sampling |                                                                                                                                                                                                             |              |          |         |              |  |

| t | b6      | TIOC    | GT0   | TR/ | AIO event in  | nput contro   | ol bit                                                        | b7 b6                                                                                                                                                                                                       |              |          |         | R/W          |  |

| t | b7      | TIO     | GT1   |     |               |               |                                                               | 0 0: Event input always enabled                                                                                                                                                                             |              |          |         |              |  |

Note:

b7

TIOGT1

1. When the same value from the TRAIO pin is sampled three times continuously, the input is determined.

0 1: Do not set.

1 1: Do not set.

(timer RC output)

1 0: Event input enabled for "L" period of TRCIOD

## 18. Timer RC

Timer RC is a 16-bit timer with four I/O pins.

### 18.1 Overview

Timer RC uses either f1, fOCO40M or fOCO-F as its operation clock. Table 18.1 lists the Timer RC Operation Clock.

### Table 18.1 Timer RC Operation Clock

| Condition                                                                  | Timer RC Operation Clock |

|----------------------------------------------------------------------------|--------------------------|

| Count source is f1, f2, f4, f8, f32, or TRCCLK input (bits TCK2 to TCK0 in | f1                       |

| TRCCR1 register are set to a value from 000b to 101b)                      |                          |

| Count source is fOCO40M (bits TCK2 to TCK0 in TRCCR1 register are set      | fOCO40M                  |

| to 110b)                                                                   |                          |

| Count source is fOCO-F (bits TCK2 to TCK0 in TRCCR1 register are set to    | fOCO-F                   |

| 111b)                                                                      |                          |

Table 18.2 lists the Pin Configuration of Timer RC, and Figure 18.1 shows a Timer RC Block Diagram. Timer RC has three modes.

• Timer mode

| - Input capture function  | The counter value is captured to a register, using an external signal as the trigger. |

|---------------------------|---------------------------------------------------------------------------------------|

| - Output compare function | Matches between the counter and register values are detected. (Pin output state       |

|                           | changes when a match is detected.)                                                    |

The following two modes use the output compare function.

- PWM mode Pulses of a given width are output continuously.

- PWM2 mode A one-shot waveform or PWM waveform is output following the trigger after the wait time has elapsed.

Input capture function, output compare function, and PWM mode settings may be specified independently for each pin.

In PWM2 mode waveforms are output based on a combination of the counter or the register.

## 18.4.1 Timer RC I/O Control Register 0 (TRCIOR0) for Input Capture Function

| Ado     | dress 0124              | 1h                 |              |              |            |                     |                      |              |                 |         |     |

|---------|-------------------------|--------------------|--------------|--------------|------------|---------------------|----------------------|--------------|-----------------|---------|-----|

|         | Bit I                   | 57                 | b6           | b5           | b4         | b3                  | b2                   | b1           | b0              |         |     |

| Sy      | Symbol — IOB2 IOB1 IOB0 |                    |              | IOB0         | IOA3       | IOA2                | IOA1                 | IOA0         |                 |         |     |

| After F | Reset                   | 1                  | 0            | 0            | 0          | 1                   | 0                    | 0            | 0               |         |     |

| Bit     | Symbol                  | 1                  | Bit          | Name         |            | i                   |                      | Function     |                 |         | R/W |

| b0      | IOA0                    | TRCC               | RA contro    |              |            | b1 b0               |                      | i anotion    |                 |         | R/W |

| b1      | IOA1                    |                    | and Control  |              |            | rising              | edge                 |              | RA register at  |         | R/W |

|         |                         |                    |              |              |            |                     | capture to t<br>edge | the TRCG     | RA register at  | the     |     |

|         |                         |                    |              |              |            | 1 0: Input<br>edges | •                    | the TRCG     | RA register at  | both    |     |

|         |                         |                    |              |              |            | 1 1: Do no          |                      |              |                 |         |     |

| b2      | IOA2                    | TRCO               | RA mode      | select bit ( | [1]        | Set to 1 (ir        | put capture          | e) in the in | out capture fui | nction. | R/W |

| b3      | IOA3                    |                    | aRA input o  | capture inp  | out switch | 0: fOCO12           |                      |              |                 |         | R/W |

|         |                         | bit <sup>(3)</sup> |              |              |            | 1: TRCIOA           | A pin input          |              |                 |         |     |

| b4      | IOB0                    | TRCC               | RB contro    | l bit        |            | b5 b4               | oopturo to t         |              | DP register at  | the     | R/W |

| b5      | IOB1                    |                    |              |              |            |                     | edge                 |              | RB register at  | lite    | R/W |

|         |                         |                    |              |              |            |                     |                      | the TRCG     | RB register at  | the     |     |

|         |                         |                    |              |              |            |                     | , edge               |              | C               |         |     |

|         |                         |                    |              |              |            |                     | •                    | the TRCG     | RB register at  | both    |     |

|         |                         |                    |              |              |            | edges<br>1 1: Do no |                      |              |                 |         |     |

| b6      | IOB2                    | TDCC               |              | aalaat bit ( | (2)        |                     |                      | ) in the in  | out capture fu  | notion  | R/W |

|         | -                       |                    | RB mode      |              |            |                     | • •                  |              | •               |         |     |

| b7      | —                       | INOTHI             | ng is assigi | nea. It nec  | essary, se | t to 0. Whe         | n read, the          | content is   | 1.              |         | —   |

Notes:

1. When the BFC bit in the TRCMR register is set to 1 (buffer register of TRCGRA register), set the IOC2 bit in the TRCIOR1 register to the same value as the IOA2 bit in the TRCIOR0 register.

2. When the BFD bit in the TRCMR register is set to 1 (buffer register of TRCGRB register), set the IOD2 bit in the TRCIOR1 register to the same value as the IOB2 bit in the TRCIOR0 register.

3. The IOA3 bit is enabled when the IOA2 bit is set to 1 (input capture function).

### 21.2 Registers

### 21.2.1 UART2 Transmit/Receive Mode Register (U2MR)

| Address 00A8h              |       |        |              |              |           |                                                                                            |                       |             |                     |      |     |

|----------------------------|-------|--------|--------------|--------------|-----------|--------------------------------------------------------------------------------------------|-----------------------|-------------|---------------------|------|-----|

|                            | Bit   | b7     | b6           | b5           | b4        | b3                                                                                         | b2                    | b1          | b0                  |      |     |

| Symbol IOPOL PRYE PRY STPS |       | CKDIR  | SMD2         | SMD1         | SMD0      | ]                                                                                          |                       |             |                     |      |     |

| After Re                   | eset  | 0      | 0            | 0            | 0         | 0                                                                                          | 0                     | 0           | 0                   | 4    |     |

| Bit Symbol Bit Name        |       |        |              |              |           |                                                                                            | Function              |             |                     |      | R/W |

| b0                         | SMDC  | ) Ser  | ial I/O mod  | le select bi | t         | b2 b1 b0                                                                                   | 0                     | (           | la al               |      | R/W |

| b1                         | SMD1  | SMD1   |              |              |           |                                                                                            | Serial inter          |             | iea<br>erial I/O mo | odo  | R/W |

| b2                         | SMD2  | 2      |              |              |           |                                                                                            | l <sup>2</sup> C mode | monous se   |                     | Jue  | R/W |

|                            |       |        |              |              |           |                                                                                            |                       | le transfer | data 7 bits         | lona |     |

|                            |       |        |              |              |           | 1 0 0: UART mode, transfer data 7 bits long<br>1 0 1: UART mode, transfer data 8 bits long |                       |             | •                   |      |     |

|                            |       |        |              |              |           | 1 1 0: UART mode, transfer data 9 bits long                                                |                       |             |                     |      |     |

|                            |       |        |              |              |           | Other t                                                                                    | han above             | : Do not se | et.                 | -    |     |

| b3                         | CKDIF | R Inte | rnal/extern  | al clock se  | elect bit | 0: Inter                                                                                   | nal clock             |             |                     |      | R/W |

|                            |       |        |              |              |           | 1: Exte                                                                                    | rnal clock            |             |                     |      |     |

| b4                         | STPS  | 6 Sto  | o bit length | select bit   |           |                                                                                            | stop bit              |             |                     |      | R/W |

|                            |       |        |              |              |           |                                                                                            | stop bits             |             |                     |      |     |

| b5                         | PRY   | Ode    | d/even pari  | ty select b  | it        |                                                                                            | d when PR             | IYE = 1     |                     |      | R/W |

|                            |       |        |              |              |           | 0: Odd parity                                                                              |                       |             |                     |      |     |

|                            |       |        |              |              |           | 1: Ever                                                                                    |                       |             |                     |      |     |

| b6                         | PRYE  | E Par  | ity enable l | oit          |           |                                                                                            | y disabled            |             |                     |      | R/W |

|                            |       |        |              |              |           |                                                                                            | y enabled             |             |                     |      |     |

| b7                         | IOPOI |        | D, RXD I/O   | polarity sv  | witch bit | 001                                                                                        | inverted              |             |                     |      | R/W |

|                            |       |        |              |              |           | 1: Inve                                                                                    | rted                  |             |                     |      |     |

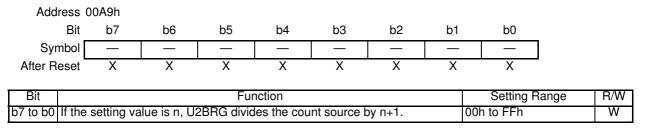

# 21.2.2 UART2 Bit Rate Register (U2BRG)

Write to the U2BRG register while transmission and reception stop. Use the MOV instruction to write to this register.

Set bits CLK1 to CLK0 in the U2C0 register before writing to the U2BRG register.

### 21.3.1 Measure for Dealing with Communication Errors

If communication is aborted or a communication error occurs while transmitting or receiving in clock synchronous serial I/O mode, follow the procedures below:

- (1) Set the TE bit in the U2C1 register to 0 (transmission disabled) and the RE bit to 0 (reception disabled).

- (2) Set bits SMD2 to SMD0 in the U2MR register to 000b (serial interface disabled).

- (3) Set bits SMD2 to SMD0 in the U2MR register to 001b (clock synchronous serial I/O mode).

- (4) Set the TE bit in the U2C1 register to 1 (transmission enabled) and the RE bit to 1 (reception enabled).

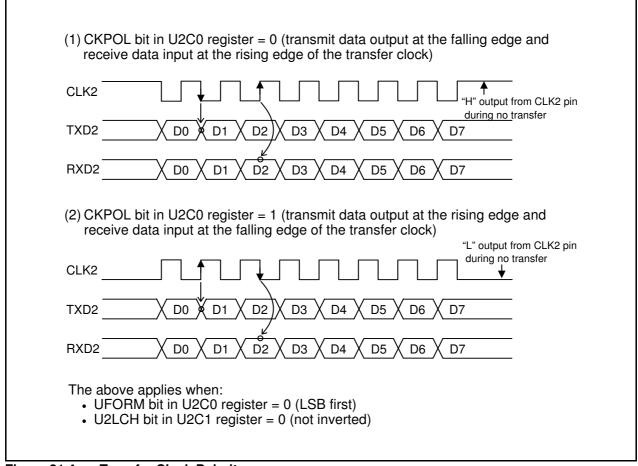

### 21.3.2 CLK Polarity Select Function

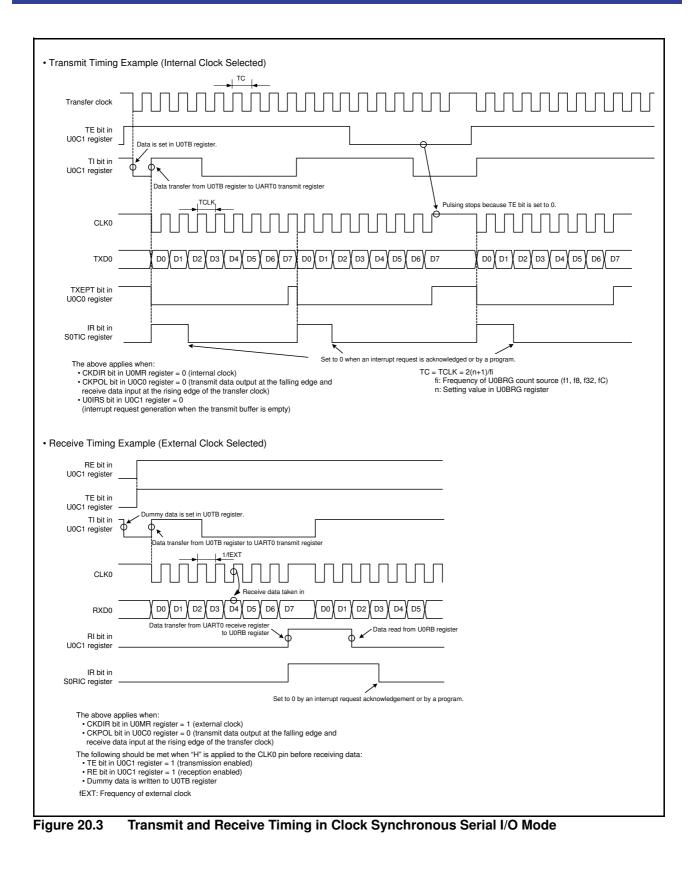

Use the CKPOL bit in the U2C0 register to select the transfer clock polarity. Figure 21.4 shows the Transfer Clock Polarity.

Figure 21.4 Transfer Clock Polarity

| Register | Bit                     | Function                                                        |                                                                           |  |  |  |  |  |

|----------|-------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------|--|--|--|--|--|

| negistei | DIL                     | Master                                                          | Slave                                                                     |  |  |  |  |  |

| U2SMR3   | b0, b2, b4, and<br>NODC | Set to 0.                                                       | Set to 0.                                                                 |  |  |  |  |  |

|          | СКРН                    | Refer to Table 21.12 I <sup>2</sup> C Mode Functions.           | Refer to Table 21.12 I <sup>2</sup> C Mode Functions.                     |  |  |  |  |  |

|          | DL2 to DL0              | Set the amount of SDA2 digital delay.                           | Set the amount of SDA2 digital delay.                                     |  |  |  |  |  |

| U2SMR4   | STAREQ                  | Set to 1 to generate a start condition.                         | Set to 0.                                                                 |  |  |  |  |  |

|          | RSTAREQ                 | Set to 1 to generate a restart condition.                       | Set to 0.                                                                 |  |  |  |  |  |

|          | STPREQ                  | Set to 1 to generate a stop condition.                          | Set to 0.                                                                 |  |  |  |  |  |

|          | STSPSEL                 | Set to 1 to output each condition.                              | Set to 0.                                                                 |  |  |  |  |  |

|          | ACKD                    | Select ACK or NACK.                                             | Select ACK or NACK.                                                       |  |  |  |  |  |

|          | ACKC                    | Set to 1 to output ACK data.                                    | Set to 1 to output ACK data.                                              |  |  |  |  |  |

|          | SCLHI                   | Set to 1 to stop SCL2 output when a stop condition is detected. | Set to 0.                                                                 |  |  |  |  |  |

|          | SWC9                    | Set to 0.                                                       | Set to 1 to hold SCL2 low at the falling<br>edge of the 9th bit of clock. |  |  |  |  |  |

| URXDF    | DF2EN                   | Set to 0.                                                       | Set to 0.                                                                 |  |  |  |  |  |

| U2SMR5   | MP                      | Set to 0.                                                       | Set to 0.                                                                 |  |  |  |  |  |

| Table 21.11 R | Registers Used | and Settings in | n I <sup>2</sup> C Mode (2) |

|---------------|----------------|-----------------|-----------------------------|

|---------------|----------------|-----------------|-----------------------------|

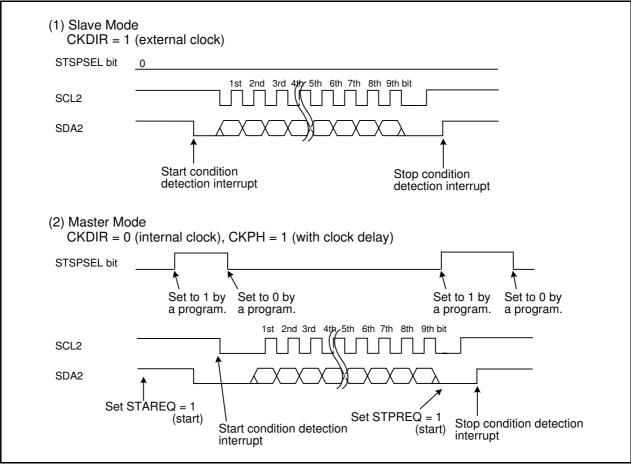

### 21.5.2 Output of Start and Stop Conditions

Table 21.13 STSPSEL Bit Functions

A start condition is generated by setting the STAREQ bit in the U2SMR4 register to 1 (start). A restart condition is generated by setting the RSTAREQ bit in the U2SMR4 register to 1 (start). A stop condition is generated by setting the STPREQ bit in the U2SMR4 register to 1 (start). The output procedure is as follows:

(1) Set the STAREQ bit, RSTAREQ bit or STPREQ bit to 1 (start).

(2) Set the STSPSEL bit in the U2SMR4 register to 1 (output).

Table 21.13 lists the STSPSEL Bit Functions. Figure 21.16 shows the STSPSEL Bit Functions.

| Function                                                       | STSPSEL = 0                                                                                                                                                      | STSPSEL = 1                                                                         |

|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| Output of pins SCL2<br>and SDA2                                | Output of transfer clock and data<br>Output of start/stop conditions is<br>accomplished by a program using ports<br>(not automatically generated in<br>hardware) | Output of start/stop conditions<br>according to bits STAREQ,<br>RSTAREQ, and STPREQ |

| Start/stop condition<br>interrupt request<br>generation timing | Detection of start/stop conditions                                                                                                                               | Completion of start/stop condition generation                                       |

Figure 21.16 STSPSEL Bit Functions

### 21.6.3 RXD2 Digital Filter Select Function

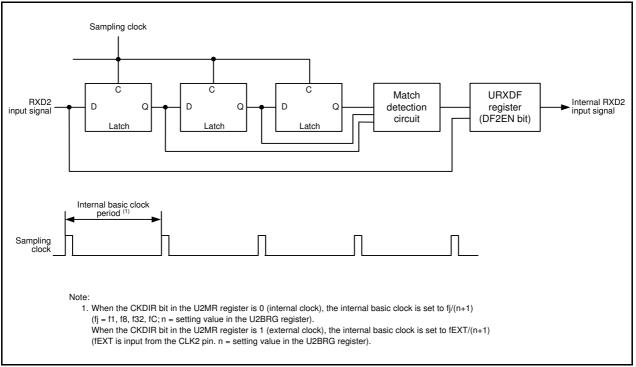

When the DF2EN bit in the URXDF register is set to 1 (RXD2 digital filer enabled), the RXD2 input signal is loaded internally via the digital filter circuit for noise reduction. The noise canceller consists of three cascaded latch circuits and a match detection circuit. The RXD2 input signal is sampled on the internal basic clock with a frequency 16 times the bit rate. It is recognized as a signal and the level is passed forward to the next circuit when three latch outputs match. When the outputs do not match, the previous value is retained.

In other words, when the level is changed within three clocks, the change is recognized as not a signal but noise. Figure 21.22 shows a Block Diagram of RXD2 Digital Filter Circuit.

Figure 21.22 Block Diagram of RXD2 Digital Filter Circuit

### 22.2 Registers

### 22.2.1 On-Chip Reference Voltage Control Register (OCVREFCR)

| Bit | Symbol | Bit Name                                                             | Function                                                                                                                                         | R/W |

|-----|--------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0  |        | On-chip reference voltage to analog input connect bit <sup>(1)</sup> | <ul> <li>On-chip reference voltage and analog input are cut off</li> <li>On-chip reference voltage and analog input are<br/>connected</li> </ul> | R/W |

| b1  | —      | Reserved bits                                                        | Set to 0.                                                                                                                                        | R/W |

| b2  |        |                                                                      |                                                                                                                                                  |     |

| b3  |        |                                                                      |                                                                                                                                                  |     |

| b4  | —      |                                                                      |                                                                                                                                                  |     |

| b5  |        |                                                                      |                                                                                                                                                  |     |

| b6  | —      |                                                                      |                                                                                                                                                  |     |

| b7  | —      |                                                                      |                                                                                                                                                  |     |

Note:

1. When on-chip reference voltage is used as analog input, first set the ADEX0 bit in the ADCON1 register to 1 (onchip reference voltage selected) and then set the OCVREFAN bit to 1 (on-chip reference voltage and analog input are connected).

When on-chip reference voltage is not used as analog input, first set the OCVREFAN bit to 0 (on-chip reference voltage and analog input are cut off) and then set the ADEX0 bit to 0 (extended analog input pin not selected).

Set the PRC3 bit in the PRCR register to 1 (write enabled) before rewriting the OCVREFCR register. If the contents of the OCVREFCR register are rewritten during A/D conversion, the conversion result is undefined.

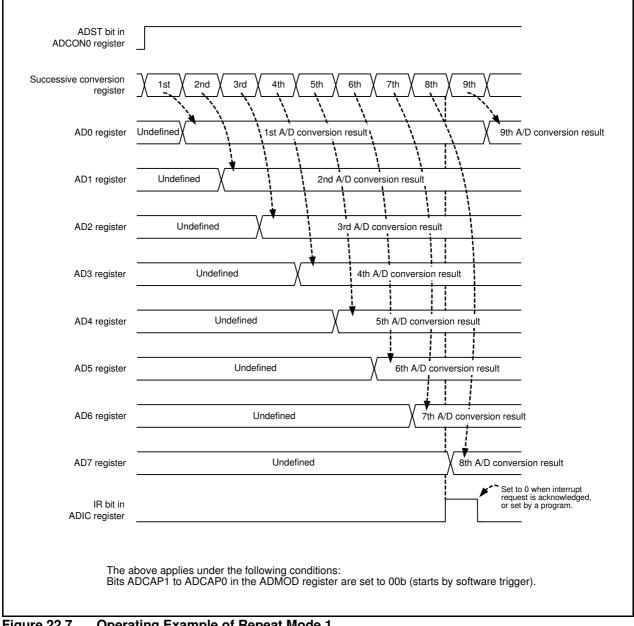

Figure 22.7 **Operating Example of Repeat Mode 1**

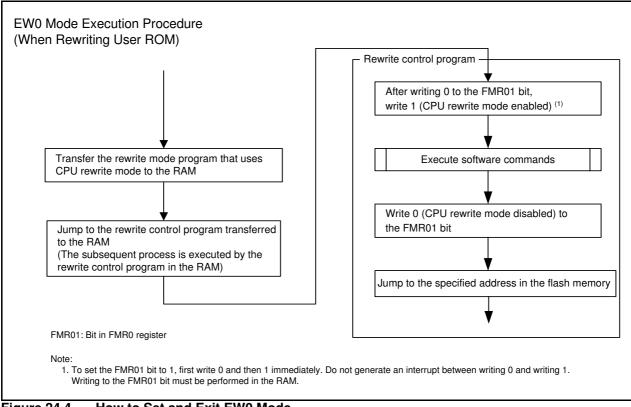

### 24.4.8 How to Set and Exit Each Mode

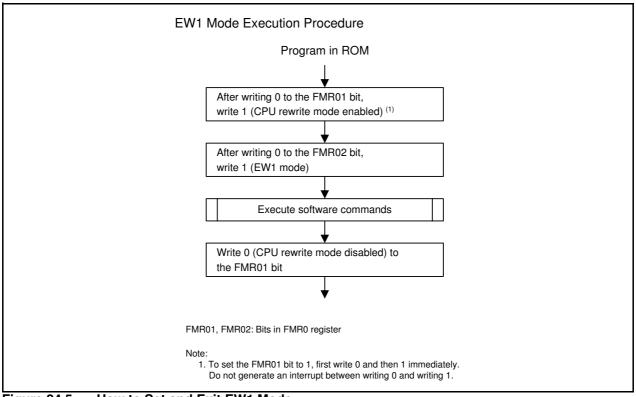

Figure 24.4 shows How to Set and Exit EW0 Mode and Figure 24.5 shows How to Set and Exit EW1 Mode.

Figure 24.4 How to Set and Exit EW0 Mode

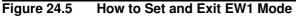

Figure 24.8 Program Flowchart (Flash Ready Status Interrupt Enabled)

| Symbol                      | Pa                  |                                                                                                     | ameter                 |                                    | Conditions                                                                                            | Standard |        |          | Unit |

|-----------------------------|---------------------|-----------------------------------------------------------------------------------------------------|------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------|----------|--------|----------|------|

| Symbol                      |                     | Par                                                                                                 | ameter                 |                                    | Conditions                                                                                            | Min.     | Тур.   | Max.     |      |

| Vcc/AVcc                    | Supply voltage      |                                                                                                     |                        |                                    |                                                                                                       | 1.8      | -      | 5.5      | V    |

| Vss/AVss                    | Supply voltage      |                                                                                                     |                        |                                    |                                                                                                       | -        | 0      | -        | V    |

| Vih                         | Input "H" voltage   | Other than                                                                                          | n CMOS inp             | ut                                 |                                                                                                       | 0.8 Vcc  | -      | Vcc      | V    |

|                             |                     | CMOS                                                                                                |                        | Input level selection              | $4.0~V \leq Vcc \leq 5.5~V$                                                                           | 0.5 Vcc  | -      | Vcc      | V    |

|                             |                     | input                                                                                               | switching              | : 0.35 Vcc                         | $2.7~V \leq V \text{CC} < 4.0~V$                                                                      | 0.55 Vcc | -      | Vcc      | V    |

|                             |                     |                                                                                                     | function               |                                    | $1.8~V \leq V \text{CC} < 2.7~V$                                                                      | 0.65 Vcc | -      | Vcc      | V    |

|                             |                     |                                                                                                     | (I/O port)             | Input level selection              | $4.0~V \leq V \text{CC} \leq 5.5~V$                                                                   | 0.65 Vcc | -      | Vcc      | V    |

|                             |                     |                                                                                                     |                        | : 0.5 Vcc                          | $2.7~V \leq V \text{CC} < 4.0~V$                                                                      | 0.7 Vcc  | -      | Vcc      | V    |

|                             |                     |                                                                                                     |                        |                                    | $1.8~V \leq V \text{CC} < 2.7~V$                                                                      | 0.8 Vcc  | -      | Vcc      | V    |

|                             |                     |                                                                                                     |                        | Input level selection              | $4.0~V \leq V \text{CC} \leq 5.5~V$                                                                   | 0.85 Vcc | -      | Vcc      | V    |

|                             |                     |                                                                                                     |                        | : 0.7 Vcc                          | $2.7 \text{ V} \le \text{Vcc} < 4.0 \text{ V}$                                                        | 0.85 Vcc | -      | Vcc      | V    |

|                             |                     |                                                                                                     |                        |                                    | $1.8 \text{ V} \le \text{Vcc} < 2.7 \text{ V}$                                                        | 0.85 Vcc | -      | Vcc      | V    |

|                             |                     | External c                                                                                          | lock input (X          | OUT)                               |                                                                                                       | 1.2      | _      | Vcc      | V    |

| VIL                         | Input "L" voltage   | Other than                                                                                          | n CMOS inp             | ut                                 |                                                                                                       | 0        | _      | 0.2 Vcc  | V    |

|                             |                     | CMOS                                                                                                | Input level            | Input level selection              | $4.0 \text{ V} \leq \text{Vcc} \leq 5.5 \text{ V}$                                                    | 0        | -      | 0.2 Vcc  | V    |

|                             |                     | input                                                                                               | switching              | : 0.35 Vcc                         | 2.7 V ≤ Vcc < 4.0 V                                                                                   | 0        | _      | 0.2 Vcc  | V    |

|                             |                     |                                                                                                     | function<br>(I/O port) |                                    | 1.8 V ≤ Vcc < 2.7 V                                                                                   | 0        | _      | 0.2 Vcc  | V    |

|                             |                     |                                                                                                     |                        | Input level selection<br>: 0.5 Vcc | $4.0 \text{ V} \leq \text{Vcc} \leq 5.5 \text{ V}$                                                    | 0        | -      | 0.4 Vcc  | V    |

|                             |                     |                                                                                                     |                        |                                    | 2.7 V ≤ Vcc < 4.0 V                                                                                   | 0        | -      | 0.3 Vcc  | V    |

|                             |                     |                                                                                                     |                        |                                    | 1.8 V ≤ Vcc < 2.7 V                                                                                   | 0        | _      | 0.2 Vcc  | V    |

|                             |                     |                                                                                                     |                        | Input level selection<br>: 0.7 Vcc | 4.0 V ≤ Vcc ≤ 5.5 V                                                                                   | 0        | _      | 0.55 Vcc | V    |

|                             |                     |                                                                                                     |                        |                                    | $2.7 \text{ V} \le \text{Vcc} < 4.0 \text{ V}$                                                        | 0        | _      | 0.45 Vcc | V    |

|                             |                     |                                                                                                     |                        |                                    | $1.8 \text{ V} \le \text{Vcc} < 2.7 \text{ V}$                                                        | 0        | _      | 0.35 Vcc | V    |

|                             |                     | External c                                                                                          | lock input (X          |                                    |                                                                                                       | 0        | -      | 0.4      | V    |

| IOH(sum)                    | Peak sum output "   |                                                                                                     |                        | pins IOH(peak)                     |                                                                                                       | -        | _      | -160     | mA   |

| IOH(sum)                    | Average sum output  |                                                                                                     |                        | pins IOH(avg)                      |                                                                                                       | _        | _      | -80      | mA   |

| IOH(peak)                   | Peak output "H" ci  |                                                                                                     | Drive capa             |                                    |                                                                                                       | _        | _      | -10      | mA   |

| - (i <sup>,</sup> - · · · ) |                     |                                                                                                     | Drive capa             | -                                  |                                                                                                       | _        | _      | -40      | mA   |

| IOH(avg)                    | Average output "H   | l" current                                                                                          | Drive capa             |                                    |                                                                                                       | _        | _      | -5       | mA   |

|                             |                     |                                                                                                     | Drive capa             |                                    |                                                                                                       | _        | _      | -20      | mA   |

| IOL(sum)                    | Peak sum output '   | L" current                                                                                          | -                      | pins IOL(peak)                     |                                                                                                       | _        | _      | 160      | mA   |

| IOL(sum)                    | Average sum output  |                                                                                                     |                        | pins IOL(avg)                      |                                                                                                       | _        | _      | 80       | mA   |

| IOL(peak)                   | Peak output "L" cu  |                                                                                                     | Drive capa             |                                    |                                                                                                       | _        | _      | 10       | mA   |

| 102(pourt)                  |                     |                                                                                                     | Drive capa             | -                                  |                                                                                                       | _        | _      | 40       | mA   |

| IOL(avg)                    | Average output "L   | " current                                                                                           | Drive capa             |                                    |                                                                                                       | _        | _      | 5        | mA   |

| ioc(aig)                    |                     | ourront                                                                                             | Drive capa             | -                                  |                                                                                                       | _        | _      | 20       | mA   |

| f(XIN)                      | XIN clock input os  | cillation free                                                                                      |                        |                                    | 2.7 V ≤ Vcc ≤ 5.5 V                                                                                   |          |        | 20       | MHz  |

|                             |                     |                                                                                                     | 1.0.109                |                                    | $1.8 \text{ V} \le \text{Vcc} < 2.7 \text{ V}$                                                        | _        |        | 5        | MHz  |

| f(XCIN)                     | XCIN clock input of | scillation fr                                                                                       | equency                |                                    | $1.8 V \le VCC \le 2.7 V$<br>$1.8 V \le VCC \le 5.5 V$                                                | _        | 32.768 | 50       | kHz  |

| fOCO40M                     |                     | XCIN clock input oscillation frequency<br>When used as the count source for timer RC <sup>(3)</sup> |                        |                                    |                                                                                                       | 32       |        | 40       | MHz  |

| fOCO-F                      | fOCO-F frequency    |                                                                                                     |                        | <u>\-</u> /                        | $2.7 \text{ V} \leq \text{Vcc} \leq 5.5 \text{ V}$ $2.7 \text{ V} \leq \text{Vcc} \leq 5.5 \text{ V}$ |          |        | 20       | MHz  |

| 1000-F                      |                     | 1                                                                                                   |                        |                                    | $1.8 \text{ V} \le \text{VCC} \le 5.5 \text{ V}$                                                      | -        |        | 20<br>5  | MHz  |

| _                           | System clock from   |                                                                                                     |                        |                                    | $1.8 V \le VCC < 2.7 V$<br>$2.7 V \le VCC \le 5.5 V$                                                  | -        | _      | 5<br>20  |      |

| -                           | System clock freq   | uency                                                                                               |                        |                                    | $2.7 V \le VCC \le 5.5 V$<br>1.8 V $\le VCC < 2.7 V$                                                  | -        | _      | 20<br>5  | MHz  |

| frontin                     | CPU clock freque    | 201                                                                                                 |                        |                                    | $1.8 V \le VCC < 2.7 V$<br>2.7 V $\le Vcc \le 5.5 V$                                                  | -        | _      |          | MHz  |

| f(BCLK)                     |                     | icy                                                                                                 |                        |                                    |                                                                                                       | -        | -      | 20<br>5  | MHz  |

|                             |                     |                                                                                                     |                        |                                    | $1.8~V \leq V \text{CC} < 2.7~V$                                                                      | -        | -      | 5        | MHz  |

| Table 26.2 | Recommended | Operating | Conditions |

|------------|-------------|-----------|------------|

|------------|-------------|-----------|------------|

Notes:

1. Vcc = 1.8 to 5.5 V at  $T_{opr}$  = -20 to 85°C (N version) / -40 to 85°C (D version), unless otherwise specified.

2. The average output current indicates the average value of current measured during 100 ms.

3. fOCO40M can be used as the count source for timer RC in the range of Vcc = 2.7 V to 5.5V.