Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | R8C                                                                              |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 20MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, LINbus, SIO, SSU, UART/USART                                   |

| Peripherals                | POR, PWM, Voltage Detect, WDT                                                    |

| Number of I/O              | 15                                                                               |

| Program Memory Size        | 16KB (16K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 1.5К х 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                      |

| Data Converters            | A/D 4x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 20-LSSOP (0.173", 4.40mm Width)                                                  |

| Supplier Device Package    | 20-LSSOP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f21324ddsp-u0 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 5.7    | Cold Start-Up/Warm Start-Up Determination Function  |     |

|--------|-----------------------------------------------------|-----|

| 5.8    | Reset Source Determination Function                 |     |

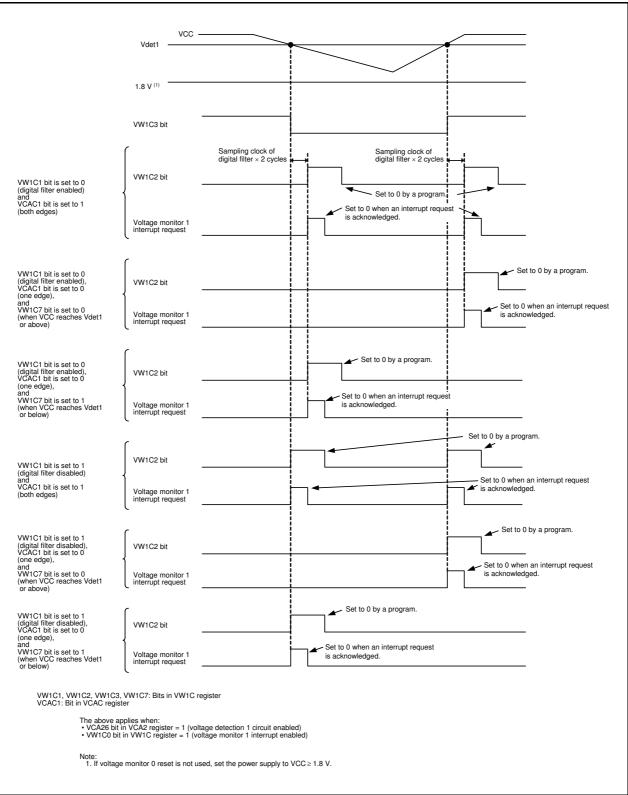

| 6. Vo  | Itage Detection Circuit                             | 33  |

| 6.1    | Overview                                            |     |

| 6.2    | Registers                                           |     |

| 6.2.1  | Voltage Monitor Circuit Control Register (CMPA)     |     |

| 6.2.2  | Voltage Monitor Circuit Edge Select Register (VCAC) |     |

| 6.2.3  | Voltage Detect Register 1 (VCA1)                    |     |

| 6.2.4  | Voltage Detect Register 2 (VCA2)                    |     |

| 6.2.5  | Voltage Detection 1 Level Select Register (VD1LS)   |     |

| 6.2.6  | Voltage Monitor 0 Circuit Control Register (VW0C)   |     |

| 6.2.7  | Voltage Monitor 1 Circuit Control Register (VW1C)   |     |

| 6.2.8  | Voltage Monitor 2 Circuit Control Register (VW2C)   |     |

| 6.2.9  | Option Function Select Register (OFS)               |     |

| 6.3    | VCC Input Voltage                                   |     |

| 6.3.1  | Monitoring Vdet0                                    |     |

| 6.3.2  | Monitoring Vdet1                                    |     |

| 6.3.3  | Monitoring Vdet2                                    |     |

| 6.4    | Voltage Monitor 0 Reset                             |     |

| 6.5    | Voltage Monitor 1 Interrupt                         |     |

| 6.6    | Voltage Monitor 2 Interrupt                         |     |

|        |                                                     | - 4 |

|        | ) Ports                                             |     |

| 7.1    | Functions of I/O Ports                              |     |

| 7.2    | Effect on Peripheral Functions                      |     |

| 7.3    | Pins Other than I/O Ports                           |     |

| 7.4    | Registers                                           |     |

| 7.4.1  | Port Pi Direction Register (PDi) (i = 1, 3, 4)      |     |

| 7.4.2  | Port Pi Register (Pi) $(i = 1, 3, 4)$               |     |

| 7.4.3  | Timer RA Pin Select Register (TRASR)                |     |

| 7.4.4  | Timer RC Pin Select Register (TRBRCSR)              |     |

| 7.4.5  | Timer RC Pin Select Register 0 (TRCPSR0)            |     |

| 7.4.6  | Timer RC Pin Select Register 1 (TRCPSR1)            |     |

| 7.4.7  | UARTO Pin Select Register (UOSR)                    |     |

| 7.4.8  | UART2 Pin Select Register 0 (U2SR0)                 |     |

| 7.4.9  | UART2 Pin Select Register 1 (U2SR1)                 |     |

| 7.4.10 |                                                     |     |

| 7.4.11 |                                                     |     |

| 7.4.12 | - <b>i</b>                                          |     |

| 7.4.13 |                                                     |     |

| 7.4.14 |                                                     |     |

| 7.4.15 |                                                     |     |

| 7.4.16 |                                                     |     |

| 7.4.17 |                                                     |     |

| 7.4.18 |                                                     |     |

| 7.5    | Port Settings                                       |     |

| 7.6    | Unassigned Pin Handling                             |     |

#### 1.5 **Pin Functions**

Table 1.5 lists Pin Functions.

#### Table 1.5 **Pin Functions**

| Item                         | Pin Name                                             | I/O Type | Description                                                                                                                                                                                                               |

|------------------------------|------------------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power supply input           | VCC, VSS                                             | -        | Apply 1.8 V to 5.5 V to the VCC pin. Apply 0 V to the VSS pin.                                                                                                                                                            |

| Analog power<br>supply input | AVCC, AVSS                                           | _        | Power supply for the A/D converter.<br>Connect a capacitor between AVCC and AVSS.                                                                                                                                         |

| Reset input                  | RESET                                                | 1        | Input "L" on this pin resets the MCU.                                                                                                                                                                                     |

| MODE                         | MODE                                                 | I        | Connect this pin to VCC via a resistor.                                                                                                                                                                                   |

| XIN clock input              | XIN                                                  | I        | These pins are provided for XIN clock generation circuit I/O.<br>Connect a ceramic resonator or a crystal oscillator between                                                                                              |

| XIN clock output             | XOUT                                                 | I/O      | the XIN and XOUT pins <sup>(1)</sup> . To use an external clock, input it to the XOUT pin and leave the XIN pin open.                                                                                                     |

| XCIN clock input             | XCIN                                                 | I        | These pins are provided for XCIN clock generation circuit I/O.<br>Connect a crystal oscillator between the XCIN and XCOUT                                                                                                 |

| XCIN clock output            | XCOUT                                                | 0        | pins <sup>(1)</sup> . To use an external clock, input it to the XCIN pin and leave the XCOUT pin open.                                                                                                                    |

| INT interrupt input          | INTO, INT1, INT3                                     | I        | INT interrupt input pins.<br>INT0 is timer RB, and RC input pin.                                                                                                                                                          |

| Key input interrupt          | KI0 to KI3                                           | I        | Key input interrupt input pins                                                                                                                                                                                            |

| Timer RA                     | TRAIO                                                | I/O      | Timer RA I/O pin                                                                                                                                                                                                          |

|                              | TRAO                                                 | 0        | Timer RA output pin                                                                                                                                                                                                       |

| Timer RB                     | TRBO                                                 | 0        | Timer RB output pin                                                                                                                                                                                                       |

| Timer RC                     | TRCCLK                                               | I        | External clock input pin                                                                                                                                                                                                  |

|                              | TRCTRG                                               | 1        | External trigger input pin                                                                                                                                                                                                |

|                              | TRCIOA, TRCIOB,<br>TRCIOC, TRCIOD                    | I/O      | Timer RC I/O pins                                                                                                                                                                                                         |

| Serial interface             | CLK0, CLK2                                           | I/O      | Transfer clock I/O pins                                                                                                                                                                                                   |

|                              | RXD0, RXD2                                           | I        | Serial data input pins                                                                                                                                                                                                    |

|                              | TXD0, TXD2                                           | 0        | Serial data output pins                                                                                                                                                                                                   |

|                              | CTS2                                                 | I.       | Transmission control input pin                                                                                                                                                                                            |

|                              | RTS2                                                 | 0        | Reception control output pin                                                                                                                                                                                              |

|                              | SCL2                                                 | I/O      | I <sup>2</sup> C mode clock I/O pin                                                                                                                                                                                       |

|                              | SDA2                                                 | I/O      | I <sup>2</sup> C mode data I/O pin                                                                                                                                                                                        |

| Reference voltage input      | VREF                                                 | I        | Reference voltage input pin to A/D converter                                                                                                                                                                              |

| A/D converter                | AN8 to AN11                                          | I        | Analog input pins to A/D converter                                                                                                                                                                                        |

|                              | ADTRG                                                | I        | A/D external trigger input pin                                                                                                                                                                                            |

| Comparator B                 | IVCMP1, IVCMP3                                       | I        | Comparator B analog voltage input pins                                                                                                                                                                                    |

|                              | IVREF1, IVREF3                                       | I        | Comparator B reference voltage input pins                                                                                                                                                                                 |

| I/O port                     | P1_0 to P1_7,<br>P3_3 to P3_5, P3_7,<br>P4_5 to P4_7 | I/O      | CMOS I/O ports. Each port has an I/O select direction<br>register, allowing each pin in the port to be directed for input<br>or output individually.<br>Any port set to input can be set to use a pull-up resistor or not |

|                              |                                                      |          | by a program.<br>All ports can be used as LED drive ports.                                                                                                                                                                |

| Input port                   | P4 2                                                 |          | Input-only port                                                                                                                                                                                                           |

I: Input Note:

1. Refer to the oscillator manufacturer for oscillation characteristics.

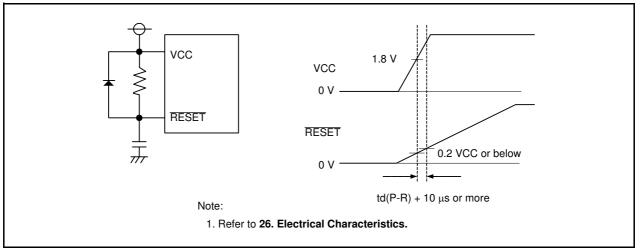

Figure 5.4 Example of Hardware Reset Circuit and Operation

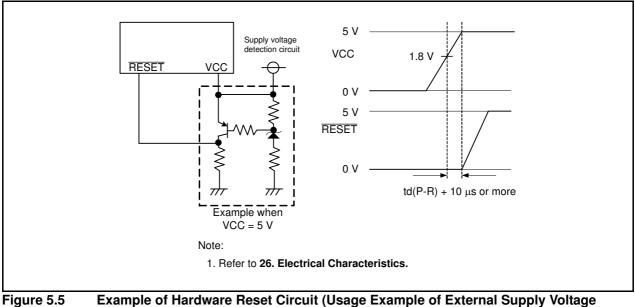

Figure 5.5 Example of Hardware Reset Circuit (Usage Example of External Supply Vo Detection Circuit) and Operation

#### 9.2.4 Oscillation Stop Detection Register (OCD)

| Address     | 000Ch |    |    |    |      |      |      |      |

|-------------|-------|----|----|----|------|------|------|------|

| Bit         | b7    | b6 | b5 | b4 | b3   | b2   | b1   | b0   |

| Symbol      |       |    | —  |    | OCD3 | OCD2 | OCD1 | OCD0 |

| After Reset | 0     | 0  | 0  | 0  | 0    | 1    | 0    | 0    |

| Bit | Symbol | Bit Name                                             | Function                                                                                                         | R/W |

|-----|--------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----|

| b0  | OCD0   | Oscillation stop detection enable bit <sup>(6)</sup> | 0: Oscillation stop detection function disabled <sup>(1)</sup><br>1: Oscillation stop detection function enabled | R/W |

| b1  | OCD1   | Oscillation stop detection interrupt<br>enable bit   | 0: Disabled <sup>(1)</sup><br>1: Enabled                                                                         | R/W |

| b2  | OCD2   | System clock select bit <sup>(3)</sup>               | 0: XIN clock selected <sup>(6)</sup><br>1: On-chip oscillator clock selected <sup>(2)</sup>                      | R/W |

| b3  | OCD3   | Clock monitor bit <sup>(4, 5)</sup>                  | 0: XIN clock oscillates<br>1: XIN clock stops                                                                    | R   |

| b4  | —      | Reserved bits                                        | Set to 0.                                                                                                        | R/W |

| b5  | —      | ]                                                    |                                                                                                                  |     |

| b6  | —      | ]                                                    |                                                                                                                  |     |

| b7  | —      | ]                                                    |                                                                                                                  |     |

Notes:

- 1. Set bits OCD1 to OCD0 to 00b before the MCU enters stop mode, high-speed on-chip oscillator mode, or lowspeed on-chip oscillator mode (XIN clock stops).

- 2. If the OCD2 bit is set to 1 (on-chip oscillator clock selected), the CM14 bit is set to 0 (low-speed on-chip oscillator on).

- 3. The OCD2 bit is automatically set to 1 (on-chip oscillator clock selected) if XIN clock oscillation stop is detected while bits OCD1 to OCD0 are set to 11b. If the OCD3 bit is set to 1 (XIN clock stops), the OCD2 bit remains unchanged even when set to 0 (XIN clock selected).

- 4. The OCD3 bit is enabled when the OCD0 bit is set to 1 (oscillation stop detection function enabled).

- 5. The OCD3 bit remains 0 (XIN clock oscillates) if bits OCD1 to OCD0 are set to 00b.

- 6. Refer to Figure 9.10 Procedure for Switching Clock Source from Low-Speed On-Chip Oscillator to XIN Clock for the switching procedure when the XIN clock re-oscillates after detecting oscillation stop.

Set the PRC0 bit in the PRCR register to 1 (write enabled) before rewriting the OCD register.

### 9.2.5 High-Speed On-Chip Oscillator Control Register 7 (FRA7)

| Address     | Address 0015h |               |    |    |    |    |    |    |  |

|-------------|---------------|---------------|----|----|----|----|----|----|--|

| Bit         | b7            | b6            | b5 | b4 | b3 | b2 | b1 | b0 |  |

| Symbol      |               | —             | —  | —  | —  | —  | —  |    |  |

| After Reset |               | When shipping |    |    |    |    |    |    |  |

| Ĩ | Bit   | Function                                                                                                                                                          | R/W |

|---|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Î | b7-b0 | 32 MHz frequency correction data is stored.                                                                                                                       | R   |

|   |       | The frequency can be adjusted by transferring this value to the FRA3 register and by transferring the correction value in the FRA6 register to the FRA1 register. |     |

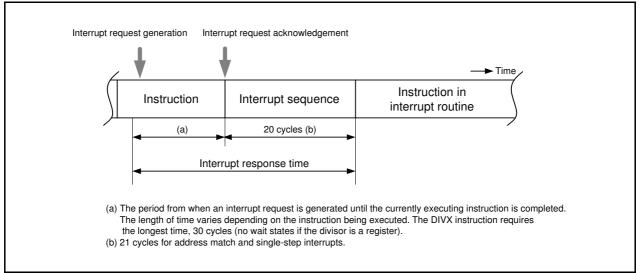

#### 11.3.5 Interrupt Response Time

Figure 11.4 shows the Interrupt Response Time. The interrupt response time is the period from when an interrupt request is generated until the first instruction in the interrupt routine is executed. The interrupt response time includes the period from when an interrupt request is generated until the currently executing instruction is completed (refer to (a) in Figure 11.4) and the period required for executing the interrupt sequence (20 cycles, refer to (b) in Figure 11.4).

Figure 11.4 Interrupt Response Time

#### 11.3.6 IPL Change when Interrupt Request is Acknowledged

When a maskable interrupt request is acknowledged, the interrupt priority level of the acknowledged interrupt is set in the IPL.

When a software interrupt or special interrupt request is acknowledged, the level listed in Table 11.5 is set in the IPL.

Table 11.5 lists the IPL Value When Software or Special Interrupt is Acknowledged.

#### Table 11.5 IPL Value When Software or Special Interrupt is Acknowledged

| Interrupt Source without Interrupt Priority Level              | Value Set in IPL |

|----------------------------------------------------------------|------------------|

| Watchdog timer, oscillation stop detection, voltage monitor 1, | 7                |

| voltage monitor 2, address break                               |                  |

| Software, address match, single-step                           | Not changed      |

#### 11.6 Address Match Interrupt

An address match interrupt request is generated immediately before execution of the instruction at the address indicated by the RMADi register (i = 0 or 1). This interrupt is used as a break function by the debugger. When the on-chip debugger is used, do not set an address match interrupt (registers AIER, RMAD0, and RMAD1, and fixed vector tables) in the user system.

Set the starting address of any instruction in the RMADi register (i = 0 or 1). Bits AIER0 and AIER1 in the AIER register can be used to select enable or disable the interrupt. The address match interrupt is not affected by the I flag and IPL.

The PC value (Refer to **11.3.7 Saving Registers**) which is saved on the stack when an address match interrupt request is acknowledged varies depending on the instruction at the address indicated by the RMADi register. (The appropriate return address is not saved on the stack.) When returning from the address match interrupt, follow one of the following means:

- Rewrite the contents of the stack and use the REIT instruction to return.

- Use an instruction such as POP to restore the stack to its previous state before the interrupt request was acknowledged. Then use a jump instruction to return.

Table 11.8 lists the PC Value Saved on Stack When Address Match Interrupt Request is Acknowledged and Table 11.9 lists the Correspondence Between Address Match Interrupt Sources and Associated Registers.

#### Table 11.8 PC Value Saved on Stack When Address Match Interrupt Request is Acknowledged

|                                 | Address Inc    | PC Value Saved (1)   |            |          |            |                      |

|---------------------------------|----------------|----------------------|------------|----------|------------|----------------------|

| <ul> <li>Instruction</li> </ul> | with 2-byte op | peration coo         | de (2)     |          |            | Address indicated by |

| <ul> <li>Instruction</li> </ul> | with 1-byte op | peration coo         | de (2)     |          |            | RMADi register + 2   |

| ADD.B:S                         | #IMM8,dest     | SUB.B:S              | #IMM8,dest | AND.B:S  | #IMM8,dest | Ū.                   |

| OR.B:S                          | #IMM8,dest     | MOV.B:S              | #IMM8,dest | STZ      | #IMM8,dest |                      |

| STNZ                            | #IMM8,dest     | STZX                 | #IMM81,#IM | M82,dest |            |                      |

| CMP.B:S                         | #IMM8,dest     | PUSHM                | src        | POPM     | dest       |                      |

| JMPS                            | #IMM8          | JSRS                 | #IMM8      |          |            |                      |

| MOV.B:S                         | #IMM,dest (h   |                      |            |          |            |                      |

| Instructions                    | other than ab  | Address indicated by |            |          |            |                      |

|                                 |                |                      |            |          |            | RMADi register + 1   |

Notes:

#### 1. Refer to the 11.3.7 Saving Registers.

2. Operation code: Refer to the R8C/Tiny Series Software Manual (REJ09B0001).

**Chapter 4. Instruction Code/Number of Cycles** contains diagrams showing operation code below each syntax. Operation code is shown in the bold frame in the diagrams.

| Table 11.9 | Correspondence Betweer | n Address Match Interru | pt Sources and Associated Registers |

|------------|------------------------|-------------------------|-------------------------------------|

|------------|------------------------|-------------------------|-------------------------------------|

| Address Match Interrupt Source | Address Match Interrupt Enable Bit | Address Match Interrupt Register |

|--------------------------------|------------------------------------|----------------------------------|

| Address match interrupt 0      | AIER0                              | RMAD0                            |

| Address match interrupt 1      | AIER1                              | RMAD1                            |

#### 17.5.3 One-Shot Trigger Selection

In programmable one-shot generation mode and programmable wait one-shot generation mode, operation starts when a one-shot trigger is generated while the TCSTF bit in the TRBCR register is set to 1 (count starts).

- A one-shot trigger can be generated by either of the following causes:

- 1 is written to the TOS<u>ST bit in the TRBOCR register by a program.</u>

- Trigger input from the  $\overline{INT0}$  pin.

When a one-shot trigger occurs, the TOSSTF bit in the TRBOCR register is set to 1 (one-shot operation in progress) after one or two cycles of the count source have elapsed. Then, in programmable one-shot generation mode, count operation begins and one-shot waveform output starts. (In programmable wait one-shot generation mode, count operation starts for the wait period.) If a one-shot trigger occurs while the TOSSTF bit is set to 1, no retriggering occurs.

To use trigger input from the INTO pin, input the trigger after making the following settings:

- Set the PD4\_5 bit in the PD4 register to 0 (input port).

- Select the INTO digital filter with bits INTOF1 and INTOF0 in the INTF register.

- Select both edges or one edge with the INTOPL bit in INTEN register. If one edge is selected, further select falling or rising edge with the INOSEG bit in TRBIOC register.

- Set the INT0EN bit in the INTEN register to 1 (enabled).

- After completing the above, set the INOSTG bit in the TRBIOC register to 1 (INT0 pin one-shot trigger enabled).

Note the following points with regard to generating interrupt requests by trigger input from the INTO pin.

- Processing to handle the interrupts is required. Refer to 11. Interrupts, for details.

- If one edge is selected, use the POL bit in the INTOIC register to select falling or rising edge. (The INOSEG bit in the TRBIOC register does not affect INTO interrupts).

- If a one-shot trigger occurs while the TOSSTF bit is set to 1, timer RB operation is not affected, but the value of the IR bit in the INTOIC register changes.

b5

b6 b7 R/W

### 18.2.15 Timer RC Pin Select Register 0 (TRCPSR0)

| Add     | dress | 0182h  |            |             |                     |                                      |                               |        |            |     |

|---------|-------|--------|------------|-------------|---------------------|--------------------------------------|-------------------------------|--------|------------|-----|

|         | Bit   | b7     | b6         | b5          | b4                  | b3                                   | b2                            | b1     | b0         |     |

| Sy      | mbol  |        |            |             | TRCIOBSEL0          | —                                    |                               | —      | TRCIOASEL0 |     |

| After F | Reset | 0      | 0          | 0           | 0                   | 0                                    | 0                             | 0      | 0          |     |

|         |       |        |            |             |                     |                                      |                               |        |            |     |

| Bit     | Sy    | ymbol  |            | Bit Name    |                     |                                      | Function                      |        |            |     |

| b0      | TRCI  | OASEL0 | TRCIOA/T   | RCTRG p     | oin select bit      | 0: TR0                               | 0: TRCIOA/TRCTRG pin not used |        |            |     |

|         |       |        |            |             |                     | 1: P1_                               |                               |        |            |     |

| b1      |       | _      | Reserved I | oits        |                     | Set to 0.                            |                               |        |            | R/W |

| b2      |       |        |            |             |                     |                                      |                               |        |            |     |

| b3      |       |        | Nothing is | assigned.   | . If necessary, set | t to 0. When read, the content is 0. |                               |        |            | —   |

| b4      | TRCI  | OBSEL0 | TRCIOB pi  | in select b | bit                 | 0: TR0                               | CIOB pin not                  | t used |            | R/W |

The TRCPSR0 register selects which pin is assigned to the timer RC I/O. To use the I/O pin for timer RC, set this register.

Nothing is assigned. If necessary, set to 0. When read, the content is 0.

1: P1\_2 assigned

Set to 0.

Set the TRCPSR0 register before setting the timer RC associated registers. Also, do not change the setting value in this register during timer RC operation.

### 18.2.16 Timer RC Pin Select Register 1 (TRCPSR1)

Reserved bits

| Ade      | dress | 0183h            |          |                 |                  |                                     |                                                                                          |              |         |            |  |

|----------|-------|------------------|----------|-----------------|------------------|-------------------------------------|------------------------------------------------------------------------------------------|--------------|---------|------------|--|

|          | Bit   | b7               | b6       | b5              | b4               | b3                                  | b2                                                                                       | b1 b0        |         |            |  |

| Sy       | /mbol | _                | —        | TRCIODSEL1      | TRCIODSEL0       | —                                   | —                                                                                        | TRCIOCSEL1   | TRCIOCS | EL0        |  |

| After F  | Reset | 0                | 0        | 0               | 0                | 0                                   | 0                                                                                        | 0            | 0       |            |  |

| Bit      | S     | /mbol            |          | Bit Name        |                  |                                     | Fu                                                                                       | inction      |         | R/W        |  |

| b0       | TRCI  | OCSEL0           | TRCIOC p | oin select bit  |                  |                                     | C nin not                                                                                | used         |         | R/W        |  |

| b1       | TRCI  | OCSEL1           |          |                 |                  |                                     | 0 0: TRCIOC pin not used<br>0 1: P1_3 assigned<br>1 0: P3_4 assigned<br>1 1: Do not set. |              |         |            |  |

| b2       |       | _                | Reserved |                 |                  | Set to 0.                           |                                                                                          |              |         | R/W        |  |

| b3       |       | _                |          | assigned. If ne | ecessary, set to | o 0. When r                         | read, the c                                                                              | ontent is 0. |         | —          |  |

| b4<br>b5 |       | ODSEL0<br>ODSEL1 | TRCIOD p | in select bit   |                  | 0 0: TRCK<br>0 1: P1_0<br>1 0: P3_5 | assigned                                                                                 | used         |         | R/W<br>R/W |  |

b6

—

Reserved bit

Set to 0.

R/W

b7

—

Nothing is assigned. If necessary, set to 0. When read, the content is 0.

—

1 1: Do not set.

The TRCPSR1 register selects which pin is assigned to the timer RC I/O. To use the I/O pin for timer RC, set this register.

Set the TRCPSR1 register before setting the timer RC associated registers. Also, do not change the setting value in this register during timer RC operation.

#### 18.3.4 Forced Cutoff of Pulse Output

When using the timer mode's output compare function, the PWM mode, or the PWM2 mode, pulse output from the TRCIOj (j = A, B, C, or D) output pin can be forcibly cut off and the TRCIOj pin set to function as a programmable I/O port by means of input to the INTO pin.

A pin used for output by the timer mode's output compare function, the PWM mode, or the PWM2 mode can be set to function as the timer RC output pin by setting the Ej bit in the TRCOER register to 0 (timer RC output enabled). If "L" is input to the  $\overline{INT0}$  pin while the PTO bit in the TRCOER register is set to 1 (pulse output forced cutoff signal input  $\overline{INT0}$  enabled), bits EA, EB, EC, and ED in the TRCOER register are all set to 1 (timer RC output disabled, TRCIOj output pin functions as the programmable I/O port). When one or two cycles of the timer RC operation clock after "L" input to the  $\overline{INT0}$  pin (refer to **Table 18.1 Timer RC Operation Clock**) has elapsed, the TRCIOj output pin becomes a programmable I/O port.

Make the following settings to use this function.

- Set the pin state following forced cutoff of pulse output (high impedance (input), "L" output, or "H" output). (Refer to **7. I/O Ports**.)

- Set the INT0EN bit in the INTEN register to 1 (INT0 input enabled) and the INT0PL bit to 0 (one edge), and set the POL bit in the INT0IC register to 0 (falling edge selected).

- Set the PD4 5 bit in the PD4 register to 0 (input mode).

- Select the INTO digital filter by means of bits INTOF1 to INTOF0 in the INTF register.

- Set the PTO bit in the TRCOER register to 1 (pulse output forced cutoff signal input INTO enabled).

The IR bit in the INTOIC register is set to 1 (interrupt request) in accordance with the setting of the POL bit in the INTOIC register and the INTOPL bit in the INTEN register and a change in the INTO pin input (refer to **11.8** Notes on Interrupts).

For details on interrupts, refer to 11. Interrupts.

### 18.4.2 Timer RC I/O Control Register 1 (TRCIOR1) for Input Capture Function

| Address     | 0125h |      |      |      |      |      |      |      |

|-------------|-------|------|------|------|------|------|------|------|

| Bit         | b7    | b6   | b5   | b4   | b3   | b2   | b1   | b0   |

| Symbol      | IOD3  | IOD2 | IOD1 | IOD0 | IOC3 | IOC2 | IOC1 | IOC0 |

| After Reset | 1     | 0    | 0    | 0    | 1    | 0    | 0    | 0    |

|             |       |      |      |      |      |      |      |      |

| Bit      | Symbol       | Bit Name                               | Function                                                                                                                                                                                                                                                                     | R/W        |

|----------|--------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| b0<br>b1 | IOC0<br>IOC1 | TRCGRC control bit                     | <ul> <li>b1 b0</li> <li>0 0: Input capture to the TRCGRC register at the rising edge</li> <li>0 1: Input capture to the TRCGRC register at the falling edge</li> <li>1 0: Input capture to the TRCGRC register at both edges</li> <li>1 1: Do not set.</li> </ul>            | R/W<br>R/W |

| b2       | IOC2         | TRCGRC mode select bit <sup>(1)</sup>  | Set to 1 (input capture) in the input capture function.                                                                                                                                                                                                                      | R/W        |

| b3       | IOC3         | TRCGRC register function select bit    | Set to 1.                                                                                                                                                                                                                                                                    | R/W        |

| b4<br>b5 | IOD0<br>IOD1 | TRCGRD control bit                     | <ul> <li><sup>b5 b4</sup></li> <li>0 0: Input capture to the TRCGRD register at the rising edge</li> <li>0 1: Input capture to the TRCGRD register at the falling edge</li> <li>1 0: Input capture to the TRCGRD register at both edges</li> <li>1 1: Do not set.</li> </ul> | R/W<br>R/W |

| b6       | IOD2         | TRCGRD mode select bit <sup>(2)</sup>  | Set to 1 (input capture) in the input capture function.                                                                                                                                                                                                                      | R/W        |

| b7       | IOD3         | TRCGRD register function select<br>bit | Set to 1.                                                                                                                                                                                                                                                                    | R/W        |

Notes:

1. When the BFC bit in the TRCMR register is set to 1 (buffer register of TRCGRA register), set the IOC2 bit in the TRCIOR1 register to the same value as the IOA2 bit in the TRCIOR0 register.

2. When the BFD bit in the TRCMR register is set to 1 (buffer register of TRCGRB register), set the IOD2 bit in the TRCIOR1 register to the same value as the IOB2 bit in the TRCIOR0 register.

| Register | Setting | Register Function                                                 | Input Capture<br>Input Pin |

|----------|---------|-------------------------------------------------------------------|----------------------------|

| TRCGRA   | -       | General register. Can be used to read the TRC register value      | TRCIOA                     |

| TRCGRB   |         | at input capture.                                                 | TRCIOB                     |

| TRCGRC   | BFC = 0 | General register. Can be used to read the TRC register value      | TRCIOC                     |

| TRCGRD   | BFD = 0 | at input capture.                                                 | TRCIOD                     |

| TRCGRC   | BFC = 1 | Buffer registers. Can be used to hold transferred value from      | TRCIOA                     |

| TRCGRD   | BFD = 1 | the general register. (Refer to <b>18.3.2 Buffer Operation</b> .) | TRCIOB                     |

j = A, B, C, or D

BFC, BFD: Bits in TRCMR register

### 18.6.3 Operating Example

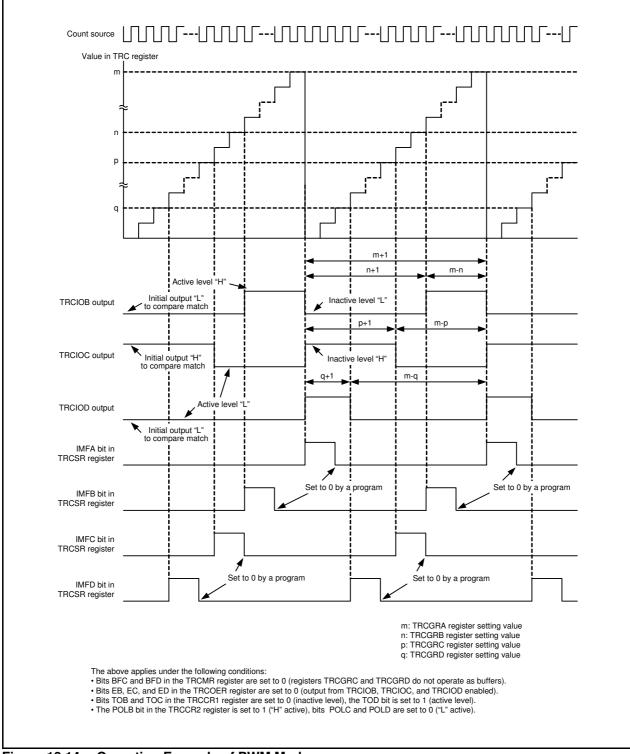

Figure 18.14 Operating Example of PWM Mode

# 19.2.5 Timer RE Control Register 1 (TRECR1) in Real-Time Clock Mode

| Address     | 011Ch  |         |    |        |     |    |       |    |

|-------------|--------|---------|----|--------|-----|----|-------|----|

| Bit         | b7     | b6      | b5 | b4     | b3  | b2 | b1    | b0 |

| Symbol      | TSTART | H12_H24 | PM | TRERST | INT |    | TCSTF |    |

| After Reset | 0      | 0       | 0  | 0      | 0   | 0  | 0     | 0  |

| Bit | Symbol  | Bit Name                       | Function                                                                                                                                                                                                                                                                                                                                          | R/W |

|-----|---------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0  | —       | Nothing is assigned. If necess | ary, set to 0. When read, the content is 0.                                                                                                                                                                                                                                                                                                       | —   |

| b1  | TCSTF   | Timer RE count status flag     | 0: Count stopped                                                                                                                                                                                                                                                                                                                                  | R   |

|     |         |                                | 1: Counting                                                                                                                                                                                                                                                                                                                                       |     |

| b2  | —       | Reserved bit                   | Set to 0.                                                                                                                                                                                                                                                                                                                                         | R/W |

| b3  | INT     | Interrupt request timing bit   | Set to 1 in real-time clock mode.                                                                                                                                                                                                                                                                                                                 | R/W |

| b4  | TRERST  | Timer RE reset bit             | <ul> <li>When setting this bit to 0, after setting it to 1, the followings will occur.</li> <li>Registers TRESEC, TREMIN, TREHR, TREWK, and TRECR2 are set to 00h.</li> <li>Bits TCSTF, INT, PM, H12_H24, and TSTART in the TRECR1 register are set to 0.</li> <li>The 8-bit counter is set to 00h and the 4-bit counter is set to 0h.</li> </ul> | R/W |

| b5  | РМ      | A.m./p.m. bit                  | When the H12_H24 bit is set to 0 (12-hour mode) <sup>(1)</sup><br>0: a.m.<br>1: p.m.<br>When the H12_H24 bit is set to 1 (24-hour mode), its value<br>is undefined.                                                                                                                                                                               | R/W |

| b6  | H12_H24 | Operating mode select bit      | 0: 12-hour mode<br>1: 24-hour mode                                                                                                                                                                                                                                                                                                                | R/W |

| b7  | TSTART  | Timer RE count start bit       | 0: Count stops<br>1: Count starts                                                                                                                                                                                                                                                                                                                 | R/W |

Note:

1. This bit is automatically modified while timer RE counts.

|                               |                                                              |         |         |    |           |          |          |      |                |       |        |    |    | on<br>I |    |      |      |    |    |

|-------------------------------|--------------------------------------------------------------|---------|---------|----|-----------|----------|----------|------|----------------|-------|--------|----|----|---------|----|------|------|----|----|

| Contents of<br>TREHR Register | H12_H24 bit = 1<br>(24-hour mode)                            | 0       | 1       | 2  | 3         | 4        | 5        | 6    | 7              | 8     | 9      | 10 | 11 | 12      | 13 | 14   | 15   | 16 | 17 |

|                               | H12_H24 bit = 0<br>(12-hour mode)                            | 0       | 1       | 2  | 3         | 4        | 5        | 6    | 7              | 8     | 9      | 10 | 11 | 0       | 1  | 2    | 3    | 4  | 5  |

| Contents of Pl                | V bit                                                        |         |         |    |           |          | 0 (a     | .m.) |                |       |        |    |    |         |    | 1 (p | .m.) |    |    |

| Contents in TRE               | EWK register                                                 |         |         |    |           |          |          |      | 0              | 00 (S | unda   | y) |    |         |    |      |      |    |    |

|                               |                                                              |         |         |    |           |          |          |      |                |       |        |    |    |         |    |      |      |    |    |

|                               |                                                              |         |         | 1  | 1         | 1        | ,        | /    |                | 1     |        |    |    |         |    |      |      |    |    |

| Contents of<br>TREHR Register | H12_H24 bit = 1<br>(24-hour mode)<br>H12_H24 bit = 0         | 18      | 19      | 20 | 21        | 22       | 23       | 0    | 1              | 2     | 3      |    |    |         |    |      |      |    |    |

| TREHR Register                | (24-hour mode)<br>H12_H24 bit = 0<br>(12-hour mode)          | 18<br>6 | 19<br>7 | 8  | 9         | 22<br>10 | 23<br>11 | 0    | 1              | 2     | 3<br>3 |    |    |         |    |      |      |    |    |

|                               | (24-hour mode)<br>H12_H24 bit = 0<br>(12-hour mode)<br>M bit | -       | 7       | 8  | 9<br>.m.) | 10       |          | 0    | 1<br>1<br>0 (a | 2     | 3      |    |    |         |    |      |      |    |    |

# Figure 19.2 Definition of Time Representation

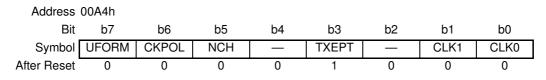

### 20.2.4 UART0 Transmit/Receive Control Register 0 (U0C0)

| Bit | Symbol | Bit Name                        | Function                                                                                                                                                                                                                                             | R/W |

|-----|--------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0  | CLK0   | BRG count source select bit (1) | 0 0: f1 selected                                                                                                                                                                                                                                     | R/W |

| b1  | CLK1   |                                 | 0 1: f8 selected                                                                                                                                                                                                                                     | R/W |

|     |        |                                 | 1 0: f32 selected                                                                                                                                                                                                                                    |     |

|     |        |                                 | 1 1: fC selected                                                                                                                                                                                                                                     |     |

| b2  | —      | Reserved bit                    | Set to 0.                                                                                                                                                                                                                                            | R/W |

| b3  | TXEPT  | Transmit register empty flag    | <ul><li>0: Data present in the transmit register<br/>(transmission in progress)</li><li>1: No data in the transmit register</li></ul>                                                                                                                | R   |

|     |        |                                 | (transmission completed)                                                                                                                                                                                                                             |     |

| b4  | _      | <b>C C C</b>                    | set to 0. When read, the content is 0.                                                                                                                                                                                                               | —   |

| b5  | NCH    | Data output select bit          | 0: TXD0 pin set to CMOS output<br>1: TXD0 pin set to N-channel open-drain output                                                                                                                                                                     | R/W |

| b6  | CKPOL  | CLK polarity select bit         | <ul> <li>0: Transmit data output at the falling edge and receive data input at the rising edge of the transfer clock</li> <li>1: Transmit data output at the rising edge and receive data input at the falling edge of the transfer clock</li> </ul> | R/W |

| b7  | UFORM  | Transfer format select bit      | 0: LSB first<br>1: MSB first                                                                                                                                                                                                                         | R/W |

Note:

1. If the BRG count source is switched, set the U0BRG register again.

## 20.2.5 UART0 Transmit/Receive Control Register 1 (U0C1)

| Address     | Address 00A5h |    |       |       |    |    |    |    |

|-------------|---------------|----|-------|-------|----|----|----|----|

| Bit         | b7            | b6 | b5    | b4    | b3 | b2 | b1 | b0 |

| Symbol      |               | _  | U0RRM | U0IRS | RI | RE | ΤI | TE |

| After Reset | 0             | 0  | 0     | 0     | 0  | 0  | 1  | 0  |

| Bit | Symbol | Bit Name                                                | Function                                                                       | R/W |

|-----|--------|---------------------------------------------------------|--------------------------------------------------------------------------------|-----|

| b0  | TE     | Transmit enable bit                                     | 0: Transmission disabled<br>1: Transmission enabled                            | R/W |

| b1  | TI     | Transmit buffer empty flag                              | 0: Data present in the U0TB register<br>1: No data in the U0TB register        | R   |

| b2  | RE     | Receive enable bit                                      | 0: Reception disabled<br>1: Reception enabled                                  | R/W |

| b3  | RI     | Receive complete flag (1)                               | 0: No data in the U0RB register<br>1: Data present in the U0RB register        | R   |

| b4  | U0IRS  | UART0 transmit interrupt source<br>select bit           | 0: Transmission buffer empty (TI = 1)<br>1: Transmission completed (TXEPT = 1) | R/W |

| b5  | UORRM  | UART0 continuous receive mode enable bit <sup>(2)</sup> | 0: Continuous receive mode disabled<br>1: Continuous receive mode enabled      | R/W |

| b6  | —      | Nothing is assigned. If necessary, se                   | t to 0. When read, the content is 0.                                           | —   |

| b7  | —      |                                                         |                                                                                |     |

Notes:

1. The RI bit is set to 0 when the higher byte of the U0RB register is read.

2. In UART mode, set the UORRM bit to 0 (continuous receive mode disabled).

### 21.4.6 CTS/RTS Function

The  $\overline{\text{CTS}}$  function is used to start transmit operation when "L" is applied to the  $\overline{\text{CTS2}/\text{RTS2}}$  pin. Transmit operation begins when the  $\overline{\text{CTS2}/\text{RTS2}}$  pin is held low. If the "L" signal is switched to "H" during transmit operation, the operation stops after the ongoing transmit/receive operation is completed.

When the  $\overline{\text{RTS}}$  function is used, the  $\overline{\text{CTS2}/\text{RTS2}}$  pin outputs "L" when the MCU is ready for a receive operation. The output level goes high at the first falling edge of the CLK2 pin.

- The CRD bit in the U2C0 register = 1 ( $\overline{CTS}/\overline{RTS}$  function disabled)

- The CTS2/RTS2 pin operates as the programmable I/O function.

- The CRD bit = 0, CRS bit = 0 ( $\overline{\text{CTS}}$  function selected)

- The  $\overline{\text{CTS2}}/\overline{\text{RTS2}}$  pin operates as the  $\overline{\text{CTS}}$  function.

- The CRD bit = 0, CRS bit = 1 ( $\overline{\text{RTS}}$  function selected) The  $\overline{\text{CTS2}}/\overline{\text{RTS2}}$  pin operates as the  $\overline{\text{RTS}}$  function.

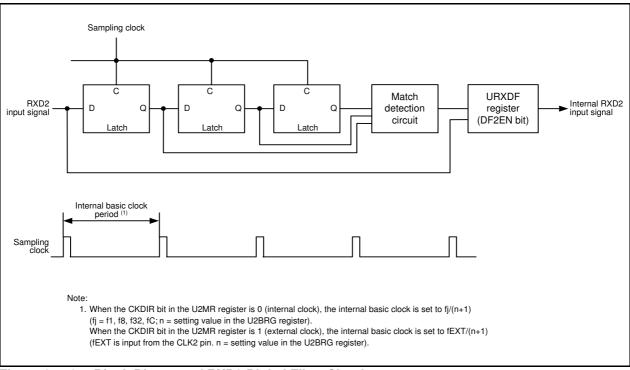

#### 21.4.7 RXD2 Digital Filter Select Function

When the DF2EN bit in the URXDF register is set to 1 (RXD2 digital filer enabled), the RXD2 input signal is loaded internally via the digital filter circuit for noise reduction. The noise canceller consists of three cascaded latch circuits and a match detection circuit. The RXD2 input signal is sampled on the internal basic clock with a frequency 16 times the bit rate. It is recognized as a signal and the level is passed forward to the next circuit when three latch outputs match. When the outputs do not match, the previous value is retained.

In other words, when the level is changed within three clocks, the change is recognized as not a signal but noise. Figure 21.12 shows a Block Diagram of RXD2 Digital Filter Circuit.

Figure 21.12 Block Diagram of RXD2 Digital Filter Circuit

### 22. A/D Converter

The A/D converter consists of one 10-bit successive approximation A/D converter circuit with a capacitive coupling amplifier. The analog input shares pins and P1\_0 to P1\_3.

#### 22.1 Overview

Table 22.1 lists the A/D Converter Performance. Figure 22.1 shows a Block Diagram of A/D Converter.

| Item                                     | Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A/D conversion method                    | Successive approximation (with capacitive coupling amplifier)                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Analog input voltage (1)                 | 0 V to AVCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Operating clock $\phi$ AD <sup>(2)</sup> | fAD, fAD divided by 2, fAD divided by 4, fAD divided by 8<br>(fAD=f1 or fOCO-F)                                                                                                                                                                                                                                                                                                                                                                                               |

| Resolution                               | 8 bits or 10 bits selectable                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Absolute accuracy                        | AVCC = Vref = 5 V, $\phi$ AD = 20 MHz<br>• 8-bit resolution ±2 LSB<br>• 10-bit resolution ±3 LSB<br>AVCC = Vref = 3.3 V, $\phi$ AD = 16 MHz<br>• 8-bit resolution ±2 LSB<br>• 10-bit resolution ±5 LSB<br>AVCC = Vref = 3.0 V, $\phi$ AD = 10 MHz<br>• 8-bit resolution ±2 LSB<br>• 10-bit resolution ±5 LSB<br>AVCC = Vref = 2.2 V, $\phi$ AD = 5 MHz<br>• 8-bit resolution ±2 LSB<br>• 10-bit resolution ±2 LSB<br>• 10-bit resolution ±2 LSB<br>• 10-bit resolution ±2 LSB |

| Operating mode                           | One-shot mode, repeat mode 0, repeat mode 1, single sweep mode, and repeat sweep mode                                                                                                                                                                                                                                                                                                                                                                                         |

| Analog input pin                         | 4 pins (AN8 to AN11)                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| A/D conversion start condition           | <ul> <li>Software trigger</li> <li>Timer RC</li> <li>External trigger<br/>(Refer to 22.3.3 A/D Conversion Start Condition.)</li> </ul>                                                                                                                                                                                                                                                                                                                                        |

| Conversion rate per pin                  | Minimum 43 ¢AD cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| $(\phi AD = fAD)$ <sup>(3)</sup>         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Table 22.1 A/D Converter Performance

Notes:

- 1. When the analog input voltage is over the reference voltage, the A/D conversion result will be 3FFh in 10-bit mode and FFh in 8-bit mode.

- 2. Refer to **Table 26.3 A/D Converter Characteristics** for the operating clock  $\phi$ AD.

- 3. The conversion rate per pin is minimum 43 ¢AD cycles for 8-bit and 10-bit resolution.

| Symbol               | Parameter                                                            | Conditions                 |           | Unit |                             |       |

|----------------------|----------------------------------------------------------------------|----------------------------|-----------|------|-----------------------------|-------|

|                      |                                                                      | Conditions                 | Min.      | Тур. | Max.                        | Unit  |

| -                    | Program/erase endurance (2)                                          |                            | 1,000 (3) | -    | -                           | times |

| -                    | Byte program time                                                    |                            | -         | 80   | 500                         | μs    |

| -                    | Block erase time                                                     |                            | -         | 0.3  | -                           | S     |

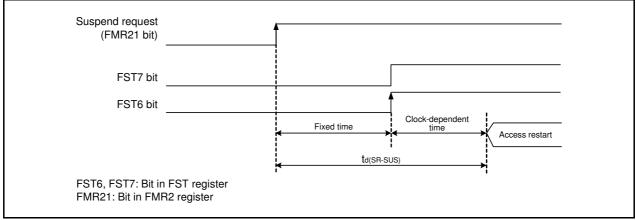

| td(SR-SUS)           | Time delay from suspend request until suspend                        |                            | -         | -    | 5 + CPU clock<br>× 3 cycles | ms    |

| _                    | Interval from erase start/restart until<br>following suspend request |                            | 0         | -    | _                           | μS    |

| _                    | Time from suspend until erase restart                                |                            | -         | -    | 30 + CPU clock<br>× 1 cycle | μS    |

| td(CMDRST-<br>READY) | Time from when command is forcibly stopped until reading is enabled  |                            | -         | -    | 30+CPU clock<br>× 1 cycle   | μS    |

| _                    | Program, erase voltage                                               |                            | 2.7       | -    | 5.5                         | V     |

| -                    | Read voltage                                                         |                            | 1.8       | -    | 5.5                         | V     |

| -                    | Program, erase temperature                                           |                            | 0         | -    | 60                          | °C    |

| -                    | Data hold time (7)                                                   | Ambient temperature = 55°C | 20        | -    | -                           | year  |

#### Table 26.5 Flash Memory (Program ROM) Electrical Characteristics

Notes:

1. Vcc = 2.7 to 5.5 V at Topr = 0 to 60°C, unless otherwise specified.

2. Definition of programming/erasure endurance

The programming and erasure endurance is defined on a per-block basis. If the programming and erasure endurance is n (n = 1,000), each block can be erased n times. For example, if 1,024 1-byte writes are performed to different addresses in block A, a 1 Kbyte block, and then the block is erased, the programming/erasure endurance still stands at one.

However, the same address must not be programmed more than once per erase operation (overwriting prohibited).

Endurance to guarantee all electrical characteristics after program and erase. (1 to Min. value can be guaranteed).

In a system that executes multiple programming operations, the actual erasure count can be reduced by writing to sequential addresses in turn so that as much of the block as possible is used up before performing an erase operation. For example, when programming groups of 16 bytes, the effective number of rewrites can be minimized by programming up to 128 groups before erasing them all in one operation. It is also advisable to retain data on the erasure endurance of each block and limit

the number of erase operations to a certain number.

If an error occurs during block erase, attempt to execute the clear status register command, then execute the block erase command at least three times until the erase error does not occur.

6. Customers desiring program/erase failure rate information should contact their Renesas technical support representative.

7. The data hold time includes time that the power supply is off or the clock is not supplied.

# Table 26.26Electrical Characteristics (6) [1.8 V $\leq$ Vcc < 2.7 V]<br/>(Topr = -20 to 85°C (N version) / -40 to 85°C (D version), unless otherwise specified.)

| Symbol      | Parameter                                                                                  | Condition                                |                                                                                                                                                                                                                                         | Standard |      |      | Unit |

|-------------|--------------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|------|------|

|             |                                                                                            |                                          |                                                                                                                                                                                                                                         | Min.     | Тур. | Max. |      |

| (<br>5<br>0 | Power supply current<br>(Vcc = 1.8 to 2.7 V)<br>Single-chip mode,<br>output pins are open, | High-speed<br>clock mode                 | XIN = 5 MHz (square wave)<br>High-speed on-chip oscillator off<br>Low-speed on-chip oscillator on = 125 kHz<br>No division                                                                                                              | _        | 2.2  | -    | mA   |

|             | other pins are Vss                                                                         |                                          | XIN = 5 MHz (square wave)<br>High-speed on-chip oscillator off<br>Low-speed on-chip oscillator on = 125 kHz<br>Divide-by-8                                                                                                              | _        | 0.8  | -    | mA   |

|             |                                                                                            | High-speed<br>on-chip<br>oscillator      | XIN clock off<br>High-speed on-chip oscillator on fOCO-F = 5 MHz<br>Low-speed on-chip oscillator on = 125 kHz<br>No division                                                                                                            | -        | 2.5  | 10   | mA   |

|             |                                                                                            | mode                                     | XIN clock off<br>High-speed on-chip oscillator on fOCO-F = 5 MHz<br>Low-speed on-chip oscillator on = 125 kHz<br>Divide-by-8                                                                                                            | -        | 1.7  | -    | mA   |

|             |                                                                                            |                                          | XIN clock off<br>High-speed on-chip oscillator on fOCO-F = 4 MHz<br>Low-speed on-chip oscillator on = 125 kHz<br>Divide-by-16<br>MSTTRC = 1                                                                                             | -        | 1    | -    | mA   |

|             |                                                                                            | Low-speed on-<br>chip oscillator<br>mode | XIN clock off<br>High-speed on-chip oscillator off<br>Low-speed on-chip oscillator on = 125 kHz<br>Divide-by-8, FMR27 = 1, VCA20 = 0                                                                                                    | -        | 90   | 300  | μA   |

|             |                                                                                            | Low-speed<br>clock mode                  | XIN clock off<br>High-speed on-chip oscillator off<br>Low-speed on-chip oscillator off<br>XCIN clock oscillator on = 32 kHz<br>No division<br>FMR27 = 1, VCA20 = 0                                                                      | -        | 80   | 350  | μA   |

|             |                                                                                            |                                          | XIN clock off<br>High-speed on-chip oscillator off<br>Low-speed on-chip oscillator off<br>XCIN clock oscillator on = 32 kHz<br>No division<br>Program operation on RAM<br>Flash memory off, FMSTP = 1, VCA20 = 0                        | -        | 40   | -    | μA   |

|             |                                                                                            | Wait mode                                | XIN clock off<br>High-speed on-chip oscillator off<br>Low-speed on-chip oscillator on = 125 kHz<br>While a WAIT instruction is executed<br>Peripheral clock operation<br>VCA27 = VCA26 = VCA25 = 0<br>VCA20 = 1                         | _        | 15   | 90   | μA   |

|             |                                                                                            |                                          | XIN clock off<br>High-speed on-chip oscillator off<br>Low-speed on-chip oscillator on = 125 kHz<br>While a WAIT instruction is executed<br>Peripheral clock off<br>VCA27 = VCA26 = VCA25 = 0<br>VCA20 = 1                               | -        | 4    | 80   | μA   |

|             |                                                                                            |                                          | XIN clock off<br>High-speed on-chip oscillator off<br>Low-speed on-chip oscillator off<br>XCIN clock oscillator on = 32 kHz (peripheral<br>clock off)<br>While a WAIT instruction is executed<br>VCA27 = VCA26 = VCA25 = 0<br>VCA20 = 1 | _        | 3.5  | _    | μA   |

|             |                                                                                            | Stop mode                                | XIN clock off, Topr = 25°C<br>High-speed on-chip oscillator off<br>Low-speed on-chip oscillator off<br>CM10 = 1<br>Peripheral clock off<br>VCA27 = VCA26 = VCA25 = 0                                                                    | -        | 2.0  | 5    | μA   |

|             |                                                                                            |                                          | XIN clock off, $T_{opr} = 85^{\circ}C$<br>High-speed on-chip oscillator off<br>Low-speed on-chip oscillator off<br>CM10 = 1<br>Peripheral clock off<br>VCA27 = VCA26 = VCA25 = 0                                                        | -        | 5.0  | -    | μA   |

### 27.10 Notes on Serial Interface (UART2)

#### 27.10.1 Clock Synchronous Serial I/O Mode

#### 27.10.1.1 Transmission/Reception

When the  $\overline{\text{RTS}}$  function is used with an external clock, the  $\overline{\text{RTS2}}$  pin outputs "L," which informs the transmitting side that the MCU is ready for a receive operation. The  $\overline{\text{RTS2}}$  pin outputs "H" when a receive operation starts. Therefore, the transmitting and receive timing can be synchronized by connecting the  $\overline{\text{RTS2}}$  pin to the  $\overline{\text{CTS2}}$  pin of the transmitting side. The  $\overline{\text{RTS}}$  function is disabled when an internal clock is selected.

#### 27.10.1.2 Transmission