Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | Coldfire V1                                                            |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 50MHz                                                                  |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                             |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                |

| Number of I/O              | 31                                                                     |

| Program Memory Size        | 128KB (128K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 32K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                           |

| Data Converters            | A/D 2x16b, 12x16b; D/A 1x12b                                           |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 44-VFLGA Exposed Pad                                                   |

| Supplier Device Package    | 44-MAPLGA (5x5)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcf51qm128vhsr |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Terminology and guidelines

| Field | Description                                     | Values                                                                                                                                                              |

|-------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| МММ   | Memory size (program flash memory) <sup>1</sup> | <ul> <li>32 = 32 KB</li> <li>64 = 64 KB</li> <li>128 = 128 KB</li> </ul>                                                                                            |

| Т     | Temperature range, ambient (°C)                 | V = -40 to 105                                                                                                                                                      |

| PP    | Package identifier                              | <ul> <li>FM = 32 QFN (5 mm x 5 mm)</li> <li>HS = 44 Laminate QFN (5 mm x 5 mm)</li> <li>LF = 48 LQFP (7 mm x 7 mm)</li> <li>LH = 64 LQFP (10 mm x 10 mm)</li> </ul> |

1. All parts also have FlexNVM, FlexRAM, and RAM.

### 2.4 Example

This is an example part number:

MCF51QM128VLH

# 3 Terminology and guidelines

## 3.1 Definition: Operating requirement

An *operating requirement* is a specified value or range of values for a technical characteristic that you must guarantee during operation to avoid incorrect operation and possibly decreasing the useful life of the chip.

### 3.1.1 Example

This is an example of an operating requirement, which you must meet for the accompanying operating behaviors to be guaranteed:

| Symbol          | Description               | Min. | Max. | Unit |

|-----------------|---------------------------|------|------|------|

| V <sub>DD</sub> | 1.0 V core supply voltage | 0.9  | 1.1  | V    |

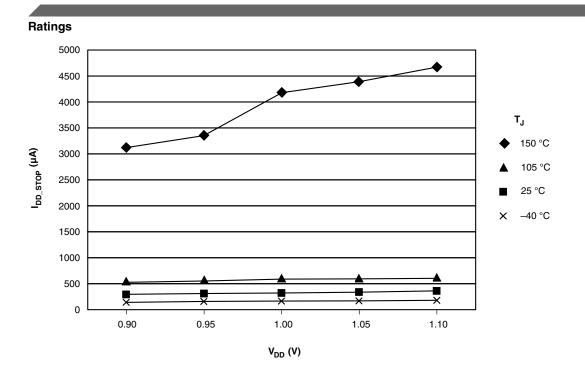

# 4 Ratings

### 4.1 Thermal handling ratings

| Symbol           | Description                   | Min. | Max. | Unit | Notes |

|------------------|-------------------------------|------|------|------|-------|

| T <sub>STG</sub> | Storage temperature           | -55  | 150  | °C   | 1     |

| T <sub>SDR</sub> | Solder temperature, lead-free | —    | 260  | °C   | 2     |

|                  | Solder temperature, leaded    | —    | 245  |      |       |

1. Determined according to JEDEC Standard JESD22-A103, High Temperature Storage Life.

2. Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices.

# 4.2 Moisture handling ratings

| Symbol | Description                | Min. | Max. | Unit | Notes |

|--------|----------------------------|------|------|------|-------|

| MSL    | Moisture sensitivity level | —    | 3    | _    | 1     |

1. Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices.

# 4.3 ESD handling ratings

| Symbol           | Description                                           | Min.  | Max.  | Unit | Notes |

|------------------|-------------------------------------------------------|-------|-------|------|-------|

| V <sub>HBM</sub> | Electrostatic discharge voltage, human body model     | -2000 | +2000 | V    | 1     |

| V <sub>CDM</sub> | Electrostatic discharge voltage, charged-device model | -500  | +500  | V    | 2     |

| I <sub>LAT</sub> | Latch-up current at ambient temperature of 105°C      | -100  | +100  | mA   |       |

1. Determined according to JEDEC Standard JESD22-A114, *Electrostatic Discharge (ESD) Sensitivity Testing Human Body Model (HBM)*.

2. Determined according to JEDEC Standard JESD22-C101, Field-Induced Charged-Device Model Test Method for Electrostatic-Discharge-Withstand Thresholds of Microelectronic Components.

## 4.4 Voltage and current operating ratings

| Symbol           | Description                                                               | Min.                  | Max.                  | Unit |

|------------------|---------------------------------------------------------------------------|-----------------------|-----------------------|------|

| V <sub>DD</sub>  | Digital supply voltage                                                    | -0.3                  | 3.8                   | V    |

| I <sub>DD</sub>  | Digital supply current                                                    | —                     | 120                   | mA   |

| V <sub>DIO</sub> | Digital input voltage (except RESET, EXTAL, and XTAL)                     | -0.3                  | V <sub>DD</sub> + 0.3 | V    |

| V <sub>AIO</sub> | Analog, RESET, EXTAL, and XTAL input voltage                              | -0.3                  | V <sub>DD</sub> + 0.3 | V    |

| Ι <sub>D</sub>   | Instantaneous maximum current single pin limit (applies to all port pins) | -25                   | 25                    | mA   |

| V <sub>DDA</sub> | Analog supply voltage                                                     | V <sub>DD</sub> – 0.3 | V <sub>DD</sub> + 0.3 | V    |

| VREGIN           | Regulator input                                                           | -0.3                  | 6.0                   | V    |

# 5 General

## 5.1 Typical Value Conditions

Typical values assume you meet the following conditions (or other conditions as specified):

| Symbol          | Description          | Value | Unit |

|-----------------|----------------------|-------|------|

| T <sub>A</sub>  | Ambient temperature  | 25    | ٥C   |

| V <sub>DD</sub> | 3.3 V supply voltage | 3.3   | V    |

# 5.2 Nonswitching electrical specifications

### 5.2.1 Voltage and Current Operating Requirements

Table 1. Voltage and current operating requirements

| Symbol             | Description                                                  | Min.                 | Max.                 | Unit | Notes |

|--------------------|--------------------------------------------------------------|----------------------|----------------------|------|-------|

| V <sub>DD</sub>    | Supply voltage                                               | 1.71                 | 3.6                  | V    |       |

| V <sub>DDA</sub>   | Analog supply voltage                                        | 1.71                 | 3.6                  | V    |       |

| $V_{DD} - V_{DDA}$ | V <sub>DD</sub> -to-V <sub>DDA</sub> differential voltage    | -0.1                 | 0.1                  | V    |       |

| $V_{SS} - V_{SSA}$ | V <sub>SS</sub> -to-V <sub>SSA</sub> differential voltage    | -0.1                 | 0.1                  | V    |       |

| V <sub>IH</sub>    | Input high voltage                                           |                      |                      |      | 1     |

|                    | • $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$ | $0.7 \times V_{DD}$  | —                    | V    |       |

|                    | • $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}$ | $0.75 \times V_{DD}$ | _                    | V    |       |

| V <sub>IL</sub>    | Input low voltage                                            |                      |                      |      | 2     |

|                    | • $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$ | _                    | $0.35 \times V_{DD}$ | V    |       |

|                    | • $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}$ | —                    | $0.3 \times V_{DD}$  | V    |       |

| I <sub>IC</sub>    | DC injection current — single pin                            |                      |                      |      | 3     |

|                    | • V <sub>IN</sub> > V <sub>DD</sub>                          | 0                    | 2                    | mA   |       |

|                    | • V <sub>IN</sub> < V <sub>SS</sub>                          | 0                    | -0.2                 | mA   |       |

|                    | DC injection current — total MCU limit, includes sum         |                      |                      |      | 3     |

|                    | of all stressed pins<br>• V <sub>IN</sub> > V <sub>DD</sub>  | 0                    | 25                   | mA   |       |

|                    | <ul> <li>V<sub>IN</sub> &lt; V<sub>SS</sub></li> </ul>       | 0                    | -5                   | mA   |       |

| V <sub>RAM</sub>   | V <sub>DD</sub> voltage required to retain RAM               | 1.2                  |                      | V    |       |

1. The device always interprets an input as a 1 when the input is greater than or equal to  $V_{IH}$  (min.) and less than or equal to  $V_{IH}$  (max.), regardless of whether input hysteresis is turned on.

2. The device always interprets an input as a 0 when the input is less than or equal to  $V_{IL}$  (max.) and greater than or equal to  $V_{IL}$  (min.), regardless of whether input hysteresis is turned on.

3. All functional non-supply pins are internally clamped to VSS and VDD. Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive and negative clamp voltages, then use the larger of the two values. Power supply must maintain regulation within operating VDD range during instantaneous and operating maximum current conditions. If positive injection current (VIn > VDD) is greater than IDD, the injection current may flow out of VDD and could result in external power supply going out of regulation. Ensure external VDD load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if clock rate is very low (which would reduce overall power consumption).

| Symbol           | Description                                                                                                                                                       | Min. | Max. | Unit | Notes |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| t <sub>POR</sub> | After a POR event, amount of time from the point $V_{DD}$ reaches 1.8 V to execution of the first instruction across the operating temperature range of the chip. |      | 300  | μs   | 1     |

|                  | • VLLS1 → RUN                                                                                                                                                     | _    | 150  | μs   | 1, 2  |

|                  | • VLLS2 $\rightarrow$ RUN                                                                                                                                         |      |      |      | 1, 2  |

|                  |                                                                                                                                                                   | _    | 75   | μs   |       |

|                  | • VLLS3 → RUN                                                                                                                                                     |      |      |      | 1, 2  |

|                  |                                                                                                                                                                   | —    | 75   | μs   |       |

|                  | • LLS $\rightarrow$ RUN                                                                                                                                           |      |      |      | 2     |

|                  |                                                                                                                                                                   | —    | 6.5  | μs   |       |

|                  | VLPS → RUN                                                                                                                                                        |      |      |      | 2     |

|                  |                                                                                                                                                                   | —    | 4.6  | μs   |       |

|                  | • STOP $\rightarrow$ RUN                                                                                                                                          |      |      |      | 2     |

|                  |                                                                                                                                                                   | —    | 4.6  | μs   |       |

Table 4. Power mode transition operating behaviors

1. Normal boot (FTFL\_FOPT[LPBOOT] is 1)

2. The wakeup time includes the execution time for a small amount of firmware used to produce a GPIO clear event. Wakeup time is measured from the falling edge of the external wakeup event to the falling edge of a GPIO clear performed by software.

# 5.2.5 Power consumption operating behaviors

### Table 5. Power consumption operating behaviors

| Symbol              | Description                                                                                                            | Min. | Тур. | Max.     | Unit | Notes |

|---------------------|------------------------------------------------------------------------------------------------------------------------|------|------|----------|------|-------|

| I <sub>DDA</sub>    | Analog supply current                                                                                                  | _    | —    | See note | mA   | 1     |

| I <sub>DD_RUN</sub> | Run mode current — all peripheral clocks disabled, code executing from RAM                                             |      |      |          |      | 2     |

|                     | • @ 1.8 V                                                                                                              | _    | 13   | _        | mA   |       |

|                     | • @ 3.0 V                                                                                                              | _    | 13   | 16       | mA   |       |

| I <sub>DD_RUN</sub> | Run mode current — all peripheral clocks<br>disabled, code executing from flash memory with<br>page buffering disabled |      |      |          |      | 2     |

|                     | • @ 1.8 V                                                                                                              | —    | 14.3 | -        | mA   |       |

|                     | • @ 3.0 V                                                                                                              | —    | 14.5 | 17.9     | mA   |       |

Table continues on the next page...

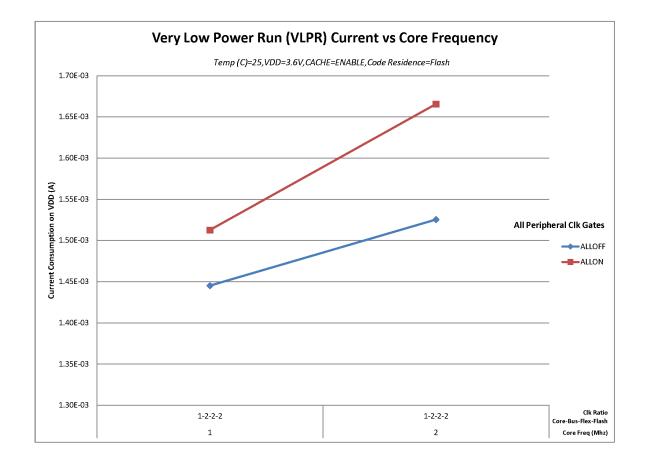

Figure 2. VLPR mode supply current vs. core frequency

### 5.2.6 EMC radiated emissions operating behaviors Table 6. EMC radiated emissions operating behaviors

| Symbol           | Description                        | Frequency<br>band (MHz) | Тур. | Unit | Notes |

|------------------|------------------------------------|-------------------------|------|------|-------|

| V <sub>RE1</sub> | Radiated emissions voltage, band 1 | 0.15–50                 | 20   | dBµV | 1, 2  |

| V <sub>RE2</sub> | Radiated emissions voltage, band 2 | 50–150                  | 19   |      |       |

| V <sub>RE3</sub> | Radiated emissions voltage, band 3 | 150–500                 | 17   |      |       |

| $V_{RE4}$        | Radiated emissions voltage, band 4 | 500–1000                | 16   |      |       |

| $V_{RE\_IEC}$    | IEC level                          | 0.15–1000               | L    | _    | 2, 3  |

Determined according to IEC Standard 61967-1, Integrated Circuits - Measurement of Electromagnetic Emissions, 150 kHz to 1 GHz Part 1: General Conditions and Definitions, and IEC Standard 61967-2, Integrated Circuits - Measurement of Electromagnetic Emissions, 150 kHz to 1 GHz Part 2: Measurement of Radiated Emissions—TEM Cell and Wideband TEM Cell Method.

#### Nonswitching electrical specifications

- 2.  $V_{DD}$  = 3 V,  $T_A$  = 25 °C,  $f_{OSC}$  = 32 kHz (crystal),  $f_{BUS}$  = 24 MHz

- 3. Specified according to Annex D of IEC Standard 61967-2, Measurement of Radiated Emissions TEM Cell and Wideband TEM Cell Method.

### 5.2.7 Designing with radiated emissions in mind

To find application notes that provide guidance on designing your system to minimize interference from radiated emissions:

- 1. Go to http://www.freescale.com.

- 2. Perform a keyword search for "EMC design."

### 5.2.8 Capacitance attributes

### Table 7. Capacitance attributes

| Symbol            | Description                     | Min. | Max. | Unit |

|-------------------|---------------------------------|------|------|------|

| C <sub>IN_A</sub> | Input capacitance: analog pins  | _    | 7    | pF   |

| C <sub>IN_D</sub> | Input capacitance: digital pins | _    | 7    | pF   |

## 5.3 Switching electrical specifications

### Table 8. Device clock specifications

| Symbol             | Description              | Min. | Max. | Unit | Notes |

|--------------------|--------------------------|------|------|------|-------|

|                    | Normal run moc           | le   |      |      | •     |

| f <sub>SYS</sub>   | System and core clock    | _    | 50   | MHz  |       |

| f <sub>BUS</sub>   | Bus clock                | _    | 25   | MHz  |       |

| FB_CLK             | Mini-FlexBus clock       | _    | 25   | MHz  | 1     |

| f <sub>LPTMR</sub> | LPTMR clock              | _    | 25   | MHz  |       |

|                    | VLPR mode                |      |      |      |       |

| f <sub>SYS</sub>   | System and core clock    | _    | 2    | MHz  |       |

| f <sub>BUS</sub>   | Bus clock                | —    | 1    | MHz  |       |

| FB_CLK             | Mini-FlexBus clock       | _    | 1    | MHz  | 1     |

| f <sub>LPTMR</sub> | LPTMR clock <sup>2</sup> | _    | 25   | MHz  |       |

1. When the Mini-FlexBus is enabled, its clock frequency is always the same as the bus clock frequency.

2. A maximum frequency of 25 MHz for the LPTMR in VLPR mode is possible when the LPTMR is configured for pulse counting mode and is driven externally via the LPTMR\_ALT1, LPTMR\_ALT2, or LPTMR\_ALT3 pin.

| Board type           | Symbol            | Description                                                                                           | 64 LQFP | 48 LQFP | 44<br>Laminate<br>QFN | 32 QFN | Unit | Notes |

|----------------------|-------------------|-------------------------------------------------------------------------------------------------------|---------|---------|-----------------------|--------|------|-------|

| Single-layer<br>(1s) | $R_{	heta JA}$    | Thermal resistance, junction to ambient (natural convection)                                          | 73      | 79      | 108                   | 98     | °C/W | 1     |

| Four-layer<br>(2s2p) | R <sub>θJA</sub>  | Thermal resistance, junction to ambient (natural convection)                                          | 54      | 55      | 69                    | 33     | °C/W | 1     |

| Single-layer<br>(1s) | R <sub>θJMA</sub> | Thermal resistance, junction to ambient (200 ft./min. air speed)                                      | 61      | 66      | 91                    | 81     | °C/W | 1     |

| Four-layer<br>(2s2p) | R <sub>θJMA</sub> | Thermal resistance, junction to ambient (200 ft./min. air speed)                                      | 48      | 48      | 63                    | 28     | °C/W | 1     |

| _                    | R <sub>θJB</sub>  | Thermal resistance, junction to board                                                                 | 37      | 34      | 44                    | 13     | °C/W | 2     |

| _                    | R <sub>θJC</sub>  | Thermal resistance, junction to case                                                                  | 20      | 20      | 31                    | 2.2    | °C/W | 3     |

| _                    | Ψ <sub>JT</sub>   | Thermal characterization<br>parameter, junction to package top<br>outside center (natural convection) | 5.0     | 4.0     | 6.0                   | 6.0    | °C/W | 4     |

## 5.4.2 Thermal attributes

1. Determined according to JEDEC Standard JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions —Natural Convection (Still Air), or EIA/JEDEC Standard JESD51-6, Integrated Circuit Thermal Test Method Environmental Conditions — Forced Convection (Moving Air).

2. Determined according to JEDEC Standard JESD51-8, Integrated Circuit Thermal Test Method Environmental Conditions —Junction-to-Board.

3. Determined according to Method 1012.1 of MIL-STD 883, *Test Method Standard, Microcircuits*, with the cold plate temperature used for the case temperature. The value includes the thermal resistance of the interface material between the top of the package and the cold plate.

4. Determined according to JEDEC Standard JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions – Natural Convection (Still Air).

# 6 Peripheral operating requirements and behaviors

### 6.1 Core modules

### 6.1.1 Debug specifications

Table 12. Background debug mode (BDM) timing

| Number | Symbol            | Description                                                                                         | Min. | Max. | Unit |

|--------|-------------------|-----------------------------------------------------------------------------------------------------|------|------|------|

| 1      | t <sub>MSSU</sub> | BKGD/MS setup time after issuing background debug force reset to enter user mode or BDM             | 500  | —    | ns   |

| 2      | t <sub>MSH</sub>  | BKGD/MS hold time after issuing background debug force reset to enter user mode or BDM <sup>1</sup> | 100  | _    | μs   |

# 6.3 Clock modules

### 6.3.1 MCG specifications

### Table 14. MCG specifications

| Symbol                   | Description                                                                                                      |                                                                                                                      | Min.                            | Тур.   | Max.    | Unit              | Notes |

|--------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------|--------|---------|-------------------|-------|

| f <sub>ints_ft</sub>     |                                                                                                                  | frequency (slow clock) —<br>nominal VDD and 25 °C                                                                    | _                               | 32.768 | —       | kHz               |       |

| f <sub>ints_t</sub>      | Internal reference<br>trimmed                                                                                    | frequency (slow clock) — user                                                                                        | 31.25                           | _      | 39.0625 | kHz               |       |

| $\Delta_{fdco\_res\_t}$  | frequency at fixed                                                                                               | Resolution of trimmed average DCO output<br>frequency at fixed voltage and temperature —<br>using SCTRIM and SCFTRIM |                                 | ± 0.3  | ± 0.6   | %f <sub>dco</sub> | 1     |

| $\Delta f_{dco\_res\_t}$ | Resolution of trimmed average DCO output<br>frequency at fixed voltage and temperature —<br>using SCTRIM only    |                                                                                                                      | _                               | ± 0.2  | ± 0.5   | %f <sub>dco</sub> | 1     |

| $\Delta f_{dco_t}$       |                                                                                                                  | otal deviation of trimmed average DCO output<br>equency over voltage and temperature                                 |                                 | ± 10   | —       | %f <sub>dco</sub> | 1     |

| $\Delta f_{dco_t}$       | Total deviation of trimmed average DCO output<br>frequency over fixed voltage and temperature<br>range of 0–70°C |                                                                                                                      | —                               | ± 1.0  | ± 4.5   | %f <sub>dco</sub> | 1     |

| f <sub>intf_ft</sub>     | Internal reference frequency (fast clock) —<br>factory trimmed at nominal VDD and 25°C                           |                                                                                                                      | _                               | 3.3    | 4       | MHz               |       |

| f <sub>intf_t</sub>      |                                                                                                                  | nternal reference frequency (fast clock) — user<br>rimmed at nominal VDD and 25 °C                                   |                                 | —      | 5       | MHz               |       |

| f <sub>loc_low</sub>     | Loss of external cl<br>RANGE = 00                                                                                | ock minimum frequency —                                                                                              | (3/5) x<br>f <sub>ints_t</sub>  | _      | _       | kHz               |       |

| f <sub>loc_high</sub>    | Loss of external cl<br>RANGE = 01, 10,                                                                           | ock minimum frequency —<br>or 11                                                                                     | (16/5) x<br>f <sub>ints_t</sub> | _      | —       | kHz               |       |

|                          |                                                                                                                  | FL                                                                                                                   | L                               |        |         |                   | •     |

| f <sub>fll_ref</sub>     | FLL reference free                                                                                               | luency range                                                                                                         | 31.25                           | —      | 39.0625 | kHz               |       |

| f <sub>dco</sub>         | DCO output<br>frequency range                                                                                    | Low range (DRS=00)<br>640 × f <sub>fl_ref</sub>                                                                      | 20                              | 20.97  | 25      | MHz               | 2, 3  |

|                          |                                                                                                                  | Mid range (DRS=01)<br>1280 × f <sub>fll_ref</sub>                                                                    | 40                              | 41.94  | 50      | MHz               |       |

|                          |                                                                                                                  | Mid-high range (DRS=10)<br>1920 × f <sub>fll_ref</sub>                                                               | 60                              | 62.91  | 75      | MHz               |       |

|                          |                                                                                                                  | High range (DRS=11)<br>2560 × f <sub>fll_ref</sub>                                                                   | 80                              | 83.89  | 100     | MHz               | -     |

Table continues on the next page ...

| Symbol                       | Description                                                                                            | Min. | Тур.            | Max. | Unit | Notes |

|------------------------------|--------------------------------------------------------------------------------------------------------|------|-----------------|------|------|-------|

| R <sub>F</sub>               | Feedback resistor — low-frequency, low-power mode (HGO=0)                                              | _    | —               | _    | MΩ   | 2, 4  |

|                              | Feedback resistor — low-frequency, high-gain mode (HGO=1)                                              | _    | 10              | _    | MΩ   | _     |

|                              | Feedback resistor — high-frequency, low-power mode (HGO=0)                                             | _    | -               | _    | ΜΩ   | _     |

|                              | Feedback resistor — high-frequency, high-gain mode (HGO=1)                                             | _    | 1               | _    | MΩ   |       |

| $R_S$                        | Series resistor — low-frequency, low-power<br>mode (HGO=0)                                             | _    | —               | _    | kΩ   |       |

|                              | Series resistor — low-frequency, high-gain mode (HGO=1)                                                | _    | 200             | _    | kΩ   |       |

|                              | Series resistor — high-frequency, low-power<br>mode (HGO=0)                                            | _    | -               | _    | kΩ   |       |

|                              | Series resistor — high-frequency, high-gain mode (HGO=1)                                               |      |                 |      |      |       |

|                              | 1 MHz resonator                                                                                        |      | 6.6             | _    | kΩ   |       |

|                              | 2 MHz resonator                                                                                        |      | 3.3             | _    | kΩ   |       |

|                              | 4 MHz resonator                                                                                        | _    | 0               | _    | kΩ   |       |

|                              | 8 MHz resonator                                                                                        |      | 0               | _    | kΩ   |       |

|                              | 16 MHz resonator                                                                                       | _    | 0               | _    | kΩ   |       |

|                              | 20 MHz resonator                                                                                       |      | 0               | _    | kΩ   |       |

|                              | 32 MHz resonator                                                                                       | _    | 0               | _    | kΩ   |       |

| V <sub>pp</sub> <sup>5</sup> | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — low-frequency, low-power mode<br>(HGO=0)  | _    | 0.6             | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — low-frequency, high-gain mode<br>(HGO=1)  | _    | V <sub>DD</sub> | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — high-frequency, low-power mode<br>(HGO=0) | _    | 0.6             | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — high-frequency, high-gain mode<br>(HGO=1) | _    | V <sub>DD</sub> | _    | V    |       |

Table 15.

Oscillator DC electrical specifications (continued)

- 1.  $V_{DD}$ =3.3 V, Temperature =25 °C

- 2. See crystal or resonator manufacturer's recommendation

- 3.  $C_{x}$ ,  $C_{y}$  can be provided by using either the integrated capacitors or by using external components.

- 4. When low power mode is selected,  $R_F$  is integrated and must not be attached externally.

- 5. The EXTAL and XTAL pins should only be connected to required oscillator components and must not be connected to any other devices.

Memories and memory interfaces

| Symbol                  | Description                                              | Min.       | Тур.         | Max.     | Unit | Notes |

|-------------------------|----------------------------------------------------------|------------|--------------|----------|------|-------|

|                         | Set FlexRAM Function execution time:                     |            |              |          |      |       |

| t <sub>setramff</sub>   | Control Code 0xFF                                        |            | 50           | _        | μs   |       |

| t <sub>setram8k</sub>   | 8 KB EEPROM backup                                       | _          | 0.3          | 0.5      | ms   |       |

| t <sub>setram32k</sub>  | 32 KB EEPROM backup                                      | _          | 0.7          | 1.0      | ms   |       |

|                         | Byte-write to FlexRAM                                    | for EEPROM | l operation  |          |      |       |

| t <sub>eewr8bers</sub>  | Byte-write to erased FlexRAM location execution time     | _          | 175          | 260      | μs   | 3     |

|                         | Byte-write to FlexRAM execution time:                    |            |              |          |      |       |

| t <sub>eewr8b8k</sub>   | 8 KB EEPROM backup                                       |            | 340          | 1700     | μs   |       |

| t <sub>eewr8b16k</sub>  | 16 KB EEPROM backup                                      | _          | 385          | 1800     | μs   |       |

| t <sub>eewr8b32k</sub>  | 32 KB EEPROM backup                                      | _          | 475          | 2000     | μs   |       |

|                         | Word-write to FlexRAM                                    | for EEPRON | A operation  |          |      |       |

| t <sub>eewr16bers</sub> | Word-write to erased FlexRAM location execution time     | _          | 175          | 260      | μs   |       |

|                         | Word-write to FlexRAM execution time:                    |            |              |          |      |       |

| t <sub>eewr16b8k</sub>  | 8 KB EEPROM backup                                       | _          | 340          | 1700     | μs   |       |

| t <sub>eewr16b16k</sub> | 16 KB EEPROM backup                                      |            | 385          | 1800     | μs   |       |

| t <sub>eewr16b32k</sub> | 32 KB EEPROM backup                                      | —          | 475          | 2000     | μs   |       |

|                         | Longword-write to FlexRA                                 | M for EEPR | OM operation | <u>ו</u> |      | I     |

| t <sub>eewr32bers</sub> | Longword-write to erased FlexRAM location execution time | _          | 360          | 540      | μs   |       |

|                         | Longword-write to FlexRAM execution time:                |            |              |          |      |       |

| t <sub>eewr32b8k</sub>  | 8 KB EEPROM backup                                       | _          | 545          | 1950     | μs   |       |

| t <sub>eewr32b16k</sub> | 16 KB EEPROM backup                                      | —          | 630          | 2050     | μs   |       |

| t <sub>eewr32b32k</sub> | 32 KB EEPROM backup                                      | —          | 810          | 2250     | μs   |       |

### Table 18. Flash command timing specifications (continued)

1. Assumes 25MHz flash clock frequency.

2. Maximum times for erase parameters based on expectations at cycling end-of-life.

3. For byte-writes to an erased FlexRAM location, the aligned word containing the byte must be erased.

### 6.4.1.3 Flash (FTFL) current and power specifications Table 19. Flash (FTFL) current and power specifications

| Sym               | nbol | Description                                     | Тур. | Unit |

|-------------------|------|-------------------------------------------------|------|------|

| I <sub>DD_F</sub> | PGM  | Worst case programming current in program flash | 10   | mA   |

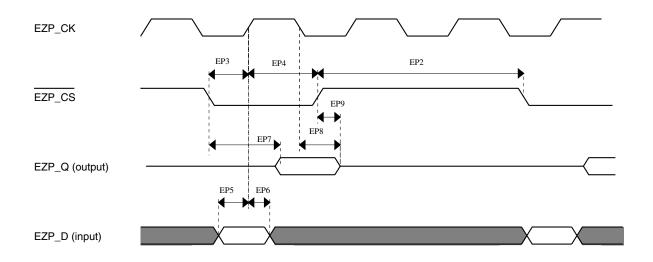

| Num | Description                               | Min. | Max. | Unit |

|-----|-------------------------------------------|------|------|------|

| EP6 | EZP_CK high to EZP_D input invalid (hold) | 0.0  | —    | ns   |

| EP7 | EZP_CK low to EZP_Q output valid (setup)  | —    | 25   | ns   |

| EP8 | EZP_CK low to EZP_Q output invalid (hold) | 0.0  | —    | ns   |

| EP9 | EZP_CS negation to EZP_Q tri-state        | —    | 12   | ns   |

Table 21. EzPort switching specifications (continued)

Figure 6. EzPort Timing Diagram

### 6.4.3 Mini-Flexbus Switching Specifications

All processor bus timings are synchronous; input setup/hold and output delay are given in respect to the rising edge of a reference clock, FB\_CLK. The FB\_CLK frequency may be the same as the internal system bus frequency or an integer divider of that frequency.

The following timing numbers indicate when data is latched or driven onto the external bus, relative to the Mini-Flexbus output clock (FB\_CLK). All other timing relationships can be derived from these values.

| Num | Description            | Min. | Max. | Unit | Notes |

|-----|------------------------|------|------|------|-------|

|     | Operating voltage      |      | 3.6  | V    |       |

|     | Frequency of operation | —    | 25   | MHz  |       |

| FB1 | Clock period           | 40   |      | ns   |       |

| Table 22. Flexb | us switching | specifications |

|-----------------|--------------|----------------|

|-----------------|--------------|----------------|

Table continues on the next page...

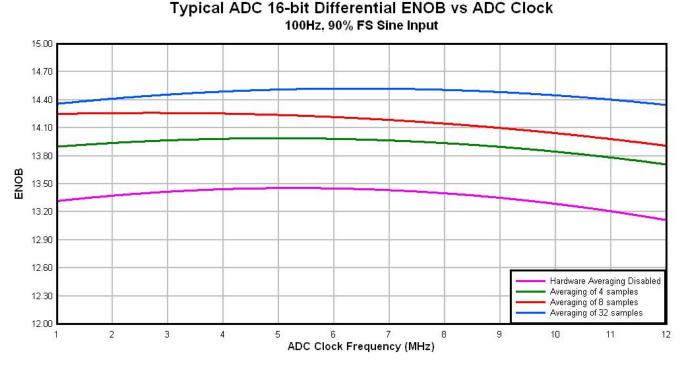

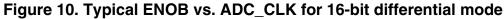

Typical ADC 16-bit Single-Ended ENOB vs ADC Clock 100Hz, 90% FS Sine Input

Figure 11. Typical ENOB vs. ADC\_CLK for 16-bit single-ended mode

Analog

**Communication interfaces**

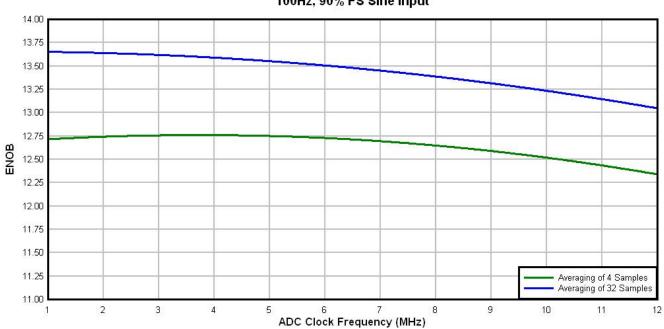

1. If configured as an output.

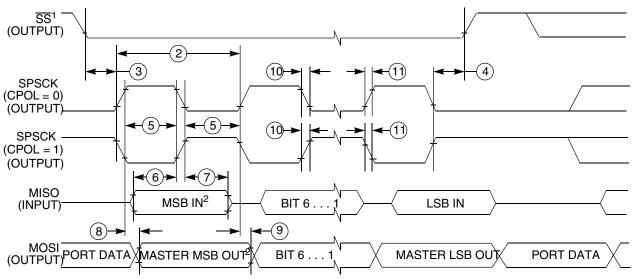

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

### Figure 16. SPI master mode timing (CPHA=0)

1.If configured as output

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

### Figure 17. SPI master mode timing (CPHA=1)

| Num. | Symbol          | Description            | Min. | Max.                | Unit | Comment                                                           |

|------|-----------------|------------------------|------|---------------------|------|-------------------------------------------------------------------|

| 1    | f <sub>op</sub> | Frequency of operation | 0    | f <sub>BUS</sub> /4 | Hz   | f <sub>BUS</sub> is the<br>bus clock<br>as defined<br>in Table 8. |

### Table 33. SPI slave mode timing

Table continues on the next page ...

| Pino       | ut         |            |            |          |          |      |                 |           |                |          |          |      |        |

|------------|------------|------------|------------|----------|----------|------|-----------------|-----------|----------------|----------|----------|------|--------|

| 64-<br>pin | 48-<br>pin | 44-<br>pin | 32-<br>pin | Default  | ALT0     | ALT1 | ALT2            | ALT3      | ALT4           | ALT5     | ALT6     | ALT7 | EzPort |

| 48         | 35         | 31         | 24         | VDD      | VDD      |      |                 |           |                |          |          |      |        |

| 49         | 36         | 32         | 25         | VSS      | VSS      |      |                 |           |                |          |          |      |        |

| 50         | 37         | 33         | 26         | EXTAL1   | EXTAL1   | PTB7 |                 | I2C1_SDA  | TMR_CLKI<br>N1 |          |          |      |        |

| 51         | 38         | 34         | 27         | XTAL1    | XTAL1    | PTC0 |                 | I2C1_SCL  | TMR_CLKI<br>N0 | RGPIO0   |          |      |        |

| 52         | 39         | 35         | 28         | RESET_b  | Disabled | PTC1 | RESET_b         |           |                |          |          |      |        |

| 53         | _          | _          | _          | CMP0_IN0 | CMP0_IN0 | PTF0 | SPI0_SS         |           |                |          | FBa_AD5  |      |        |

| 54         | _          | _          | _          | Disabled | Disabled | PTF1 | SPI0_SCLK       |           |                | CMP0_OUT | FBa_AD6  |      |        |

| 55         | _          | _          | —          | CMP0_IN1 | CMP0_IN1 | PTF2 | SPI0_MISO       |           |                |          | FBa_AD7  |      |        |

| 56         | 40         | 36         | —          | CMP0_IN2 | CMP0_IN2 | PTF3 | SPI0_MOSI       |           |                | RGPIO1   | FBa_AD8  |      |        |

| 57         | 41         | 37         | 29         | CMP0_IN3 | CMP0_IN3 | PTC2 | UART1_RT<br>S_b | SPI1_SS   |                | RGPIO2   | FBa_AD18 |      |        |

| 58         | 42         | 38         | _          | Disabled | Disabled | PTF4 | UART1_CT<br>S_b | SPI1_SCLK |                | FBa_D3   | FBa_AD19 |      |        |

| 59         | 43         | 39         | _          | Disabled | Disabled | PTF5 | UART1_RX        | SPI1_MISO |                | FBa_D2   | FBa_RW_b |      |        |

| 60         | 44         | 40         | _          | Disabled | Disabled | PTF6 | UART1_TX        | SPI1_MOSI |                | FBa_D1   | FBa_AD9  |      |        |

| 61         | 45         | 41         | -          | Disabled | Disabled | PTF7 | UART0_RT<br>S_b |           | SPI0_SS        | FBa_D0   | FBa_AD10 |      |        |

| 62         | 46         | 42         | 30         | Disabled | Disabled | PTC3 | UART0_CT        | RGPIO3    | SPI0_SCLK      | CLKOUT   |          |      |        |

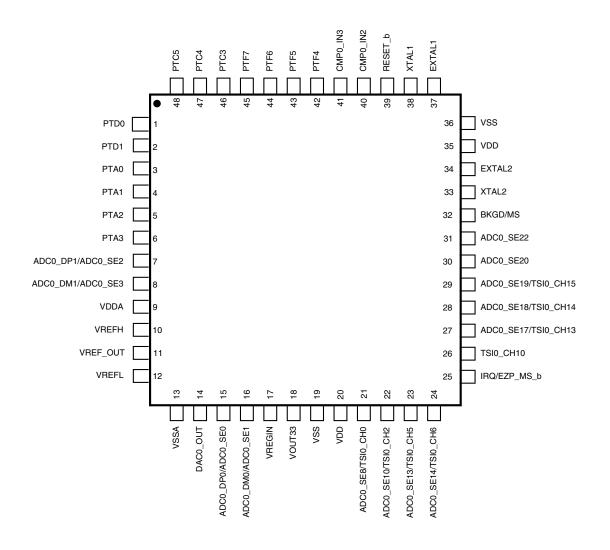

# 8.2 Pinout diagrams

31

32

Disabled

Disabled

Disabled

Disabled

PTC4

PTC5

The following diagrams show pinouts for the 64-pin, 48-pin, 44-pin, and 32-pin packages. These diagrams are representations for ease of reference. See the package drawings for mechanical details.

Sb

UARTO\_RX

UART0\_TX

RGPIO4

RGPI05

SPI0\_MISO

SPI0\_MOSI

PDB0\_EXT RG

CMT\_IRO

For each pin, the diagrams show the default function or (when disabled is the default) the ALT1 signal for a GPIO function. However, many signals may be multiplexed onto a single pin.

63

64

47

48

43

44

Figure 21. 48-pin LQFP

Table 35. Module signals by GPIO port and pin (continued)

| 64-pin | 48-pin | 44-pin | 32-pin | Port | Module signal(s)          |

|--------|--------|--------|--------|------|---------------------------|

| 48     | 35     | 31     | 24     |      | VDD                       |

| 2      |        |        |        |      | VSS                       |

| 23     | 19     | 17     | 14     |      | VSS                       |

| 49     | 36     | 32     | 25     |      | VSS                       |

|        | 1 1    | Sys    | stem   | 1    |                           |

| 45     | 32     | 28     | 21     | PTB4 | BKGD/MS                   |

| 12     | 8      | 6      | 6      | PTA5 | CLKOUT                    |

| 62     | 46     | 42     | 30     | PTC3 | CLKOUT                    |

| 10     | 6      | 4      | 4      | PTA3 | EZP_CLK                   |

| 11     | 7      | 5      | 5      | PTA4 | EZP_DI                    |

| 12     | 8      | 6      | 6      | PTA5 | EZP_DO                    |

| 35     | 25     | 23     | 17     | PTB0 | IRQ/EZP_MS_b,<br>EZP_CS_b |

| 52     | 39     | 35     | 28     | PTC1 | RESET_b                   |

|        |        | 0      | SC     |      |                           |

| 50     | 37     | 33     | 26     | PTB7 | EXTAL1                    |

| 47     | 34     | 30     | 23     | PTB6 | EXTAL2                    |

| 51     | 38     | 34     | 27     | PTC0 | XTAL1                     |

| 46     | 33     | 29     | 22     | PTB5 | XTAL2                     |

|        |        | LL     | .wu    | 1    |                           |

| 4      |        |        |        | PTC7 | LLWU_P0                   |

| 6      | 2      |        |        | PTD1 | LLWU_P1                   |

| 12     | 8      | 6      | 6      | PTA5 | LLWU_P2                   |

| 30     | 23     | 21     | 16     | PTA7 | LLWU_P3                   |

| 32     |        |        |        | PTD7 | LLWU_P4                   |

| 35     | 25     | 23     | 17     | PTB0 | LLWU_P5                   |

| 36     | 26     | 24     | 18     | PTB1 | LLWU_P6                   |

| 39     | 27     | 25     | 19     | PTB2 | LLWU_P7                   |

| 44     | 31     | 27     |        | PTE7 | LLWU_P8                   |

| 45     | 32     | 28     | 21     | PTB4 | LLWU_P9                   |

| 55     |        |        |        | PTF2 | LLWU_P10                  |

| 56     | 40     | 36     |        | PTF3 | LLWU_P11                  |

| 57     | 41     | 37     | 29     | PTC2 | LLWU_P12                  |

| 59     | 43     | 39     |        | PTF5 | LLWU_P13                  |

| 62     | 46     | 42     | 30     | PTC3 | LLWU_P14                  |

Table continues on the next page ...

| 64-pin | 48-pin | 44-pin | 32-pin  | Port | Module signal(s) |

|--------|--------|--------|---------|------|------------------|

| 60     | 44     | 40     |         | PTF6 | FBa_D1           |

| 59     | 43     | 39     |         | PTF5 | FBa_D2           |

| 58     | 42     | 38     |         | PTF4 | FBa_D3           |

| 31     | 24     | 22     |         | PTD6 | FBa_D4           |

| 30     | 23     | 21     | 16      | PTA7 | FBa_D5           |

| 27     | 22     | 20     |         | PTD3 | FBa_D6           |

| 25     | 21     | 19     | 15      | PTA6 | FBa_D7           |

| 44     | 31     | 27     |         | PTE7 | FBa_RW_b         |

|        |        | I2C0 a | nd I2C1 | 1    |                  |

| 3      |        |        |         | PTC6 | I2C0_SCL         |

| 35     | 25     | 23     | 17      | PTB0 | I2C0_SCL         |

| 4      |        |        |         | PTC7 | I2C0_SDA         |

| 36     | 26     | 24     | 18      | PTB1 | I2C0_SDA         |

| 6      | 2      |        |         | PTD1 | I2C1_SCL         |

| 42     | 30     |        |         | PTE5 | I2C1_SCL         |

| 51     | 38     | 34     | 27      | PTC0 | I2C1_SCL         |

| 5      | 1      |        |         | PTD0 | I2C1_SDA         |

| 43     |        |        |         | PTE6 | I2C1_SDA         |

| 50     | 37     | 33     | 26      | PTB7 | I2C1_SDA         |

|        |        | I2C2 a | nd I2C3 | 1    |                  |

| 7      | 3      | 1      | 1       | PTA0 | I2C2_SCL         |

| 11     | 7      | 5      | 5       | PTA4 | I2C2_SCL         |

| 8      | 4      | 2      | 2       | PTA1 | I2C2_SDA         |

| 12     | 8      | 6      | 6       | PTA5 | I2C2_SDA         |

| 32     |        |        |         | PTD7 | I2C3_SCL         |

| 37     |        |        |         | PTE2 | I2C3_SCL         |

| 33     |        |        |         | PTE0 | I2C3_SDA         |

| 38     |        |        |         | PTE3 | I2C3_SDA         |

|        |        | S      | PI0     | 1    |                  |

| 39     | 27     | 25     | 19      | PTB2 | SPI0_MISO        |

| 55     |        |        |         | PTF2 | SPI0_MISO        |

| 63     | 47     | 43     | 31      | PTC4 | SPI0_MISO        |

| 38     |        |        |         | PTE3 | SPI0_MOSI        |

| 40     | 28     | 26     | 20      | PTB3 | SPI0_MOSI        |

| 56     | 40     | 36     |         | PTF3 | SPI0_MOSI        |

Table continues on the next page...

| Table 35  | Module signals by |          | ort and r | nin (  | (continued) |   |

|-----------|-------------------|----------|-----------|--------|-------------|---|

| Table 35. | Module signals by | γ αριό ρ | ort and p | JIII ( | continuea)  | ) |

| 64-pin | 48-pin | 44-pin | 32-pin | Port | Module signal(s) |

|--------|--------|--------|--------|------|------------------|

| 64     | 48     | 44     | 32     | PTC5 | SPI0_MOSI        |

| 36     | 26     | 24     | 18     | PTB1 | SPI0_SCLK        |

| 54     |        |        |        | PTF1 | SPI0_SCLK        |

| 62     | 46     | 42     | 30     | PTC3 | SPI0_SCLK        |

| 7      | 3      | 1      | 1      | PTA0 | SPI0_SS          |

| 34     |        |        |        | PTE1 | SPI0_SS          |

| 53     |        |        |        | PTF0 | SPI0_SS          |

| 61     | 45     | 41     |        | PTF7 | SPI0_SS          |

|        |        | S      | PI1    | 1    |                  |

| 4      |        |        |        | PTC7 | SPI1_MISO        |

| 11     | 7      | 5      | 5      | PTA4 | SPI1_MISO        |

| 43     |        |        |        | PTE6 | SPI1_MISO        |

| 59     | 43     | 39     |        | PTF5 | SPI1_MISO        |

| 3      |        |        |        | PTC6 | SPI1_MOSI        |

| 12     | 8      | 6      | 6      | PTA5 | SPI1_MOSI        |

| 44     | 31     | 27     |        | PTE7 | SPI1_MOSI        |

| 60     | 44     | 40     |        | PTF6 | SPI1_MOSI        |

| 5      | 1      |        |        | PTD0 | SPI1_SCLK        |

| 10     | 6      | 4      | 4      | РТАЗ | SPI1_SCLK        |

| 42     | 30     |        |        | PTE5 | SPI1_SCLK        |

| 58     | 42     | 38     |        | PTF4 | SPI1_SCLK        |

| 6      | 2      |        |        | PTD1 | SPI1_SS          |

| 9      | 5      | 3      | 3      | PTA2 | SPI1_SS          |

| 41     | 29     |        |        | PTE4 | SPI1_SS          |

| 57     | 41     | 37     | 29     | PTC2 | SPI1_SS          |

|        |        | UA     | RT0    |      |                  |

| 5      | 1      |        |        | PTD0 | UART0_CTS_b      |

| 32     |        |        |        | PTD7 | UART0_CTS_b      |

| 42     | 30     |        |        | PTE5 | UART0_CTS_b      |

| 62     | 46     | 42     | 30     | PTC3 | UART0_CTS_b      |

| 6      | 2      |        |        | PTD1 | UART0_RTS_b      |

| 33     |        |        |        | PTE0 | UART0_RTS_b      |

| 41     | 29     |        |        | PTE4 | UART0_RTS_b      |

| 61     | 45     | 41     |        | PTF7 | UART0_RTS_b      |

| 4      |        |        |        | PTC7 | UART0_RX         |

Table continues on the next page ...

**Revision History**

| 64-pin | 48-pin | 44-pin | 32-pin | Port | Module signal(s) |

|--------|--------|--------|--------|------|------------------|

| 31     | 24     | 22     |        | PTD6 | UART0_RX         |

| 43     |        |        |        | PTE6 | UART0_RX         |

| 63     | 47     | 43     | 31     | PTC4 | UART0_RX         |

| 3      |        |        |        | PTC6 | UART0_TX         |

| 30     | 23     | 21     | 16     | PTA7 | UART0_TX         |

| 44     | 31     | 27     |        | PTE7 | UART0_TX         |

| 64     | 48     | 44     | 32     | PTC5 | UART0_TX         |

|        |        | UA     | RT1    |      |                  |

| 11     | 7      | 5      | 5      | PTA4 | UART1_CTS_b      |

| 58     | 42     | 38     |        | PTF4 | UART1_CTS_b      |

| 12     | 8      | 6      | 6      | PTA5 | UART1_RTS_b      |

| 57     | 41     | 37     | 29     | PTC2 | UART1_RTS_b      |

| 10     | 6      | 4      | 4      | PTA3 | UART1_RX         |

| 59     | 43     | 39     |        | PTF5 | UART1_RX         |

| 9      | 5      | 3      | 3      | PTA2 | UART1_TX         |

| 60     | 44     | 40     |        | PTF6 | UART1_TX         |

Table 35. Module signals by GPIO port and pin (continued)

# 9 Revision History

The following table summarizes content changes since the previous release of this document.

| Table 36. | Revision | History |

|-----------|----------|---------|

|-----------|----------|---------|

| Rev. No. | Date    | Substantial Changes                                                                   |

|----------|---------|---------------------------------------------------------------------------------------|

| 6        | 01/2012 | Thermal operating requirements: Changed maximum $T_{\rm J}$ value from 125°C to 115°C |