Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | Coldfire V1                                                          |

| Core Size                  | 32-Bit Single-Core                                                   |

| Speed                      | 50MHz                                                                |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                    |

| Peripherals                | DMA, LVD, POR, PWM                                                   |

| Number of I/O              | 22                                                                   |

| Program Memory Size        | 32KB (32K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 8K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                         |

| Data Converters            | A/D 13x16b; D/A 1x12b                                                |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                   |

| Mounting Type              | Surface Mount, Wettable Flank                                        |

| Package / Case             | 32-VFQFN Exposed Pad                                                 |

| Supplier Device Package    | 32-HVQFN (5x5)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/pcf51qm32vfm |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.2 Definition: Operating behavior

An *operating behavior* is a specified value or range of values for a technical characteristic that are guaranteed during operation if you meet the operating requirements and any other specified conditions.

## 3.2.1 Example

This is an example of an operating behavior, which is guaranteed if you meet the accompanying operating requirements:

| Symbol          | Description                                  | Min. | Max. | Unit |

|-----------------|----------------------------------------------|------|------|------|

| I <sub>WP</sub> | Digital I/O weak pullup/<br>pulldown current | 10   | 130  | μΑ   |

## 3.3 Definition: Attribute

An *attribute* is a specified value or range of values for a technical characteristic that are guaranteed, regardless of whether you meet the operating requirements.

## 3.3.1 Example

This is an example of an attribute:

| Symbol | Description                        | Min. | Max. | Unit |

|--------|------------------------------------|------|------|------|

| CIN_D  | Input capacitance:<br>digital pins |      | 7    | pF   |

# 3.4 Definition: Rating

A *rating* is a minimum or maximum value of a technical characteristic that, if exceeded, may cause permanent chip failure:

- Operating ratings apply during operation of the chip.

- *Handling ratings* apply when the chip is not powered.

- During normal operation, don't exceed any of the chip's operating requirements.

- If you must exceed an operating requirement at times other than during normal operation (for example, during power sequencing), limit the duration as much as possible.

# 3.8 Definition: Typical value

A *typical value* is a specified value for a technical characteristic that:

- Lies within the range of values specified by the operating behavior

- Given the typical manufacturing process, is representative of that characteristic during operation when you meet the typical-value conditions or other specified conditions

Typical values are provided as design guidelines and are neither tested nor guaranteed.

## 3.8.1 Example 1

This is an example of an operating behavior that includes a typical value:

| Symbol          | Description                                    | Min. | Тур. | Max. | Unit |

|-----------------|------------------------------------------------|------|------|------|------|

| I <sub>WP</sub> | Digital I/O weak<br>pullup/pulldown<br>current | 10   | 70   | 130  | μΑ   |

## 3.8.2 Example 2

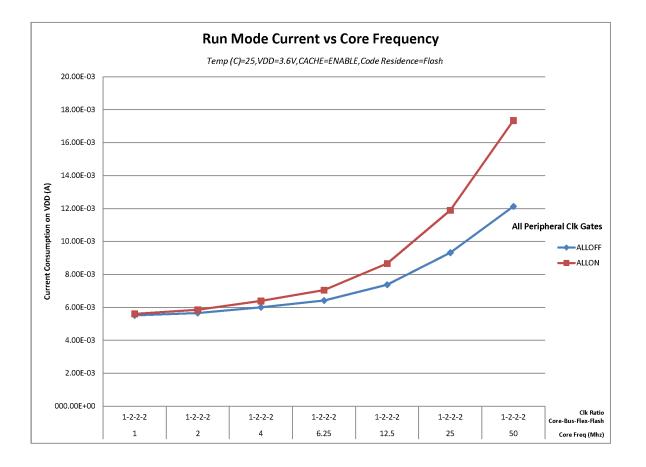

This is an example of a chart that shows typical values for various voltage and temperature conditions:

Figure 1. Run mode supply current vs. core frequency

### Thermal specifications

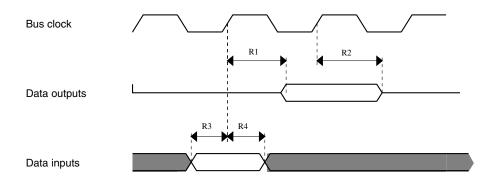

The following general purpose specifications apply to all signals configured for RGPIO, FTM, and UART. The conditions are 25 pf load,  $V_{DD} = 3.6$  V to 1.71 V, and full temperature range. The GPIO are set for high drive, no slew rate control, and no input filter, digital or analog, unless otherwise specified.

| Symbol | Description                                                       | Min. | Max. | Unit |

|--------|-------------------------------------------------------------------|------|------|------|

| R1     | CPUCLK from CLK_OUT pin high to GPIO output valid                 | —    | 16   | ns   |

| R2     | CPUCLK from CLK_OUT pin high to GPIO output invalid (output hold) | 1    | —    | ns   |

| R3     | GPIO input valid to bus clock high                                | 17   | —    | ns   |

| R4     | CPUCLK from CLK_OUT pin high to GPIO input invalid                | —    | 2    | ns   |

Table 10. RGPIO General Control Timing

# 5.4 Thermal specifications

### 5.4.1 Thermal operating requirements

Table 11. Thermal operating requirements

| Symbol         | Description              | Min. | Max. | Unit |

|----------------|--------------------------|------|------|------|

| TJ             | Die junction temperature | -40  | 115  | °C   |

| T <sub>A</sub> | Ambient temperature      | -40  | 105  | °C   |

### 6.3.2.2 Oscillator frequency specifications Table 16. Oscillator frequency specifications

| Symbol                | Description                                                                                           | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|-------------------------------------------------------------------------------------------------------|------|------|------|------|-------|

| f <sub>osc_lo</sub>   | Oscillator crystal or resonator frequency — low frequency mode (MCG_C2[RANGE]=00)                     | 32   | _    | 40   | kHz  |       |

| f <sub>osc_hi_1</sub> | Oscillator crystal or resonator frequency — high<br>frequency mode (low range)<br>(MCG_C2[RANGE]=01)  | 1    | _    | 8    | MHz  |       |

| f <sub>osc_hi_2</sub> | Oscillator crystal or resonator frequency — high<br>frequency mode (high range)<br>(MCG_C2[RANGE]=1x) | 8    | _    | 32   | MHz  |       |

| f <sub>ec_extal</sub> | Input clock frequency (external clock mode)                                                           | —    | —    | 50   | MHz  | 1, 2  |

| t <sub>dc_extal</sub> | Input clock duty cycle (external clock mode)                                                          | 40   | 50   | 60   | %    |       |

| t <sub>cst</sub>      | Crystal startup time — 32 kHz low-frequency,<br>low-power mode (HGO=0)                                | _    | 750  | _    | ms   | 3, 4  |

|                       | Crystal startup time — 32 kHz low-frequency,<br>high-gain mode (HGO=1)                                | _    | 250  | _    | ms   |       |

|                       | Crystal startup time — 8 MHz high-frequency<br>(MCG_C2[RANGE]=01), low-power mode<br>(HGO=0)          | _    | 0.6  | _    | ms   |       |

|                       | Crystal startup time — 8 MHz high-frequency<br>(MCG_C2[RANGE]=01), high-gain mode<br>(HGO=1)          | _    | 1    | _    | ms   |       |

1. Other frequency limits may apply when external clock is being used as a reference for the FLL or PLL.

2. When transitioning from FBE to FEI mode, restrict the frequency of the input clock so that, when it is divided by FRDIV, it remains within the limits of the DCO input clock frequency.

3. Proper PC board layout procedures must be followed to achieve specifications.

4. Crystal startup time is defined as the time between the oscillator being enabled and the OSCINIT bit in the MCG\_S register being set.

## 6.4 Memories and memory interfaces

### 6.4.1 Flash (FTFL) electrical specifications

This section describes the electrical characteristics of the FTFL module.

### 6.4.1.1 Flash timing specifications — program and erase

The following specifications represent the amount of time the internal charge pumps are active and do not include command overhead.

The bytes not assigned to data flash via the FlexNVM partition code are used by the FTFL to obtain an effective endurance increase for the EEPROM data. The built-in EEPROM record management system raises the number of program/erase cycles that can be attained prior to device wear-out by cycling the EEPROM data through a larger EEPROM NVM storage space.

While different partitions of the FlexNVM are available, the intention is that a single choice for the FlexNVM partition code and EEPROM data set size is used throughout the entire lifetime of a given application. The EEPROM endurance equation and graph shown below assume that only one configuration is ever used.

Writes\_FlexRAM =  $\frac{\text{EEPROM} - 2 \times \text{EEESIZE}}{\text{EEESIZE}} \times \text{Write_efficiency} \times n_{\text{nvmcycd}}$

where

- Writes\_FlexRAM minimum number of writes to each FlexRAM location

- EEPROM allocated FlexNVM based on DEPART; entered with Program Partition command

- EEESIZE allocated FlexRAM based on DEPART; entered with Program Partition command

- Write\_efficiency

- 0.25 for 8-bit writes to FlexRAM

- 0.50 for 16-bit or 32-bit writes to FlexRAM

- n<sub>nvmcycd</sub> data flash cycling endurance

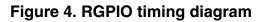

| Num | Description                               | Min. | Max. | Unit |

|-----|-------------------------------------------|------|------|------|

| EP6 | EZP_CK high to EZP_D input invalid (hold) | 0.0  | —    | ns   |

| EP7 | EZP_CK low to EZP_Q output valid (setup)  | —    | 25   | ns   |

| EP8 | EZP_CK low to EZP_Q output invalid (hold) | 0.0  | —    | ns   |

| EP9 | EZP_CS negation to EZP_Q tri-state        | —    | 12   | ns   |

Table 21. EzPort switching specifications (continued)

Figure 6. EzPort Timing Diagram

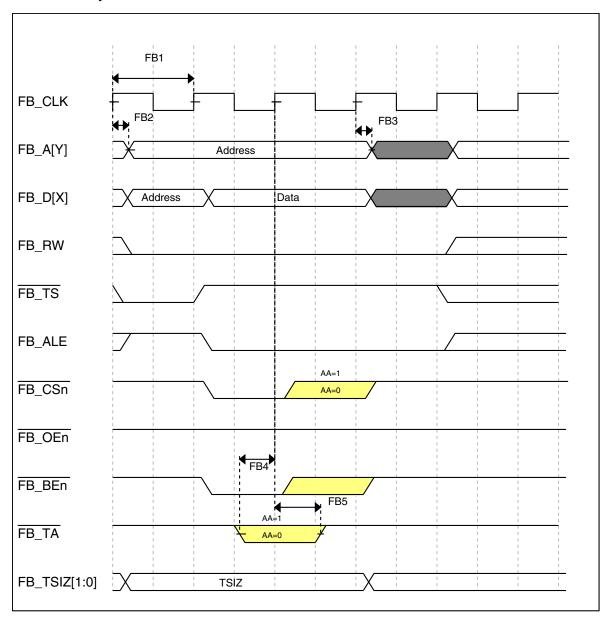

## 6.4.3 Mini-Flexbus Switching Specifications

All processor bus timings are synchronous; input setup/hold and output delay are given in respect to the rising edge of a reference clock, FB\_CLK. The FB\_CLK frequency may be the same as the internal system bus frequency or an integer divider of that frequency.

The following timing numbers indicate when data is latched or driven onto the external bus, relative to the Mini-Flexbus output clock (FB\_CLK). All other timing relationships can be derived from these values.

| Num | Description            | Min. | Max. | Unit | Notes |

|-----|------------------------|------|------|------|-------|

|     | Operating voltage      | 1.71 | 3.6  | V    |       |

|     | Frequency of operation | —    | 25   | MHz  |       |

| FB1 | Clock period           | 40   |      | ns   |       |

| Table 22. Flexb | us switching | specifications |

|-----------------|--------------|----------------|

|-----------------|--------------|----------------|

Table continues on the next page...

Figure 8. Mini-FlexBus write timing diagram

# 6.5 Security and integrity modules

There are no specifications necessary for the device's security and integrity modules.

### Analog

| Symbol            | Description    | Conditions                                                          | Min.   | Typ. <sup>1</sup> | Max.    | Unit | Notes |

|-------------------|----------------|---------------------------------------------------------------------|--------|-------------------|---------|------|-------|

| C <sub>rate</sub> | ADC conversion | ≤ 13 bit modes                                                      |        |                   |         |      | 5     |

|                   | rate           | No ADC hardware averaging                                           | 20.000 | —                 | 818.330 | Ksps |       |

|                   |                | Continuous<br>conversions enabled,<br>subsequent conversion<br>time |        |                   |         |      |       |

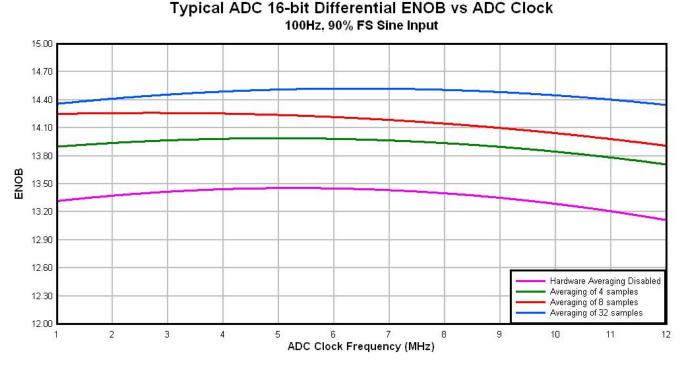

| C <sub>rate</sub> | ADC conversion | 16 bit modes                                                        |        |                   |         |      | 5     |

|                   | rate           | No ADC hardware averaging                                           | 37.037 | _                 | 461.467 | Ksps |       |

|                   |                | Continuous<br>conversions enabled,<br>subsequent conversion<br>time |        |                   |         |      |       |

Table 23.

16-bit ADC operating conditions (continued)

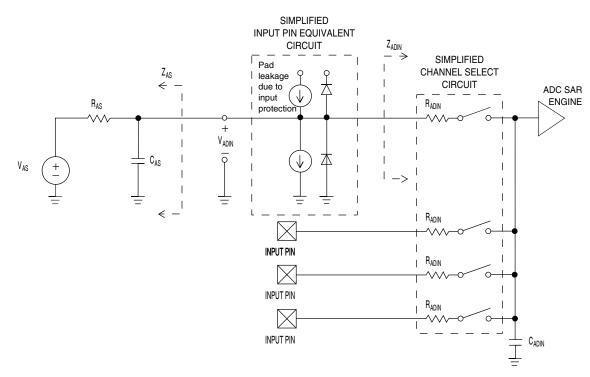

Typical values assume V<sub>DDA</sub> = 3.0 V, Temp = 25°C, f<sub>ADCK</sub> = 1.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

2. DC potential difference.

3. This resistance is external to MCU. The analog source resistance should be kept as low as possible in order to achieve the best results. The results in this datasheet were derived from a system which has <8  $\Omega$  analog source resistance. The R<sub>AS</sub>/ C<sub>AS</sub> time constant should be kept to <1ns.

4. To use the maximum ADC conversion clock frequency, the ADHSC bit should be set and the ADLPC bit should be clear.

5. For guidelines and examples of conversion rate calculation, download the ADC calculator tool: http://cache.freescale.com/ files/soft\_dev\_tools/software/app\_software/converters/ADC\_CALCULATOR\_CNV.zip?fpsp=1

Figure 9. ADC input impedance equivalency diagram

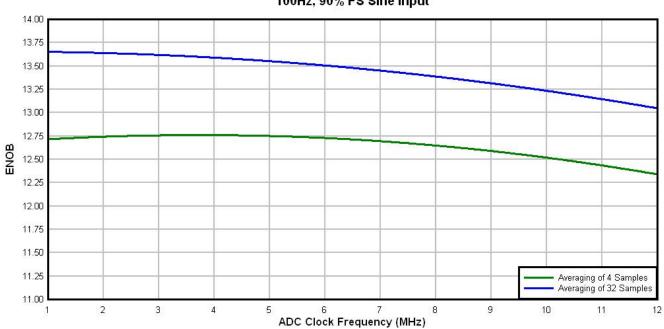

Typical ADC 16-bit Single-Ended ENOB vs ADC Clock 100Hz, 90% FS Sine Input

Figure 11. Typical ENOB vs. ADC\_CLK for 16-bit single-ended mode

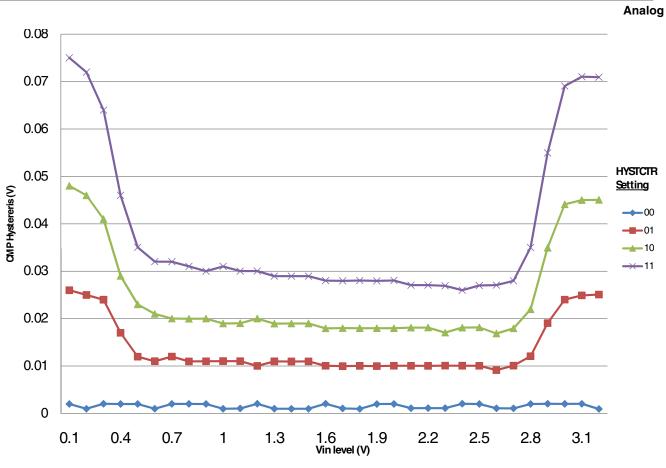

Analog

Figure 12. Typical hysteresis vs. Vin level (VDD=3.3V, PMODE=0)

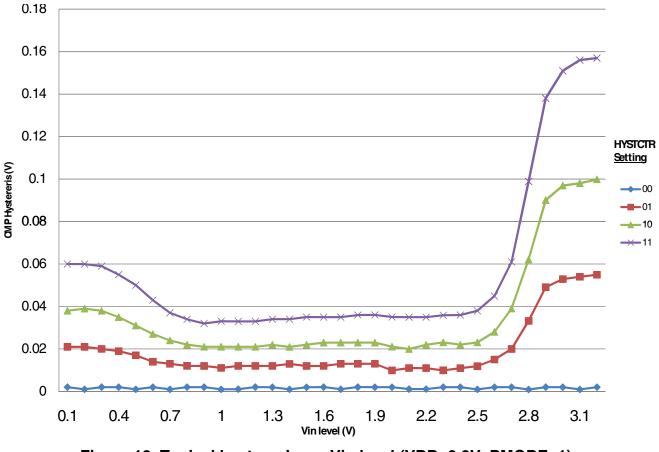

12-bit DAC electrical characteristics

Figure 13. Typical hysteresis vs. Vin level (VDD=3.3V, PMODE=1)

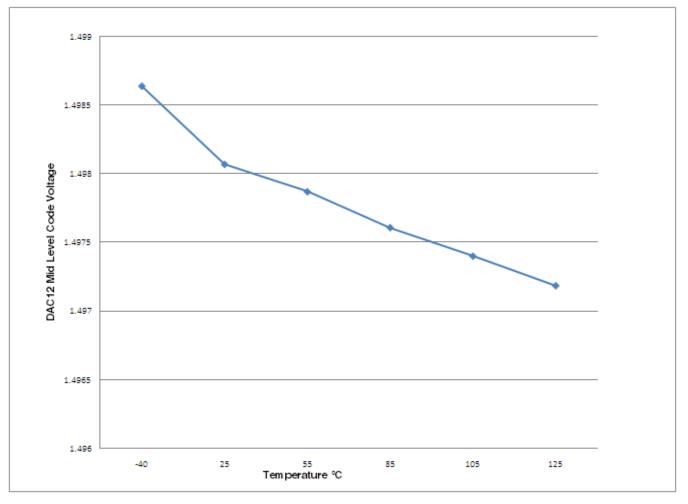

### 6.6.3 12-bit DAC electrical characteristics

### 6.6.3.1 12-bit DAC operating requirements Table 26. 12-bit DAC operating requirements

| Symbol            | Desciption              | Min. | Max. | Unit | Notes |

|-------------------|-------------------------|------|------|------|-------|

| V <sub>DDA</sub>  | Supply voltage          | 1.71 | 3.6  | V    |       |

| V <sub>DACR</sub> | Reference voltage       | 1.13 | 3.6  | V    | 1     |

| T <sub>A</sub>    | Temperature             | -40  | 105  | °C   |       |

| CL                | Output load capacitance | _    | 100  | pF   | 2     |

| ΙL                | Output load current     | _    | 1    | mA   |       |

1. The DAC reference can be selected to be VDDA or the voltage output of the VREF module (VREF\_OUT)

2. A small load capacitance (47 pF) can improve the bandwidth performance of the DAC

Figure 15. Offset at half scale vs. temperature

## 6.6.4 Voltage reference electrical specifications

| Symbol           | Description                | Min. | Max. | Unit | Notes |

|------------------|----------------------------|------|------|------|-------|

| V <sub>DDA</sub> | Supply voltage             | 1.71 | 3.6  | V    |       |

| T <sub>A</sub>   | T <sub>A</sub> Temperature |      | 105  | °C   |       |

| CL               | Output load capacitance    | 100  |      | nF   | 1     |

1. C<sub>L</sub> must be connected to VREF\_OUT if the VREF\_OUT functionality is being used for either an internal or external reference.

Human-machine interfaces (HMI)

NOTE: Not defined!

# 6.9 Human-machine interfaces (HMI)

## 6.9.1 TSI electrical specifications

Table 34. TSI electrical specifications

| Symbol              | Description                                                                   | Min.  | Тур.   | Max.  | Unit     | Notes |

|---------------------|-------------------------------------------------------------------------------|-------|--------|-------|----------|-------|

| V <sub>DDTSI</sub>  | Operating voltage                                                             | 1.71  | —      | 3.6   | V        |       |

| C <sub>ELE</sub>    | Target electrode capacitance range                                            | 1     | 20     | 500   | pF       | 1     |

| f <sub>REFmax</sub> | Reference oscillator frequency                                                | _     | 5.5    | 14    | MHz      | 2     |

| f <sub>ELEmax</sub> | Electrode oscillator frequency                                                | _     | 0.5    | 4.0   | MHz      | 3     |

| C <sub>REF</sub>    | Internal reference capacitor                                                  | 0.5   | 1      | 1.2   | pF       |       |

| V <sub>DELTA</sub>  | Oscillator delta voltage                                                      | 100   | 600    | 760   | mV       | 4     |

| I <sub>REF</sub>    | Reference oscillator current source base current<br>• 1uA setting (REFCHRG=0) | _     | 1.133  | 1.5   | μA       | 3,5   |

|                     | • 32uA setting (REFCHRG=31)                                                   | —     | 36     | 50    |          |       |

| I <sub>ELE</sub>    | Electrode oscillator current source base current<br>• 1uA setting (EXTCHRG=0) | _     | 1.133  | 1.5   | μA       | 3,6   |

|                     | • 32uA setting (EXTCHRG=31)                                                   | —     | 36     | 50    |          |       |

| Pres5               | Electrode capacitance measurement precision                                   |       | 8.3333 | 38400 | %        | 7     |

| Pres20              | Electrode capacitance measurement precision                                   | _     | 8.3333 | 38400 | %        | 8     |

| Pres100             | Electrode capacitance measurement precision                                   | —     | 8.3333 | 38400 | %        | 9     |

| MaxSens             | Maximum sensitivity                                                           | 0.003 | 12.5   | —     | fF/count | 10    |

Table continues on the next page ...

MCF51QM128 Data Sheet, Rev. 6, 01/2012.

| Symbol               | Description                  | Min. | Тур. | Max. | Unit | Notes |

|----------------------|------------------------------|------|------|------|------|-------|

| Res                  | Res Resolution               |      | —    | 16   | bits |       |

| T <sub>Con20</sub>   | Response time @ 20 pF        |      | 15   | 25   | μs   | 11    |

| I <sub>TSI_RUN</sub> | Current added in run mode    | _    | 55   | _    | μA   |       |

| I <sub>TSI_LP</sub>  | Low power mode current adder |      | 1.3  | 2.5  | μA   | 12    |

Table 34. TSI electrical specifications (continued)

1. The TSI module is functional with capacitance values outside this range. However, optimal performance is not guaranteed.

- 2. CAPTRM=7, DELVOL=7, and fixed external capacitance of 20 pF.

- 3. CAPTRM=0, DELVOL=2, and fixed external capacitance of 20 pF.

- 4. CAPTRM=0, EXTCHRG=9, and fixed external capacitance of 20 pF.

- 5. The programmable current source value is generated by multiplying the SCANC[REFCHRG] value and the base current.

- 6. The programmable current source value is generated by multiplying the SCANC[EXTCHRG] value and the base current.

- 7. Measured with a 5 pF electrode, reference oscillator frequency of 10 MHz, PS = 128, NSCN = 8; lext = 16.

- 8. Measured with a 20 pF electrode, reference oscillator frequency of 10 MHz, PS = 128, NSCN = 2; lext = 16.

- 9. Measured with a 20 pF electrode, reference oscillator frequency of 10 MHz, PS = 16, NSCN = 3; lext = 16.

10. Sensitivity defines the minimum capacitance change when a single count from the TSI module changes, it is equal to (C<sub>ref</sub> \* I<sub>ext</sub>)/(I<sub>ref</sub> \* PS \* NSCN). Sensitivity depends on the configuration used. The typical value listed is based on the following configuration: lext = 5 μA, EXTCHRG = 4, PS = 128, NSCN = 2, I<sub>ref</sub> = 16 μA, REFCHRG = 15, C<sub>ref</sub> = 1.0 pF. The minimum sensitivity describes the smallest possible capacitance that can be measured by a single count (this is the best sensitivity but is described as a minimum because it's the smallest number). The minimum sensitivity parameter is based on the following configuration: I<sub>ext</sub> = 1 μA, EXTCHRG = 0, PS = 128, NSCN = 32, I<sub>ref</sub> = 32 μA, REFCHRG = 31, C<sub>ref</sub> = 0.5 pF

- 11. Time to do one complete measurement of the electrode. Sensitivity resolution of 0.0133 pF, PS = 0, NSCN = 0, 1 electrode, DELVOL = 2, EXTCHRG = 15.

- 12. CAPTRM=7, DELVOL=2, REFCHRG=0, EXTCHRG=4, PS=7, NSCN=0F, LPSCNITV=F, LPO is selected (1 kHz), and fixed external capacitance of 20 pF. Data is captured with an average of 7 periods window.

# 7 Dimensions

## 7.1 Obtaining package dimensions

Package dimensions are provided in package drawings.

To find a package drawing, go to http://www.freescale.com and perform a keyword search for the drawing's document number:

| If you want the drawing for this package | Then use this document number |

|------------------------------------------|-------------------------------|

| 32-pin QFN                               | 98ARE10566D                   |

| 44-pin Laminate QFN                      | 98ASA00239D                   |

| 48-pin LQFP                              | 98ASH00962A                   |

| 64-pin LQFP                              | 98ASS23234W                   |

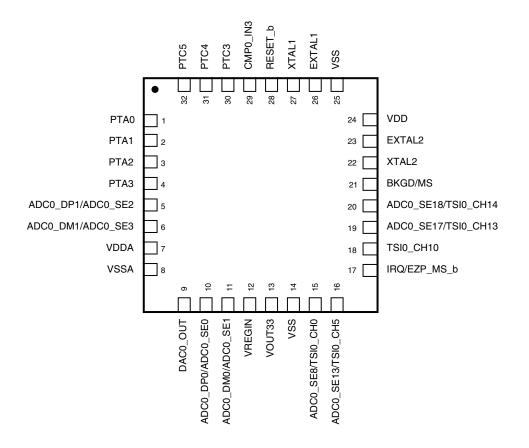

# 8 Pinout

# 8.1 Signal Multiplexing and Pin Assignments

The following table shows the signals available on each pin and the locations of these pins on the devices supported by this document. The Port Mux Control module is responsible for selecting which ALT functionality is available on each pin.

### NOTE

• On PTB0, EZP\_MS\_b is active only during reset. Refer to the detailed boot description.

| 64-<br>pin | 48-<br>pin | 44-<br>pin | 32-<br>pin | Default               | ALT0                  | ALT1 | ALT2            | ALT3     | ALT4     | ALT5      | ALT6     | ALT7 | EzPort  |

|------------|------------|------------|------------|-----------------------|-----------------------|------|-----------------|----------|----------|-----------|----------|------|---------|

| 1          | -          | -          | -          | VDD                   | VDD                   |      |                 |          |          |           |          |      |         |

| 2          | _          | _          | _          | VSS                   | VSS                   |      |                 |          |          |           |          |      |         |

| 3          | _          | _          | _          | Disabled              | Disabled              | PTC6 | UART0_TX        | I2C0_SCL | RGPIO6   | SPI1_MOSI | FBa_AD11 |      |         |

| 4          | _          | _          | _          | Disabled              | Disabled              | PTC7 | UART0_RX        | I2C0_SDA | RGPI07   | SPI1_MISO | FBa_AD12 |      |         |

| 5          | 1          | _          | _          | Disabled              | Disabled              | PTD0 | UART0_CT<br>S_b | I2C1_SDA | RGPIO8   | SPI1_SCLK | FBa_AD13 |      |         |

| 6          | 2          | —          | _          | Disabled              | Disabled              | PTD1 | UART0_RT<br>S_b | I2C1_SCL | RGPIO9   | SPI1_SS   | FBa_AD14 |      |         |

| 7          | 3          | 1          | 1          | Disabled              | Disabled              | PTA0 |                 | I2C2_SCL | FTM1_CH0 | SPI0_SS   | FBa_AD15 |      |         |

| 8          | 4          | 2          | 2          | Disabled              | Disabled              | PTA1 |                 | I2C2_SDA | FTM1_CH1 |           | FBa_AD16 |      |         |

| 9          | 5          | 3          | 3          | Disabled              | Disabled              | PTA2 | UART1_TX        |          | FTM1_CH2 | SPI1_SS   |          |      |         |

| 10         | 6          | 4          | 4          | Disabled              | Disabled              | PTA3 | UART1_RX        |          | FTM1_CH3 | SPI1_SCLK |          |      | EZP_CLK |

| 11         | 7          | 5          | 5          | ADC0_DP1/<br>ADC0_SE2 | ADC0_DP1/<br>ADC0_SE2 | PTA4 | UART1_CT<br>S_b | I2C2_SCL | FTM1_CH4 | SPI1_MISO |          |      | EZP_DI  |

| 12         | 8          | 6          | 6          | ADC0_DM1/<br>ADC0_SE3 | ADC0_DM1/<br>ADC0_SE3 | PTA5 | UART1_RT<br>S_b | I2C2_SDA | FTM1_CH5 | SPI1_MOSI | CLKOUT   |      | EZP_DO  |

| 13         | 9          | 7          | 7          | VDDA                  | VDDA                  |      |                 |          |          |           |          |      |         |

| 14         | 10         | 8          | —          | VREFH                 | VREFH                 |      |                 |          |          |           |          |      |         |

| 15         | 11         | 9          | -          | VREF_OUT              | VREF_OUT              |      |                 |          |          |           |          |      |         |

| 16         | 12         | 10         | -          | VREFL                 | VREFL                 |      |                 |          |          |           |          |      |         |

| 17         | 13         | 11         | 8          | VSSA                  | VSSA                  |      |                 |          |          |           |          |      |         |

| 18         | 14         | 12         | 9          | DAC0_OUT              | DAC0_OUT              |      |                 |          |          |           |          |      |         |

| 19         | 15         | 13         | 10         | ADC0_DP0/<br>ADC0_SE0 | ADC0_DP0/<br>ADC0_SE0 |      |                 |          |          |           |          |      |         |

| 20         | 16         | 14         | 11         | ADC0_DM0/<br>ADC0_SE1 | ADC0_DM0/<br>ADC0_SE1 |      |                 |          |          |           |          |      |         |

| 21         | 17         | 15         | 12         | VREGIN                | VREGIN                |      |                 |          |          |           |          |      |         |

| 22         | 18         | 16         | 13         | VOUT33                | VOUT33                |      |                 |          |          |           |          |      |         |

• PTC1 is open drain.

Figure 23. 32-pin QFN

## 8.3 Module-by-module signals

### NOTE

- On PTB0, EZP\_MS\_b is active only during reset. Refer to the detailed boot description.

- PTC1 is open drain.

### Table 35. Module signals by GPIO port and pin

| 64-pin | 48-pin           | 44-pin 32-pin Port |  | Module signal(s) |     |  |  |  |

|--------|------------------|--------------------|--|------------------|-----|--|--|--|

|        | Power and ground |                    |  |                  |     |  |  |  |

| 1      |                  |                    |  |                  | VDD |  |  |  |

| 24     | 20               | 18                 |  |                  | VDD |  |  |  |

Table continues on the next page ...

### MCF51QM128 Data Sheet, Rev. 6, 01/2012.

Table 35. Module signals by GPIO port and pin (continued)

| 64-pin | 48-pin | 44-pin | 32-pin | Port | Module signal(s)          |

|--------|--------|--------|--------|------|---------------------------|

| 48     | 35     | 31     | 24     |      | VDD                       |

| 2      |        |        |        |      | VSS                       |

| 23     | 19     | 17     | 14     |      | VSS                       |

| 49     | 36     | 32     | 25     |      | VSS                       |

|        | 1 1    | Sys    | stem   | 1    |                           |

| 45     | 32     | 28     | 21     | PTB4 | BKGD/MS                   |

| 12     | 8      | 6      | 6      | PTA5 | CLKOUT                    |

| 62     | 46     | 42     | 30     | PTC3 | CLKOUT                    |

| 10     | 6      | 4      | 4      | PTA3 | EZP_CLK                   |

| 11     | 7      | 5      | 5      | PTA4 | EZP_DI                    |

| 12     | 8      | 6      | 6      | PTA5 | EZP_DO                    |

| 35     | 25     | 23     | 17     | PTB0 | IRQ/EZP_MS_b,<br>EZP_CS_b |

| 52     | 39     | 35     | 28     | PTC1 | RESET_b                   |

|        |        | 0      | SC     |      |                           |

| 50     | 37     | 33     | 26     | PTB7 | EXTAL1                    |

| 47     | 34     | 30     | 23     | PTB6 | EXTAL2                    |

| 51     | 38     | 34     | 27     | PTC0 | XTAL1                     |

| 46     | 33     | 29     | 22     | PTB5 | XTAL2                     |

|        |        | LL     | .wu    | 1    |                           |

| 4      |        |        |        | PTC7 | LLWU_P0                   |

| 6      | 2      |        |        | PTD1 | LLWU_P1                   |

| 12     | 8      | 6      | 6      | PTA5 | LLWU_P2                   |

| 30     | 23     | 21     | 16     | PTA7 | LLWU_P3                   |

| 32     |        |        |        | PTD7 | LLWU_P4                   |

| 35     | 25     | 23     | 17     | PTB0 | LLWU_P5                   |

| 36     | 26     | 24     | 18     | PTB1 | LLWU_P6                   |

| 39     | 27     | 25     | 19     | PTB2 | LLWU_P7                   |

| 44     | 31     | 27     |        | PTE7 | LLWU_P8                   |

| 45     | 32     | 28     | 21     | PTB4 | LLWU_P9                   |

| 55     |        |        |        | PTF2 | LLWU_P10                  |

| 56     | 40     | 36     |        | PTF3 | LLWU_P11                  |

| 57     | 41     | 37     | 29     | PTC2 | LLWU_P12                  |

| 59     | 43     | 39     |        | PTF5 | LLWU_P13                  |

| 62     | 46     | 42     | 30     | PTC3 | LLWU_P14                  |

Table continues on the next page...

| 64-pin | 48-pin | 44-pin | 32-pin | Port | Module signal(s) |

|--------|--------|--------|--------|------|------------------|

| 11     | 7      | 5      | 5      | PTA4 | PTA4             |

| 12     | 8      | 6      | 6      | PTA5 | PTA5             |

| 25     | 21     | 19     | 15     | PTA6 | PTA6             |

| 30     | 23     | 21     | 16     | PTA7 | PTA7             |

|        | ł      | F      | νтв    | 4    | 1                |

| 35     | 25     | 23     | 17     | PTB0 | PTB0             |

| 36     | 26     | 24     | 18     | PTB1 | PTB1             |

| 39     | 27     | 25     | 19     | PTB2 | PTB2             |

| 40     | 28     | 26     | 20     | PTB3 | PTB3             |

| 45     | 32     | 28     | 21     | PTB4 | PTB4             |

| 46     | 33     | 29     | 22     | PTB5 | PTB5             |

| 47     | 34     | 30     | 23     | PTB6 | PTB6             |

| 50     | 37     | 33     | 26     | PTB7 | PTB7             |

|        | 1      | F      | νтс    | 1    |                  |

| 51     | 38     | 34     | 27     | PTC0 | PTC0             |

| 52     | 39     | 35     | 28     | PTC1 | PTC1             |

| 57     | 41     | 37     | 29     | PTC2 | PTC2             |

| 62     | 46     | 42     | 30     | PTC3 | PTC3             |

| 63     | 47     | 43     | 31     | PTC4 | PTC4             |

| 64     | 48     | 44     | 32     | PTC5 | PTC5             |

| 3      |        |        |        | PTC6 | PTC6             |

| 4      |        |        |        | PTC7 | PTC7             |

|        |        | F      | PTD    | 1    |                  |

| 5      | 1      |        |        | PTD0 | PTD0             |

| 6      | 2      |        |        | PTD1 | PTD1             |

| 26     |        |        |        | PTD2 | PTD2             |

| 27     | 22     | 20     |        | PTD3 | PTD3             |

| 28     |        |        |        | PTD4 | PTD4             |

| 29     |        |        |        | PTD5 | PTD5             |

| 31     | 24     | 22     |        | PTD6 | PTD6             |

| 32     |        |        |        | PTD7 | PTD7             |

|        | 1      | l<br>F | PTE    | 1    | I                |

| 33     |        |        |        | PTE0 | PTE0             |

| 34     |        |        |        | PTE1 | PTE1             |

| 38     |        |        |        | PTE3 | PTE2             |

Table 35. Module signals by GPIO port and pin (continued)

Table continues on the next page ...

### How to Reach Us:

Home Page: www.freescale.com

Web Support: http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center 1-800-441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductors products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claims alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-complaint and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

$\label{eq:FreescaleTM} Freescale TM and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.$

© 2010–2012 Freescale Semiconductor, Inc.

Document Number: MCF51QM128 Rev. 6, 01/2012