#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | RL78                                                                            |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | CANbus, CSI, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 130                                                                             |

| Program Memory Size        | 192KB (192K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 8K x 8                                                                          |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                     |

| Data Converters            | A/D 31x10b; D/A 1x8b                                                            |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 144-LQFP                                                                        |

| Supplier Device Package    | 144-LFQFP (20x20)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f113thlfb-x0 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 7.2 I/O Pins                                                        | 533 |

|---------------------------------------------------------------------|-----|

| 7.3 Registers                                                       | 534 |

| 7.3.1 Peripheral enable register 1 (PER1)                           |     |

| 7.3.2 Operation speed mode control register (OSMC)                  |     |

| 7.3.3 Clock Select Register (CKSEL)                                 |     |

| 7.3.4 Timer RJ Counter Register 0 (TRJ0), Timer RJ Reload Register  |     |

| 7.3.5 Timer RJ Control Register 0 (TRJCR0)                          | 538 |

| 7.3.6 Timer RJ I/O Control Register 0 (TRJIOC0)                     |     |

| 7.3.7 Timer RJ Mode Register 0 (TRJMR0)                             |     |

| 7.3.8 Timer RJ Event Pin Select Register 0 (TRJISR0)                |     |

| 7.3.9 Port mode registers 1, 4 (PM1, PM4)                           |     |

| 7.4 Operation                                                       |     |

| 7.4.1 Reload Register and Counter Rewrite Operation                 | 545 |

| 7.4.2 Timer Mode                                                    | 546 |

| 7.4.3 Pulse Output Mode                                             |     |

| 7.4.4 Event Counter Mode                                            |     |

| 7.4.5 Pulse Width Measurement Mode                                  | 550 |

| 7.4.6 Pulse Period Measurement Mode                                 | 551 |

| 7.4.7 Coordination with Event Link Controller (ELC)                 | 552 |

| 7.4.8 Output Settings for Each Mode                                 | 552 |

| 7.5 Notes on Timer RJ                                               | 553 |

| 7.5.1 Count Operation Start and Stop Control                        | 553 |

| 7.5.2 Access to Flags (Bits TEDGF and TUNDF in TRJCR0 Register)     | 553 |

| 7.5.3 Access to Counter Register                                    | 553 |

| 7.5.4 When Changing Mode                                            | 553 |

| 7.5.5 Procedure for Setting Pins TRJO0 and TRJIO0                   | 554 |

| 7.5.6 When Timer RJ is not Used                                     | 554 |

| 7.5.7 When Timer RJ Operating Clock is Stopped                      | 554 |

| 7.5.8 Procedure for Setting STOP Mode (Event Counter Mode)          |     |

| 7.5.9 Functional Restriction in STOP Mode (Event Counter Mode Only) | 555 |

| 7.5.10 When Count is Forcibly Stopped by TSTOP Bit                  | 555 |

| 7.5.11 Digital Filter                                               | 555 |

| 7.5.12 When Selecting fIL as Count Source                           | 555 |

| IAPTER 8 TIMER RD                                                   |     |

| 8.1 Overview                                                        |     |

| 8.2 Registers                                                       | 558 |

| 8.2.1 Peripheral enable register 1 (PER1)                           | 559 |

| 8.2.2 Clock Select Register (CKSEL)                                 |     |

| 8.2.3 Timer RD ELC Register (TRDELC)                                |     |

| 8.2.4 Timer RD Start Register (TRDSTR)                              |     |

# 2.1.6 Pins for each product (pins other than port pins)

This subchapter shows the pins other than the ports shown in tables 2-2.

$\checkmark$  indicates the pin that is provided in the product and — indicates the pin that is not provided.

| Pin      | I/O   | Function                                                |              | Pi           | n Count      |              |              |

|----------|-------|---------------------------------------------------------|--------------|--------------|--------------|--------------|--------------|

| Function |       |                                                         | 144-pin      | 100-pin      | 80-pin       | 64-pin       | 48-pin       |

| ANI0     | Input | A/D converter analog input (V <sub>DD</sub> connection) | $\checkmark$ | $\checkmark$ |              | $\checkmark$ | $\checkmark$ |

| ANI1     | Input |                                                         | $\checkmark$ | $\checkmark$ |              | $\checkmark$ | $\checkmark$ |

| ANI2     | Input |                                                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| ANI3     | Input |                                                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| ANI4     | Input |                                                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| ANI5     | Input |                                                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| ANI6     | Input |                                                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| ANI7     | Input |                                                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| ANI8     | Input |                                                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| ANI9     | Input |                                                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| ANI10    | Input |                                                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| ANI11    | Input |                                                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| ANI12    | Input |                                                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| ANI13    | Input |                                                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | _            |

| ANI14    | Input |                                                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | _            |

| ANI15    | Input |                                                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | _            |

| ANI16    | Input |                                                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | —            |

| ANI17    | Input |                                                         | $\checkmark$ | $\checkmark$ | $\checkmark$ |              | _            |

| ANI18    | Input |                                                         | $\checkmark$ | $\checkmark$ | _            |              | _            |

| ANI19    | Input |                                                         | $\checkmark$ | $\checkmark$ | _            |              | _            |

| ANI20    | Input |                                                         | $\checkmark$ | $\checkmark$ | _            |              | _            |

| ANI21    | Input |                                                         |              |              | _            | —            | _            |

| ANI22    | Input |                                                         |              |              | _            | —            | _            |

| ANI23    | Input |                                                         | $\checkmark$ |              | _            |              | _            |

| ANI24    | Input | A/D converter analog input (EVDD connection)            | $\checkmark$ |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| ANI25    | Input |                                                         |              |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| ANI26    | Input |                                                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| ANI27    | Input |                                                         |              |              | $\checkmark$ | _            | $\checkmark$ |

| ANI28    | Input |                                                         |              |              | $\checkmark$ | _            | $\checkmark$ |

| ANI29    | Input |                                                         |              |              | $\checkmark$ | _            | _            |

| ANI30    | Input |                                                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | _            | _            |

| IVCMP00  | Input | Comparator analog voltage input                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| IVCMP01  | Input |                                                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| IVCMP02  | Input |                                                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| IVCMP03  | Input |                                                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| IVREF0   | Input | Comparator reference voltage input                      | $\checkmark$ |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

## Table 2-2. List of RL78/F15 Pins Other than Port Pins (1/5)

| Address | Special Function Register (2nd SFR) Name   | Sy        | rmbol    | R/W | Manip | After        |              |       |

|---------|--------------------------------------------|-----------|----------|-----|-------|--------------|--------------|-------|

|         |                                            |           |          |     | 1-bit | 8-bit        | 16-bit       | reset |

| F03D4H  | CAN receive buffer register 3BL Note 2     | RMTS3L    | RMTS3    | R   | -     | $\checkmark$ | $\checkmark$ | 0000H |

| F03D5H  |                                            | RMTS3H    |          |     | _     | $\checkmark$ |              |       |

| F03D6H  | CAN receive rule entry register 4BH Note 1 | GAFLMH4L  | GAFLMH4  | R/W | -     | $\checkmark$ | $\checkmark$ | 0000H |

| F03D7H  |                                            | GAFLMH4H  | _        |     | _     | $\checkmark$ |              |       |

| F03D6H  | CAN receive buffer register 3BH Note 2     | RMPTR3L   | RMPTR3   | R   | _     | $\checkmark$ | $\checkmark$ | 0000H |

| F03D7H  |                                            | RMPTR3H   | _        |     | _     | $\checkmark$ |              |       |

| F03D8H  | CAN receive rule entry register 4CL Note 1 | GAFLPL4L  | GAFLPL4  | R/W | _     | $\checkmark$ | $\checkmark$ | 0000H |

| F03D9H  |                                            | GAFLPL4H  | _        |     | _     | $\checkmark$ |              |       |

| F03D8H  | CAN receive buffer register 3CL Note 2     | RMDF03L   | RMDF03   | R   | _     | $\checkmark$ | $\checkmark$ | 0000H |

| F03D9H  |                                            | RMDF03H   | -        |     | _     | $\checkmark$ |              |       |

| F03DAH  | CAN receive rule entry register 4CH Note 1 | GAFLPH4L  | GAFLPH4  | R/W | _     |              |              | 0000H |

| F03DBH  |                                            | GAFLPH4H  | _        |     | _     |              |              |       |

| F03DAH  | CAN receive buffer register 3CH Note 2     | RMDF13L   | RMDF13   | R   | _     | $\checkmark$ | $\checkmark$ | 0000H |

| F03DBH  |                                            | RMDF13H   | -        |     | _     | $\checkmark$ |              |       |

| F03DCH  | CAN receive rule entry register 5AL Note 1 | GAFLIDL5L | GAFLIDL5 | R/W | _     | $\checkmark$ | $\checkmark$ | 0000H |

| F03DDH  | 1                                          | GAFLIDL5H | _        |     | _     | $\checkmark$ |              |       |

| F03DCH  | CAN receive buffer register 3DL Note 2     | RMDF23L   | RMDF23   | R   | _     | $\checkmark$ | $\checkmark$ | 0000H |

| F03DDH  |                                            | RMDF23H   | _        |     | _     | $\checkmark$ |              |       |

| F03DEH  | CAN receive rule entry register 5AH Note 1 | GAFLIDH5L | GAFLIDH5 | R/W | _     | $\checkmark$ | $\checkmark$ | 0000H |

| F03DFH  | 1                                          | GAFLIDH5H | _        |     | _     | $\checkmark$ |              |       |

| F03DEH  | CAN receive buffer register 3DH Note 2     | RMDF33L   | RMDF33   | R   | _     | $\checkmark$ | $\checkmark$ | 0000H |

| F03DFH  | 1                                          | RMDF33H   | _        |     | I     | $\checkmark$ |              |       |

| F03E0H  | CAN receive rule entry register 5BL Note 1 | GAFLML5L  | GAFLML5  | R/W | -     | $\checkmark$ | $\checkmark$ | 0000H |

| F03E1H  | ]                                          | GAFLML5H  |          |     | I     | $\checkmark$ |              |       |

| F03E0H  | CAN receive buffer register 4AL Note 2     | RMIDL4L   | RMIDL4   | R   | -     | $\checkmark$ | $\checkmark$ | 0000H |

| F03E1H  |                                            | RMIDL4H   |          |     | -     | $\checkmark$ |              |       |

| F03E2H  | CAN receive rule entry register 5BH Note 1 | GAFLMH5L  | GAFLMH5  | R/W | -     | $\checkmark$ | $\checkmark$ | 0000H |

| F03E3H  |                                            | GAFLMH5H  |          |     | ١     | $\checkmark$ |              |       |

| F03E2H  | CAN receive buffer register 4AH Note 2     | RMIDH4L   | RMIDH4   | R   | ١     | $\checkmark$ | $\checkmark$ | 0000H |

| F03E3H  |                                            | RMIDH4H   |          |     | -     | $\checkmark$ |              |       |

| F03E4H  | CAN receive rule entry register 5CL Note 1 | GAFLPL5L  | GAFLPL5  | R/W | ١     | $\checkmark$ | $\checkmark$ | 0000H |

| F03E5H  |                                            | GAFLPL5H  |          |     | ١     | $\checkmark$ |              |       |

| F03E4H  | CAN receive buffer register 4BL Note 2     | RMTS4L    | RMTS4    | R   | 1     | $\checkmark$ | $\checkmark$ | 0000H |

| F03E5H  |                                            | RMTS4H    |          |     | -     | $\checkmark$ |              |       |

| F03E6H  | CAN receive rule entry register 5CH Note 1 | GAFLPH5L  | GAFLPH5  | R/W | -     | $\checkmark$ | $\checkmark$ | 0000H |

| F03E7H  |                                            | GAFLPH5H  |          |     | -     | $\checkmark$ |              |       |

| F03E6H  | CAN receive buffer register 4BH Note 2     | RMPTR4L   | RMPTR4   | R   | 1     | $\checkmark$ | $\checkmark$ | 0000H |

| F03E7H  |                                            | RMPTR4H   |          |     | -     | $\checkmark$ |              |       |

| F03E8H  | CAN receive rule entry register 6AL Note 1 | GAFLIDL6L | GAFLIDL6 | R/W |       | $\checkmark$ | $\checkmark$ | 0000H |

| F03E9H  |                                            | GAFLIDL6H |          |     | -     | $\checkmark$ |              |       |

| F03E8H  | CAN receive buffer register 4CL Note 2     | RMDF04L   | RMDF04   | R   | -     | $\checkmark$ | $\checkmark$ | 0000H |

| F03E9H  |                                            | RMDF04H   |          |     | I     | $\checkmark$ |              |       |

| F03EAH  | CAN receive rule entry register 6AH Note 1 | GAFLIDH6L | GAFLIDH6 | R/W | -     | $\checkmark$ | $\checkmark$ | 0000H |

| F03EBH  |                                            | GAFLIDH6H |          |     | _     | $\checkmark$ |              |       |

| Table 3-6. | Extended SFR (2nd SFR) List (19/52) |

|------------|-------------------------------------|

|------------|-------------------------------------|

**Notes 1.** These registers are allocated to the RAM window 0 for the CAN module (receive rule and CAN RAM test register). When setting these registers, set the RPAGE bit in the GRWCR register to 0.

2. These registers are allocated to the RAM window 1 for the CAN module (receive buffer, receive FIFO buffer, transmit/receive FIFO buffer, transmit buffer, and transmit history data). When setting these registers, set the RPAGE bit in the GRWCR register to 1.

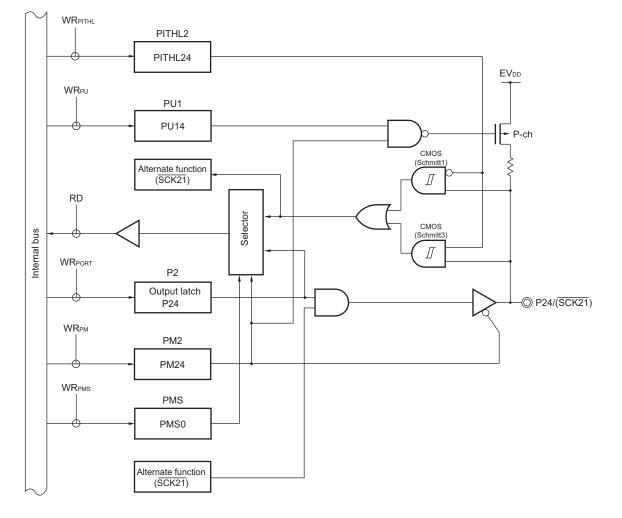

Figure 4-19. Block Diagram of P24

- P2: Port register 2

- PU2: Pull-up resistor option register 2

- PM2: Port mode register 2

- PMS: Port mode select register

- PITHL2: Port input threshold control register 2

- RD: Read signal

- WRxx: Write signal

# 4.3.9 Peripheral I/O redirection register 0 (PIOR0)

This register is used to specify whether to enable or disable the peripheral I/O redirect function.

PIOR0 enables or disables redirection of the timer array unit functions; that is, it specifies which I/O port is assigned to each input pin of timer array unit 0.

This register can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

#### Figure 4-100. Format of Peripheral I/O Redirection Register 0 (PIOR0)

| Address: F0016H Af |        | After reset: 00H | R/W    |        |        |        |        |        |

|--------------------|--------|------------------|--------|--------|--------|--------|--------|--------|

| Symbol             | 7      | 6                | 5      | 4      | 3      | 2      | 1      | 0      |

| PIOR0              | PIOR07 | PIOR06           | PIOR05 | PIOR04 | PIOR03 | PIOR02 | PIOR01 | PIOR00 |

| Bit    | Function  | 144      | -pin    | 100     | )-pin    | 80-     | pin     | 64-     | pin     | 48-     | pin     |

|--------|-----------|----------|---------|---------|----------|---------|---------|---------|---------|---------|---------|

|        |           | Setting  | g value | Setting | g value  | Setting | g value | Setting | g value | Setting | g value |

|        |           | 0 1      |         | 0       | 1        | 0       | 0 1     |         | 1       | 0       | 1       |

| PIOR07 | TI07      | P120     | P44     | P120    | P44      | P120    | P44     | P120    | _       | P120    | _       |

| PIOR06 | TI06      | P14      | P02     | P14     | P02      | P14     | P02     | P14     |         | P14     | _       |

| PIOR05 | TI05      | P15 P00  |         | P15     | P15 P00  |         | P00     | P15     | P00     | P15     | P00     |

| PIOR04 | TI04      | P13      | P01     | P13     | P01      | P13     | P01     | P13     |         | P13     | _       |

| PIOR03 | DR03 TI03 |          | P127    | P125    | P127     | P125    | _       | P125    |         | P125    | _       |

| PIOR02 | TI02      | P16      | P67     | P16     | P67      | P16     | P67     | P16     |         | P16     | _       |

| PIOR01 | TI01      | P30 P126 |         | P30     | P30 P126 |         | P126    | P30     |         | P30     | _       |

| PIOR00 | TI00      | P17      | P66     | P17     | P66      | P17     | P66     | P17     | _       | P17     |         |

- (3) Change the CPU from operating with the high-speed on-chip oscillator clock (B) or operating with the high-speed system clock (C) to operating with the subsystem clock (D).

- Set the RTCLPC bit of the OSMC register.

- Set the SELLOSC bit of the CKSEL register to 0.

- Set the CMC register (EXCLKS = x, OSCSELS = 1, AMPHS[1:0] = xx). Note

- Set the XTSTOP bit of the CSC register to 0.

- Wait for oscillation stabilization.

- Set the CSS bit of the CKC register to 1.

- Confirm that the CLS bit of the CKC register is set to 1.

- **Note** The clock operation mode control register (CMC) can be written only once by an 8-bit memory manipulation instruction after reset release.

- (4) Change the CPU from operating with the high-speed on-chip oscillator clock (B) or operating with the highspeed system clock (C) to operating with the low-speed on-chip oscillator clock (M).

- Set the SELLOSC bit of the CKSEL register to 1.

- Set the CMC register (EXCLKS = x, OSCSELS = 1). Note

- Set the CSS bit of the CKC register to 1.

- Confirm that the CLS bit of the CKC register is set to 1.

- **Note** The clock operation mode control register (CMC) can be written only once by an 8-bit memory manipulation instruction after reset release.

- (5) Change the CPU from operating with the high-speed on-chip oscillator clock (B) or operating with the highspeed system clock (C) to operating with the PLL clock (K).

- Set the PLLCTL register (PLLDIV1 = x, LCKSEL[1:0] = xx, PLLDIV0 = x, PLLMUL = x).

- Wait for the selection of the PLL multiplication value to become effective (After setting the PLLMUL bit, wait for at least 1 μs).

- Set the PLLON bit of the PLLCTL register to 1.

- Confirm that the LOCK bit of the PLLSTS register is set to 1 (checking PLL locked state).

- Set the MDIV [2:0] bits of the MDIV register.

- Set the SELPLL bit of the PLLCTL register to 1.

- Confirm that the SELPLLS bit of the PLLSTS register is set to 1.

- (6) Change the CPU from operating with the high-speed system clock (C) to operating with the high-speed onchip oscillator clock (B).

- Set the HIOSTOP bit of the CSC register to 0. Note

- Set the MCM0 bit of the CKC register to 0.

- Confirm that the MCS bit of the CKC register is set to 0.

- Note When oscillation starts from a high-speed on-chip oscillator clock stop state (HIOSTOP = 1), have the software wait for the following oscillation accuracy stabilization time, and then change the clock.

FRQSEL4 of the user option byte (000C2H/020C2H) = 0: 18 μs to 65 μs

FRQSEL4 of the user option byte (000C2H/020C2H) = 1: 18 μs to 105 μs

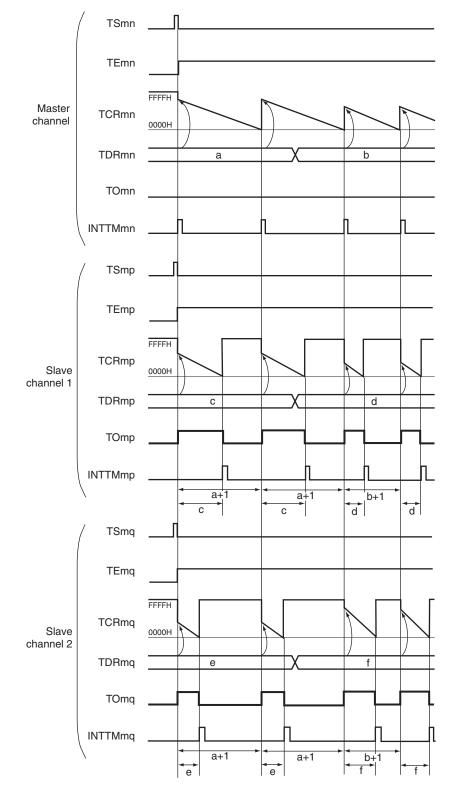

Figure 6-80 Example of Basic Timing of Operation as Multiple PWM Output Function (Output two types of PWMs)

(Remarks are listed on the next page.)

# 8.2.9 Timer RD Output Master Enable Register 2 (TRDOER2)

# Figure 8-10. Format of Timer RD Output Master Enable Register 2 (TRDOER2) [PWM Function, Reset Synchronous PWM Mode, Complementary PWM Mode, and PWM3 Mode]

Address: F0268H After Reset: 00H Note 1

| Symbol  | <7>    | 6 | 5 | 4 | 3 | 2 | 1 | <0>      |

|---------|--------|---|---|---|---|---|---|----------|

| TRDOER2 | TRDPTO | 0 | 0 | 0 | 0 | 0 | 0 | TRDSHUTS |

| TRDPTO | INTP0 of pulse output forced cutoff signal input enabled Note 2              | R/W |

|--------|------------------------------------------------------------------------------|-----|

| 0      | Pulse output forced cutoff input disabled                                    | R/W |

| 1      | Pulse output forced cutoff input enabled                                     |     |

|        | (The TRDSHUTS bit is set to 1 when a low level is applied to the INTP0 pin.) |     |

| Bits 6 to 1 | Nothing is assigned                             | R/W |

|-------------|-------------------------------------------------|-----|

| _           | The write value must be 0. The read value is 0. | R   |

| TRDSHUTS                                                                                                | Forced cutoff flag                                                                      | R/W |  |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----|--|--|--|--|--|--|--|--|

| 0                                                                                                       | Not forcibly cut off                                                                    | R/W |  |  |  |  |  |  |  |  |

| 1                                                                                                       | 1 Forcibly cut off                                                                      |     |  |  |  |  |  |  |  |  |

| This bit is set to 1 when the pulse is forcibly cut off by an INTP0 or ELC input event. This bit is not |                                                                                         |     |  |  |  |  |  |  |  |  |

| automatically                                                                                           | cleared. To stop the forced cutoff of the pulse, write 0 to this bit while the count is |     |  |  |  |  |  |  |  |  |

| stopped (TSTARTi = 0). The pulse is also forcibly cut off when 1 is written to the TRDSHUTS bit in      |                                                                                         |     |  |  |  |  |  |  |  |  |

| an enabled m                                                                                            | node.                                                                                   |     |  |  |  |  |  |  |  |  |

- **Notes 1.** The value after reset is undefined when FRQSEL4 = 1 in the user option byte (000C2H/020C2H) and TRD0EN = 0 in the PER1 register. If it is necessary to read the initial value, set fclk to fiH and TRD0EN = 1 before reading.

- 2. See 8.3.1 (4) Pulse Output Forced Cutoff.

# 14.2.5 A/D port configuration register (ADPC)

This register switches the ANI0/P33 to ANI23/P105 pins to digital I/O of port or analog input.

When the comparator is in use, set the pins selected from among P81/ANI3/IVCMP00, P82/ANI4/IVCMP01, P83/ANI5/IVCMP02, P84/ANI6/IVCMP03, and P85/ANI7/IVREF0 to analog input by using the ADPC register.

The ADPC register can be set by an 8-bit memory manipulation instruction.

Reset signal generation sets this register to 00H.

## Figure 14-6. Format of A/D Port Configuration Register (ADPC)

| A        | Address: F0076H After reset: 00H |       |       |       |            |            |            |            |            |            |           |           |           |           |           |           |           |           |          |          |                 |                  |                  |                  |                  |               |          |          |

|----------|----------------------------------|-------|-------|-------|------------|------------|------------|------------|------------|------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|----------|----------|-----------------|------------------|------------------|------------------|------------------|---------------|----------|----------|

| Symbol 7 |                                  |       |       |       |            |            | 6          |            |            |            | 5         |           |           | 4         |           |           | 3         |           |          | 2        |                 |                  | 1                |                  |                  | 0             |          |          |

|          | AD                               | PC    | Γ     |       | 0          |            |            | 0          |            | 0          |           |           | ADPC4     |           | Ļ         | ADPC3     |           |           | ADPC2    |          |                 | ADPC1            |                  |                  | ADPC0            |               |          |          |

|          |                                  |       | -     |       |            |            |            |            |            |            |           |           |           |           |           |           |           |           |          |          |                 |                  |                  |                  |                  |               |          |          |

|          |                                  |       |       |       |            |            |            |            |            |            |           |           | Analo     | og inp    | out (A    | )/dig     | ital I/0  | ) (D      | swite    | ching    |                 |                  |                  |                  |                  |               |          |          |

| ADPC4    | ADPC3                            | ADPC2 | ADPC1 | ADPC0 | ANI23/P105 | ANI22/P104 | ANI21/P103 | ANI20/P102 | ANI19/P101 | ANI18/P100 | ANI17/P97 | ANI16/P96 | ANI15/P95 | ANI14/P94 | ANI13/P93 | ANI12/P92 | ANI11/P91 | ANI10/P90 | ANI9/P87 | ANI8/P86 | ANI7/IVREF0/P85 | ANI6/IVCMP03/P84 | ANI5/IVCMP02/P83 | ANI4/IVCMP01/P82 | ANI3/IVCMP00/P81 | ANI2/ANO0/P80 | ANI1/P34 | ANI0/P33 |

| 0        | 0                                | 0     | 0     | 0     | Α          | А          | Α          | Α          | Α          | А          | А         | А         | А         | А         | Α         | Α         | Α         | Α         | А        | Α        | Α               | Α                | А                | А                | А                | А             | А        | Α        |

| 0        | 0                                | 0     | 0     | 1     | D          | D          | D          | D          | D          | D          | D         | D         | D         | D         | D         | D         | D         | D         | D        | D        | D               | D                | D                | D                | D                | D             | D        | D        |

| 0        | 0                                | 0     | 1     | 0     | D          | D          | D          | D          | D          | D          | D         | D         | D         | D         | D         | D         | D         | D         | D        | D        | D               | D                | D                | D                | D                | D             | D        | Α        |

| 0        | 0                                | 0     | 1     | 1     | D          | D          | D          | D          | D          | D          | D         | D         | D         | D         | D         | D         | D         | D         | D        | D        | D               | D                | D                | D                | D                | D             | Α        | Α        |

| 0        | 0                                | 1     | 0     | 0     | D          | D          | D          | D          | D          | D          | D         | D         | D         | D         | D         | D         | D         | D         | D        | D        | D               | D                | D                | D                | D                | Α             | Α        | Α        |

| 0        | 0                                | 1     | 0     | 1     | D          | D          | D          | D          | D          | D          | D         | D         | D         | D         | D         | D         | D         | D         | D        | D        | D               | D                | D                | D                | Α                | Α             | Α        | Α        |

| 0        | 0                                | 1     | 1     | 0     | D          | D          | D          | D          | D          | D          | D         | D         | D         | D         | D         | D         | D         | D         | D        | D        | D               | D                | D                | А                | Α                | Α             | Α        | Α        |

| 0        | 0                                | 1     | 1     | 1     | D          | D          | D          | D          | D          | D          | D         | D         | D         | D         | D         | D         | D         | D         | D        | D        | D               | D                | Α                | А                | Α                | Α             | Α        | Α        |

| 0        | 1                                | 0     | 0     | 0     | D          | D          | D          | D          | D          | D          | D         | D         | D         | D         | D         | D         | D         | D         | D        | D        | D               | Α                | Α                | А                | Α                | Α             | Α        | Α        |

| 0        | 1                                | 0     | 0     | 1     | D          | D          | D          | D          | D          | D          | D         | D         | D         | D         | D         | D         | D         | D         | D        | D        | Α               | Α                | А                | А                | А                | Α             | Α        | Α        |

| 0        | 1                                | 0     | 1     | 0     | D          | D          | D          | D          | D          | D          | D         | D         | D         | D         | D         | D         | D         | D         | D        | Α        | Α               | Α                | Α                | А                | Α                | Α             | Α        | Α        |

| 0        | 1                                | 0     | 1     | 1     | D          | D          | D          | D          | D          | D          | D         | D         | D         | D         | D         | D         | D         | D         | Α        | Α        | Α               | Α                | Α                | Α                | Α                | Α             | Α        | Α        |

| 0        | 1                                | 1     | 0     | 0     | D          | D          | D          | D          | D          | D          | D         | D         | D         | D         | D         | D         | D         | Α         | Α        | Α        | Α               | Α                | Α                | Α                | Α                | Α             | Α        | Α        |

| 0        | 1                                | 1     | 0     | 1     | D          | D          | D          | D          | D          | D          | D         | D         | D         | D         | D         | D         | Α         | Α         | Α        | Α        | Α               | Α                | А                | А                | А                | А             | Α        | Α        |

| 0        | 1                                | 1     | 1     | 0     | D          | D          | D          | D          | D          | D          | D         | D         | D         | D         | D         | Α         | Α         | Α         | Α        | Α        | Α               | Α                | А                | А                | А                | А             | Α        | Α        |

| 0        | 1                                | 1     | 1     | 1     | D          | D          | D          | D          | D          | D          | D         | D         | D         | D         | Α         | Α         | Α         | Α         | Α        | Α        | Α               | Α                | Α                | А                | А                | А             | Α        | Α        |

| 1        | 0                                | 0     | 0     | 0     | D          | D          | D          | D          | D          | D          | D         | D         | D         | Α         | Α         | Α         | А         | Α         | Α        | Α        | Α               | Α                | А                | Α                | Α                | Α             | Α        | Α        |

| 1        | 0                                | 0     | 0     | 1     | D          | D          | D          | D          | D          | D          | D         | D         | Α         | Α         | Α         | Α         | Α         | Α         | Α        | Α        | Α               | Α                | Α                | Α                | Α                | Α             | Α        | Α        |

| 1        | 0                                | 0     | 1     | 0     | D          | D          | D          | D          | D          | D          | D         | Α         | Α         | Α         | Α         | Α         | Α         | Α         | Α        | Α        | Α               | Α                | Α                | Α                | Α                | Α             | Α        | Α        |

| 1        | 0                                | 0     | 1     | 1     | D          | D          | D          | D          | D          | D          | Α         | Α         | Α         | Α         | Α         | Α         | Α         | Α         | Α        | Α        | Α               | Α                | Α                | Α                | Α                | Α             | Α        | Α        |

| 1        | 0                                | 1     | 0     | 0     | D          | D          | D          | D          | D          | Α          | Α         | Α         | Α         | Α         | Α         | Α         | Α         | Α         | Α        | Α        | Α               | Α                | Α                | Α                | Α                | Α             | Α        | Α        |

| 1        | 0                                | 1     | 0     | 1     | D          | D          | D          | D          | Α          | Α          | Α         | Α         | Α         | Α         | Α         | Α         | Α         | Α         | Α        | Α        | Α               | Α                | Α                | Α                | Α                | Α             | Α        | Α        |

| 1        | 0                                | 1     | 1     | 0     | D          | D          | D          | Α          | Α          | А          | Α         | Α         | Α         | Α         | Α         | Α         | Α         | Α         | А        | Α        | Α               | Α                | Α                | Α                | Α                | Α             | А        | Α        |

| 1        | 0                                | 1     | 1     | 1     | D          | D          | Α          | Α          | Α          | Α          | Α         | Α         | Α         | Α         | Α         | Α         | Α         | Α         | Α        | Α        | Α               | Α                | Α                | Α                | Α                | Α             | Α        | Α        |

| 1        | 1                                | 0     | 0     | 0     | D          | А          | Α          | Α          | А          | А          | А         | А         | А         | А         | А         | Α         | Α         | А         | А        | Α        | Α               | Α                | А                | А                | А                | А             | А        | Α        |

| 0        | ther                             | than  | abov  | /e    |            |            |            |            |            |            |           |           |           |           | Set       | ing p     | rohib     | ited      |          |          |                 |                  |                  |                  |                  |               |          |          |

Caution Set the pins to be used for the comparator (P81/ANI3/IVCMP00, P82/ANI4/IVCMP01, P83/ANI5/IVCMP02, P84/ANI6/IVCMP03, and P85/ANI7/IVREF0) to the input mode by using port mode registers 8 (PM8).

RENESAS

#### 16.4.2 Setting transfer clock by using IICWL0 and IICWH0 registers

#### (1) Setting transfer clock on master side

| Transfer clock = | fмск                             |

|------------------|----------------------------------|

|                  | IICWL0 + IICWH0 + fмск (tr + tr) |

At this time, the optimal setting values of the IICWL0 and IICWH0 registers are as follows. (The fractional parts of all setting values are rounded up.)

• When the fast mode

$$\begin{split} \text{IICWL0} = \frac{0.52}{\text{Transfer clock}} \times \text{f}_{\text{MCK}} \\ \text{IICWH0} = (\frac{0.48}{\text{Transfer clock}} - \text{t}_{\text{R}} - \text{t}_{\text{F}}) \times \text{f}_{\text{MCK}} \end{split}$$

• When the normal mode

$$IICWL0 = \frac{0.47}{Transfer clock} \times f_{MCK}$$

$$IICWH0 = (\frac{0.53}{Transfer clock} - t_R - t_F) \times f_{MCK}$$

• When the fast mode plus

$$\begin{split} \text{IICWL0} = \frac{0.50}{\text{Transfer clock}} \times \text{f}_{\text{MCK}} \\ \text{IICWH0} = (\frac{0.50}{\text{Transfer clock}} - \text{t}_{\text{R}} - \text{t}_{\text{F}}) \times \text{f}_{\text{MCK}} \end{split}$$

(2) Setting IICWL0 and IICWH0 registers on slave side

(The fractional parts of all setting values are truncated.)

When the fast mode

IICWL0 = 1.3  $\mu$ s × fmck IICWH0 = (1.2  $\mu$ s – tr – tr) × fmck

When the normal mode

IICWL0 = 4.7  $\mu$ s × fmck IICWH0 = (5.3  $\mu$ s - tr - tr) × fmck

• When the fast mode plus

IICWL0 = 0.50  $\mu$ s × fmck IICWH0 = (0.50  $\mu$ s – tr – tf) × fmck

(Cautions and Remarks are listed on the next page.)

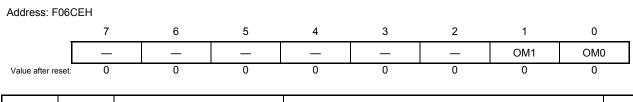

# (16) LIN/UART Control Register (LCUCn)

| Bit    | Symbol | Bit Name        | Function                                                             | R/W |

|--------|--------|-----------------|----------------------------------------------------------------------|-----|

| 0      | OM0    | LIN Reset       | 0: LIN reset mode is caused.<br>1: LIN reset mode is canceled.       | R/W |

| 1      | OM1    | LIN Mode Select | 0: LIN wake-up mode is caused.<br>1: LIN operation mode is caused.   | R/W |

| 7 to 2 | —      | Reserved        | These bits are always read as 0. The write value should always be 0. | R/W |

Set the LCUCn register to 01H to cause a transition to LIN wake-up mode after canceling LIN reset mode, and set the LCUCn register to 03H to cause a transition to LIN operation mode.

In LIN self-test mode, set the LCUCn register to 03H after a transition to LIN self-test mode is completed.

After a value is written to this register, confirm that the value written is actually indicated in the LMSTn register before writing another value.

## OM0 bit (LIN reset bit)

The OM0 bit selects either causing a transition to LIN reset mode or canceling LIN reset mode.

With 0 set, LIN reset mode is caused.

With 1 set, LIN reset mode is canceled.

#### OM1 bit (LIN mode select bit)

The OM1 bit selects the specific operation mode (either LIN wake-up mode or LIN operation mode) after canceling LIN reset mode.

With 0 set, LIN wake-up mode is caused.

With 1 set, LIN operation mode is caused.

This register is valid only when the OMM0 bit in the LMSTn register is 1.

Writing a value to this bit is disabled while the FTS bit in the LTRCn register is 1.

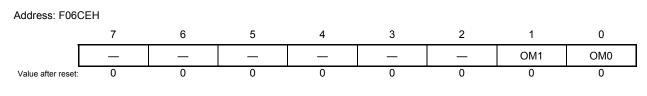

# (15) LIN/UART Control Register (LCUCn)

| Bit    | Symbol | Bit Name        | Function                                                             | R/W |

|--------|--------|-----------------|----------------------------------------------------------------------|-----|

| 0      | OM0    | LIN Reset       | 0: LIN reset mode is caused.<br>1: LIN reset mode is canceled.       | R/W |

| 1      | OM1    | LIN Mode Select | 0: LIN wake-up mode is caused.<br>1: LIN operation mode is caused.   | R/W |

| 7 to 2 | —      | Reserved        | These bits are always read as 0. The write value should always be 0. | R/W |

Set the LCUCn register to 01H to cause a transition to LIN wake-up mode after canceling LIN reset mode, and set the LCUCn register to 03H to cause a transition to LIN operation mode.

In LIN self-test mode, set the LCUCn register to 03H after a transition to LIN self-test mode is completed.

When the LIN/UART module makes a transition from the LIN operating mode to the LIN reset mode while operating as a LIN slave (at a fixed baud rate), write 1 to the LIN0EN bit (or the LIN1EN bit) in the PER2 register after having cleared the given bit to 0.

After a value is written to this register, confirm that the value written is actually indicated in the LMSTn register before writing another value.

## OM0 bit (LIN reset bit)

The OM0 bit selects either causing a transition to LIN reset mode or canceling LIN reset mode.

With 0 set, LIN reset mode is caused.

With 1 set, LIN reset mode is canceled.

# OM1 bit (LIN mode select bit)

The OM1 bit selects the specific operation mode (either LIN wake-up mode or LIN operation mode) after canceling LIN reset mode.

With 0 set, LIN wake-up mode is caused.

With 1 set, LIN operation mode is caused.

This register is valid only when the OMM0 bit in the LMSTn register is 1.

Writing a value to this bit is disabled while the FTS bit in the LTRCn register is 1.

# (23) LIN/UART Data Buffer m Register (LDBnm) (m = 1 to 8)

| Address: LDBn1 F06D8H, LDBn2 F06D9H, LDBn3 F06DAH, LDBn4 F06DBH, LDBn5 F06DCH, LDBn6 F06DDH, LDBn7 F06DEH, LDBn8 F06DFH |                                                                         |   |   |   |   |   |   |                  |     |

|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---|---|---|---|---|---|------------------|-----|

|                                                                                                                         | 7                                                                       | 6 | 5 | 4 | 3 | 2 | 1 | 0                |     |

|                                                                                                                         |                                                                         |   |   |   |   |   |   |                  |     |

| Value after re                                                                                                          | Value after reset: 0 0 0 0 0 0 0 0                                      |   |   |   |   |   |   | 0                |     |

| Bit                                                                                                                     | Function                                                                |   |   |   |   |   |   | Setting<br>Range | R/W |

| 7 to 0                                                                                                                  | Sets the data to be transmitted or allows the received data to be read. |   |   |   |   |   |   | 00H to FFH       | R/W |

For response transmission:

These registers set the data to be transmitted in the response field.

Set these registers when the RTS bit is 0 (response reception/transmission is halted).

For response reception:

These registers hold the data received in the response field.

The received data is overwritten. If an error is detected, the data prior to reception interruption is stored in the register. Do not read these registers when the RTS bit is 1 (response transmission/reception is started)

In LIN self-test mode, this register operates as follows:

Write the value to be transmitted before communication. The reversed value of the value received can be read from the register after frame transmission/reception is completed (after loopback).

For details of LIN self-test mode, refer to 17.6 LIN Self-Test Mode.

# Figure 22-3. Format of Interrupt Mask Flag Registers (MK0L, MK0H, MK1L, MK1H, MK2L, MK2H, MK3L, MK3H) (2/2)

| Address: FFF | D7H Afte                                                                   | r reset: FFH | R/W |                    |     |           |           |           |  |

|--------------|----------------------------------------------------------------------------|--------------|-----|--------------------|-----|-----------|-----------|-----------|--|

| Symbol       | 7                                                                          | 6            | 5   | <4>                | <3> | <2>       | <1>       | <0>       |  |

| МКЗН         | -                                                                          | _            | _   | PMK14<br>LIN2WUPMK | -   | CAN1CFRMK | CAN1WUPMK | CAN1ERRMK |  |

|              | MKxx Interrupt servicing control                                           |              |     |                    |     |           |           |           |  |

|              | 0     Interrupt servicing enabled       1     Interrupt servicing disabled |              |     |                    |     |           |           |           |  |

|              |                                                                            |              |     |                    |     |           |           |           |  |

Caution The above is the bit layout for the 144-pin. The available bits differ depending on the product. For details about the bits available for each product, see Table 22-2. Be sure to set bits that are not available to 1.

| H/<br>Item                 | ALT Mode Setting |                                                                                                                                                                                                                     | kecuted While CPU Is Operating<br>ystem Clock                    | When HALT Instruction Is<br>Executed While CPU Is           |  |  |  |

|----------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------|--|--|--|

|                            |                  | When CPU Is Operating on XT1 Clock (fxr)                                                                                                                                                                            | When CPU Is Operating on<br>External<br>Subsystem Clock (fexs)   | Operating on Low-speed<br>On-chip Oscillator Clock<br>(fiL) |  |  |  |

| System clock               |                  | Clock supply to the CPU is s                                                                                                                                                                                        | topped                                                           |                                                             |  |  |  |

| Main system clock          | fıн              | Operation disabled                                                                                                                                                                                                  |                                                                  |                                                             |  |  |  |

|                            | fx               |                                                                                                                                                                                                                     |                                                                  |                                                             |  |  |  |

|                            | fex              |                                                                                                                                                                                                                     |                                                                  |                                                             |  |  |  |

|                            | fpll             |                                                                                                                                                                                                                     |                                                                  |                                                             |  |  |  |

| Subsystem clock            | fхт              | Operation continues<br>(cannot be stopped)                                                                                                                                                                          | Cannot operate                                                   | Cannot operate                                              |  |  |  |

|                            | fexs             | Cannot operate                                                                                                                                                                                                      | Operation continues (cannot be stopped)                          |                                                             |  |  |  |

| fı∟                        |                  |                                                                                                                                                                                                                     | hip debug option byte (000C3H/02<br>4 (WUTMMCK0) of the OSMC reg |                                                             |  |  |  |

|                            |                  | • WUTMMCK0 = 1: Oscillate                                                                                                                                                                                           |                                                                  |                                                             |  |  |  |

|                            |                  | WUTMMCK0 = 0 and SELL                                                                                                                                                                                               |                                                                  |                                                             |  |  |  |

|                            |                  |                                                                                                                                                                                                                     | C = 0, and HPIEN = 1: Oscillates                                 |                                                             |  |  |  |

| <b>6</b>                   |                  |                                                                                                                                                                                                                     | C = 0, and HPIEN = 0: Stops                                      |                                                             |  |  |  |

| fwbт                       |                  | <ul> <li>Set by bits 0 (WDSTBYON) and 4 (WDTON) of user option byte (000C0H/020C0H)</li> <li>WDTON = 0: Stops</li> <li>WDTON = 1 and WDSTBYON = 1: Oscillates</li> <li>WDTON = 1 and WDSTBYON = 0: Stops</li> </ul> |                                                                  |                                                             |  |  |  |

| CPU                        |                  | Operation stopped                                                                                                                                                                                                   |                                                                  |                                                             |  |  |  |

| Code flash memory          |                  |                                                                                                                                                                                                                     |                                                                  |                                                             |  |  |  |

| Data flash memory          |                  |                                                                                                                                                                                                                     |                                                                  |                                                             |  |  |  |

| RAM                        |                  | Operation stopped (operation can continue during DTC transfer)                                                                                                                                                      |                                                                  |                                                             |  |  |  |

| Port (latch)               |                  | Status before HALT mode was set is retained                                                                                                                                                                         |                                                                  |                                                             |  |  |  |

| Timer array unit           |                  | Operable (Operation is disabled while in the low consumption RTC mode)                                                                                                                                              |                                                                  |                                                             |  |  |  |

| Real-time clock (RTC)      |                  | Operable                                                                                                                                                                                                            |                                                                  |                                                             |  |  |  |

| Watchdog timer             |                  | See CHAPTER 11 WATCHDOG TIMER                                                                                                                                                                                       |                                                                  |                                                             |  |  |  |

| Clock monitor              |                  | Operation stopped                                                                                                                                                                                                   |                                                                  |                                                             |  |  |  |

| Timer RJ                   |                  | Operable (Operation is disabled while in the low consumption RTC mode)                                                                                                                                              |                                                                  |                                                             |  |  |  |

| Timer RD                   |                  | ]                                                                                                                                                                                                                   |                                                                  |                                                             |  |  |  |

| Clock output/buzzer output | ıt               |                                                                                                                                                                                                                     |                                                                  |                                                             |  |  |  |

| A/D converter              |                  | Operation disabled                                                                                                                                                                                                  |                                                                  |                                                             |  |  |  |

| D/A converter              |                  |                                                                                                                                                                                                                     |                                                                  |                                                             |  |  |  |

| Comparator                 |                  |                                                                                                                                                                                                                     |                                                                  |                                                             |  |  |  |

| Serial array unit (SAU)    |                  | Operable (Operation is disabled while in the low consumption RTC mode)                                                                                                                                              |                                                                  |                                                             |  |  |  |

| Serial interface (IICA)    |                  | Operation disabled                                                                                                                                                                                                  |                                                                  |                                                             |  |  |  |

| DTC                        |                  | Operable                                                                                                                                                                                                            |                                                                  |                                                             |  |  |  |

| ELC                        |                  | Linking between operational function blocks is possible.                                                                                                                                                            |                                                                  |                                                             |  |  |  |

| LIN/UART module (RLIN3     | ,                | Operation disabled                                                                                                                                                                                                  |                                                                  |                                                             |  |  |  |

| CAN interface (RS-CAN li   | te)              | 4                                                                                                                                                                                                                   |                                                                  |                                                             |  |  |  |

| IEBus Controller           |                  |                                                                                                                                                                                                                     |                                                                  |                                                             |  |  |  |

| Power-on-reset function    |                  | Operable                                                                                                                                                                                                            |                                                                  |                                                             |  |  |  |

| Voltage detection function | 1                |                                                                                                                                                                                                                     |                                                                  |                                                             |  |  |  |

| External interrupt         |                  |                                                                                                                                                                                                                     |                                                                  |                                                             |  |  |  |

| Key interrupt function     |                  |                                                                                                                                                                                                                     |                                                                  |                                                             |  |  |  |

# Table 24-1. Operating Statuses in HALT Mode (2/2)

# CHAPTER 26 POWER-ON-RESET CIRCUIT

# 26.1 Functions of Power-on-reset Circuit

The power-on-reset circuit (POR) has the following functions.

- Generates internal reset signal at power on.

The reset signal is released when the supply voltage (VDD) exceeds 1.56 V (typ.).

- Compares supply voltage (V<sub>DD</sub>) and detection voltage (V<sub>PDR</sub> = 1.55 V (typ.)), generates internal reset signal when V<sub>DD</sub> < V<sub>PDR</sub>.

- Caution If an internal reset signal is generated in the POR circuit, the POCRES\_0 and CLKRF flags of the POR/CLM reset confirmation register (POCRES) and the TRAP, WDCLRF, IAWRF, and LVIRF flags of the reset control flag register (RESF) are cleared (00H).

- **Remark** This product incorporates multiple hardware functions that generate an internal reset signal. A flag that indicates the reset source is located in the RESF and POCRES registers for when an internal reset signal is generated by the power-on reset (POR), watchdog timer (WDT), clock monitor, voltage detector (LVD), illegal instruction execution, or illegal-memory access. The RESF register is not cleared to 00H and the flag is set to 1 when an internal reset signal is generated by the watchdog timer (WDT), voltage detector (LVD), illegal instruction execution, clock monitor, or illegal-memory access. The POCRES register is not cleared to 00H and the flag is set to 1 when an internal reset signal is generated by the watchdog timer (WDT), voltage detector (LVD), illegal instruction execution, clock monitor, or illegal-memory access. The POCRES register is not cleared to 00H and the flag is set to 1 when an internal reset signal is generated by the clock monitor. For details of the POCRES and RESF registers, see **CHAPTER 25 RESET FUNCTION**.

### 28.3.4 CPU stack pointer monitor function

The CPU stack pointer monitor is used to detect overflows and underflows of the stack pointer and to generate interrupts in response.

#### Caution The CPU stack pointer monitor function is disabled during on-chip debugging.

## <Configuration>

This function has the following functions.

- SP overflow/underflow detection function

- SP overflow/underflow interrupt output function

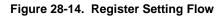

When the SPM enable bit (SPMEN) is 1, an interrupt signal (INTSPM) is generated if the monitored stack pointer value is greater than the specified SFR value (SPOFR) or smaller than the specified SFR value (SPUFR).

When the SPM enable bit (SPMEN) is 1, writing to the SPOFR and SPUFR registers is invalid.

#### <Register setting method>

Figure 28-14 shows the register setting method of this function.

| Instruction | Mnemon | Operands                 | Bytes | Bytes Clocks Note 1 Note 2 |               | Clocks                                                    |   | Flag |    |

|-------------|--------|--------------------------|-------|----------------------------|---------------|-----------------------------------------------------------|---|------|----|

| Group       | ic     |                          |       |                            |               |                                                           | Ζ | AC   | CY |

| Stack       | PUSH   | PSW                      | 2     | 1                          | _             | $(SP - 1) \leftarrow PSW$ , $(SP - 2) \leftarrow 00H$ ,   |   |      |    |

| manipulate  |        |                          |       |                            |               | $SP \leftarrow SP-2$                                      |   |      |    |

|             |        | rp                       | 1     | 1                          | -             | $(SP - 1) \leftarrow rp_{H}, (SP - 2) \leftarrow rp_{L},$ |   |      |    |

|             |        |                          |       |                            |               | $SP \leftarrow SP - 2$                                    |   |      |    |

|             | POP    | PSW                      | 2     | 3                          | -             | $PSW \gets (SP+1),  SP \gets SP+2$                        | R | R    | R  |

|             |        | rp                       | 1     | 1                          | _             | rp∟←(SP), rp⊢← (SP+1), SP ← SP + 2                        |   |      |    |

|             | MOVW   | SP, #word                | 4     | 1                          | -             | $SP \gets word$                                           |   |      |    |

|             |        | SP, AX                   | 2     | 1                          | -             | $SP \gets AX$                                             |   |      |    |

|             |        | AX, SP                   | 2     | 1                          | -             | $AX \leftarrow SP$                                        |   |      |    |

|             |        | HL, SP                   | 3     | 1                          | -             | $HL \leftarrow SP$                                        |   |      |    |

|             |        | BC, SP                   | 3     | 1                          | -             | $BC \gets SP$                                             |   |      |    |

|             | DE, SP | 3                        | 1     | _                          | $DE \gets SP$ |                                                           |   |      |    |

|             | ADDW   | SP, #byte                | 2     | 1                          | -             | $SP \leftarrow SP + byte$                                 |   |      |    |

| SUBW        | SUBW   | SP, #byte                | 2     | 1                          | _             | $SP \leftarrow SP$ – byte                                 |   |      |    |

| Unconditio  | BR     | AX                       | 2     | 3                          | -             | $PC \gets CS, AX$                                         |   |      |    |

| nal branch  |        | \$addr20                 | 2     | 3                          | _             | $PC \gets PC + 2 + jdisp8$                                |   |      |    |

|             |        | \$!addr20                | 3     | 3                          | -             | $PC \leftarrow PC + 3 + jdisp16$                          |   |      |    |

|             |        | !addr16                  | 3     | 3                          | -             | PC ← 0000, addr16                                         |   |      |    |

|             |        | !!addr20                 | 4     | 3                          | _             | $PC \leftarrow addr20$                                    |   |      |    |

| Conditional | BC     | \$addr20                 | 2     | 2/4 Note3                  | -             | $PC \gets PC + 2 + jdisp8 \text{ if } CY = 1$             |   |      |    |

| branch      | BNC    | \$addr20                 | 2     | 2/4 Note3                  | -             | $PC \gets PC + 2 + jdisp8 \text{ if } CY = 0$             |   |      |    |

|             | BZ     | \$addr20                 | 2     | 2/4 Note3                  | -             | $PC \leftarrow PC + 2 + jdisp8$ if $Z = 1$                |   |      |    |

|             | BNZ    | \$addr20                 | 2     | 2/4 Note3                  | -             | $PC \leftarrow PC + 2 + jdisp8$ if $Z = 0$                |   |      |    |

|             | BH     | \$addr20                 | 3     | 2/4 Note3                  | -             | $PC \gets PC + 3 + jdisp8 \text{ if } (Z{\lor}CY){=}0$    |   |      |    |

|             | BNH    | \$addr20                 | 3     | 2/4 Note3                  | _             | $PC \gets PC + 3 + jdisp8 \text{ if } (Z{\lor}CY){=}1$    |   |      |    |

|             | ВТ     | saddr.bit, \$addr20      | 4     | 3/5 Note3                  | -             | $PC \leftarrow PC + 4 + jdisp8$ if (saddr).bit = 1        |   |      |    |

|             |        | sfr.bit, \$addr20        | 4     | 3/5 Note3                  | -             | $PC \leftarrow PC + 4 + jdisp8$ if sfr.bit = 1            |   |      |    |

|             |        | A.bit, \$addr20          | 3     | 3/5 Note3                  | -             | $PC \leftarrow PC + 3 + jdisp8$ if A.bit = 1              |   |      |    |

|             |        | PSW.bit, \$addr20        | 4     | 3/5 Note3                  | _             | $PC \leftarrow PC + 4 + jdisp8$ if PSW.bit = 1            |   |      |    |

|             |        | [HL].bit, \$addr20       | 3     | 3/5 Note3                  | 6/7           | $PC \leftarrow PC + 3 + jdisp8$ if (HL).bit = 1           |   |      |    |

|             |        | ES:[HL].bit,<br>\$addr20 | 4     | 4/6 Note3                  | 7/8           | $PC \gets PC + 4 + jdisp8 \text{ if (ES, HL).bit} = 1$    |   |      |    |

**Notes 1.** Number of CPU clocks (fcLk) when the internal RAM area, SFR area, or extended SFR area is accessed, or when no data is accessed.