# E·XF

# Intel - EP20K1000EBC652-2X Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding Embedded - FPGAs (Field Programmable Gate Array)

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Obsolete                                                      |

| Number of LABs/CLBs            | 3840                                                          |

| Number of Logic Elements/Cells | 38400                                                         |

| Total RAM Bits                 | 327680                                                        |

| Number of I/O                  | 488                                                           |

| Number of Gates                | 1772000                                                       |

| Voltage - Supply               | 1.71V ~ 1.89V                                                 |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                               |

| Package / Case                 | 652-BGA                                                       |

| Supplier Device Package        | 652-BGA (45x45)                                               |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep20k1000ebc652-2x |

|                                |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Windows-based PCs, Sun SPARCstations, and HP 9000 Series 700/800 workstations

- Altera MegaCore<sup>®</sup> functions and Altera Megafunction Partners Program (AMPP<sup>SM</sup>) megafunctions

- NativeLink<sup>™</sup> integration with popular synthesis, simulation, and timing analysis tools

- Quartus II SignalTap<sup>®</sup> embedded logic analyzer simplifies in-system design evaluation by giving access to internal nodes during device operation

- Supports popular revision-control software packages including PVCS, Revision Control System (RCS), and Source Code Control System (SCCS)

Table 4. APEX 20K QFP, BGA & PGA Package Options & I/O Count

Notes (1), (2)

| Device     | 144-Pin<br>TQFP | 208-Pin<br>PQFP<br>RQFP | 240-Pin<br>PQFP<br>RQFP | 356-Pin BGA | 652-Pin BGA | 655-Pin PGA |

|------------|-----------------|-------------------------|-------------------------|-------------|-------------|-------------|

| EP20K30E   | 92              | 125                     |                         |             |             |             |

| EP20K60E   | 92              | 148                     | 151                     | 196         |             |             |

| EP20K100   | 101             | 159                     | 189                     | 252         |             |             |

| EP20K100E  | 92              | 151                     | 183                     | 246         |             |             |

| EP20K160E  | 88              | 143                     | 175                     | 271         |             |             |

| EP20K200   |                 | 144                     | 174                     | 277         |             |             |

| EP20K200E  |                 | 136                     | 168                     | 271         | 376         |             |

| EP20K300E  |                 |                         | 152                     |             | 408         |             |

| EP20K400   |                 |                         |                         |             | 502         | 502         |

| EP20K400E  |                 |                         |                         |             | 488         |             |

| EP20K600E  |                 |                         |                         |             | 488         |             |

| EP20K1000E |                 |                         |                         |             | 488         |             |

| EP20K1500E |                 |                         |                         |             | 488         |             |

| Feature                        | APEX 20K Devices                                                                                                                                                    | APEX 20KE Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MultiCore system integration   | Full support                                                                                                                                                        | Full support                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SignalTap logic analysis       | Full support                                                                                                                                                        | Full support                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 32/64-Bit, 33-MHz PCI          | Full compliance in -1, -2 speed grades                                                                                                                              | Full compliance in -1, -2 speed grades                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 32/64-Bit, 66-MHz PCI          | -                                                                                                                                                                   | Full compliance in -1 speed grade                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MultiVolt I/O                  | 2.5-V or 3.3-V $V_{CCIO}$<br>V <sub>CCIO</sub> selected for device<br>Certain devices are 5.0-V tolerant                                                            | 1.8-V, 2.5-V, or 3.3-V V <sub>CCIO</sub><br>V <sub>CCIO</sub> selected block-by-block<br>5.0-V tolerant with use of external resistor                                                                                                                                                                                                                                                                                                                                 |

| ClockLock support              | Clock delay reduction<br>2× and 4× clock multiplication                                                                                                             | Clock delay reduction<br>$m/(n \times v)$ or $m/(n \times k)$ clock multiplication<br>Drive ClockLock output off-chip<br>External clock feedback<br>ClockShift<br>LVDS support<br>Up to four PLLs<br>ClockShift, clock phase adjustment                                                                                                                                                                                                                               |

| Dedicated clock and input pins | Six                                                                                                                                                                 | Eight                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| I/O standard support           | 2.5-V, 3.3-V, 5.0-V I/O<br>3.3-V PCI<br>Low-voltage complementary<br>metal-oxide semiconductor<br>(LVCMOS)<br>Low-voltage transistor-to-transistor<br>logic (LVTTL) | 1.8-V, 2.5-V, 3.3-V, 5.0-V I/O<br>2.5-V I/O<br>3.3-V PCI and PCI-X<br>3.3-V Advanced Graphics Port (AGP)<br>Center tap terminated (CTT)<br>GTL+<br>LVCMOS<br>LVTTL<br>True-LVDS and LVPECL data pins<br>(in EP20K300E and larger devices)<br>LVDS and LVPECL signaling (in all BGA<br>and FineLine BGA devices)<br>LVDS and LVPECL data pins up to<br>156 Mbps (in -1 speed grade devices)<br>HSTL Class I<br>PCI-X<br>SSTL-2 Class I and II<br>SSTL-3 Class I and II |

| Memory support                 | Dual-port RAM<br>FIFO<br>RAM<br>ROM                                                                                                                                 | CAM<br>Dual-port RAM<br>FIFO<br>RAM<br>ROM                                                                                                                                                                                                                                                                                                                                                                                                                            |

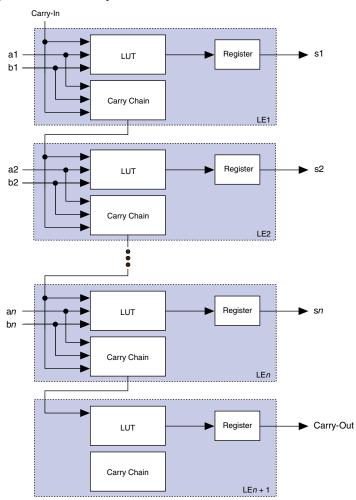

Figure 6. APEX 20K Carry Chain

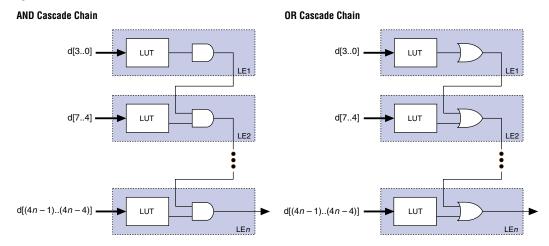

#### Cascade Chain

With the cascade chain, the APEX 20K architecture can implement functions with a very wide fan-in. Adjacent LUTs can compute portions of a function in parallel; the cascade chain serially connects the intermediate values. The cascade chain can use a logical AND or logical OR (via De Morgan's inversion) to connect the outputs of adjacent LEs. Each additional LE provides four more inputs to the effective width of a function, with a short cascade delay. Cascade chain logic can be created automatically by the Quartus II software Compiler during design processing, or manually by the designer during design entry.

Cascade chains longer than ten LEs are implemented automatically by linking LABs together. For enhanced fitting, a long cascade chain skips alternate LABs in a MegaLAB structure. A cascade chain longer than one LAB skips either from an even-numbered LAB to the next even-numbered LAB, or from an odd-numbered LAB to the next odd-numbered LAB. For example, the last LE of the first LAB in the upper-left MegaLAB structure carries to the first LE of the third LAB in the MegaLAB structure. Figure 7 shows how the cascade function can connect adjacent LEs to form functions with a wide fan-in.

Figure 7. APEX 20K Cascade Chain

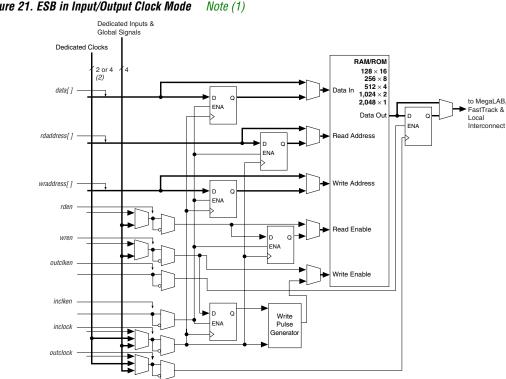

# Input/Output Clock Mode

The input/output clock mode contains two clocks. One clock controls all registers for inputs into the ESB: data input, WE, RE, read address, and write address. The other clock controls the ESB data output registers. The ESB also supports clock enable and asynchronous clear signals; these signals also control the reading and writing of registers independently. Input/output clock mode is commonly used for applications where the reads and writes occur at the same system frequency, but require different clock enable signals for the input and output registers. Figure 21 shows the ESB in input/output clock mode.

#### Figure 21. ESB in Input/Output Clock Mode

#### Notes to Figure 21:

All registers can be cleared asynchronously by ESB local interconnect signals, global signals, or the chip-wide reset. (1)APEX 20KE devices have four dedicated clocks. (2)

## Single-Port Mode

The APEX 20K ESB also supports a single-port mode, which is used when simultaneous reads and writes are not required. See Figure 22.

#### Altera Corporation

#### Advanced I/O Standard Support

APEX 20KE IOEs support the following I/O standards: LVTTL, LVCMOS, 1.8-V I/O, 2.5-V I/O, 3.3-V PCI, PCI-X, 3.3-V AGP, LVDS, LVPECL, GTL+, CTT, HSTL Class I, SSTL-3 Class I and II, and SSTL-2 Class I and II.

For more information on I/O standards supported by APEX 20KE devices, see *Application Note* 117 (*Using Selectable I/O Standards in Altera Devices*).

The APEX 20KE device contains eight I/O banks. In QFP packages, the banks are linked to form four I/O banks. The I/O banks directly support all standards except LVDS and LVPECL. All I/O banks can support LVDS and LVPECL with the addition of external resistors. In addition, one block within a bank contains circuitry to support high-speed True-LVDS and LVPECL inputs, and another block within a particular bank supports high-speed True-LVDS and LVPECL outputs. The LVDS blocks support all of the I/O standards. Each I/O bank has its own VCCIO pins. A single device can support 1.8-V, 2.5-V, and 3.3-V interfaces; each bank can support a different standard independently. Each bank can also use a separate V<sub>REF</sub> level so that each bank can support any of the terminated standards (such as SSTL-3) independently. Within a bank, any one of the terminated standards can be supported. EP20K300E and larger APEX 20KE devices support the LVDS interface for data pins (smaller devices support LVDS clock pins, but not data pins). All EP20K300E and larger devices support the LVDS interface for data pins up to 155 Mbit per channel; EP20K400E devices and larger with an X-suffix on the ordering code add a serializer/deserializer circuit and PLL for higher-speed support.

Each bank can support multiple standards with the same VCCIO for output pins. Each bank can support one voltage-referenced I/O standard, but it can support multiple I/O standards with the same VCCIO voltage level. For example, when VCCIO is 3.3 V, a bank can support LVTTL, LVCMOS, 3.3-V PCI, and SSTL-3 for inputs and outputs.

When the LVDS banks are not used as LVDS I/O banks, they support all of the other I/O standards. Figure 29 shows the arrangement of the APEX 20KE I/O banks.

APEX 20KE devices also support the MultiVolt I/O interface feature. The APEX 20KE VCCINT pins must always be connected to a 1.8-V power supply. With a 1.8-V V<sub>CCINT</sub> level, input pins are 1.8-V, 2.5-V, and 3.3-V tolerant. The VCCIO pins can be connected to either a 1.8-V, 2.5-V, or 3.3-V power supply, depending on the I/O standard requirements. When the VCCIO pins are connected to a 1.8-V power supply, the output levels are compatible with 1.8-V systems. When VCCIO pins are connected to a 2.5-V power supply, the output levels are compatible with 2.5-V systems. When VCCIO pins are connected to a 3.3-V power supply, the output levels are sometime with 2.5-V systems. When VCCIO pins are connected to a 3.3-V power supply, the output high is 3.3 V and compatible with 3.3-V or 5.0-V systems. An APEX 20KE device is 5.0-V tolerant with the addition of a resistor.

#### Table 13 summarizes APEX 20KE MultiVolt I/O support.

| Table 13. APEX 20KE MultiVolt I/O Support     Note (1) |              |              |              |     |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |     |  |  |

|--------------------------------------------------------|--------------|--------------|--------------|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----|--|--|

| V <sub>CCIO</sub> (V)                                  |              | Input Siç    | jnals (V)    |     |              | Output S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ignals (V)   |     |  |  |

|                                                        | 1.8          | 2.5          | 3.3          | 5.0 | 1.8          | 2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.3          | 5.0 |  |  |

| 1.8                                                    | <b>&gt;</b>  | $\checkmark$ | <b>&gt;</b>  |     | $\checkmark$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |     |  |  |

| 2.5                                                    | $\checkmark$ | $\checkmark$ | $\checkmark$ |     |              | <ul> <li>Image: A start of the start of</li></ul> |              |     |  |  |

| 3.3                                                    | ~            | $\checkmark$ | >            | (2) |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>√</b> (3) |     |  |  |

#### Notes to Table 13:

The PCI clamping diode must be disabled to drive an input with voltages higher than V<sub>CCIO</sub>, except for the 5.0-V input case.

(2) An APEX 20KE device can be made 5.0-V tolerant with the addition of an external resistor. You also need a PCI clamp and series resistor.

(3) When V<sub>CCIO</sub> = 3.3 V, an APEX 20KE device can drive a 2.5-V device with 3.3-V tolerant inputs.

# ClockLock & ClockBoost Features

APEX 20K devices support the ClockLock and ClockBoost clock management features, which are implemented with PLLs. The ClockLock circuitry uses a synchronizing PLL that reduces the clock delay and skew within a device. This reduction minimizes clock-to-output and setup times while maintaining zero hold times. The ClockBoost circuitry, which provides a clock multiplier, allows the designer to enhance device area efficiency by sharing resources within the device. The ClockBoost circuitry allows the designer to distribute a low-speed clock and multiply that clock on-device. APEX 20K devices include a high-speed clock tree; unlike ASICs, the user does not have to design and optimize the clock tree. The ClockLock and ClockBoost features work in conjunction with the APEX 20K device's high-speed clock to provide significant improvements in system performance and band-width. Devices with an X-suffix on the ordering code include the ClockLock circuit.

The ClockLock and ClockBoost features in APEX 20K devices are enabled through the Quartus II software. External devices are not required to use these features.

For designs that require both a multiplied and non-multiplied clock, the clock trace on the board can be connected to CLK2p. Table 14 shows the combinations supported by the ClockLock and ClockBoost circuitry. The CLK2p pin can feed both the ClockLock and ClockBoost circuitry in the APEX 20K device. However, when both circuits are used, the other clock pin (CLK1p) cannot be used.

| Table 14. Multiplication Factor Combinations |    |  |  |  |  |  |

|----------------------------------------------|----|--|--|--|--|--|

| Clock 1 Clock 2                              |    |  |  |  |  |  |

| ×1                                           | ×1 |  |  |  |  |  |

| ×1, ×2                                       | ×2 |  |  |  |  |  |

| ×1, ×2, ×4                                   | ×4 |  |  |  |  |  |

## APEX 20KE ClockLock Feature

APEX 20KE devices include an enhanced ClockLock feature set. These devices include up to four PLLs, which can be used independently. Two PLLs are designed for either general-purpose use or LVDS use (on devices that support LVDS I/O pins). The remaining two PLLs are designed for general-purpose use. The EP20K200E and smaller devices have two PLLs; the EP20K300E and larger devices have four PLLs.

The following sections describe some of the features offered by the APEX 20KE PLLs.

#### External PLL Feedback

The ClockLock circuit's output can be driven off-chip to clock other devices in the system; further, the feedback loop of the PLL can be routed off-chip. This feature allows the designer to exercise fine control over the I/O interface between the APEX 20KE device and another high-speed device, such as SDRAM.

#### Clock Multiplication

The APEX 20KE ClockBoost circuit can multiply or divide clocks by a programmable number. The clock can be multiplied by  $m/(n \times k)$  or  $m/(n \times v)$ , where *m* and *k* range from 2 to 160, and *n* and *v* range from 1 to 16. Clock multiplication and division can be used for time-domain multiplexing and other functions, which can reduce design LE requirements.

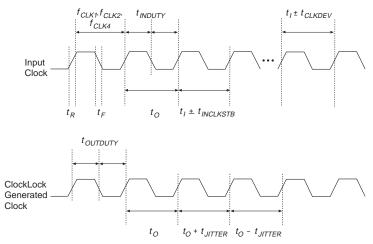

Figure 30. Specifications for the Incoming & Generated Clocks Note (1)

#### Note to Figure 30:

(1) The tI parameter refers to the nominal input clock period; the tO parameter refers to the nominal output clock period.

Table 15 summarizes the APEX 20K ClockLock and ClockBoost parameters for -1 speed-grade devices.

| Symbol                | Parameter                                                                                                                      | Min | Мах        | Unit |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------|-----|------------|------|

| f <sub>OUT</sub>      | Output frequency                                                                                                               | 25  | 180        | MHz  |

| f <sub>CLK1</sub> (1) | Input clock frequency (ClockBoost clock multiplication factor equals 1)                                                        | 25  | 180 (1)    | MHz  |

| f <sub>CLK2</sub>     | Input clock frequency (ClockBoost clock multiplication factor equals 2)                                                        | 16  | 90         | MHz  |

| f <sub>CLK4</sub>     | Input clock frequency (ClockBoost clock multiplication factor equals 4)                                                        | 10  | 48         | MHz  |

| toutduty              | Duty cycle for ClockLock/ClockBoost-generated<br>clock                                                                         | 40  | 60         | %    |

| f <sub>CLKDEV</sub>   | Input deviation from user specification in the<br>Quartus II software (ClockBoost clock<br>multiplication factor equals 1) (2) |     | 25,000 (3) | PPM  |

| t <sub>R</sub>        | Input rise time                                                                                                                |     | 5          | ns   |

| t <sub>F</sub>        | Input fall time                                                                                                                |     | 5          | ns   |

| t <sub>LOCK</sub>     | Time required for ClockLock/ClockBoost to acquire lock (4)                                                                     |     | 10         | μs   |

٦

| Table 2            | Table 28. APEX 20KE Device Recommended Operating Conditions |                    |                  |                   |      |  |  |  |  |  |

|--------------------|-------------------------------------------------------------|--------------------|------------------|-------------------|------|--|--|--|--|--|

| Symbol             | Parameter                                                   | Conditions         | Min              | Max               | Unit |  |  |  |  |  |

| V <sub>CCINT</sub> | Supply voltage for internal logic and input buffers         | (3), (4)           | 1.71 (1.71)      | 1.89 (1.89)       | V    |  |  |  |  |  |

| V <sub>CCIO</sub>  | Supply voltage for output buffers, 3.3-V operation          | (3), (4)           | 3.00 (3.00)      | 3.60 (3.60)       | V    |  |  |  |  |  |

|                    | Supply voltage for output buffers, 2.5-V operation          | (3), (4)           | 2.375<br>(2.375) | 2.625<br>(2.625)  | V    |  |  |  |  |  |

|                    | Supply voltage for output buffers, 1.8-V operation          | (3), (4)           | 1.71 (1.71)      | 1.89 (1.89)       | V    |  |  |  |  |  |

| VI                 | Input voltage                                               | (5), (6)           | -0.5             | 4.0               | V    |  |  |  |  |  |

| Vo                 | Output voltage                                              |                    | 0                | V <sub>CCIO</sub> | V    |  |  |  |  |  |

| ТJ                 | Junction temperature                                        | For commercial use | 0                | 85                | °C   |  |  |  |  |  |

|                    |                                                             | For industrial use | -40              | 100               | °C   |  |  |  |  |  |

| t <sub>R</sub>     | Input rise time                                             |                    |                  | 40                | ns   |  |  |  |  |  |

| t <sub>F</sub>     | Input fall time                                             |                    |                  | 40                | ns   |  |  |  |  |  |

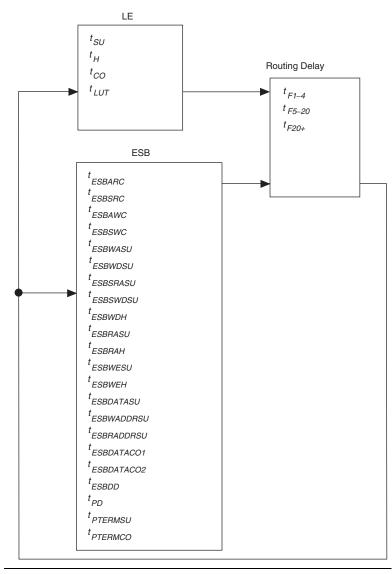

Figure 37. APEX 20KE f<sub>MAX</sub> Timing Model

| Symbol                  | -1 Spee | d Grade | -2 Spee | d Grade | -3 Spee | d Grade | Units |

|-------------------------|---------|---------|---------|---------|---------|---------|-------|

|                         | Min     | Мах     | Min     | Max     | Min     | Max     |       |

| t <sub>SU</sub>         | 0.5     |         | 0.6     |         | 0.8     |         | ns    |

| t <sub>H</sub>          | 0.7     |         | 0.8     |         | 1.0     |         | ns    |

| t <sub>co</sub>         |         | 0.3     |         | 0.4     |         | 0.5     | ns    |

| t <sub>lut</sub>        |         | 0.8     |         | 1.0     |         | 1.3     | ns    |

| t <sub>ESBRC</sub>      |         | 1.7     |         | 2.1     |         | 2.4     | ns    |

| t <sub>ESBWC</sub>      |         | 5.7     |         | 6.9     |         | 8.1     | ns    |

| t <sub>ESBWESU</sub>    | 3.3     |         | 3.9     |         | 4.6     |         | ns    |

| t <sub>ESBDATASU</sub>  | 2.2     |         | 2.7     |         | 3.1     |         | ns    |

| t <sub>ESBDATAH</sub>   | 0.6     |         | 0.8     |         | 0.9     |         | ns    |

| t <sub>ESBADDRSU</sub>  | 2.4     |         | 2.9     |         | 3.3     |         | ns    |

| t <sub>ESBDATACO1</sub> |         | 1.3     |         | 1.6     |         | 1.8     | ns    |

| t <sub>ESBDATACO2</sub> |         | 2.6     |         | 3.1     |         | 3.6     | ns    |

| t <sub>ESBDD</sub>      |         | 2.5     |         | 3.3     |         | 3.6     | ns    |

| t <sub>PD</sub>         |         | 2.5     |         | 3.0     |         | 3.6     | ns    |

| t <sub>PTERMSU</sub>    | 2.3     |         | 2.7     |         | 3.2     |         | ns    |

| t <sub>PTERMCO</sub>    |         | 1.5     |         | 1.8     |         | 2.1     | ns    |

| t <sub>F1-4</sub>       |         | 0.5     |         | 0.6     |         | 0.7     | ns    |

| t <sub>F5-20</sub>      |         | 1.6     |         | 1.7     |         | 1.8     | ns    |

| t <sub>F20+</sub>       |         | 2.2     |         | 2.2     |         | 2.3     | ns    |

| t <sub>CH</sub>         | 2.0     |         | 2.5     |         | 3.0     |         | ns    |

| t <sub>CL</sub>         | 2.0     |         | 2.5     |         | 3.0     |         | ns    |

| t <sub>CLRP</sub>       | 0.3     |         | 0.4     |         | 0.4     |         | ns    |

| t <sub>PREP</sub>       | 0.4     |         | 0.5     |         | 0.5     |         | ns    |

| t <sub>ESBCH</sub>      | 2.0     |         | 2.5     |         | 3.0     |         | ns    |

| t <sub>ESBCL</sub>      | 2.0     |         | 2.5     |         | 3.0     |         | ns    |

| t <sub>ESBWP</sub>      | 1.6     |         | 1.9     |         | 2.2     |         | ns    |

| t <sub>ESBRP</sub>      | 1.0     |         | 1.3     |         | 1.4     |         | ns    |

| Symbol                  | -'    | 1    | -     | 2    | -:    | 3    | Unit |

|-------------------------|-------|------|-------|------|-------|------|------|

|                         | Min   | Max  | Min   | Max  | Min   | Max  |      |

| t <sub>ESBARC</sub>     |       | 1.61 |       | 1.84 |       | 1.97 | ns   |

| t <sub>ESBSRC</sub>     |       | 2.57 |       | 2.97 |       | 3.20 | ns   |

| t <sub>ESBAWC</sub>     |       | 0.52 |       | 4.09 |       | 4.39 | ns   |

| t <sub>ESBSWC</sub>     |       | 3.17 |       | 3.78 |       | 4.09 | ns   |

| t <sub>ESBWASU</sub>    | 0.56  |      | 6.41  |      | 0.63  |      | ns   |

| t <sub>ESBWAH</sub>     | 0.48  |      | 0.54  |      | 0.55  |      | ns   |

| t <sub>ESBWDSU</sub>    | 0.71  |      | 0.80  |      | 0.81  |      | ns   |

| t <sub>ESBWDH</sub>     | .048  |      | 0.54  |      | 0.55  |      | ns   |

| t <sub>ESBRASU</sub>    | 1.57  |      | 1.75  |      | 1.87  |      | ns   |

| t <sub>ESBRAH</sub>     | 0.00  |      | 0.00  |      | 0.20  |      | ns   |

| t <sub>ESBWESU</sub>    | 1.54  |      | 1.72  |      | 1.80  |      | ns   |

| t <sub>ESBWEH</sub>     | 0.00  |      | 0.00  |      | 0.00  |      | ns   |

| t <sub>ESBDATASU</sub>  | -0.16 |      | -0.20 |      | -0.20 |      | ns   |

| t <sub>ESBDATAH</sub>   | 0.13  |      | 0.13  |      | 0.13  |      | ns   |

| t <sub>ESBWADDRSU</sub> | 0.12  |      | 0.08  |      | 0.13  |      | ns   |

| t <sub>ESBRADDRSU</sub> | 0.17  |      | 0.15  |      | 0.19  |      | ns   |

| t <sub>ESBDATACO1</sub> |       | 1.20 |       | 1.39 |       | 1.52 | ns   |

| t <sub>ESBDATACO2</sub> |       | 2.54 |       | 2.99 |       | 3.22 | ns   |

| t <sub>ESBDD</sub>      |       | 3.06 |       | 3.56 |       | 3.85 | ns   |

| t <sub>PD</sub>         |       | 1.73 |       | 2.02 |       | 2.20 | ns   |

| t <sub>PTERMSU</sub>    | 1.11  |      | 1.26  |      | 1.38  |      | ns   |

| t <sub>PTERMCO</sub>    |       | 1.19 |       | 1.40 |       | 1.08 | ns   |

| Table 63. EP20K100E f <sub>MAX</sub> Routing Delays |     |      |     |      |     |      |    |  |  |  |  |

|-----------------------------------------------------|-----|------|-----|------|-----|------|----|--|--|--|--|

| Symbol                                              | -1  |      |     | -2   |     | -3   |    |  |  |  |  |

|                                                     | Min | Max  | Min | Max  | Min | Мах  |    |  |  |  |  |

| t <sub>F1-4</sub>                                   |     | 0.24 |     | 0.27 |     | 0.29 | ns |  |  |  |  |

| t <sub>F5-20</sub>                                  |     | 1.04 |     | 1.26 |     | 1.52 | ns |  |  |  |  |

| t <sub>F20+</sub>                                   |     | 1.12 |     | 1.36 |     | 1.86 | ns |  |  |  |  |

| Table 78. EP20K200E External Bidirectional Timing Parameters |      |      |      |      |      |      |    |  |  |

|--------------------------------------------------------------|------|------|------|------|------|------|----|--|--|

| Symbol                                                       | -1   |      | -    | 2    | -    | Unit |    |  |  |

|                                                              | Min  | Мах  | Min  | Max  | Min  | Max  |    |  |  |

| t <sub>insubidir</sub>                                       | 2.81 |      | 3.19 |      | 3.54 |      | ns |  |  |

| t <sub>INHBIDIR</sub>                                        | 0.00 |      | 0.00 |      | 0.00 |      | ns |  |  |

| t <sub>outcobidir</sub>                                      | 2.00 | 5.12 | 2.00 | 5.62 | 2.00 | 6.11 | ns |  |  |

| t <sub>XZBIDIR</sub>                                         |      | 7.51 |      | 8.32 |      | 8.67 | ns |  |  |

| t <sub>ZXBIDIR</sub>                                         |      | 7.51 |      | 8.32 |      | 8.67 | ns |  |  |

| t <sub>insubidirpll</sub>                                    | 3.30 |      | 3.64 |      | -    |      | ns |  |  |

| t <sub>inhbidirpll</sub>                                     | 0.00 |      | 0.00 |      | -    |      | ns |  |  |

| t <sub>outcobidirpll</sub>                                   | 0.50 | 3.01 | 0.50 | 3.36 | -    | -    | ns |  |  |

| t <sub>XZBIDIRPLL</sub>                                      |      | 5.40 |      | 6.05 |      | -    | ns |  |  |

| t <sub>ZXBIDIRPLL</sub>                                      |      | 5.40 |      | 6.05 |      | -    | ns |  |  |

Tables 79 through 84 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K300E APEX 20KE devices.

| Table 79. EP20K300E f <sub>MAX</sub> LE Timing Microparameters |      |      |      |      |      |      |      |  |  |

|----------------------------------------------------------------|------|------|------|------|------|------|------|--|--|

| Symbol                                                         | -1   |      | -    | 2    | -;   | 3    | Unit |  |  |

|                                                                | Min  | Max  | Min  | Max  | Min  | Мах  |      |  |  |

| t <sub>SU</sub>                                                | 0.16 |      | 0.17 |      | 0.18 |      | ns   |  |  |

| t <sub>H</sub>                                                 | 0.31 |      | 0.33 |      | 0.38 |      | ns   |  |  |

| t <sub>CO</sub>                                                |      | 0.28 |      | 0.38 |      | 0.51 | ns   |  |  |

| t <sub>LUT</sub>                                               |      | 0.79 |      | 1.07 |      | 1.43 | ns   |  |  |

#### APEX 20K Programmable Logic Device Family Data Sheet

| Table 87. EP20K400E f <sub>MAX</sub> Routing Delays |                |      |                                    |      |         |         |      |  |  |

|-----------------------------------------------------|----------------|------|------------------------------------|------|---------|---------|------|--|--|

| Symbol                                              | -1 Speed Grade |      | nbol -1 Speed Grade -2 Speed Grade |      | -3 Spee | d Grade | Unit |  |  |

|                                                     | Min            | Max  | Min                                | Max  | Min     | Мах     |      |  |  |

| t <sub>F1-4</sub>                                   |                | 0.25 |                                    | 0.25 |         | 0.26    | ns   |  |  |

| t <sub>F5-20</sub>                                  |                | 1.01 |                                    | 1.12 |         | 1.25    | ns   |  |  |

| t <sub>F20+</sub>                                   |                | 3.71 |                                    | 3.92 |         | 4.17    | ns   |  |  |

| Symbol             | -1 Speed Grade |     | -2 Speed Grade |     | -3 Spee | Unit |    |

|--------------------|----------------|-----|----------------|-----|---------|------|----|

|                    | Min            | Max | Min            | Max | Min     | Max  |    |

| t <sub>CH</sub>    | 1.36           |     | 2.22           |     | 2.35    |      | ns |

| t <sub>CL</sub>    | 1.36           |     | 2.26           |     | 2.35    |      | ns |

| t <sub>CLRP</sub>  | 0.18           |     | 0.18           |     | 0.19    |      | ns |

| t <sub>PREP</sub>  | 0.18           |     | 0.18           |     | 0.19    |      | ns |

| t <sub>ESBCH</sub> | 1.36           |     | 2.26           |     | 2.35    |      | ns |

| t <sub>ESBCL</sub> | 1.36           |     | 2.26           |     | 2.35    |      | ns |

| t <sub>ESBWP</sub> | 1.17           |     | 1.38           |     | 1.56    |      | ns |

| t <sub>ESBRP</sub> | 0.94           |     | 1.09           |     | 1.25    |      | ns |

| Table 89. EP20K400E External Timing Parameters |         |         |                |      |                |      |      |  |  |  |

|------------------------------------------------|---------|---------|----------------|------|----------------|------|------|--|--|--|

| Symbol                                         | -1 Spee | d Grade | -2 Speed Grade |      | -3 Speed Grade |      | Unit |  |  |  |

|                                                | Min     | Max     | Min            | Max  | Min            | Max  | -    |  |  |  |

| t <sub>INSU</sub>                              | 2.51    |         | 2.64           |      | 2.77           |      | ns   |  |  |  |

| t <sub>INH</sub>                               | 0.00    |         | 0.00           |      | 0.00           |      | ns   |  |  |  |

| t <sub>outco</sub>                             | 2.00    | 5.25    | 2.00           | 5.79 | 2.00           | 6.32 | ns   |  |  |  |

| tINSUPLL                                       | 3.221   |         | 3.38           |      | -              |      | ns   |  |  |  |

| t <sub>INHPLL</sub>                            | 0.00    |         | 0.00           |      | -              |      | ns   |  |  |  |

| t <sub>outcopll</sub>                          | 0.50    | 2.25    | 0.50           | 2.45 | -              | -    | ns   |  |  |  |

Г

Tables 97 through 102 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K1000E APEX 20KE devices.

| Table 97. EP20K1000E f <sub>MAX</sub> LE Timing Microparameters |                |      |         |          |         |         |      |  |  |

|-----------------------------------------------------------------|----------------|------|---------|----------|---------|---------|------|--|--|

| Symbol                                                          | -1 Speed Grade |      | -2 Spec | ed Grade | -3 Spee | d Grade | Unit |  |  |

|                                                                 | Min            | Max  | Min     | Max      | Min     | Max     |      |  |  |

| t <sub>SU</sub>                                                 | 0.25           |      | 0.25    |          | 0.25    |         | ns   |  |  |

| t <sub>H</sub>                                                  | 0.25           |      | 0.25    |          | 0.25    |         | ns   |  |  |

| t <sub>CO</sub>                                                 |                | 0.28 |         | 0.32     |         | 0.33    | ns   |  |  |

| t <sub>LUT</sub>                                                |                | 0.80 |         | 0.95     |         | 1.13    | ns   |  |  |

| Symbol                     | -1 Spee | d Grade | -2 Spee | d Grade | -3 Spee | Unit |    |

|----------------------------|---------|---------|---------|---------|---------|------|----|

|                            | Min     | Max     | Min     | Max     | Min     | Max  |    |

| t <sub>insubidir</sub>     | 3.22    |         | 3.33    |         | 3.51    |      | ns |

| t <sub>inhbidir</sub>      | 0.00    |         | 0.00    |         | 0.00    |      | ns |

| toutcobidir                | 2.00    | 5.75    | 2.00    | 6.33    | 2.00    | 6.90 | ns |

| t <sub>xzbidir</sub>       |         | 6.31    |         | 7.09    |         | 7.76 | ns |

| t <sub>ZXBIDIR</sub>       |         | 6.31    |         | 7.09    |         | 7.76 | ns |

| t <sub>insubidirpl</sub> L | 3.25    |         | 3.26    |         |         |      | ns |

| t <sub>inhbidirpll</sub>   | 0.00    |         | 0.00    |         |         |      | ns |

| toutcobidirpll             | 0.50    | 2.25    | 0.50    | 2.99    |         |      | ns |

| t <sub>xzbidirpll</sub>    |         | 2.81    |         | 3.80    |         |      | ns |

| t <sub>zxbidirpll</sub>    |         | 2.81    |         | 3.80    |         |      | ns |

Tables 103 through 108 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K1500E APEX 20KE devices.

| Table 103. EP20K1500E f <sub>MAX</sub> LE Timing Microparameters |                |      |         |          |         |         |      |  |  |

|------------------------------------------------------------------|----------------|------|---------|----------|---------|---------|------|--|--|

| Symbol                                                           | -1 Speed Grade |      | -2 Spee | ed Grade | -3 Spee | d Grade | Unit |  |  |

|                                                                  | Min            | Max  | Min     | Max      | Min     | Max     |      |  |  |

| t <sub>SU</sub>                                                  | 0.25           |      | 0.25    |          | 0.25    |         | ns   |  |  |

| t <sub>H</sub>                                                   | 0.25           |      | 0.25    |          | 0.25    |         | ns   |  |  |

| t <sub>CO</sub>                                                  |                | 0.28 |         | 0.32     |         | 0.33    | ns   |  |  |

| t <sub>LUT</sub>                                                 |                | 0.80 |         | 0.95     |         | 1.13    | ns   |  |  |

Т

| Symbol             | -1 Spee | d Grade | -2 Spee | d Grade | -3 Spee | d Grade | Unit |

|--------------------|---------|---------|---------|---------|---------|---------|------|

|                    | Min     | Max     | Min     | Max     | Min     | Мах     |      |

| t <sub>CH</sub>    | 1.25    |         | 1.43    |         | 1.67    |         | ns   |

| t <sub>CL</sub>    | 1.25    |         | 1.43    |         | 1.67    |         | ns   |

| t <sub>CLRP</sub>  | 0.20    |         | 0.20    |         | 0.20    |         | ns   |

| t <sub>PREP</sub>  | 0.20    |         | 0.20    |         | 0.20    |         | ns   |

| t <sub>ESBCH</sub> | 1.25    |         | 1.43    |         | 1.67    |         | ns   |

| t <sub>ESBCL</sub> | 1.25    |         | 1.43    |         | 1.67    |         | ns   |

| t <sub>ESBWP</sub> | 1.28    |         | 1.51    |         | 1.65    |         | ns   |

| t <sub>ESBRP</sub> | 1.11    |         | 1.29    |         | 1.41    |         | ns   |

| Table 107. EP20K1500E External Timing Parameters |                       |      |                |      |          |                |    |  |  |  |

|--------------------------------------------------|-----------------------|------|----------------|------|----------|----------------|----|--|--|--|

| Symbol                                           | Symbol -1 Speed Grade |      | -2 Speed Grade |      | -3 Speed | -3 Speed Grade |    |  |  |  |

|                                                  | Min                   | Max  | Min            | Max  | Min      | Max            | -  |  |  |  |

| tINSU                                            | 3.09                  |      | 3.30           |      | 3.58     |                | ns |  |  |  |

| t <sub>INH</sub>                                 | 0.00                  |      | 0.00           |      | 0.00     |                | ns |  |  |  |

| t <sub>outco</sub>                               | 2.00                  | 6.18 | 2.00           | 6.81 | 2.00     | 7.36           | ns |  |  |  |

| t <sub>INSUPLL</sub>                             | 1.94                  |      | 2.08           |      | -        |                | ns |  |  |  |

| t <sub>INHPLL</sub>                              | 0.00                  |      | 0.00           |      | -        |                | ns |  |  |  |

| toutcopll                                        | 0.50                  | 2.67 | 0.50           | 2.99 | -        | -              | ns |  |  |  |

SRAM configuration elements allow APEX 20K devices to be reconfigured in-circuit by loading new configuration data into the device. Real-time reconfiguration is performed by forcing the device into command mode with a device pin, loading different configuration data, reinitializing the device, and resuming usermode operation. In-field upgrades can be performed by distributing new configuration files.

# **Configuration Schemes**

The configuration data for an APEX 20K device can be loaded with one of five configuration schemes (see Table 111), chosen on the basis of the target application. An EPC2 or EPC16 configuration device, intelligent controller, or the JTAG port can be used to control the configuration of an APEX 20K device. When a configuration device is used, the system can configure automatically at system power-up.

Multiple APEX 20K devices can be configured in any of five configuration schemes by connecting the configuration enable (nCE) and configuration enable output (nCEO) pins on each device.

| Table 111. Data Sources for Configuration |                                                                     |  |  |  |  |

|-------------------------------------------|---------------------------------------------------------------------|--|--|--|--|

| Configuration Scheme                      | Data Source                                                         |  |  |  |  |

| Configuration device                      | EPC1, EPC2, EPC16 configuration devices                             |  |  |  |  |

| Passive serial (PS)                       | MasterBlaster or ByteBlasterMV download cable or serial data source |  |  |  |  |

| Passive parallel asynchronous (PPA)       | Parallel data source                                                |  |  |  |  |

| Passive parallel synchronous (PPS)        | Parallel data source                                                |  |  |  |  |

| JTAG                                      | MasterBlaster or ByteBlasterMV download cable or a microprocessor   |  |  |  |  |

|                                           | with a Jam or JBC File                                              |  |  |  |  |

For more information on configuration, see *Application Note* 116 (*Configuring APEX 20K, FLEX 10K, & FLEX 6000 Devices.*)

# **Device Pin-Outs**

See the Altera web site (http://www.altera.com) or the *Altera Digital Library* for pin-out information

# Revision History

The information contained in the *APEX 20K Programmable Logic Device Family Data Sheet* version 5.1 supersedes information published in previous versions.

# Version 5.1

*APEX 20K Programmable Logic Device Family Data Sheet* version 5.1 contains the following changes:

- In version 5.0, the VI input voltage spec was updated in Table 28 on page 63.

- In version 5.0, *Note* (5) to Tables 27 through 30 was revised.

- Added *Note* (2) to Figure 21 on page 33.

# Version 5.0

*APEX 20K Programmable Logic Device Family Data Sheet* version 5.0 contains the following changes:

- Updated Tables 23 through 26. Removed 2.5-V operating condition tables because all APEX 20K devices are now 5.0-V tolerant.

- Updated conditions in Tables 33, 38 and 39.

- Updated data for t<sub>ESBDATAH</sub> parameter.

## Version 4.3

*APEX 20K Programmable Logic Device Family Data Sheet* version 4.3 contains the following changes:

- Updated Figure 20.

- Updated *Note* (2) to Table 13.

- Updated notes to Tables 27 through 30.

#### Version 4.2

*APEX 20K Programmable Logic Device Family Data Sheet* version 4.2 contains the following changes:

- Updated Figure 29.

- Updated *Note* (1) to Figure 29.