Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 416                                                        |

| Number of Logic Elements/Cells | 4160                                                       |

| Total RAM Bits                 | 53248                                                      |

| Number of I/O                  | 252                                                        |

| Number of Gates                | 263000                                                     |

| Voltage - Supply               | 2.375V ~ 2.625V                                            |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                         |

| Package / Case                 | 356-LBGA                                                   |

| Supplier Device Package        | 356-BGA (35x35)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep20k100bi356-3 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

All APEX 20K devices are reconfigurable and are 100% tested prior to shipment. As a result, test vectors do not have to be generated for fault coverage purposes. Instead, the designer can focus on simulation and design verification. In addition, the designer does not need to manage inventories of different application-specific integrated circuit (ASIC) designs; APEX 20K devices can be configured on the board for the specific functionality required.

APEX 20K devices are configured at system power-up with data stored in an Altera serial configuration device or provided by a system controller. Altera offers in-system programmability (ISP)-capable EPC1, EPC2, and EPC16 configuration devices, which configure APEX 20K devices via a serial data stream. Moreover, APEX 20K devices contain an optimized interface that permits microprocessors to configure APEX 20K devices serially or in parallel, and synchronously or asynchronously. The interface also enables microprocessors to treat APEX 20K devices as memory and configure the device by writing to a virtual memory location, making reconfiguration easy.

After an APEX 20K device has been configured, it can be reconfigured in-circuit by resetting the device and loading new data. Real-time changes can be made during system operation, enabling innovative reconfigurable computing applications.

APEX 20K devices are supported by the Altera Quartus II development system, a single, integrated package that offers HDL and schematic design entry, compilation and logic synthesis, full simulation and worst-case timing analysis, SignalTap logic analysis, and device configuration. The Quartus II software runs on Windows-based PCs, Sun SPARCstations, and HP 9000 Series 700/800 workstations.

The Quartus II software provides NativeLink interfaces to other industry-standard PC- and UNIX workstation-based EDA tools. For example, designers can invoke the Quartus II software from within third-party design tools. Further, the Quartus II software contains built-in optimized synthesis libraries; synthesis tools can use these libraries to optimize designs for APEX 20K devices. For example, the Synopsys Design Compiler library, supplied with the Quartus II development system, includes DesignWare functions optimized for the APEX 20K architecture.

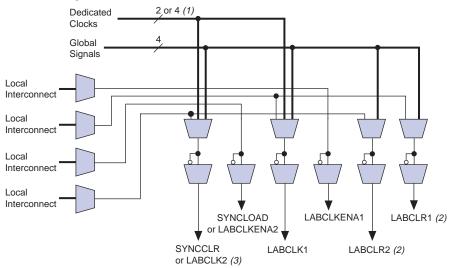

APEX 20K devices provide two dedicated clock pins and four dedicated input pins that drive register control inputs. These signals ensure efficient distribution of high-speed, low-skew control signals. These signals use dedicated routing channels to provide short delays and low skews. Four of the dedicated inputs drive four global signals. These four global signals can also be driven by internal logic, providing an ideal solution for a clock divider or internally generated asynchronous clear signals with high fan-out. The dedicated clock pins featured on the APEX 20K devices can also feed logic. The devices also feature ClockLock and ClockBoost clock management circuitry. APEX 20KE devices provide two additional dedicated clock pins, for a total of four dedicated clock pins.

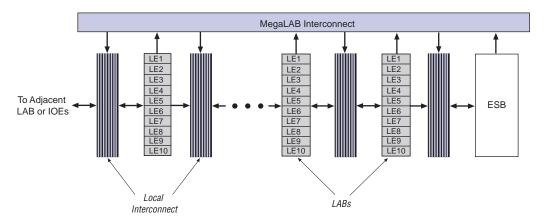

### MegaLAB Structure

APEX 20K devices are constructed from a series of MegaLAB<sup>TM</sup> structures. Each MegaLAB structure contains a group of logic array blocks (LABs), one ESB, and a MegaLAB interconnect, which routes signals within the MegaLAB structure. The EP20K30E device has 10 LABs, EP20K60E through EP20K600E devices have 16 LABs, and the EP20K1000E and EP20K1500E devices have 24 LABs. Signals are routed between MegaLAB structures and I/O pins via the FastTrack Interconnect. In addition, edge LABs can be driven by I/O pins through the local interconnect. Figure 2 shows the MegaLAB structure.

Figure 2. MegaLAB Structure

Each LAB contains dedicated logic for driving control signals to its LEs and ESBs. The control signals include clock, clock enable, asynchronous clear, asynchronous preset, asynchronous load, synchronous clear, and synchronous load signals. A maximum of six control signals can be used at a time. Although synchronous load and clear signals are generally used when implementing counters, they can also be used with other functions.

Each LAB can use two clocks and two clock enable signals. Each LAB's clock and clock enable signals are linked (e.g., any LE in a particular LAB using CLK1 will also use CLKENA1). LEs with the same clock but different clock enable signals either use both clock signals in one LAB or are placed into separate LABs.

If both the rising and falling edges of a clock are used in a LAB, both LAB-wide clock signals are used.

The LAB-wide control signals can be generated from the LAB local interconnect, global signals, and dedicated clock pins. The inherent low skew of the FastTrack Interconnect enables it to be used for clock distribution. Figure 4 shows the LAB control signal generation circuit.

Figure 4. LAB Control Signal Generation

#### Notes to Figure 4:

- (1) APEX 20KE devices have four dedicated clocks.

- (2) The LABCLR1 and LABCLR2 signals also control asynchronous load and asynchronous preset for LEs within the LAB.

- (3) The SYNCCLR signal can be generated by the local interconnect or global signals.

### LE Operating Modes

The APEX 20K LE can operate in one of the following three modes:

- Normal mode

- Arithmetic mode

- Counter mode

Each mode uses LE resources differently. In each mode, seven available inputs to the LE—the four data inputs from the LAB local interconnect, the feedback from the programmable register, and the carry-in and cascade-in from the previous LE—are directed to different destinations to implement the desired logic function. LAB-wide signals provide clock, asynchronous clear, asynchronous preset, asynchronous load, synchronous clear, synchronous load, and clock enable control for the register. These LAB-wide signals are available in all LE modes.

The Quartus II software, in conjunction with parameterized functions such as LPM and DesignWare functions, automatically chooses the appropriate mode for common functions such as counters, adders, and multipliers. If required, the designer can also create special-purpose functions that specify which LE operating mode to use for optimal performance. Figure 8 shows the LE operating modes.

#### Normal Mode

The normal mode is suitable for general logic applications, combinatorial functions, or wide decoding functions that can take advantage of a cascade chain. In normal mode, four data inputs from the LAB local interconnect and the carry-in are inputs to a four-input LUT. The Quartus II software Compiler automatically selects the carry-in or the DATA3 signal as one of the inputs to the LUT. The LUT output can be combined with the cascade-in signal to form a cascade chain through the cascade-out signal. LEs in normal mode support packed registers.

#### Arithmetic Mode

The arithmetic mode is ideal for implementing adders, accumulators, and comparators. An LE in arithmetic mode uses two 3-input LUTs. One LUT computes a three-input function; the other generates a carry output. As shown in Figure 8, the first LUT uses the carry-in signal and two data inputs from the LAB local interconnect to generate a combinatorial or registered output. For example, when implementing an adder, this output is the sum of three signals: DATA1, DATA2, and carry-in. The second LUT uses the same three signals to generate a carry-out signal, thereby creating a carry chain. The arithmetic mode also supports simultaneous use of the cascade chain. LEs in arithmetic mode can drive out registered and unregistered versions of the LUT output.

The Quartus II software implements parameterized functions that use the arithmetic mode automatically where appropriate; the designer does not need to specify how the carry chain will be used.

#### Counter Mode

The counter mode offers clock enable, counter enable, synchronous up/down control, synchronous clear, and synchronous load options. The counter enable and synchronous up/down control signals are generated from the data inputs of the LAB local interconnect. The synchronous clear and synchronous load options are LAB-wide signals that affect all registers in the LAB. Consequently, if any of the LEs in an LAB use the counter mode, other LEs in that LAB must be used as part of the same counter or be used for a combinatorial function. The Quartus II software automatically places any registers that are not used by the counter into other LABs.

The programmable register also supports an asynchronous clear function. Within the ESB, two asynchronous clears are generated from global signals and the local interconnect. Each macrocell can either choose between the two asynchronous clear signals or choose to not be cleared. Either of the two clear signals can be inverted within the ESB. Figure 15 shows the ESB control logic when implementing product-terms.

Dedicated Clocks Global Signals Local Interconnect Local Interconnect Local Interconnect Local Interconnect CLR1 CLKENA2 CLK1 CLKENA1 CLR<sub>2</sub>

Figure 15. ESB Product-Term Mode Control Logic

Note to Figure 15:

(1) APEX 20KE devices have four dedicated clocks.

### Parallel Expanders

Parallel expanders are unused product terms that can be allocated to a neighboring macrocell to implement fast, complex logic functions. Parallel expanders allow up to 32 product terms to feed the macrocell OR logic directly, with two product terms provided by the macrocell and 30 parallel expanders provided by the neighboring macrocells in the ESB.

The Quartus II software Compiler can allocate up to 15 sets of up to two parallel expanders per set to the macrocells automatically. Each set of two parallel expanders incurs a small, incremental timing delay. Figure 16 shows the APEX 20K parallel expanders.

From Previous Macrocell Product-Macrocell Term Product-Select Term Logic Matrix Parallel Expander Switch Product-Macrocell Term Product-Select Term Logic Matrix Parallel Expander Switch 32 Signals from To Next

Figure 16. APEX 20K Parallel Expanders

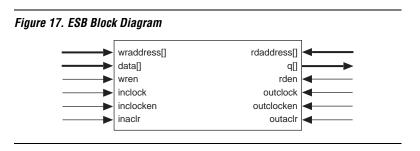

# Embedded System Block

Local Interconnect

The ESB can implement various types of memory blocks, including dual-port RAM, ROM, FIFO, and CAM blocks. The ESB includes input and output registers; the input registers synchronize writes, and the output registers can pipeline designs to improve system performance. The ESB offers a dual-port mode, which supports simultaneous reads and writes at two different clock frequencies. Figure 17 shows the ESB block diagram.

Macrocell

| Symbol                  | Parameter                                     | I/O Standard | -1X Speed Grade |     | -2X Speed Grade |     | Units |  |

|-------------------------|-----------------------------------------------|--------------|-----------------|-----|-----------------|-----|-------|--|

|                         |                                               |              | Min             | Max | Min             | Max | 1     |  |

| f <sub>VCO</sub> (4)    | Voltage controlled oscillator operating range |              | 200             | 500 | 200             | 500 | MHz   |  |

| f <sub>CLOCK0</sub>     | Clock0 PLL output frequency for internal use  |              | 1.5             | 335 | 1.5             | 200 | MHz   |  |

| f <sub>CLOCK1</sub>     | Clock1 PLL output frequency for internal use  |              | 20              | 335 | 20              | 200 | MHz   |  |

| f <sub>CLOCK0_EXT</sub> | Output clock frequency for                    | 3.3-V LVTTL  | 1.5             | 245 | 1.5             | 226 | MHz   |  |

|                         | external clock0 output                        | 2.5-V LVTTL  | 1.5             | 234 | 1.5             | 221 | MHz   |  |

|                         |                                               | 1.8-V LVTTL  | 1.5             | 223 | 1.5             | 216 | MHz   |  |

|                         |                                               | GTL+         | 1.5             | 205 | 1.5             | 193 | MHz   |  |

|                         |                                               | SSTL-2 Class | 1.5             | 158 | 1.5             | 157 | MHz   |  |

|                         |                                               | SSTL-2 Class | 1.5             | 142 | 1.5             | 142 | MHz   |  |

|                         |                                               | SSTL-3 Class | 1.5             | 166 | 1.5             | 162 | MHz   |  |

|                         |                                               | SSTL-3 Class | 1.5             | 149 | 1.5             | 146 | MHz   |  |

|                         |                                               | LVDS         | 1.5             | 420 | 1.5             | 350 | MHz   |  |

| f <sub>CLOCK1_EXT</sub> | Output clock frequency for                    | 3.3-V LVTTL  | 20              | 245 | 20              | 226 | MHz   |  |

|                         | external clock1 output                        | 2.5-V LVTTL  | 20              | 234 | 20              | 221 | MHz   |  |

|                         |                                               | 1.8-V LVTTL  | 20              | 223 | 20              | 216 | MHz   |  |

|                         |                                               | GTL+         | 20              | 205 | 20              | 193 | MHz   |  |

|                         |                                               | SSTL-2 Class | 20              | 158 | 20              | 157 | MHz   |  |

|                         |                                               | SSTL-2 Class | 20              | 142 | 20              | 142 | MHz   |  |

|                         |                                               | SSTL-3 Class | 20              | 166 | 20              | 162 | MHz   |  |

|                         |                                               | SSTL-3 Class | 20              | 149 | 20              | 146 | MHz   |  |

|                         |                                               | LVDS         | 20              | 420 | 20              | 350 | MHz   |  |

| Device     |                     | IDCODE (32 Bits) (1)  |                                    |           |  |  |  |  |  |  |  |

|------------|---------------------|-----------------------|------------------------------------|-----------|--|--|--|--|--|--|--|

|            | Version<br>(4 Bits) | Part Number (16 Bits) | Manufacturer<br>Identity (11 Bits) | 1 (1 Bit) |  |  |  |  |  |  |  |

| EP20K30E   | 0000                | 1000 0000 0011 0000   | 000 0110 1110                      | 1         |  |  |  |  |  |  |  |

| EP20K60E   | 0000                | 1000 0000 0110 0000   | 000 0110 1110                      | 1         |  |  |  |  |  |  |  |

| EP20K100   | 0000                | 0000 0100 0001 0110   | 000 0110 1110                      | 1         |  |  |  |  |  |  |  |

| EP20K100E  | 0000                | 1000 0001 0000 0000   | 000 0110 1110                      | 1         |  |  |  |  |  |  |  |

| EP20K160E  | 0000                | 1000 0001 0110 0000   | 000 0110 1110                      | 1         |  |  |  |  |  |  |  |

| EP20K200   | 0000                | 0000 1000 0011 0010   | 000 0110 1110                      | 1         |  |  |  |  |  |  |  |

| EP20K200E  | 0000                | 1000 0010 0000 0000   | 000 0110 1110                      | 1         |  |  |  |  |  |  |  |

| EP20K300E  | 0000                | 1000 0011 0000 0000   | 000 0110 1110                      | 1         |  |  |  |  |  |  |  |

| EP20K400   | 0000                | 0001 0110 0110 0100   | 000 0110 1110                      | 1         |  |  |  |  |  |  |  |

| EP20K400E  | 0000                | 1000 0100 0000 0000   | 000 0110 1110                      | 1         |  |  |  |  |  |  |  |

| EP20K600E  | 0000                | 1000 0110 0000 0000   | 000 0110 1110                      | 1         |  |  |  |  |  |  |  |

| EP20K1000E | 0000                | 1001 0000 0000 0000   | 000 0110 1110                      | 1         |  |  |  |  |  |  |  |

#### Notes to Table 21:

- (1) The most significant bit (MSB) is on the left.

- (2) The IDCODE's least significant bit (LSB) is always 1.

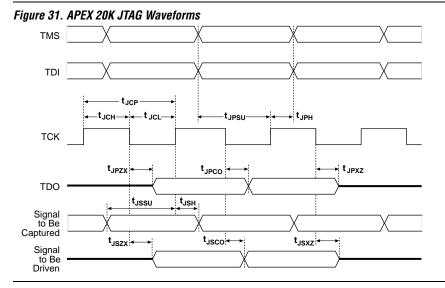

Figure 31 shows the timing requirements for the JTAG signals.

| Symbol                  | Parameter                                                                  | Conditions                                                                             | Min                               | Тур | Max                               | Unit |

|-------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------|-----|-----------------------------------|------|

| V <sub>IH</sub>         | High-level LVTTL, CMOS, or 3.3-V<br>PCI input voltage                      |                                                                                        | 1.7, 0.5 × V <sub>CCIO</sub> (10) |     | 4.1                               | V    |

| V <sub>IL</sub>         | Low-level LVTTL, CMOS, or 3.3-V<br>PCI input voltage                       |                                                                                        | -0.5                              |     | 0.8, 0.3 × V <sub>CCIO</sub> (10) | V    |

| V <sub>OH</sub>         | 3.3-V high-level LVTTL output voltage                                      | I <sub>OH</sub> = -12 mA DC,<br>V <sub>CCIO</sub> = 3.00 V (11)                        | 2.4                               |     |                                   | V    |

|                         | 3.3-V high-level LVCMOS output voltage                                     | $I_{OH} = -0.1 \text{ mA DC},$<br>$V_{CCIO} = 3.00 \text{ V } (11)$                    | V <sub>CCIO</sub> - 0.2           |     |                                   | V    |

|                         | 3.3-V high-level PCI output voltage                                        | $I_{OH} = -0.5 \text{ mA DC},$<br>$V_{CCIO} = 3.00 \text{ to } 3.60 \text{ V}$<br>(11) | 0.9 × V <sub>CCIO</sub>           |     |                                   | V    |

| 2.5-V high-level output | 2.5-V high-level output voltage                                            | I <sub>OH</sub> = -0.1 mA DC,<br>V <sub>CCIO</sub> = 2.30 V (11)                       | 2.1                               |     |                                   | V    |

|                         |                                                                            | $I_{OH} = -1 \text{ mA DC},$<br>$V_{CCIO} = 2.30 \text{ V } (11)$                      | 2.0                               |     |                                   | V    |

|                         |                                                                            | $I_{OH} = -2 \text{ mA DC},$<br>$V_{CCIO} = 2.30 \text{ V } (11)$                      | 1.7                               |     |                                   | V    |

| Ŭ-                      | 3.3-V low-level LVTTL output voltage                                       | $I_{OL}$ = 12 mA DC,<br>$V_{CCIO}$ = 3.00 V (12)                                       |                                   |     | 0.4                               | V    |

|                         | 3.3-V low-level LVCMOS output voltage   3.3-V low-level PCI output voltage | $I_{OL} = 0.1 \text{ mA DC},$<br>$V_{CCIO} = 3.00 \text{ V } (12)$                     |                                   |     | 0.2                               | V    |

|                         |                                                                            | $I_{OL} = 1.5 \text{ mA DC},$<br>$V_{CCIO} = 3.00 \text{ to } 3.60 \text{ V}$<br>(12)  |                                   |     | 0.1 × V <sub>CCIO</sub>           | V    |

|                         | 2.5-V low-level output voltage                                             | I <sub>OL</sub> = 0.1 mA DC,<br>V <sub>CCIO</sub> = 2.30 V (12)                        |                                   |     | 0.2                               | V    |

|                         |                                                                            | I <sub>OL</sub> = 1 mA DC,<br>V <sub>CCIO</sub> = 2.30 V (12)                          |                                   |     | 0.4                               | V    |

|                         |                                                                            | I <sub>OL</sub> = 2 mA DC,<br>V <sub>CCIO</sub> = 2.30 V (12)                          |                                   |     | 0.7                               | V    |

| I <sub>I</sub>          | Input pin leakage current                                                  | V <sub>I</sub> = 4.1 to -0.5 V (13)                                                    | -10                               |     | 10                                | μΑ   |

| I <sub>OZ</sub>         | Tri-stated I/O pin leakage current                                         | $V_0 = 4.1 \text{ to } -0.5 \text{ V } (13)$                                           | -10                               |     | 10                                | μΑ   |

| I <sub>CC0</sub>        | V <sub>CC</sub> supply current (standby)<br>(All ESBs in power-down mode)  | $V_{I} =$ ground, no load, no toggling inputs, -1 speed grade                          |                                   | 10  |                                   | mA   |

|                         |                                                                            | V <sub>I</sub> = ground, no load, no<br>toggling inputs,<br>-2, -3 speed grades        |                                   | 5   |                                   | mA   |

| R <sub>CONF</sub>       | Value of I/O pin pull-up resistor                                          | V <sub>CCIO</sub> = 3.0 V (14)                                                         | 20                                |     | 50                                | kΩ   |

|                         | before and during configuration                                            | V <sub>CCIO</sub> = 2.375 V (14)                                                       | 30                                |     | 80                                | kΩ   |

|                         |                                                                            | V <sub>CCIO</sub> = 1.71 V (14)                                                        | 60                                |     | 150                               | kΩ   |

For DC Operating Specifications on APEX 20KE I/O standards, please refer to *Application Note 117 (Using Selectable I/O Standards in Altera Devices).*

| Table 30. APEX 20KE Device Capacitance Note (15) |                                          |                                     |     |     |      |  |  |  |

|--------------------------------------------------|------------------------------------------|-------------------------------------|-----|-----|------|--|--|--|

| Symbol                                           | Parameter                                | Conditions                          | Min | Max | Unit |  |  |  |

| C <sub>IN</sub>                                  | Input capacitance                        | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 8   | pF   |  |  |  |

| C <sub>INCLK</sub>                               | Input capacitance on dedicated clock pin | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 12  | pF   |  |  |  |

| C <sub>OUT</sub>                                 | Output capacitance                       | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 8   | pF   |  |  |  |

#### Notes to Tables 27 through 30:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to 5.75 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Numbers in parentheses are for industrial-temperature-range devices.

- (4) Maximum V<sub>CC</sub> rise time is 100 ms, and V<sub>CC</sub> must rise monotonically.

- (5) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to the voltage shown in the following table based on input duty cycle for input currents less than 100 mA. The overshoot is dependent upon duty cycle of the signal. The DC case is equivalent to 100% duty cycle.

Vin Max. Duty Cycle 4.0V 100% (DC) 4.1 90% 4.2 50% 4.3 30% 4.4 17% 4.5 10%

- (6) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are powered.

- Typical values are for  $T_A = 25^{\circ}$  C,  $V_{CCINT} = 1.8$  V, and  $V_{CCIO} = 1.8$  V, 2.5 V or 3.3 V.

- (8) These values are specified under the APEX 20KE device recommended operating conditions, shown in Table 24 on page 60.

- (9) Refer to Application Note 117 (Using Selectable I/O Standards in Altera Devices) for the V<sub>IH</sub>, V<sub>IL</sub>, V<sub>OH</sub>, V<sub>OL</sub>, and I<sub>I</sub> parameters when VCCIO = 1.8 V.

- (10) The APEX 20KE input buffers are compatible with 1.8-V, 2.5-V and 3.3-V (LVTTL and LVCMOS) signals. Additionally, the input buffers are 3.3-V PCI compliant. Input buffers also meet specifications for GTL+, CTT, AGP, SSTL-2, SSTL-3, and HSTL.

- (11) The I<sub>OH</sub> parameter refers to high-level TTL, PCI, or CMOS output current.

- (12) The I<sub>OL</sub> parameter refers to low-level TTL, PCI, or CMOS output current. This parameter applies to open-drain pins as well as output pins.

- (13) This value is specified for normal device operation. The value may vary during power-up.

- (14) Pin pull-up resistance values will be lower if an external source drives the pin higher than V<sub>CCIO</sub>.

- (15) Capacitance is sample-tested only.

Figure 33 shows the relationship between  $V_{CCIO}$  and  $V_{CCINT}$  for 3.3-V PCI compliance on APEX 20K devices.

All specifications are always representative of worst-case supply voltage and junction temperature conditions. All output-pin-timing specifications are reported for maximum driver strength.

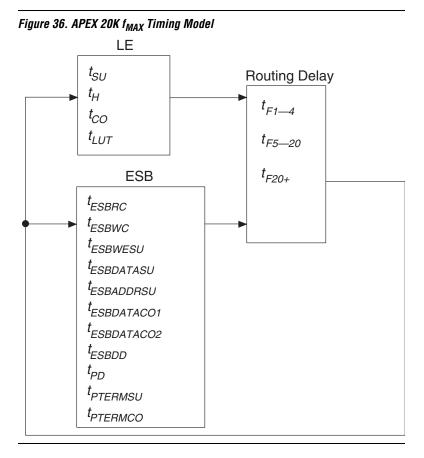

Figure 36 shows the  $f_{MAX}$  timing model for APEX 20K devices.

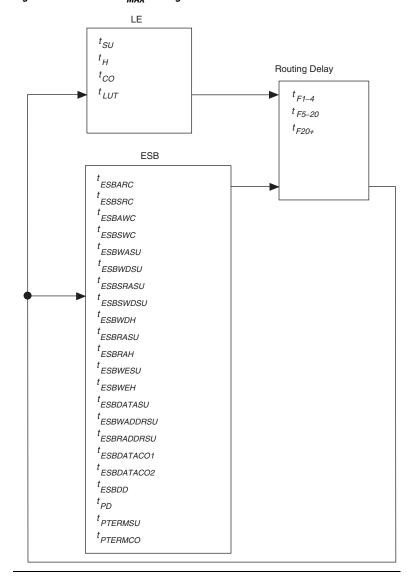

Figure 37 shows the  $f_{MAX}$  timing model for APEX 20KE devices. These parameters can be used to estimate  $f_{MAX}$  for multiple levels of logic. Quartus II software timing analysis should be used for more accurate timing information.

Figure 37. APEX 20KE  $f_{MAX}$  Timing Model

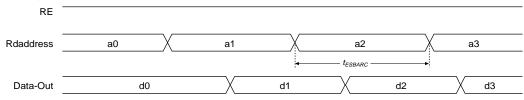

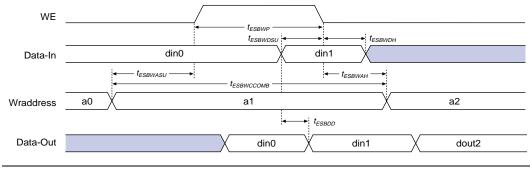

Figures 38 and 39 show the asynchronous and synchronous timing waveforms, respectively, for the ESB macroparameters in Table 31.

Figure 38. ESB Asynchronous Timing Waveforms

### **ESB Asynchronous Write**

| Table 31. APEX 2        | POK f <sub>MAX</sub> Timing Parameters (Part 2 of 2) |   |  |  |  |

|-------------------------|------------------------------------------------------|---|--|--|--|

| Symbol                  | Parameter                                            |   |  |  |  |

| t <sub>ESBDATACO2</sub> | ESB clock-to-output delay without output registers   |   |  |  |  |

| t <sub>ESBDD</sub>      | ESB data-in to data-out delay for RAM mode           |   |  |  |  |

| t <sub>PD</sub>         | ESB macrocell input to non-registered output         |   |  |  |  |

| t <sub>PTERMSU</sub>    | ESB macrocell register setup time before clock       |   |  |  |  |

| t <sub>PTERMCO</sub>    | ESB macrocell register clock-to-output delay         | - |  |  |  |

| t <sub>F1-4</sub>       | Fanout delay using local interconnect                |   |  |  |  |

| t <sub>F5-20</sub>      | Fanout delay using MegaLab Interconnect              |   |  |  |  |

| t <sub>F20+</sub>       | Fanout delay using FastTrack Interconnect            |   |  |  |  |

| t <sub>CH</sub>         | Minimum clock high time from clock pin               |   |  |  |  |

| t <sub>CL</sub>         | Minimum clock low time from clock pin                |   |  |  |  |

| t <sub>CLRP</sub>       | LE clear pulse width                                 |   |  |  |  |

| t <sub>PREP</sub>       | LE preset pulse width                                |   |  |  |  |

| t <sub>ESBCH</sub>      | Clock high time                                      |   |  |  |  |

| t <sub>ESBCL</sub>      | Clock low time                                       |   |  |  |  |

| t <sub>ESBWP</sub>      | Write pulse width                                    |   |  |  |  |

| t <sub>ESBRP</sub>      | Read pulse width                                     |   |  |  |  |

Tables 32 and 33 describe APEX 20K external timing parameters.

| Table 32. APEX 20K External Timing Parameters Note (1) |                                                         |  |  |  |  |

|--------------------------------------------------------|---------------------------------------------------------|--|--|--|--|

| Symbol                                                 | Clock Parameter                                         |  |  |  |  |

| t <sub>INSU</sub>                                      | Setup time with global clock at IOE register            |  |  |  |  |

| t <sub>INH</sub>                                       | Hold time with global clock at IOE register             |  |  |  |  |

| tоитсо                                                 | Clock-to-output delay with global clock at IOE register |  |  |  |  |

| Table 33. APEX 20K External Bidirectional Timing Parameters       Note (1) |                                                                                            |            |  |  |  |  |

|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------|--|--|--|--|

| Symbol                                                                     | Parameter                                                                                  | Conditions |  |  |  |  |

| t <sub>INSUBIDIR</sub>                                                     | Setup time for bidirectional pins with global clock at same-row or same-column LE register |            |  |  |  |  |

| t <sub>INHBIDIR</sub>                                                      | Hold time for bidirectional pins with global clock at same-row or same-column LE register  |            |  |  |  |  |

| <sup>t</sup> OUTCOBIDIR                                                    | Clock-to-output delay for bidirectional pins with global clock at IOE register             | C1 = 10 pF |  |  |  |  |

| t <sub>XZBIDIR</sub>                                                       | Synchronous IOE output buffer disable delay                                                | C1 = 10 pF |  |  |  |  |

| t <sub>ZXBIDIR</sub>                                                       | Synchronous IOE output buffer enable delay, slow slew rate = off                           | C1 = 10 pF |  |  |  |  |

| Symbol             | -1   | -1  |      | -2  |      | -3  |    |

|--------------------|------|-----|------|-----|------|-----|----|

|                    | Min  | Max | Min  | Max | Min  | Max |    |

| t <sub>CH</sub>    | 1.25 |     | 1.43 |     | 1.67 |     | ns |

| t <sub>CL</sub>    | 1.25 |     | 1.43 |     | 1.67 |     | ns |

| t <sub>CLRP</sub>  | 0.19 |     | 0.26 |     | 0.35 |     | ns |

| t <sub>PREP</sub>  | 0.19 |     | 0.26 |     | 0.35 |     | ns |

| t <sub>ESBCH</sub> | 1.25 |     | 1.43 |     | 1.67 |     | ns |

| t <sub>ESBCL</sub> | 1.25 |     | 1.43 |     | 1.67 |     | ns |

| t <sub>ESBWP</sub> | 1.25 |     | 1.71 |     | 2.28 |     | ns |

| t <sub>ESBRP</sub> | 1.01 |     | 1.38 |     | 1.84 |     | ns |

| Symbol               | -1   |      | -2   |      | -3   |      | Unit |

|----------------------|------|------|------|------|------|------|------|

|                      | Min  | Max  | Min  | Max  | Min  | Max  |      |

| t <sub>INSU</sub>    | 2.31 |      | 2.44 |      | 2.57 |      | ns   |

| t <sub>INH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>OUTCO</sub>   | 2.00 | 5.29 | 2.00 | 5.82 | 2.00 | 6.24 | ns   |

| t <sub>INSUPLL</sub> | 1.76 |      | 1.85 |      | -    |      | ns   |

| t <sub>INHPLL</sub>  | 0.00 |      | 0.00 |      | -    |      | ns   |

| toutcople            | 0.50 | 2.65 | 0.50 | 2.95 | _    | -    | ns   |

| Symbol                    | -1   |      | -2   |      | -3   |      | Unit |

|---------------------------|------|------|------|------|------|------|------|

|                           | Min  | Max  | Min  | Max  | Min  | Max  |      |

| t <sub>INSUBIDIR</sub>    | 2.77 |      | 2.85 |      | 3.11 |      | ns   |

| t <sub>INHBIDIR</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>OUTCOBIDIR</sub>   | 2.00 | 5.29 | 2.00 | 5.82 | 2.00 | 6.24 | ns   |

| t <sub>XZBIDIR</sub>      |      | 7.59 |      | 8.30 |      | 9.09 | ns   |

| t <sub>ZXBIDIR</sub>      |      | 7.59 |      | 8.30 |      | 9.09 | ns   |

| t <sub>INSUBIDIRPLL</sub> | 2.50 |      | 2.76 |      | -    |      | ns   |

| t <sub>INHBIDIRPLL</sub>  | 0.00 |      | 0.00 |      | -    |      | ns   |

| toutcobidirpll            | 0.50 | 2.65 | 0.50 | 2.95 | -    | -    | ns   |

| <sup>t</sup> xzbidirpll   |      | 5.00 |      | 5.43 |      | -    | ns   |

| tzxbidirpll               |      | 5.00 |      | 5.43 |      | -    | ns   |

| Symbol                  | -1 Speed Grade |      | -2 Spee | -2 Speed Grade |       | -3 Speed Grade |    |  |

|-------------------------|----------------|------|---------|----------------|-------|----------------|----|--|

|                         | Min            | Max  | Min     | Max            | Min   | Max            |    |  |

| t <sub>ESBARC</sub>     |                | 1.67 |         | 1.91           |       | 1.99           | ns |  |

| t <sub>ESBSRC</sub>     |                | 2.30 |         | 2.66           |       | 2.93           | ns |  |

| t <sub>ESBAWC</sub>     |                | 3.09 |         | 3.58           |       | 3.99           | ns |  |

| t <sub>ESBSWC</sub>     |                | 3.01 |         | 3.65           |       | 4.05           | ns |  |

| t <sub>ESBWASU</sub>    | 0.54           |      | 0.63    |                | 0.65  |                | ns |  |

| t <sub>ESBWAH</sub>     | 0.36           |      | 0.43    |                | 0.42  |                | ns |  |

| t <sub>ESBWDSU</sub>    | 0.69           |      | 0.77    |                | 0.84  |                | ns |  |

| t <sub>ESBWDH</sub>     | 0.36           |      | 0.43    |                | 0.42  |                | ns |  |

| t <sub>ESBRASU</sub>    | 1.61           |      | 1.77    |                | 1.86  |                | ns |  |

| t <sub>ESBRAH</sub>     | 0.00           |      | 0.00    |                | 0.01  |                | ns |  |

| t <sub>ESBWESU</sub>    | 1.35           |      | 1.47    |                | 1.61  |                | ns |  |

| t <sub>ESBWEH</sub>     | 0.00           |      | 0.00    |                | 0.00  |                | ns |  |

| t <sub>ESBDATASU</sub>  | -0.18          |      | -0.30   |                | -0.27 |                | ns |  |

| t <sub>ESBDATAH</sub>   | 0.13           |      | 0.13    |                | 0.13  |                | ns |  |

| t <sub>ESBWADDRSU</sub> | -0.02          |      | -0.11   |                | -0.03 |                | ns |  |

| t <sub>ESBRADDRSU</sub> | 0.06           |      | -0.01   |                | -0.05 |                | ns |  |

| t <sub>ESBDATACO1</sub> |                | 1.16 |         | 1.40           |       | 1.54           | ns |  |

| t <sub>ESBDATACO2</sub> |                | 2.18 |         | 2.55           |       | 2.85           | ns |  |

| t <sub>ESBDD</sub>      |                | 2.73 |         | 3.17           |       | 3.58           | ns |  |

| t <sub>PD</sub>         |                | 1.57 |         | 1.83           |       | 2.07           | ns |  |

| t <sub>PTERMSU</sub>    | 0.92           |      | 0.99    |                | 1.18  |                | ns |  |

| t <sub>PTERMCO</sub>    |                | 1.18 |         | 1.43           |       | 1.17           | ns |  |

| Table 92. EP20K600E f <sub>MAX</sub> ESB Timing Microparameters |                |      |                |      |                |      |      |

|-----------------------------------------------------------------|----------------|------|----------------|------|----------------|------|------|

| Symbol                                                          | -1 Speed Grade |      | -2 Speed Grade |      | -3 Speed Grade |      | Unit |

|                                                                 | Min            | Max  | Min            | Max  | Min            | Max  | ╡ !  |

| t <sub>ESBARC</sub>                                             |                | 1.67 |                | 2.39 |                | 3.11 | ns   |

| t <sub>ESBSRC</sub>                                             |                | 2.27 |                | 3.07 |                | 3.86 | ns   |

| t <sub>ESBAWC</sub>                                             |                | 3.19 |                | 4.56 |                | 5.93 | ns   |

| t <sub>ESBSWC</sub>                                             |                | 3.51 |                | 4.62 |                | 5.72 | ns   |

| t <sub>ESBWASU</sub>                                            | 1.46           |      | 2.08           |      | 2.70           |      | ns   |

| t <sub>ESBWAH</sub>                                             | 0.00           |      | 0.00           |      | 0.00           |      | ns   |

| t <sub>ESBWDSU</sub>                                            | 1.60           |      | 2.29           |      | 2.97           |      | ns   |

| t <sub>ESBWDH</sub>                                             | 0.00           |      | 0.00           |      | 0.00           |      | ns   |

| t <sub>ESBRASU</sub>                                            | 1.61           |      | 2.30           |      | 2.99           |      | ns   |

| t <sub>ESBRAH</sub>                                             | 0.00           |      | 0.00           |      | 0.00           |      | ns   |

| t <sub>ESBWESU</sub>                                            | 1.49           |      | 2.30           |      | 3.11           |      | ns   |

| t <sub>ESBWEH</sub>                                             | 0.00           |      | 0.00           |      | 0.00           |      | ns   |

| t <sub>ESBDATASU</sub>                                          | -0.01          |      | 0.35           |      | 0.71           |      | ns   |

| t <sub>ESBDATAH</sub>                                           | 0.13           |      | 0.13           |      | 0.13           |      | ns   |

| t <sub>ESBWADDRSU</sub>                                         | 0.19           |      | 0.62           |      | 1.06           |      | ns   |

| t <sub>ESBRADDRSU</sub>                                         | 0.25           |      | 0.71           |      | 1.17           |      | ns   |

| t <sub>ESBDATACO1</sub>                                         |                | 1.01 |                | 1.19 |                | 1.37 | ns   |

| t <sub>ESBDATACO2</sub>                                         |                | 2.18 |                | 3.12 |                | 4.05 | ns   |

| t <sub>ESBDD</sub>                                              |                | 3.19 |                | 4.56 |                | 5.93 | ns   |

| t <sub>PD</sub>                                                 |                | 1.57 |                | 2.25 |                | 2.92 | ns   |

| t <sub>PTERMSU</sub>                                            | 0.85           |      | 1.43           |      | 2.01           |      | ns   |

| t <sub>PTERMCO</sub>                                            |                | 1.03 |                | 1.21 |                | 1.39 | ns   |

| Table 93. EP20K600E f <sub>MAX</sub> Routing Delays |     |                  |     |          |                |      |      |

|-----------------------------------------------------|-----|------------------|-----|----------|----------------|------|------|

| Symbol -1 Spee                                      |     | d Grade -2 Speed |     | ed Grade | -3 Speed Grade |      | Unit |

|                                                     | Min | Max              | Min | Max      | Min            | Max  |      |

| t <sub>F1-4</sub>                                   |     | 0.22             |     | 0.25     |                | 0.26 | ns   |

| t <sub>F5-20</sub>                                  |     | 1.26             |     | 1.39     |                | 1.52 | ns   |

| t <sub>F20+</sub>                                   |     | 3.51             |     | 3.88     |                | 4.26 | ns   |

| Symbol                  | -1 Speed Grade |      | -2 Speed Grade |      | -3 Speed Grade |      | Unit |

|-------------------------|----------------|------|----------------|------|----------------|------|------|

|                         | Min            | Max  | Min            | Max  | Min            | Max  | 1    |

| t <sub>ESBARC</sub>     |                | 1.78 |                | 2.02 |                | 1.95 | ns   |

| t <sub>ESBSRC</sub>     |                | 2.52 |                | 2.91 |                | 3.14 | ns   |

| t <sub>ESBAWC</sub>     |                | 3.52 |                | 4.11 |                | 4.40 | ns   |

| t <sub>ESBSWC</sub>     |                | 3.23 |                | 3.84 |                | 4.16 | ns   |

| t <sub>ESBWASU</sub>    | 0.62           |      | 0.67           |      | 0.61           |      | ns   |

| t <sub>ESBWAH</sub>     | 0.41           |      | 0.55           |      | 0.55           |      | ns   |

| t <sub>ESBWDSU</sub>    | 0.77           |      | 0.79           |      | 0.81           |      | ns   |

| t <sub>ESBWDH</sub>     | 0.41           |      | 0.55           |      | 0.55           |      | ns   |

| t <sub>ESBRASU</sub>    | 1.74           |      | 1.92           |      | 1.85           |      | ns   |

| t <sub>ESBRAH</sub>     | 0.00           |      | 0.01           |      | 0.23           |      | ns   |

| t <sub>ESBWESU</sub>    | 2.07           |      | 2.28           |      | 2.41           |      | ns   |

| t <sub>ESBWEH</sub>     | 0.00           |      | 0.00           |      | 0.00           |      | ns   |

| t <sub>ESBDATASU</sub>  | 0.25           |      | 0.27           |      | 0.29           |      | ns   |

| t <sub>ESBDATAH</sub>   | 0.13           |      | 0.13           |      | 0.13           |      | ns   |

| t <sub>ESBWADDRSU</sub> | 0.11           |      | 0.04           |      | 0.11           |      | ns   |

| t <sub>ESBRADDRSU</sub> | 0.14           |      | 0.11           |      | 0.16           |      | ns   |

| t <sub>ESBDATACO1</sub> |                | 1.29 |                | 1.50 |                | 1.63 | ns   |

| t <sub>ESBDATACO2</sub> |                | 2.55 |                | 2.99 |                | 3.22 | ns   |

| t <sub>ESBDD</sub>      |                | 3.12 |                | 3.57 |                | 3.85 | ns   |

| t <sub>PD</sub>         |                | 1.84 |                | 2.13 |                | 2.32 | ns   |

| t <sub>PTERMSU</sub>    | 1.08           |      | 1.19           |      | 1.32           | _    | ns   |

| t <sub>PTERMCO</sub>    |                | 1.31 |                | 1.53 |                | 1.66 | ns   |

| Table 105. EP20K1500E f <sub>MAX</sub> Routing Delays |         |         |                      |      |                |      |      |

|-------------------------------------------------------|---------|---------|----------------------|------|----------------|------|------|

| Symbol                                                | -1 Spee | d Grade | Grade -2 Speed Grade |      | -3 Speed Grade |      | Unit |

|                                                       | Min     | Max     | Min                  | Max  | Min            | Max  |      |

| t <sub>F1-4</sub>                                     |         | 0.28    |                      | 0.28 |                | 0.28 | ns   |

| t <sub>F5-20</sub>                                    |         | 1.36    |                      | 1.50 |                | 1.62 | ns   |

| t <sub>F20+</sub>                                     |         | 4.43    |                      | 4.48 |                | 5.07 | ns   |

SRAM configuration elements allow APEX 20K devices to be reconfigured in-circuit by loading new configuration data into the device. Real-time reconfiguration is performed by forcing the device into command mode with a device pin, loading different configuration data, reinitializing the device, and resuming usermode operation. In-field upgrades can be performed by distributing new configuration files.

### **Configuration Schemes**

The configuration data for an APEX 20K device can be loaded with one of five configuration schemes (see Table 111), chosen on the basis of the target application. An EPC2 or EPC16 configuration device, intelligent controller, or the JTAG port can be used to control the configuration of an APEX 20K device. When a configuration device is used, the system can configure automatically at system power-up.

Multiple APEX 20K devices can be configured in any of five configuration schemes by connecting the configuration enable (nCE) and configuration enable output (nCEO) pins on each device.

| Table 111. Data Sources for Configuration |                                                                                          |  |  |  |

|-------------------------------------------|------------------------------------------------------------------------------------------|--|--|--|

| Configuration Scheme                      | Data Source                                                                              |  |  |  |

| Configuration device                      | EPC1, EPC2, EPC16 configuration devices                                                  |  |  |  |

| Passive serial (PS)                       | MasterBlaster or ByteBlasterMV download cable or serial data source                      |  |  |  |

| Passive parallel asynchronous (PPA)       | Parallel data source                                                                     |  |  |  |

| Passive parallel synchronous (PPS)        | Parallel data source                                                                     |  |  |  |

| JTAG                                      | MasterBlaster or ByteBlasterMV download cable or a microprocessor with a Jam or JBC File |  |  |  |

For more information on configuration, see *Application Note* 116 (*Configuring APEX 20K, FLEX 10K, & FLEX 6000 Devices.*)

## **Device Pin-Outs**

See the Altera web site (http://www.altera.com) or the *Altera Digital Library* for pin-out information