Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 416                                                          |

| Number of Logic Elements/Cells | 4160                                                         |

| Total RAM Bits                 | 53248                                                        |

| Number of I/O                  | 246                                                          |

| Number of Gates                | 263000                                                       |

| Voltage - Supply               | 1.71V ~ 1.89V                                                |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                           |

| Package / Case                 | 356-LBGA                                                     |

| Supplier Device Package        | 356-BGA (35x35)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep20k100ebi356-2x |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Flexible clock management circuitry with up to four phase-locked loops (PLLs)

- Built-in low-skew clock tree

- Up to eight global clock signals

- ClockLock<sup>®</sup> feature reducing clock delay and skew

- ClockBoost<sup>®</sup> feature providing clock multiplication and division

- ClockShift™ programmable clock phase and delay shifting

# Powerful I/O features

- Compliant with peripheral component interconnect Special Interest Group (PCI SIG) PCI Local Bus Specification, Revision 2.2 for 3.3-V operation at 33 or 66 MHz and 32 or 64 bits

- Support for high-speed external memories, including DDR SDRAM and ZBT SRAM (ZBT is a trademark of Integrated Device Technology, Inc.)

- Bidirectional I/O performance ( $t_{CO} + t_{SU}$ ) up to 250 MHz

- LVDS performance up to 840 Mbits per channel

- Direct connection from I/O pins to local interconnect providing fast t<sub>CO</sub> and t<sub>SU</sub> times for complex logic

- MultiVolt I/O interface support to interface with 1.8-V, 2.5-V,

3.3-V, and 5.0-V devices (see Table 3)

- Programmable clamp to V<sub>CCIO</sub>

- Individual tri-state output enable control for each pin

- Programmable output slew-rate control to reduce switching noise

- Support for advanced I/O standards, including low-voltage differential signaling (LVDS), LVPECL, PCI-X, AGP, CTT, stubseries terminated logic (SSTL-3 and SSTL-2), Gunning transceiver logic plus (GTL+), and high-speed terminated logic (HSTL Class I)

- Pull-up on I/O pins before and during configuration

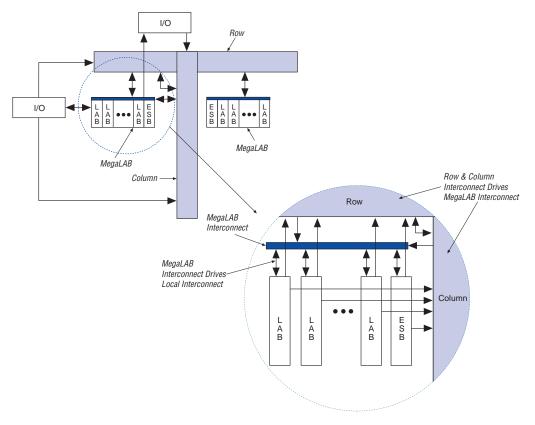

#### Advanced interconnect structure

- Four-level hierarchical FastTrack<sup>®</sup> Interconnect structure providing fast, predictable interconnect delays

- Dedicated carry chain that implements arithmetic functions such as fast adders, counters, and comparators (automatically used by software tools and megafunctions)

- Dedicated cascade chain that implements high-speed, high-fan-in logic functions (automatically used by software tools and megafunctions)

- Interleaved local interconnect allows one LE to drive 29 other LEs through the fast local interconnect

## Advanced packaging options

- Available in a variety of packages with 144 to 1,020 pins (see Tables 4 through 7)

- FineLine BGA® packages maximize board space efficiency

#### Advanced software support

Software design support and automatic place-and-route provided by the Altera® Quartus® II development system for

- Windows-based PCs, Sun SPARCstations, and HP 9000 Series 700/800 workstations

- Altera MegaCore® functions and Altera Megafunction Partners Program (AMPP<sup>SM</sup>) megafunctions

- NativeLink™ integration with popular synthesis, simulation, and timing analysis tools

- Quartus II SignalTap<sup>®</sup> embedded logic analyzer simplifies in-system design evaluation by giving access to internal nodes during device operation

- Supports popular revision-control software packages including PVCS, Revision Control System (RCS), and Source Code Control System (SCCS)

| Device     | 144-Pin<br>TQFP | 208-Pin<br>PQFP<br>RQFP | 240-Pin<br>PQFP<br>RQFP | 356-Pin BGA | 652-Pin BGA | 655-Pin PGA |

|------------|-----------------|-------------------------|-------------------------|-------------|-------------|-------------|

| EP20K30E   | 92              | 125                     |                         |             |             |             |

| EP20K60E   | 92              | 148                     | 151                     | 196         |             |             |

| EP20K100   | 101             | 159                     | 189                     | 252         |             |             |

| EP20K100E  | 92              | 151                     | 183                     | 246         |             |             |

| EP20K160E  | 88              | 143                     | 175                     | 271         |             |             |

| EP20K200   |                 | 144                     | 174                     | 277         |             |             |

| EP20K200E  |                 | 136                     | 168                     | 271         | 376         |             |

| EP20K300E  |                 |                         | 152                     |             | 408         |             |

| EP20K400   |                 |                         |                         |             | 502         | 502         |

| EP20K400E  |                 |                         |                         |             | 488         |             |

| EP20K600E  |                 |                         |                         |             | 488         |             |

| EP20K1000E |                 |                         |                         |             | 488         |             |

| EP20K1500E |                 |                         |                         |             | 488         |             |

| Table 5. APEX 20K F | Table 5. APEX 20K FineLine BGA Package Options & I/O Count       Notes (1), (2) |         |         |                |           |

|---------------------|---------------------------------------------------------------------------------|---------|---------|----------------|-----------|

| Device              | 144 Pin                                                                         | 324 Pin | 484 Pin | 672 Pin        | 1,020 Pin |

| EP20K30E            | 93                                                                              | 128     |         |                |           |

| EP20K60E            | 93                                                                              | 196     |         |                |           |

| EP20K100            |                                                                                 | 252     |         |                |           |

| EP20K100E           | 93                                                                              | 246     |         |                |           |

| EP20K160E           |                                                                                 |         | 316     |                |           |

| EP20K200            |                                                                                 |         | 382     |                |           |

| EP20K200E           |                                                                                 |         | 376     | 376            |           |

| EP20K300E           |                                                                                 |         |         | 408            |           |

| EP20K400            |                                                                                 |         |         | 502 <i>(3)</i> |           |

| EP20K400E           |                                                                                 |         |         | 488 (3)        |           |

| EP20K600E           |                                                                                 |         |         | 508 (3)        | 588       |

| EP20K1000E          |                                                                                 |         |         | 508 (3)        | 708       |

| EP20K1500E          |                                                                                 |         |         |                | 808       |

#### Notes to Tables 4 and 5:

- (1) I/O counts include dedicated input and clock pins.

- (2) APEX 20K device package types include thin quad flat pack (TQFP), plastic quad flat pack (PQFP), power quad flat pack (RQFP), 1.27-mm pitch ball-grid array (BGA), 1.00-mm pitch FineLine BGA, and pin-grid array (PGA) packages.

- (3) This device uses a thermally enhanced package, which is taller than the regular package. Consult the *Altera Device Package Information Data Sheet* for detailed package size information.

| Table 6. APEX 20K QFP, BGA & PGA Package Sizes                                                   |              |             |             |             |             |             |

|--------------------------------------------------------------------------------------------------|--------------|-------------|-------------|-------------|-------------|-------------|

| Feature                                                                                          | 144-Pin TQFP | 208-Pin QFP | 240-Pin QFP | 356-Pin BGA | 652-Pin BGA | 655-Pin PGA |

| Pitch (mm)                                                                                       | 0.50         | 0.50        | 0.50        | 1.27        | 1.27        | _           |

| Area (mm <sup>2</sup> )                                                                          | 484          | 924         | 1,218       | 1,225       | 2,025       | 3,906       |

| $\begin{array}{c} \text{Length} \times \text{Width} \\ \text{(mm} \times \text{mm)} \end{array}$ | 22 × 22      | 30.4 × 30.4 | 34.9 × 34.9 | 35 × 35     | 45 × 45     | 62.5 × 62.5 |

| Table 7. APEX 20K FineLine BGA Package Sizes |         |         |         |         |           |

|----------------------------------------------|---------|---------|---------|---------|-----------|

| Feature                                      | 144 Pin | 324 Pin | 484 Pin | 672 Pin | 1,020 Pin |

| Pitch (mm)                                   | 1.00    | 1.00    | 1.00    | 1.00    | 1.00      |

| Area (mm <sup>2</sup> )                      | 169     | 361     | 529     | 729     | 1,089     |

| $Length \times Width (mm \times mm)$         | 13 × 13 | 19×19   | 23 × 23 | 27 × 27 | 33 × 33   |

| Feature                                                                                                              | APEX 20K Devices                                                                                                                                  | APEX 20KE Devices                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MultiCore system integration                                                                                         | Full support                                                                                                                                      | Full support                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| SignalTap logic analysis                                                                                             | Full support                                                                                                                                      | Full support                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 32/64-Bit, 33-MHz PCI                                                                                                | Full compliance in -1, -2 speed grades                                                                                                            | Full compliance in -1, -2 speed grades                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 32/64-Bit, 66-MHz PCI                                                                                                | -                                                                                                                                                 | Full compliance in -1 speed grade                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| MultiVolt I/O  2.5-V or 3.3-V V <sub>CCIO</sub> V <sub>CCIO</sub> selected for device  Certain devices are 5.0-V tol |                                                                                                                                                   | 1.8-V, 2.5-V, or 3.3-V V <sub>CCIO</sub> V <sub>CCIO</sub> selected block-by-block 5.0-V tolerant with use of external resistor                                                                                                                                                                                                                                                                                    |  |  |

| Drive ClockLock output off-<br>External clock feedback<br>ClockShift<br>LVDS support<br>Up to four PLLs              |                                                                                                                                                   | $m/(n \times v)$ or $m/(n \times k)$ clock multiplication<br>Drive ClockLock output off-chip<br>External clock feedback<br>ClockShift<br>LVDS support                                                                                                                                                                                                                                                              |  |  |

| Dedicated clock and input pins                                                                                       | Six                                                                                                                                               | Eight                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| I/O standard support                                                                                                 | 2.5-V, 3.3-V, 5.0-V I/O 3.3-V PCI Low-voltage complementary metal-oxide semiconductor (LVCMOS) Low-voltage transistor-to-transistor logic (LVTTL) | 1.8-V, 2.5-V, 3.3-V, 5.0-V I/O 2.5-V I/O 3.3-V PCI and PCI-X 3.3-V Advanced Graphics Port (AGP) Center tap terminated (CTT) GTL+ LVCMOS LVTTL True-LVDS and LVPECL data pins (in EP20K300E and larger devices) LVDS and LVPECL signaling (in all BGA and FineLine BGA devices) LVDS and LVPECL data pins up to 156 Mbps (in -1 speed grade devices) HSTL Class I PCI-X SSTL-2 Class I and II SSTL-3 Class I and II |  |  |

| Memory support                                                                                                       | Dual-port RAM<br>FIFO<br>RAM<br>ROM                                                                                                               | CAM Dual-port RAM FIFO RAM ROM                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

All APEX 20K devices are reconfigurable and are 100% tested prior to shipment. As a result, test vectors do not have to be generated for fault coverage purposes. Instead, the designer can focus on simulation and design verification. In addition, the designer does not need to manage inventories of different application-specific integrated circuit (ASIC) designs; APEX 20K devices can be configured on the board for the specific functionality required.

APEX 20K devices are configured at system power-up with data stored in an Altera serial configuration device or provided by a system controller. Altera offers in-system programmability (ISP)-capable EPC1, EPC2, and EPC16 configuration devices, which configure APEX 20K devices via a serial data stream. Moreover, APEX 20K devices contain an optimized interface that permits microprocessors to configure APEX 20K devices serially or in parallel, and synchronously or asynchronously. The interface also enables microprocessors to treat APEX 20K devices as memory and configure the device by writing to a virtual memory location, making reconfiguration easy.

After an APEX 20K device has been configured, it can be reconfigured in-circuit by resetting the device and loading new data. Real-time changes can be made during system operation, enabling innovative reconfigurable computing applications.

APEX 20K devices are supported by the Altera Quartus II development system, a single, integrated package that offers HDL and schematic design entry, compilation and logic synthesis, full simulation and worst-case timing analysis, SignalTap logic analysis, and device configuration. The Quartus II software runs on Windows-based PCs, Sun SPARCstations, and HP 9000 Series 700/800 workstations.

The Quartus II software provides NativeLink interfaces to other industry-standard PC- and UNIX workstation-based EDA tools. For example, designers can invoke the Quartus II software from within third-party design tools. Further, the Quartus II software contains built-in optimized synthesis libraries; synthesis tools can use these libraries to optimize designs for APEX 20K devices. For example, the Synopsys Design Compiler library, supplied with the Quartus II development system, includes DesignWare functions optimized for the APEX 20K architecture.

Each LE has two outputs that drive the local, MegaLAB, or FastTrack Interconnect routing structure. Each output can be driven independently by the LUT's or register's output. For example, the LUT can drive one output while the register drives the other output. This feature, called register packing, improves device utilization because the register and the LUT can be used for unrelated functions. The LE can also drive out registered and unregistered versions of the LUT output.

The APEX 20K architecture provides two types of dedicated high-speed data paths that connect adjacent LEs without using local interconnect paths: carry chains and cascade chains. A carry chain supports high-speed arithmetic functions such as counters and adders, while a cascade chain implements wide-input functions such as equality comparators with minimum delay. Carry and cascade chains connect LEs 1 through 10 in an LAB and all LABs in the same MegaLAB structure.

# Carry Chain

The carry chain provides a very fast carry-forward function between LEs. The carry-in signal from a lower-order bit drives forward into the higher-order bit via the carry chain, and feeds into both the LUT and the next portion of the carry chain. This feature allows the APEX 20K architecture to implement high-speed counters, adders, and comparators of arbitrary width. Carry chain logic can be created automatically by the Quartus II software Compiler during design processing, or manually by the designer during design entry. Parameterized functions such as library of parameterized modules (LPM) and DesignWare functions automatically take advantage of carry chains for the appropriate functions.

The Quartus II software Compiler creates carry chains longer than ten LEs by linking LABs together automatically. For enhanced fitting, a long carry chain skips alternate LABs in a MegaLAB<sup>TM</sup> structure. A carry chain longer than one LAB skips either from an even-numbered LAB to the next even-numbered LAB, or from an odd-numbered LAB to the next odd-numbered LAB. For example, the last LE of the first LAB in the upper-left MegaLAB structure carries to the first LE of the third LAB in the MegaLAB structure.

Figure 6 shows how an n-bit full adder can be implemented in n+1 LEs with the carry chain. One portion of the LUT generates the sum of two bits using the input signals and the carry-in signal; the sum is routed to the output of the LE. The register can be bypassed for simple adders or used for accumulator functions. Another portion of the LUT and the carry chain logic generates the carry-out signal, which is routed directly to the carryin signal of the next-higher-order bit. The final carry-out signal is routed to an LE, where it is driven onto the local, MegaLAB, or FastTrack Interconnect routing structures.

Figure 10. FastTrack Connection to Local Interconnect

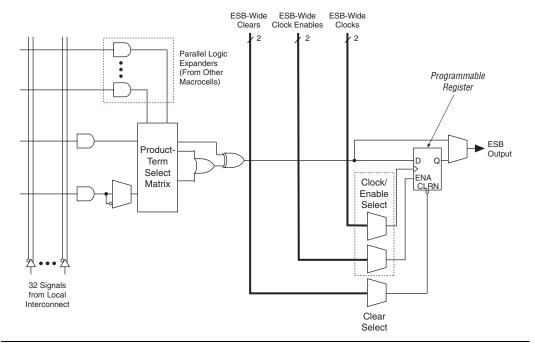

Figure 14. APEX 20K Macrocell

For registered functions, each macrocell register can be programmed individually to implement D, T, JK, or SR operation with programmable clock control. The register can be bypassed for combinatorial operation. During design entry, the designer specifies the desired register type; the Quartus II software then selects the most efficient register operation for each registered function to optimize resource utilization. The Quartus II software or other synthesis tools can also select the most efficient register operation automatically when synthesizing HDL designs.

Each programmable register can be clocked by one of two ESB-wide clocks. The ESB-wide clocks can be generated from device dedicated clock pins, global signals, or local interconnect. Each clock also has an associated clock enable, generated from the local interconnect. The clock and clock enable signals are related for a particular ESB; any macrocell using a clock also uses the associated clock enable.

If both the rising and falling edges of a clock are used in an ESB, both ESB-wide clock signals are used.

For more information on APEX 20KE devices and CAM, see *Application Note 119 (Implementing High-Speed Search Applications with APEX CAM).*

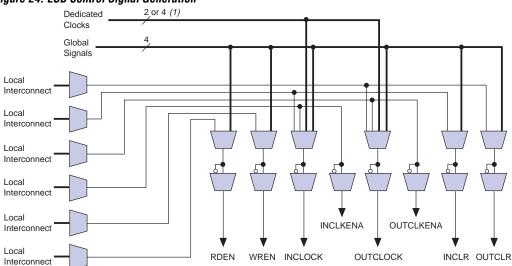

# **Driving Signals to the ESB**

ESBs provide flexible options for driving control signals. Different clocks can be used for the ESB inputs and outputs. Registers can be inserted independently on the data input, data output, read address, write address, WE, and RE signals. The global signals and the local interconnect can drive the WE and RE signals. The global signals, dedicated clock pins, and local interconnect can drive the ESB clock signals. Because the LEs drive the local interconnect, the LEs can control the WE and RE signals and the ESB clock, clock enable, and asynchronous clear signals. Figure 24 shows the ESB control signal generation logic.

Figure 24. ESB Control Signal Generation

Note to Figure 24:

(1) APEX 20KE devices have four dedicated clocks.

An ESB is fed by the local interconnect, which is driven by adjacent LEs (for high-speed connection to the ESB) or the MegaLAB interconnect. The ESB can drive the local, MegaLAB, or FastTrack Interconnect routing structure to drive LEs and IOEs in the same MegaLAB structure or anywhere in the device.

APEX 20KE devices include an enhanced IOE, which drives the FastRow interconnect. The FastRow interconnect connects a column I/O pin directly to the LAB local interconnect within two MegaLAB structures. This feature provides fast setup times for pins that drive high fan-outs with complex logic, such as PCI designs. For fast bidirectional I/O timing, LE registers using local routing can improve setup times and OE timing. The APEX 20KE IOE also includes direct support for open-drain operation, giving faster clock-to-output for open-drain signals. Some programmable delays in the APEX 20KE IOE offer multiple levels of delay to fine-tune setup and hold time requirements. The Quartus II software compiler can set these delays automatically to minimize setup time while providing a zero hold time.

Table 11 describes the APEX 20KE programmable delays and their logic options in the Quartus II software.

| Table 11. APEX 20KE Programmable Delay Chains |                                         |  |  |  |

|-----------------------------------------------|-----------------------------------------|--|--|--|

| Programmable Delays                           | Quartus II Logic Option                 |  |  |  |

| Input Pin to Core Delay                       | Decrease input delay to internal cells  |  |  |  |

| Input Pin to Input Register Delay             | Decrease input delay to input registers |  |  |  |

| Core to Output Register Delay                 | Decrease input delay to output register |  |  |  |

| Output Register t <sub>CO</sub> Delay         | Increase delay to output pin            |  |  |  |

| Clock Enable Delay                            | Increase clock enable delay             |  |  |  |

The register in the APEX 20KE IOE can be programmed to power-up high or low after configuration is complete. If it is programmed to power-up low, an asynchronous clear can control the register. If it is programmed to power-up high, an asynchronous preset can control the register. Figure 26 shows how fast bidirectional I/O pins are implemented in APEX 20KE devices. This feature is useful for cases where the APEX 20KE device controls an active-low input or another device; it prevents inadvertent activation of the input upon power-up.

# Advanced I/O Standard Support

APEX 20KE IOEs support the following I/O standards: LVTTL, LVCMOS, 1.8-V I/O, 2.5-V I/O, 3.3-V PCI, PCI-X, 3.3-V AGP, LVDS, LVPECL, GTL+, CTT, HSTL Class I, SSTL-3 Class I and II, and SSTL-2 Class I and II.

For more information on I/O standards supported by APEX 20KE devices, see *Application Note 117 (Using Selectable I/O Standards in Altera Devices)*.

The APEX 20KE device contains eight I/O banks. In QFP packages, the banks are linked to form four I/O banks. The I/O banks directly support all standards except LVDS and LVPECL. All I/O banks can support LVDS and LVPECL with the addition of external resistors. In addition, one block within a bank contains circuitry to support high-speed True-LVDS and LVPECL inputs, and another block within a particular bank supports high-speed True-LVDS and LVPECL outputs. The LVDS blocks support all of the I/O standards. Each I/O bank has its own VCCIO pins. A single device can support 1.8-V, 2.5-V, and 3.3-V interfaces; each bank can support a different standard independently. Each bank can also use a separate V<sub>REF</sub> level so that each bank can support any of the terminated standards (such as SSTL-3) independently. Within a bank, any one of the terminated standards can be supported. EP20K300E and larger APEX 20KE devices support the LVDS interface for data pins (smaller devices support LVDS clock pins, but not data pins). All EP20K300E and larger devices support the LVDS interface for data pins up to 155 Mbit per channel; EP20K400E devices and larger with an X-suffix on the ordering code add a serializer/deserializer circuit and PLL for higher-speed support.

Each bank can support multiple standards with the same VCCIO for output pins. Each bank can support one voltage-referenced I/O standard, but it can support multiple I/O standards with the same VCCIO voltage level. For example, when VCCIO is 3.3 V, a bank can support LVTTL, LVCMOS, 3.3-V PCI, and SSTL-3 for inputs and outputs.

When the LVDS banks are not used as LVDS I/O banks, they support all of the other I/O standards. Figure 29 shows the arrangement of the APEX 20KE I/O banks.

## Clock Phase & Delay Adjustment

The APEX 20KE ClockShift feature allows the clock phase and delay to be adjusted. The clock phase can be adjusted by 90° steps. The clock delay can be adjusted to increase or decrease the clock delay by an arbitrary amount, up to one clock period.

## LVDS Support

Two PLLs are designed to support the LVDS interface. When using LVDS, the I/O clock runs at a slower rate than the data transfer rate. Thus, PLLs are used to multiply the I/O clock internally to capture the LVDS data. For example, an I/O clock may run at 105 MHz to support 840 megabits per second (Mbps) LVDS data transfer. In this example, the PLL multiplies the incoming clock by eight to support the high-speed data transfer. You can use PLLs in EP20K400E and larger devices for high-speed LVDS interfacing.

## Lock Signals

The APEX 20KE ClockLock circuitry supports individual LOCK signals. The LOCK signal drives high when the ClockLock circuit has locked onto the input clock. The LOCK signals are optional for each ClockLock circuit; when not used, they are I/O pins.

# ClockLock & ClockBoost Timing Parameters

For the ClockLock and ClockBoost circuitry to function properly, the incoming clock must meet certain requirements. If these specifications are not met, the circuitry may not lock onto the incoming clock, which generates an erroneous clock within the device. The clock generated by the ClockLock and ClockBoost circuitry must also meet certain specifications. If the incoming clock meets these requirements during configuration, the APEX 20K ClockLock and ClockBoost circuitry will lock onto the clock during configuration. The circuit will be ready for use immediately after configuration. In APEX 20KE devices, the clock input standard is programmable, so the PLL cannot respond to the clock until the device is configured. The PLL locks onto the input clock as soon as configuration is complete. Figure 30 shows the incoming and generated clock specifications.

For more information on ClockLock and ClockBoost circuitry, see *Application Note 115: Using the ClockLock and ClockBoost PLL Features in APEX Devices*.

#### Notes to Table 16:

- (1) To implement the ClockLock and ClockBoost circuitry with the Quartus II software, designers must specify the input frequency. The Quartus II software tunes the PLL in the ClockLock and ClockBoost circuitry to this frequency. The f<sub>CLKDEV</sub> parameter specifies how much the incoming clock can differ from the specified frequency during device operation. Simulation does not reflect this parameter.

- (2) Twenty-five thousand parts per million (PPM) equates to 2.5% of input clock period.

- (3) During device configuration, the ClockLock and ClockBoost circuitry is configured before the rest of the device. If the incoming clock is supplied during configuration, the ClockLock and ClockBoost circuitry locks during configuration because the  $t_{LOCK}$  value is less than the time required for configuration.

- (4) The  $t_{IITTER}$  specification is measured under long-term observation.

Tables 17 and 18 summarize the ClockLock and ClockBoost parameters for APEX 20KE devices.

| Table 17. APEX 20KE ClockLock & ClockBoost Parameters   Note (1) |                                                           |            |     |     |                        |                  |

|------------------------------------------------------------------|-----------------------------------------------------------|------------|-----|-----|------------------------|------------------|

| Symbol                                                           | Parameter                                                 | Conditions | Min | Тур | Max                    | Unit             |

| t <sub>R</sub>                                                   | Input rise time                                           |            |     |     | 5                      | ns               |

| t <sub>F</sub>                                                   | Input fall time                                           |            |     |     | 5                      | ns               |

| t <sub>INDUTY</sub>                                              | Input duty cycle                                          |            | 40  |     | 60                     | %                |

| t <sub>INJITTER</sub>                                            | Input jitter peak-to-peak                                 |            |     |     | 2% of input period     | peak-to-<br>peak |

| t <sub>OUTJITTER</sub>                                           | Jitter on ClockLock or ClockBoost-<br>generated clock     |            |     |     | 0.35% of output period | RMS              |

| t <sub>OUTDUTY</sub>                                             | Duty cycle for ClockLock or ClockBoost-generated clock    |            | 45  |     | 55                     | %                |

| t <sub>LOCK</sub> (2), (3)                                       | Time required for ClockLock or ClockBoost to acquire lock |            |     |     | 40                     | μs               |

| Symbol                  | Parameter                                     | I/O Standard | -1X Speed Grade |     | -2X Speed Grade |     | Units |

|-------------------------|-----------------------------------------------|--------------|-----------------|-----|-----------------|-----|-------|

|                         |                                               | -            | Min             | Max | Min             | Max |       |

| f <sub>VCO</sub> (4)    | Voltage controlled oscillator operating range |              | 200             | 500 | 200             | 500 | MHz   |

| f <sub>CLOCK0</sub>     | Clock0 PLL output frequency for internal use  |              | 1.5             | 335 | 1.5             | 200 | MHz   |

| f <sub>CLOCK1</sub>     | Clock1 PLL output frequency for internal use  |              | 20              | 335 | 20              | 200 | MHz   |

| f <sub>CLOCK0_EXT</sub> | Output clock frequency for                    | 3.3-V LVTTL  | 1.5             | 245 | 1.5             | 226 | MHz   |

|                         | external clock0 output                        | 2.5-V LVTTL  | 1.5             | 234 | 1.5             | 221 | MHz   |

|                         |                                               | 1.8-V LVTTL  | 1.5             | 223 | 1.5             | 216 | MHz   |

|                         |                                               | GTL+         | 1.5             | 205 | 1.5             | 193 | MHz   |

|                         |                                               | SSTL-2 Class | 1.5             | 158 | 1.5             | 157 | MHz   |

|                         |                                               | SSTL-2 Class | 1.5             | 142 | 1.5             | 142 | MHz   |

|                         |                                               | SSTL-3 Class | 1.5             | 166 | 1.5             | 162 | MHz   |

|                         |                                               | SSTL-3 Class | 1.5             | 149 | 1.5             | 146 | MHz   |

|                         |                                               | LVDS         | 1.5             | 420 | 1.5             | 350 | MHz   |

| f <sub>CLOCK1_EXT</sub> | Output clock frequency for                    | 3.3-V LVTTL  | 20              | 245 | 20              | 226 | MHz   |

|                         | external clock1 output                        | 2.5-V LVTTL  | 20              | 234 | 20              | 221 | MHz   |

|                         |                                               | 1.8-V LVTTL  | 20              | 223 | 20              | 216 | MHz   |

|                         |                                               | GTL+         | 20              | 205 | 20              | 193 | MHz   |

|                         |                                               | SSTL-2 Class | 20              | 158 | 20              | 157 | MHz   |

|                         |                                               | SSTL-2 Class | 20              | 142 | 20              | 142 | MHz   |

|                         |                                               | SSTL-3 Class | 20              | 166 | 20              | 162 | MHz   |

|                         |                                               | SSTL-3 Class | 20              | 149 | 20              | 146 | MHz   |

|                         |                                               | LVDS         | 20              | 420 | 20              | 350 | MHz   |

The APEX 20K device instruction register length is 10 bits. The APEX 20K device USERCODE register length is 32 bits. Tables 20 and 21 show the boundary-scan register length and device IDCODE information for APEX 20K devices.

| Table 20. APEX 20K Boundary-Scan Register Length |                               |  |  |  |

|--------------------------------------------------|-------------------------------|--|--|--|

| Device                                           | Boundary-Scan Register Length |  |  |  |

| EP20K30E                                         | 420                           |  |  |  |

| EP20K60E                                         | 624                           |  |  |  |

| EP20K100                                         | 786                           |  |  |  |

| EP20K100E                                        | 774                           |  |  |  |

| EP20K160E                                        | 984                           |  |  |  |

| EP20K200                                         | 1,176                         |  |  |  |

| EP20K200E                                        | 1,164                         |  |  |  |

| EP20K300E                                        | 1,266                         |  |  |  |

| EP20K400                                         | 1,536                         |  |  |  |

| EP20K400E                                        | 1,506                         |  |  |  |

| EP20K600E                                        | 1,806                         |  |  |  |

| EP20K1000E                                       | 2,190                         |  |  |  |

| EP20K1500E                                       | 1 (1)                         |  |  |  |

### Note to Table 20:

(1) This device does not support JTAG boundary scan testing.

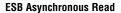

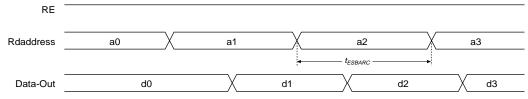

Figures 38 and 39 show the asynchronous and synchronous timing waveforms, respectively, for the ESB macroparameters in Table 31.

Figure 38. ESB Asynchronous Timing Waveforms

## **ESB Asynchronous Write**

| Table 31. APEX 2        | Table 31. APEX 20K f <sub>MAX</sub> Timing Parameters (Part 2 of 2) |                                                |  |  |  |

|-------------------------|---------------------------------------------------------------------|------------------------------------------------|--|--|--|

| Symbol                  | Parameter                                                           |                                                |  |  |  |

| t <sub>ESBDATACO2</sub> | ESB clock-to-output delay without output registers                  |                                                |  |  |  |

| t <sub>ESBDD</sub>      | ESB data-in to data-out delay for RAM mode                          |                                                |  |  |  |

| t <sub>PD</sub>         | ESB macrocell input to non-registered output                        |                                                |  |  |  |

| t <sub>PTERMSU</sub>    | ESB macrocell register setup time before clock                      | ESB macrocell register setup time before clock |  |  |  |

| t <sub>PTERMCO</sub>    | ESB macrocell register clock-to-output delay                        |                                                |  |  |  |

| t <sub>F1-4</sub>       | Fanout delay using local interconnect                               |                                                |  |  |  |

| t <sub>F5-20</sub>      | Fanout delay using MegaLab Interconnect                             |                                                |  |  |  |

| t <sub>F20+</sub>       | Fanout delay using FastTrack Interconnect                           |                                                |  |  |  |

| t <sub>CH</sub>         | Minimum clock high time from clock pin                              |                                                |  |  |  |

| t <sub>CL</sub>         | Minimum clock low time from clock pin                               |                                                |  |  |  |

| t <sub>CLRP</sub>       | LE clear pulse width                                                |                                                |  |  |  |

| t <sub>PREP</sub>       | LE preset pulse width                                               |                                                |  |  |  |

| t <sub>ESBCH</sub>      | Clock high time                                                     |                                                |  |  |  |

| t <sub>ESBCL</sub>      | Clock low time                                                      |                                                |  |  |  |

| t <sub>ESBWP</sub>      | Write pulse width                                                   |                                                |  |  |  |

| t <sub>ESBRP</sub>      | Read pulse width                                                    |                                                |  |  |  |

Tables 32 and 33 describe APEX 20K external timing parameters.

| Table 32. APEX 20K External Timing Parameters   Note (1) |                                                         |  |  |

|----------------------------------------------------------|---------------------------------------------------------|--|--|

| Symbol                                                   | ol Clock Parameter                                      |  |  |

| t <sub>INSU</sub>                                        | Setup time with global clock at IOE register            |  |  |

| t <sub>INH</sub>                                         | Hold time with global clock at IOE register             |  |  |

| t <sub>OUTCO</sub>                                       | Clock-to-output delay with global clock at IOE register |  |  |

| Table 33. APEX 20K External Bidirectional Timing Parameters         Note (1) |                                                                                            |            |  |  |  |

|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------|--|--|--|

| Symbol                                                                       | Symbol Parameter                                                                           |            |  |  |  |

| t <sub>INSUBIDIR</sub>                                                       | Setup time for bidirectional pins with global clock at same-row or same-column LE register |            |  |  |  |

| t <sub>INHBIDIR</sub>                                                        | Hold time for bidirectional pins with global clock at same-row or same-column LE register  |            |  |  |  |

| <sup>t</sup> OUTCOBIDIR                                                      | Clock-to-output delay for bidirectional pins with global clock at IOE register             | C1 = 10 pF |  |  |  |

| t <sub>XZBIDIR</sub>                                                         | Synchronous IOE output buffer disable delay                                                | C1 = 10 pF |  |  |  |

| t <sub>ZXBIDIR</sub>                                                         | Synchronous IOE output buffer enable delay, slow slew rate = off                           | C1 = 10 pF |  |  |  |

Note to Tables 32 and 33:

(1) These timing parameters are sample-tested only.

Tables 34 through 37 show APEX 20KE LE, ESB, routing, and functional timing microparameters for the  $f_{MAX}$  timing model.

| Table 34. APEX 20KE LE Timing Microparameters |                                     |  |  |  |  |  |

|-----------------------------------------------|-------------------------------------|--|--|--|--|--|

| Symbol                                        | Symbol Parameter                    |  |  |  |  |  |

| t <sub>SU</sub>                               | LE register setup time before clock |  |  |  |  |  |

| t <sub>H</sub>                                | LE register hold time after clock   |  |  |  |  |  |

| t <sub>CO</sub>                               | LE register clock-to-output delay   |  |  |  |  |  |

| t <sub>LUT</sub>                              | LUT delay for data-in to data-out   |  |  |  |  |  |

| Symbol                  | Parameter                                                            |  |  |  |  |

|-------------------------|----------------------------------------------------------------------|--|--|--|--|

| t <sub>ESBARC</sub>     | ESB Asynchronous read cycle time                                     |  |  |  |  |

| t <sub>ESBSRC</sub>     | ESB Synchronous read cycle time                                      |  |  |  |  |

| t <sub>ESBAWC</sub>     | ESB Asynchronous write cycle time                                    |  |  |  |  |

| t <sub>ESBSWC</sub>     | ESB Synchronous write cycle time                                     |  |  |  |  |

| t <sub>ESBWASU</sub>    | ESB write address setup time with respect to WE                      |  |  |  |  |

| t <sub>ESBWAH</sub>     | ESB write address hold time with respect to WE                       |  |  |  |  |

| t <sub>ESBWDSU</sub>    | ESB data setup time with respect to WE                               |  |  |  |  |

| t <sub>ESBWDH</sub>     | ESB data hold time with respect to WE                                |  |  |  |  |

| t <sub>ESBRASU</sub>    | ESB read address setup time with respect to RE                       |  |  |  |  |

| t <sub>ESBRAH</sub>     | ESB read address hold time with respect to RE                        |  |  |  |  |

| t <sub>ESBWESU</sub>    | ESB WE setup time before clock when using input register             |  |  |  |  |

| t <sub>ESBWEH</sub>     | ESB WE hold time after clock when using input register               |  |  |  |  |

| t <sub>ESBDATASU</sub>  | ESB data setup time before clock when using input register           |  |  |  |  |

| t <sub>ESBDATAH</sub>   | ESB data hold time after clock when using input register             |  |  |  |  |

| t <sub>ESBWADDRSU</sub> | ESB write address setup time before clock when using input registers |  |  |  |  |

| t <sub>ESBRADDRSU</sub> | ESB read address setup time before clock when using input registers  |  |  |  |  |

| t <sub>ESBDATACO1</sub> | ESB clock-to-output delay when using output registers                |  |  |  |  |

| t <sub>ESBDATACO2</sub> | ESB clock-to-output delay without output registers                   |  |  |  |  |

| t <sub>ESBDD</sub>      | ESB data-in to data-out delay for RAM mode                           |  |  |  |  |

| t <sub>PD</sub>         | ESB Macrocell input to non-registered output                         |  |  |  |  |

| t <sub>PTERMSU</sub>    | ESB Macrocell register setup time before clock                       |  |  |  |  |

| t <sub>PTERMCO</sub>    | ESB Macrocell register clock-to-output delay                         |  |  |  |  |

Tables 55 through 60 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K60E APEX 20KE devices.

| Symbol           | -1   |      | -2   |      | -3   |      | Unit |

|------------------|------|------|------|------|------|------|------|

|                  | Min  | Max  | Min  | Max  | Min  | Max  | 1    |

| t <sub>SU</sub>  | 0.17 |      | 0.15 |      | 0.16 |      | ns   |

| t <sub>H</sub>   | 0.32 |      | 0.33 |      | 0.39 |      | ns   |

| t <sub>CO</sub>  |      | 0.29 |      | 0.40 |      | 0.60 | ns   |

| t <sub>LUT</sub> |      | 0.77 |      | 1.07 |      | 1.59 | ns   |

Tables 67 through 72 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K160E APEX 20KE devices.

| Table 67. EP20K160E f <sub>MAX</sub> LE Timing Microparameters |      |      |      |      |      |      |      |  |

|----------------------------------------------------------------|------|------|------|------|------|------|------|--|

| Symbol                                                         | -1   |      | -2   |      | -3   |      | Unit |  |

|                                                                | Min  | Max  | Min  | Max  | Min  | Max  | 1    |  |

| t <sub>SU</sub>                                                | 0.22 |      | 0.24 |      | 0.26 |      | ns   |  |

| t <sub>H</sub>                                                 | 0.22 |      | 0.24 |      | 0.26 |      | ns   |  |

| t <sub>CO</sub>                                                |      | 0.25 |      | 0.31 |      | 0.35 | ns   |  |

| t <sub>LUT</sub>                                               |      | 0.69 |      | 0.88 |      | 1.12 | ns   |  |