Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Obsolete                                                      |

| Number of LABs/CLBs            | 416                                                           |

| Number of Logic Elements/Cells | 4160                                                          |

| Total RAM Bits                 | 53248                                                         |

| Number of I/O                  | 151                                                           |

| Number of Gates                | 263000                                                        |

| Voltage - Supply               | 1.71V ~ 1.89V                                                 |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                               |

| Package / Case                 | 208-BFQFP                                                     |

| Supplier Device Package        | 208-PQFP (28x28)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep20k100eqc208-2xn |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Windows-based PCs, Sun SPARCstations, and HP 9000 Series 700/800 workstations

- Altera MegaCore® functions and Altera Megafunction Partners Program (AMPP<sup>SM</sup>) megafunctions

- NativeLink<sup>TM</sup> integration with popular synthesis, simulation, and timing analysis tools

- Quartus II SignalTap<sup>®</sup> embedded logic analyzer simplifies in-system design evaluation by giving access to internal nodes during device operation

- Supports popular revision-control software packages including PVCS, Revision Control System (RCS), and Source Code Control System (SCCS)

| Device     | 144-Pin<br>TQFP | 208-Pin<br>PQFP<br>RQFP | 240-Pin<br>PQFP<br>RQFP | 356-Pin BGA | 652-Pin BGA | 655-Pin PGA |

|------------|-----------------|-------------------------|-------------------------|-------------|-------------|-------------|

| EP20K30E   | 92              | 125                     |                         |             |             |             |

| EP20K60E   | 92              | 148                     | 151                     | 196         |             |             |

| EP20K100   | 101             | 159                     | 189                     | 252         |             |             |

| EP20K100E  | 92              | 151                     | 183                     | 246         |             |             |

| EP20K160E  | 88              | 143                     | 175                     | 271         |             |             |

| EP20K200   |                 | 144                     | 174                     | 277         |             |             |

| EP20K200E  |                 | 136                     | 168                     | 271         | 376         |             |

| EP20K300E  |                 |                         | 152                     |             | 408         |             |

| EP20K400   |                 |                         |                         |             | 502         | 502         |

| EP20K400E  |                 |                         |                         |             | 488         |             |

| EP20K600E  |                 |                         |                         |             | 488         |             |

| EP20K1000E |                 |                         |                         |             | 488         |             |

| EP20K1500E |                 |                         |                         |             | 488         |             |

Each LE has two outputs that drive the local, MegaLAB, or FastTrack Interconnect routing structure. Each output can be driven independently by the LUT's or register's output. For example, the LUT can drive one output while the register drives the other output. This feature, called register packing, improves device utilization because the register and the LUT can be used for unrelated functions. The LE can also drive out registered and unregistered versions of the LUT output.

The APEX 20K architecture provides two types of dedicated high-speed data paths that connect adjacent LEs without using local interconnect paths: carry chains and cascade chains. A carry chain supports high-speed arithmetic functions such as counters and adders, while a cascade chain implements wide-input functions such as equality comparators with minimum delay. Carry and cascade chains connect LEs 1 through 10 in an LAB and all LABs in the same MegaLAB structure.

### Carry Chain

The carry chain provides a very fast carry-forward function between LEs. The carry-in signal from a lower-order bit drives forward into the higher-order bit via the carry chain, and feeds into both the LUT and the next portion of the carry chain. This feature allows the APEX 20K architecture to implement high-speed counters, adders, and comparators of arbitrary width. Carry chain logic can be created automatically by the Quartus II software Compiler during design processing, or manually by the designer during design entry. Parameterized functions such as library of parameterized modules (LPM) and DesignWare functions automatically take advantage of carry chains for the appropriate functions.

The Quartus II software Compiler creates carry chains longer than ten LEs by linking LABs together automatically. For enhanced fitting, a long carry chain skips alternate LABs in a MegaLAB<sup>TM</sup> structure. A carry chain longer than one LAB skips either from an even-numbered LAB to the next even-numbered LAB, or from an odd-numbered LAB to the next odd-numbered LAB. For example, the last LE of the first LAB in the upper-left MegaLAB structure carries to the first LE of the third LAB in the MegaLAB structure.

Figure 6 shows how an n-bit full adder can be implemented in n+1 LEs with the carry chain. One portion of the LUT generates the sum of two bits using the input signals and the carry-in signal; the sum is routed to the output of the LE. The register can be bypassed for simple adders or used for accumulator functions. Another portion of the LUT and the carry chain logic generates the carry-out signal, which is routed directly to the carryin signal of the next-higher-order bit. The final carry-out signal is routed to an LE, where it is driven onto the local, MegaLAB, or FastTrack Interconnect routing structures.

| Source                           | Destination    |                   |          |          |                       |                         |                                  |                                     |                         |

|----------------------------------|----------------|-------------------|----------|----------|-----------------------|-------------------------|----------------------------------|-------------------------------------|-------------------------|

|                                  | Row<br>I/O Pin | Column<br>I/O Pin | LE       | ESB      | Local<br>Interconnect | MegaLAB<br>Interconnect | Row<br>FastTrack<br>Interconnect | Column<br>FastTrack<br>Interconnect | FastRow<br>Interconnect |

| Row I/O Pin                      |                |                   |          |          | ✓                     | <b>✓</b>                | <b>✓</b>                         | ✓                                   |                         |

| Column I/O<br>Pin                |                |                   |          |          |                       |                         |                                  | <b>✓</b>                            | <b>√</b> (1)            |

| LE                               |                |                   |          |          | ✓                     | ✓                       | ✓                                | ✓                                   |                         |

| ESB                              |                |                   |          |          | ✓                     | ✓                       | ✓                                | ✓                                   |                         |

| Local<br>Interconnect            | <b>✓</b>       | ✓                 | <b>✓</b> | <b>✓</b> |                       |                         |                                  |                                     |                         |

| MegaLAB<br>Interconnect          |                |                   |          |          | ~                     |                         |                                  |                                     |                         |

| Row<br>FastTrack<br>Interconnect |                |                   |          |          |                       | <b>✓</b>                |                                  | <b>✓</b>                            |                         |

| Column                           |                |                   |          |          |                       | <b>✓</b>                | <b>✓</b>                         |                                     |                         |

| FastTrack<br>Interconnect        |                |                   |          |          |                       |                         |                                  |                                     |                         |

| FastRow<br>Interconnect          |                |                   |          |          | <b>✓</b> (1)          |                         |                                  |                                     |                         |

Note to Table 9:

(1) This connection is supported in APEX 20KE devices only.

## **Product-Term Logic**

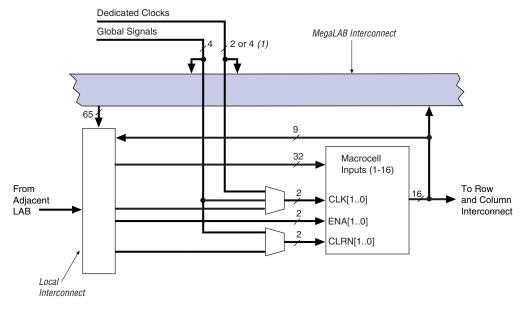

The product-term portion of the MultiCore architecture is implemented with the ESB. The ESB can be configured to act as a block of macrocells on an ESB-by-ESB basis. Each ESB is fed by 32 inputs from the adjacent local interconnect; therefore, it can be driven by the MegaLAB interconnect or the adjacent LAB. Also, nine ESB macrocells feed back into the ESB through the local interconnect for higher performance. Dedicated clock pins, global signals, and additional inputs from the local interconnect drive the ESB control signals.

In product-term mode, each ESB contains 16 macrocells. Each macrocell consists of two product terms and a programmable register. Figure 13 shows the ESB in product-term mode.

Figure 13. Product-Term Logic in ESB

Note to Figure 13:

(1) APEX 20KE devices have four dedicated clocks.

### Macrocells

APEX 20K macrocells can be configured individually for either sequential or combinatorial logic operation. The macrocell consists of three functional blocks: the logic array, the product-term select matrix, and the programmable register.

Combinatorial logic is implemented in the product terms. The product-term select matrix allocates these product terms for use as either primary logic inputs (to the OR and XOR gates) to implement combinatorial functions, or as parallel expanders to be used to increase the logic available to another macrocell. One product term can be inverted; the Quartus II software uses this feature to perform DeMorgan's inversion for more efficient implementation of wide OR functions. The Quartus II software Compiler can use a NOT-gate push-back technique to emulate an asynchronous preset. Figure 14 shows the APEX 20K macrocell.

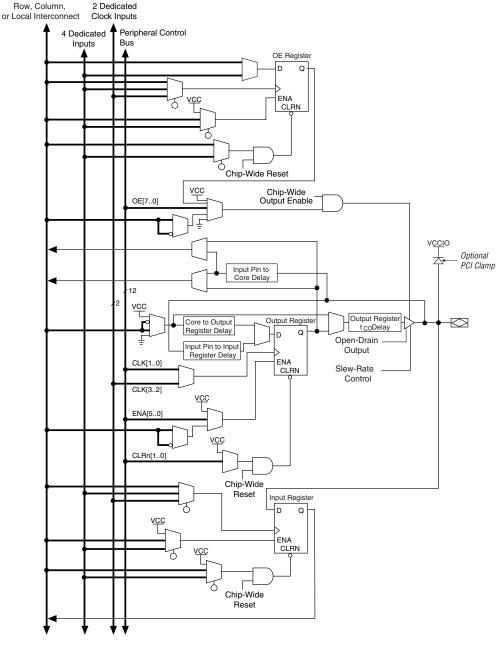

Figure 25. APEX 20K Bidirectional I/O Registers Note (1)

Note to Figure 25:

(1) The output enable and input registers are LE registers in the LAB adjacent to the bidirectional pin.

Under hot socketing conditions, APEX 20KE devices will not sustain any damage, but the I/O pins will drive out.

# MultiVolt I/O Interface

The APEX device architecture supports the MultiVolt I/O interface feature, which allows APEX devices in all packages to interface with systems of different supply voltages. The devices have one set of VCC pins for internal operation and input buffers (VCCINT), and another set for I/O output drivers (VCCIO).

The APEX 20K VCCINT pins must always be connected to a 2.5 V power supply. With a 2.5-V  $V_{CCINT}$  level, input pins are 2.5-V, 3.3-V, and 5.0-V tolerant. The VCCIO pins can be connected to either a 2.5-V or 3.3-V power supply, depending on the output requirements. When VCCIO pins are connected to a 2.5-V power supply, the output levels are compatible with 2.5-V systems. When the VCCIO pins are connected to a 3.3-V power supply, the output high is 3.3 V and is compatible with 3.3-V or 5.0-V systems.

| Table 12. 5.0-V Tolerant APEX 20K MultiVolt I/O Support |          |                                      |              |              |     |          |  |  |

|---------------------------------------------------------|----------|--------------------------------------|--------------|--------------|-----|----------|--|--|

| V <sub>CCIO</sub> (V)                                   | In       | Input Signals (V) Output Signals (V) |              |              |     |          |  |  |

|                                                         | 2.5      | 3.3                                  | 5.0          | 2.5          | 3.3 | 5.0      |  |  |

| 2.5                                                     | ✓        | <b>√</b> (1)                         | <b>√</b> (1) | ✓            |     |          |  |  |

| 3.3                                                     | <b>✓</b> | ✓                                    | <b>√</b> (1) | <b>√</b> (2) | ✓   | <b>✓</b> |  |  |

#### Notes to Table 12:

- (1) The PCI clamping diode must be disabled to drive an input with voltages higher than  $V_{\text{CCIO}}$ .

- (2) When  $V_{\rm CCIO}$  = 3.3 V, an APEX 20K device can drive a 2.5-V device with 3.3-V tolerant inputs.

Open-drain output pins on 5.0-V tolerant APEX 20K devices (with a pull-up resistor to the 5.0-V supply) can drive 5.0-V CMOS input pins that require a  $V_{\rm IH}$  of 3.5 V. When the pin is inactive, the trace will be pulled up to 5.0 V by the resistor. The open-drain pin will only drive low or tri-state; it will never drive high. The rise time is dependent on the value of the pull-up resistor and load impedance. The  $I_{\rm OL}$  current specification should be considered when selecting a pull-up resistor.

For designs that require both a multiplied and non-multiplied clock, the clock trace on the board can be connected to CLK2p. Table 14 shows the combinations supported by the ClockLock and ClockBoost circuitry. The CLK2p pin can feed both the ClockLock and ClockBoost circuitry in the APEX 20K device. However, when both circuits are used, the other clock pin (CLK1p) cannot be used.

| Table 14. Multiplication Factor Combinations |    |  |  |  |

|----------------------------------------------|----|--|--|--|

| Clock 1 Clock 2                              |    |  |  |  |

| ×1                                           | ×1 |  |  |  |

| ×1,×2                                        | ×2 |  |  |  |

| ×1, ×2, ×4                                   | ×4 |  |  |  |

#### **APEX 20KE ClockLock Feature**

APEX 20KE devices include an enhanced ClockLock feature set. These devices include up to four PLLs, which can be used independently. Two PLLs are designed for either general-purpose use or LVDS use (on devices that support LVDS I/O pins). The remaining two PLLs are designed for general-purpose use. The EP20K200E and smaller devices have two PLLs; the EP20K300E and larger devices have four PLLs.

The following sections describe some of the features offered by the APEX 20KE PLLs.

#### External PLL Feedback

The ClockLock circuit's output can be driven off-chip to clock other devices in the system; further, the feedback loop of the PLL can be routed off-chip. This feature allows the designer to exercise fine control over the I/O interface between the APEX 20KE device and another high-speed device, such as SDRAM.

#### Clock Multiplication

The APEX 20KE ClockBoost circuit can multiply or divide clocks by a programmable number. The clock can be multiplied by  $m/(n \times k)$  or  $m/(n \times v)$ , where m and k range from 2 to 160, and n and v range from 1 to 16. Clock multiplication and division can be used for time-domain multiplexing and other functions, which can reduce design LE requirements.

# IEEE Std. 1149.1 (JTAG) Boundary-Scan Support

All APEX 20K devices provide JTAG BST circuitry that complies with the IEEE Std. 1149.1-1990 specification. JTAG boundary-scan testing can be performed before or after configuration, but not during configuration. APEX 20K devices can also use the JTAG port for configuration with the Quartus II software or with hardware using either Jam Files (.jam) or Jam Byte-Code Files (.jbc). Finally, APEX 20K devices use the JTAG port to monitor the logic operation of the device with the SignalTap embedded logic analyzer. APEX 20K devices support the JTAG instructions shown in Table 19. Although EP20K1500E devices support the JTAG BYPASS and SignalTap instructions, they do not support boundary-scan testing or the use of the JTAG port for configuration.

| Table 19. APEX 20K JT      | Table 19. APEX 20K JTAG Instructions                                                                                                                                                                                                 |  |  |  |  |  |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| JTAG Instruction           | Description                                                                                                                                                                                                                          |  |  |  |  |  |

| SAMPLE/PRELOAD             | Allows a snapshot of signals at the device pins to be captured and examined during normal device operation, and permits an initial data pattern to be output at the device pins. Also used by the SignalTap embedded logic analyzer. |  |  |  |  |  |

| EXTEST                     | Allows the external circuitry and board-level interconnections to be tested by forcing a test pattern at the output pins and capturing test results at the input pins.                                                               |  |  |  |  |  |

| BYPASS (1)                 | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation.                                          |  |  |  |  |  |

| USERCODE                   | Selects the 32-bit USERCODE register and places it between the TDI and TDO pins, allowing the USERCODE to be serially shifted out of TDO.                                                                                            |  |  |  |  |  |

| IDCODE                     | Selects the IDCODE register and places it between TDI and TDO, allowing the IDCODE to be serially shifted out of TDO.                                                                                                                |  |  |  |  |  |

| ICR Instructions           | Used when configuring an APEX 20K device via the JTAG port with a MasterBlaster <sup>TM</sup> or ByteBlasterMV <sup>TM</sup> download cable, or when using a Jam File or Jam Byte-Code File via an embedded processor.               |  |  |  |  |  |

| SignalTap Instructions (1) | Monitors internal device operation with the SignalTap embedded logic analyzer.                                                                                                                                                       |  |  |  |  |  |

#### Note to Table 19:

(1) The EP20K1500E device supports the JTAG BYPASS instruction and the SignalTap instructions.

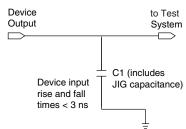

Figure 32. APEX 20K AC Test Conditions Note (1)

#### Note to Figure 32:

(1) Power supply transients can affect AC measurements. Simultaneous transitions of multiple outputs should be avoided for accurate measurement. Threshold tests must not be performed under AC conditions. Large-amplitude, fast-ground-current transients normally occur as the device outputs discharge the load capacitances. When these transients flow through the parasitic inductance between the device ground pin and the test system ground, significant reductions in observable noise immunity can result.

# Operating Conditions

Tables 23 through 26 provide information on absolute maximum ratings, recommended operating conditions, DC operating conditions, and capacitance for 2.5-V APEX 20K devices.

| Table 2            | Table 23. APEX 20K 5.0-V Tolerant Device Absolute Maximum Ratings Notes (1), (2) |                                                |      |      |      |  |  |  |  |

|--------------------|----------------------------------------------------------------------------------|------------------------------------------------|------|------|------|--|--|--|--|

| Symbol             | Parameter                                                                        | Conditions                                     | Min  | Max  | Unit |  |  |  |  |

| V <sub>CCINT</sub> | Supply voltage                                                                   | With respect to ground (3)                     | -0.5 | 3.6  | V    |  |  |  |  |

| V <sub>CCIO</sub>  |                                                                                  |                                                | -0.5 | 4.6  | V    |  |  |  |  |

| V <sub>I</sub>     | DC input voltage                                                                 |                                                | -2.0 | 5.75 | V    |  |  |  |  |

| I <sub>OUT</sub>   | DC output current, per pin                                                       |                                                | -25  | 25   | mA   |  |  |  |  |

| T <sub>STG</sub>   | Storage temperature                                                              | No bias                                        | -65  | 150  | ° C  |  |  |  |  |

| T <sub>AMB</sub>   | Ambient temperature                                                              | Under bias                                     | -65  | 135  | ° C  |  |  |  |  |

| TJ                 | Junction temperature                                                             | PQFP, RQFP, TQFP, and BGA packages, under bias |      | 135  | ° C  |  |  |  |  |

|                    |                                                                                  | Ceramic PGA packages, under bias               |      | 150  | °C   |  |  |  |  |

| Symbol            | Parameter                                                                 | Conditions                                                                        | Min | Тур | Max                     | Unit |

|-------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----|-----|-------------------------|------|

| V <sub>OL</sub>   | 3.3-V low-level TTL output voltage                                        | I <sub>OL</sub> = 12 mA DC,<br>V <sub>CCIO</sub> = 3.00 V (11)                    |     |     | 0.45                    | V    |

|                   | 3.3-V low-level CMOS output voltage                                       | I <sub>OL</sub> = 0.1 mA DC,<br>V <sub>CCIO</sub> = 3.00 V (11)                   |     |     | 0.2                     | V    |

|                   | 3.3-V low-level PCI output voltage                                        | I <sub>OL</sub> = 1.5 mA DC,<br>V <sub>CCIO</sub> = 3.00 to 3.60 V<br>(11)        |     |     | 0.1 × V <sub>CCIO</sub> | V    |

|                   | 2.5-V low-level output voltage                                            | I <sub>OL</sub> = 0.1 mA DC,<br>V <sub>CCIO</sub> = 2.30 V (11)                   |     |     | 0.2                     | ٧    |

|                   |                                                                           | I <sub>OL</sub> = 1 mA DC,<br>V <sub>CCIO</sub> = 2.30 V (11)                     |     |     | 0.4                     | ٧    |

|                   |                                                                           | I <sub>OL</sub> = 2 mA DC,<br>V <sub>CCIO</sub> = 2.30 V (11)                     |     |     | 0.7                     | ٧    |

| I <sub>I</sub>    | Input pin leakage current                                                 | $V_1 = 5.75 \text{ to } -0.5 \text{ V}$                                           | -10 |     | 10                      | μΑ   |

| I <sub>OZ</sub>   | Tri-stated I/O pin leakage current                                        | $V_O = 5.75 \text{ to } -0.5 \text{ V}$                                           | -10 |     | 10                      | μΑ   |

| I <sub>CC0</sub>  | V <sub>CC</sub> supply current (standby)<br>(All ESBs in power-down mode) | V <sub>I</sub> = ground, no load, no toggling inputs, -1 speed grade (12)         |     | 10  |                         | mA   |

|                   |                                                                           | V <sub>I</sub> = ground, no load, no toggling inputs,<br>-2, -3 speed grades (12) |     | 5   |                         | mA   |

| R <sub>CONF</sub> | Value of I/O pin pull-up resistor                                         | V <sub>CCIO</sub> = 3.0 V (13)                                                    | 20  |     | 50                      | W    |

|                   | before and during configuration                                           | V <sub>CCIO</sub> = 2.375 V (13)                                                  | 30  |     | 80                      | W    |

| Table 26. APEX 20K 5.0-V Tolerant Device CapacitanceNotes (2), (14) |                                          |                                     |     |     |      |  |  |

|---------------------------------------------------------------------|------------------------------------------|-------------------------------------|-----|-----|------|--|--|

| Symbol                                                              | Parameter                                | Conditions                          | Min | Max | Unit |  |  |

| C <sub>IN</sub>                                                     | Input capacitance                        | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 8   | pF   |  |  |

| C <sub>INCLK</sub>                                                  | Input capacitance on dedicated clock pin | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 12  | pF   |  |  |

| C <sub>OUT</sub>                                                    | Output capacitance                       | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 8   | pF   |  |  |

#### Notes to Tables 23 through 26:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) All APEX 20K devices are 5.0-V tolerant.

- (3) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to 5.75 V for input currents less than 100 mA and periods shorter than 20 ns.

- (4) Numbers in parentheses are for industrial-temperature-range devices.

- (5) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically.

- (6) All pins, including dedicated inputs, clock I/O, and JTAG pins, may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are powered.

- (7) Typical values are for  $T_A = 25^{\circ}$  C,  $V_{CCINT} = 2.5$  V, and  $V_{CCIO} = 2.5$  or 3.3 V.

- (8) These values are specified in the APEX 20K device recommended operating conditions, shown in Table 26 on page 62.

- (9) The APEX 20K input buffers are compatible with 2.5-V and 3.3-V (LVTTL and LVCMOS) signals. Additionally, the input buffers are 3.3-V PCI compliant when V<sub>CCIO</sub> and V<sub>CCINT</sub> meet the relationship shown in Figure 33 on page 68.

- (10) The I<sub>OH</sub> parameter refers to high-level TTL, PCI or CMOS output current.

- (11) The I<sub>OL</sub> parameter refers to low-level TTL, PCI, or CMOS output current. This parameter applies to open-drain pins as well as output pins.

- (12) This value is specified for normal device operation. The value may vary during power-up.

- (13) Pin pull-up resistance values will be lower if an external source drives the pin higher than  $V_{\text{CCIO}}$ .

- (14) Capacitance is sample-tested only.

Tables 27 through 30 provide information on absolute maximum ratings, recommended operating conditions, DC operating conditions, and capacitance for 1.8-V APEX 20KE devices.

| Table 27. APEX 20KE Device Absolute Maximum Ratings Note (1) |                            |                                                |      |     |      |  |  |

|--------------------------------------------------------------|----------------------------|------------------------------------------------|------|-----|------|--|--|

| Symbol                                                       | Parameter                  | Conditions                                     | Min  | Max | Unit |  |  |

| V <sub>CCINT</sub>                                           | Supply voltage             | With respect to ground (2)                     | -0.5 | 2.5 | V    |  |  |

| $V_{CCIO}$                                                   |                            |                                                | -0.5 | 4.6 | ٧    |  |  |

| V <sub>I</sub>                                               | DC input voltage           |                                                | -0.5 | 4.6 | V    |  |  |

| I <sub>OUT</sub>                                             | DC output current, per pin |                                                | -25  | 25  | mA   |  |  |

| T <sub>STG</sub>                                             | Storage temperature        | No bias                                        | -65  | 150 | ° C  |  |  |

| T <sub>AMB</sub>                                             | Ambient temperature        | Under bias                                     | -65  | 135 | ° C  |  |  |

| TJ                                                           | Junction temperature       | PQFP, RQFP, TQFP, and BGA packages, under bias |      | 135 | ° C  |  |  |

|                                                              |                            | Ceramic PGA packages, under bias               |      | 150 | ° C  |  |  |

For DC Operating Specifications on APEX 20KE I/O standards, please refer to *Application Note 117 (Using Selectable I/O Standards in Altera Devices).*

| Table 30. APEX 20KE Device Capacitance Note (15) |                                          |                                     |     |     |      |  |  |

|--------------------------------------------------|------------------------------------------|-------------------------------------|-----|-----|------|--|--|

| Symbol                                           | Parameter                                | Conditions                          | Min | Max | Unit |  |  |

| C <sub>IN</sub>                                  | Input capacitance                        | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 8   | pF   |  |  |

| C <sub>INCLK</sub>                               | Input capacitance on dedicated clock pin | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 12  | pF   |  |  |

| C <sub>OUT</sub>                                 | Output capacitance                       | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 8   | pF   |  |  |

#### Notes to Tables 27 through 30:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to 5.75 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Numbers in parentheses are for industrial-temperature-range devices.

- (4) Maximum V<sub>CC</sub> rise time is 100 ms, and V<sub>CC</sub> must rise monotonically.

- (5) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to the voltage shown in the following table based on input duty cycle for input currents less than 100 mA. The overshoot is dependent upon duty cycle of the signal. The DC case is equivalent to 100% duty cycle.

Vin Max. Duty Cycle 4.0V 100% (DC) 4.1 90% 4.2 50% 4.3 30% 4.4 17% 4.5 10%

- (6) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are powered.

- Typical values are for  $T_A = 25^{\circ}$  C,  $V_{CCINT} = 1.8$  V, and  $V_{CCIO} = 1.8$  V, 2.5 V or 3.3 V.

- (8) These values are specified under the APEX 20KE device recommended operating conditions, shown in Table 24 on page 60.

- (9) Refer to Application Note 117 (Using Selectable I/O Standards in Altera Devices) for the V<sub>IH</sub>, V<sub>IL</sub>, V<sub>OH</sub>, V<sub>OL</sub>, and I<sub>I</sub> parameters when VCCIO = 1.8 V.

- (10) The APEX 20KE input buffers are compatible with 1.8-V, 2.5-V and 3.3-V (LVTTL and LVCMOS) signals. Additionally, the input buffers are 3.3-V PCI compliant. Input buffers also meet specifications for GTL+, CTT, AGP, SSTL-2, SSTL-3, and HSTL.

- (11) The I<sub>OH</sub> parameter refers to high-level TTL, PCI, or CMOS output current.

- (12) The I<sub>OL</sub> parameter refers to low-level TTL, PCI, or CMOS output current. This parameter applies to open-drain pins as well as output pins.

- (13) This value is specified for normal device operation. The value may vary during power-up.

- (14) Pin pull-up resistance values will be lower if an external source drives the pin higher than V<sub>CCIO</sub>.

- (15) Capacitance is sample-tested only.

Figure 33 shows the relationship between  $V_{CCIO}$  and  $V_{CCINT}$  for 3.3-V PCI compliance on APEX 20K devices.

| Symbol                  | -1 Spee | d Grade | -2 Spee | d Grade | -3 Spee | d Grade | Units |

|-------------------------|---------|---------|---------|---------|---------|---------|-------|

|                         | Min     | Max     | Min     | Max     | Min     | Max     |       |

| t <sub>SU</sub>         | 0.5     |         | 0.6     |         | 0.8     |         | ns    |

| t <sub>H</sub>          | 0.7     |         | 0.8     |         | 1.0     |         | ns    |

| t <sub>CO</sub>         |         | 0.3     |         | 0.4     |         | 0.5     | ns    |

| t <sub>LUT</sub>        |         | 0.8     |         | 1.0     |         | 1.3     | ns    |

| t <sub>ESBRC</sub>      |         | 1.7     |         | 2.1     |         | 2.4     | ns    |

| t <sub>ESBWC</sub>      |         | 5.7     |         | 6.9     |         | 8.1     | ns    |

| t <sub>ESBWESU</sub>    | 3.3     |         | 3.9     |         | 4.6     |         | ns    |

| t <sub>ESBDATASU</sub>  | 2.2     |         | 2.7     |         | 3.1     |         | ns    |

| t <sub>ESBDATAH</sub>   | 0.6     |         | 0.8     |         | 0.9     |         | ns    |

| t <sub>ESBADDRSU</sub>  | 2.4     |         | 2.9     |         | 3.3     |         | ns    |

| t <sub>ESBDATACO1</sub> |         | 1.3     |         | 1.6     |         | 1.8     | ns    |

| t <sub>ESBDATACO2</sub> |         | 2.6     |         | 3.1     |         | 3.6     | ns    |

| t <sub>ESBDD</sub>      |         | 2.5     |         | 3.3     |         | 3.6     | ns    |

| t <sub>PD</sub>         |         | 2.5     |         | 3.0     |         | 3.6     | ns    |

| t <sub>PTERMSU</sub>    | 2.3     |         | 2.7     |         | 3.2     |         | ns    |

| t <sub>PTERMCO</sub>    |         | 1.5     |         | 1.8     |         | 2.1     | ns    |

| t <sub>F1-4</sub>       |         | 0.5     |         | 0.6     |         | 0.7     | ns    |

| t <sub>F5-20</sub>      |         | 1.6     |         | 1.7     |         | 1.8     | ns    |

| t <sub>F20+</sub>       |         | 2.2     |         | 2.2     |         | 2.3     | ns    |

| t <sub>CH</sub>         | 2.0     |         | 2.5     |         | 3.0     |         | ns    |

| $t_{CL}$                | 2.0     |         | 2.5     |         | 3.0     |         | ns    |

| t <sub>CLRP</sub>       | 0.3     |         | 0.4     |         | 0.4     |         | ns    |

| t <sub>PREP</sub>       | 0.4     |         | 0.5     |         | 0.5     |         | ns    |

| t <sub>ESBCH</sub>      | 2.0     |         | 2.5     |         | 3.0     |         | ns    |

| t <sub>ESBCL</sub>      | 2.0     |         | 2.5     |         | 3.0     |         | ns    |

| t <sub>ESBWP</sub>      | 1.6     |         | 1.9     |         | 2.2     |         | ns    |

| t <sub>ESBRP</sub>      | 1.0     |         | 1.3     | _       | 1.4     |         | ns    |

| Table 43. EP20         | K100 Externa | l Timing Para | meters |          |         |                |    |

|------------------------|--------------|---------------|--------|----------|---------|----------------|----|

| Symbol                 | -1 Spe       | ed Grade      | -2 Spe | ed Grade | -3 Spee | -3 Speed Grade |    |

|                        | Min          | Max           | Min    | Max      | Min     | Max            |    |

| t <sub>INSU</sub> (1)  | 2.3          |               | 2.8    |          | 3.2     |                | ns |

| t <sub>INH</sub> (1)   | 0.0          |               | 0.0    |          | 0.0     |                | ns |

| t <sub>OUTCO</sub> (1) | 2.0          | 4.5           | 2.0    | 4.9      | 2.0     | 6.6            | ns |

| t <sub>INSU</sub> (2)  | 1.1          |               | 1.2    |          | -       |                | ns |

| t <sub>INH</sub> (2)   | 0.0          |               | 0.0    |          | -       |                | ns |

| t <sub>OUTCO</sub> (2) | 0.5          | 2.7           | 0.5    | 3.1      | _       | 4.8            | ns |

| Symbol                     | -1 Spee | ed Grade | -2 Spee | d Grade | -3 Spee | d Grade | Unit |

|----------------------------|---------|----------|---------|---------|---------|---------|------|

|                            | Min     | Max      | Min     | Max     | Min     | Max     |      |

| t <sub>INSUBIDIR</sub> (1) | 2.3     |          | 2.8     |         | 3.2     |         | ns   |

| t <sub>INHBIDIR</sub> (1)  | 0.0     |          | 0.0     |         | 0.0     |         | ns   |

| toutcobidir<br>(1)         | 2.0     | 4.5      | 2.0     | 4.9     | 2.0     | 6.6     | ns   |

| t <sub>XZBIDIR</sub> (1)   |         | 5.0      |         | 5.9     |         | 6.9     | ns   |

| t <sub>ZXBIDIR</sub> (1)   |         | 5.0      |         | 5.9     |         | 6.9     | ns   |

| t <sub>INSUBIDIR</sub> (2) | 1.0     |          | 1.2     |         | -       |         | ns   |

| t <sub>INHBIDIR</sub> (2)  | 0.0     |          | 0.0     |         | -       |         | ns   |

| toutcobidir<br>(2)         | 0.5     | 2.7      | 0.5     | 3.1     | -       | -       | ns   |

| t <sub>XZBIDIR</sub> (2)   |         | 4.3      |         | 5.0     |         | _       | ns   |

| t <sub>ZXBIDIR</sub> (2)   |         | 4.3      |         | 5.0     |         | _       | ns   |

| Table 45. EP20                | K200 Externa | l Timing Para | meters |          |         |                |    |

|-------------------------------|--------------|---------------|--------|----------|---------|----------------|----|

| Symbol                        | -1 Spec      | ed Grade      | -2 Spe | ed Grade | -3 Spee | -3 Speed Grade |    |

|                               | Min          | Max           | Min    | Max      | Min     | Max            |    |

| t <sub>INSU</sub> (1)         | 1.9          |               | 2.3    |          | 2.6     |                | ns |

| t <sub>INH</sub> (1)          | 0.0          |               | 0.0    |          | 0.0     |                | ns |

| t <sub>OUTCO</sub> (1)        | 2.0          | 4.6           | 2.0    | 5.6      | 2.0     | 6.8            | ns |

| t <sub>INSU</sub> (2)         | 1.1          |               | 1.2    |          | -       |                | ns |

| t <sub>INH</sub> (2)          | 0.0          |               | 0.0    |          | -       |                | ns |

| t <sub>оитсо</sub> <i>(2)</i> | 0.5          | 2.7           | 0.5    | 3.1      | -       | _              | ns |

#### Notes to Tables 43 through 48:

- (1) This parameter is measured without using ClockLock or ClockBoost circuits.

- (2) This parameter is measured using ClockLock or ClockBoost circuits.

Tables 49 through 54 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K30E APEX 20KE devices.

| Table 49. EP20K30E f <sub>MAX</sub> LE Timing Microparameters |       |      |      |      |      |      |      |  |  |

|---------------------------------------------------------------|-------|------|------|------|------|------|------|--|--|

| Symbol                                                        | ıl -1 |      | -2   |      | -3   |      | Unit |  |  |

|                                                               | Min   | Max  | Min  | Max  | Min  | Max  |      |  |  |

| t <sub>SU</sub>                                               | 0.01  |      | 0.02 |      | 0.02 |      | ns   |  |  |

| t <sub>H</sub>                                                | 0.11  |      | 0.16 |      | 0.23 |      | ns   |  |  |

| t <sub>CO</sub>                                               |       | 0.32 |      | 0.45 |      | 0.67 | ns   |  |  |

| t <sub>LUT</sub>                                              |       | 0.85 |      | 1.20 |      | 1.77 | ns   |  |  |

| Table 57. EP2      | OK60E f <sub>MAX</sub> R | outing Delays |     |      |     |      |      |

|--------------------|--------------------------|---------------|-----|------|-----|------|------|

| Symbol             | -                        | 1             |     | -2   |     | 3    | Unit |

|                    | Min                      | Max           | Min | Max  | Min | Max  |      |

| t <sub>F1-4</sub>  |                          | 0.24          |     | 0.26 |     | 0.30 | ns   |

| t <sub>F5-20</sub> |                          | 1.45          |     | 1.58 |     | 1.79 | ns   |

| t <sub>F20+</sub>  |                          | 1.96          |     | 2.14 |     | 2.45 | ns   |

| Symbol             | -    | 1   | -    | -2  |      | 3   | Unit |

|--------------------|------|-----|------|-----|------|-----|------|

|                    | Min  | Max | Min  | Max | Min  | Max |      |

| t <sub>CH</sub>    | 2.00 |     | 2.50 |     | 2.75 |     | ns   |

| t <sub>CL</sub>    | 2.00 |     | 2.50 |     | 2.75 |     | ns   |

| t <sub>CLRP</sub>  | 0.20 |     | 0.28 |     | 0.41 |     | ns   |

| t <sub>PREP</sub>  | 0.20 |     | 0.28 |     | 0.41 |     | ns   |

| t <sub>ESBCH</sub> | 2.00 |     | 2.50 |     | 2.75 |     | ns   |

| t <sub>ESBCL</sub> | 2.00 |     | 2.50 |     | 2.75 |     | ns   |

| t <sub>ESBWP</sub> | 1.29 |     | 1.80 |     | 2.66 |     | ns   |

| t <sub>ESBRP</sub> | 1.04 |     | 1.45 |     | 2.14 |     | ns   |

| Symbol               | -    | 1    | -2   |      | -3   |      | Unit |

|----------------------|------|------|------|------|------|------|------|

|                      | Min  | Max  | Min  | Max  | Min  | Max  |      |

| t <sub>INSU</sub>    | 2.03 |      | 2.12 |      | 2.23 |      | ns   |

| t <sub>INH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>OUTCO</sub>   | 2.00 | 4.84 | 2.00 | 5.31 | 2.00 | 5.81 | ns   |

| t <sub>INSUPLL</sub> | 1.12 |      | 1.15 |      | -    |      | ns   |

| t <sub>INHPLL</sub>  | 0.00 |      | 0.00 |      | -    |      | ns   |

| toutcople            | 0.50 | 3.37 | 0.50 | 3.69 | -    | -    | ns   |

Tables 67 through 72 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K160E APEX 20KE devices.

| Table 67. EP2    | OK160E f <sub>MAX</sub> | LE Timing Mic | roparameter | s    |      |      |      |

|------------------|-------------------------|---------------|-------------|------|------|------|------|

| Symbol           | mbol -1                 |               |             | -2   | -3   |      | Unit |

|                  | Min                     | Max           | Min         | Max  | Min  | Max  |      |

| t <sub>SU</sub>  | 0.22                    |               | 0.24        |      | 0.26 |      | ns   |

| t <sub>H</sub>   | 0.22                    |               | 0.24        |      | 0.26 |      | ns   |

| t <sub>CO</sub>  |                         | 0.25          |             | 0.31 |      | 0.35 | ns   |

| t <sub>LUT</sub> |                         | 0.69          |             | 0.88 |      | 1.12 | ns   |

| Symbol             | -1   | İ   | -    | -2  | -3   | 3   | Unit |

|--------------------|------|-----|------|-----|------|-----|------|

|                    | Min  | Max | Min  | Max | Min  | Max |      |

| t <sub>CH</sub>    | 1.25 |     | 1.43 |     | 1.67 |     | ns   |

| t <sub>CL</sub>    | 1.25 |     | 1.43 |     | 1.67 |     | ns   |

| t <sub>CLRP</sub>  | 0.19 |     | 0.26 |     | 0.35 |     | ns   |

| t <sub>PREP</sub>  | 0.19 |     | 0.26 |     | 0.35 |     | ns   |

| t <sub>ESBCH</sub> | 1.25 |     | 1.43 |     | 1.67 |     | ns   |

| t <sub>ESBCL</sub> | 1.25 |     | 1.43 |     | 1.67 |     | ns   |

| t <sub>ESBWP</sub> | 1.25 |     | 1.71 |     | 2.28 |     | ns   |

| t <sub>ESBRP</sub> | 1.01 |     | 1.38 |     | 1.84 |     | ns   |

| Symbol               | -    | 1    | -    | 2    | -3   | }    | Unit |

|----------------------|------|------|------|------|------|------|------|

|                      | Min  | Max  | Min  | Max  | Min  | Max  |      |

| t <sub>INSU</sub>    | 2.31 |      | 2.44 |      | 2.57 |      | ns   |

| t <sub>INH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>OUTCO</sub>   | 2.00 | 5.29 | 2.00 | 5.82 | 2.00 | 6.24 | ns   |

| t <sub>INSUPLL</sub> | 1.76 |      | 1.85 |      | -    |      | ns   |

| t <sub>INHPLL</sub>  | 0.00 |      | 0.00 |      | -    |      | ns   |

| toutcople            | 0.50 | 2.65 | 0.50 | 2.95 | _    | -    | ns   |

| Symbol                    | -    | 1    | -    | 2    | -    | 3    | Unit |

|---------------------------|------|------|------|------|------|------|------|

|                           | Min  | Max  | Min  | Max  | Min  | Max  |      |

| t <sub>INSUBIDIR</sub>    | 2.77 |      | 2.85 |      | 3.11 |      | ns   |

| t <sub>INHBIDIR</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>OUTCOBIDIR</sub>   | 2.00 | 5.29 | 2.00 | 5.82 | 2.00 | 6.24 | ns   |

| t <sub>XZBIDIR</sub>      |      | 7.59 |      | 8.30 |      | 9.09 | ns   |

| t <sub>ZXBIDIR</sub>      |      | 7.59 |      | 8.30 |      | 9.09 | ns   |

| t <sub>INSUBIDIRPLL</sub> | 2.50 |      | 2.76 |      | -    |      | ns   |

| t <sub>INHBIDIRPLL</sub>  | 0.00 |      | 0.00 |      | -    |      | ns   |

| toutcobidirpll            | 0.50 | 2.65 | 0.50 | 2.95 | -    | -    | ns   |

| <sup>t</sup> xzbidirpll   |      | 5.00 |      | 5.43 |      | -    | ns   |

| tzxbidirpll               |      | 5.00 |      | 5.43 |      | -    | ns   |

| Symbol                  | -1 Speed Grade |      | -2 Speed Grade |      | -3 Speed Grade |      | Unit |

|-------------------------|----------------|------|----------------|------|----------------|------|------|

|                         | Min            | Max  | Min            | Max  | Min            | Max  |      |

| t <sub>ESBARC</sub>     |                | 1.78 |                | 2.02 |                | 1.95 | ns   |

| t <sub>ESBSRC</sub>     |                | 2.52 |                | 2.91 |                | 3.14 | ns   |

| t <sub>ESBAWC</sub>     |                | 3.52 |                | 4.11 |                | 4.40 | ns   |

| t <sub>ESBSWC</sub>     |                | 3.23 |                | 3.84 |                | 4.16 | ns   |

| t <sub>ESBWASU</sub>    | 0.62           |      | 0.67           |      | 0.61           |      | ns   |

| t <sub>ESBWAH</sub>     | 0.41           |      | 0.55           |      | 0.55           |      | ns   |

| t <sub>ESBWDSU</sub>    | 0.77           |      | 0.79           |      | 0.81           |      | ns   |

| t <sub>ESBWDH</sub>     | 0.41           |      | 0.55           |      | 0.55           |      | ns   |

| t <sub>ESBRASU</sub>    | 1.74           |      | 1.92           |      | 1.85           |      | ns   |

| t <sub>ESBRAH</sub>     | 0.00           |      | 0.01           |      | 0.23           |      | ns   |

| t <sub>ESBWESU</sub>    | 2.07           |      | 2.28           |      | 2.41           |      | ns   |

| t <sub>ESBWEH</sub>     | 0.00           |      | 0.00           |      | 0.00           |      | ns   |

| t <sub>ESBDATASU</sub>  | 0.25           |      | 0.27           |      | 0.29           |      | ns   |

| t <sub>ESBDATAH</sub>   | 0.13           |      | 0.13           |      | 0.13           |      | ns   |

| t <sub>ESBWADDRSU</sub> | 0.11           |      | 0.04           |      | 0.11           |      | ns   |

| t <sub>ESBRADDRSU</sub> | 0.14           |      | 0.11           |      | 0.16           |      | ns   |

| t <sub>ESBDATACO1</sub> |                | 1.29 |                | 1.50 |                | 1.63 | ns   |

| t <sub>ESBDATACO2</sub> |                | 2.55 |                | 2.99 |                | 3.22 | ns   |

| t <sub>ESBDD</sub>      |                | 3.12 |                | 3.57 |                | 3.85 | ns   |

| t <sub>PD</sub>         |                | 1.84 |                | 2.13 |                | 2.32 | ns   |

| t <sub>PTERMSU</sub>    | 1.08           |      | 1.19           |      | 1.32           | _    | ns   |

| t <sub>PTERMCO</sub>    |                | 1.31 |                | 1.53 |                | 1.66 | ns   |

| Table 105. EP20K1500E f <sub>MAX</sub> Routing Delays |                |      |                |      |                |      |      |  |  |  |  |  |

|-------------------------------------------------------|----------------|------|----------------|------|----------------|------|------|--|--|--|--|--|

| Symbol                                                | -1 Speed Grade |      | -2 Speed Grade |      | -3 Speed Grade |      | Unit |  |  |  |  |  |

|                                                       | Min            | Max  | Min            | Max  | Min            | Max  |      |  |  |  |  |  |

| t <sub>F1-4</sub>                                     |                | 0.28 |                | 0.28 |                | 0.28 | ns   |  |  |  |  |  |

| t <sub>F5-20</sub>                                    |                | 1.36 |                | 1.50 |                | 1.62 | ns   |  |  |  |  |  |

| t <sub>F20+</sub>                                     |                | 4.43 |                | 4.48 |                | 5.07 | ns   |  |  |  |  |  |

## Revision History

The information contained in the *APEX 20K Programmable Logic Device Family Data Sheet* version 5.1 supersedes information published in previous versions.

#### Version 5.1

APEX 20K Programmable Logic Device Family Data Sheet version 5.1 contains the following changes:

- In version 5.0, the VI input voltage spec was updated in Table 28 on page 63.

- In version 5.0, *Note* (5) to Tables 27 through 30 was revised.

- Added Note (2) to Figure 21 on page 33.

#### Version 5.0

APEX 20K Programmable Logic Device Family Data Sheet version 5.0 contains the following changes:

- Updated Tables 23 through 26. Removed 2.5-V operating condition tables because all APEX 20K devices are now 5.0-V tolerant.

- Updated conditions in Tables 33, 38 and 39.

- Updated data for t<sub>ESBDATAH</sub> parameter.

#### Version 4.3

APEX 20K Programmable Logic Device Family Data Sheet version 4.3 contains the following changes:

- Updated Figure 20.

- Updated *Note* (2) to Table 13.

- Updated notes to Tables 27 through 30.

#### Version 4.2

APEX 20K Programmable Logic Device Family Data Sheet version 4.2 contains the following changes:

- Updated Figure 29.

- Updated *Note* (1) to Figure 29.