## E·XFL

### Intel - EP20K1500EBC652-1X Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Obsolete                                                      |

| Number of LABs/CLBs            | 5184                                                          |

| Number of Logic Elements/Cells | 51840                                                         |

| Total RAM Bits                 | 442368                                                        |

| Number of I/O                  | 488                                                           |

| Number of Gates                | 2392000                                                       |

| Voltage - Supply               | 1.71V ~ 1.89V                                                 |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                               |

| Package / Case                 | 652-BGA                                                       |

| Supplier Device Package        | 652-BGA (45x45)                                               |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep20k1500ebc652-1x |

|                                |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Flexible clock management circuitry with up to four phase-locked loops (PLLs)

- Built-in low-skew clock tree

- Up to eight global clock signals

- ClockLock<sup>®</sup> feature reducing clock delay and skew

- ClockBoost<sup>®</sup> feature providing clock multiplication and division

- ClockShift<sup>TM</sup> programmable clock phase and delay shifting

- Powerful I/O features

- Compliant with peripheral component interconnect Special Interest Group (PCI SIG) *PCI Local Bus Specification, Revision 2.2* for 3.3-V operation at 33 or 66 MHz and 32 or 64 bits

- Support for high-speed external memories, including DDR SDRAM and ZBT SRAM (ZBT is a trademark of Integrated Device Technology, Inc.)

- Bidirectional I/O performance  $(t_{CO} + t_{SU})$  up to 250 MHz

- LVDS performance up to 840 Mbits per channel

- Direct connection from I/O pins to local interconnect providing fast t<sub>CO</sub> and t<sub>SU</sub> times for complex logic

- MultiVolt I/O interface support to interface with 1.8-V, 2.5-V, 3.3-V, and 5.0-V devices (see Table 3)

- Programmable clamp to V<sub>CCIO</sub>

- Individual tri-state output enable control for each pin

- Programmable output slew-rate control to reduce switching noise

- Support for advanced I/O standards, including low-voltage differential signaling (LVDS), LVPECL, PCI-X, AGP, CTT, stubseries terminated logic (SSTL-3 and SSTL-2), Gunning transceiver logic plus (GTL+), and high-speed terminated logic (HSTL Class I)

- Pull-up on I/O pins before and during configuration

- Advanced interconnect structure

- Four-level hierarchical FastTrack<sup>®</sup> Interconnect structure providing fast, predictable interconnect delays

- Dedicated carry chain that implements arithmetic functions such as fast adders, counters, and comparators (automatically used by software tools and megafunctions)

- Dedicated cascade chain that implements high-speed, high-fan-in logic functions (automatically used by software tools and megafunctions)

- Interleaved local interconnect allows one LE to drive 29 other LEs through the fast local interconnect

- Advanced packaging options

- Available in a variety of packages with 144 to 1,020 pins (see Tables 4 through 7)

- FineLine BGA<sup>®</sup> packages maximize board space efficiency

- Advanced software support

- Software design support and automatic place-and-route provided by the Altera<sup>®</sup> Quartus<sup>®</sup> II development system for

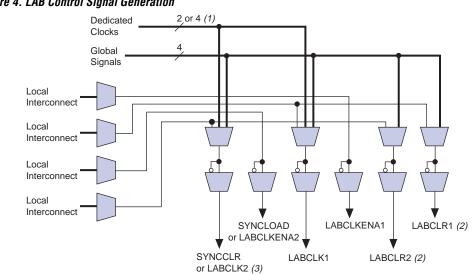

Each LAB contains dedicated logic for driving control signals to its LEs and ESBs. The control signals include clock, clock enable, asynchronous clear, asynchronous preset, asynchronous load, synchronous clear, and synchronous load signals. A maximum of six control signals can be used at a time. Although synchronous load and clear signals are generally used when implementing counters, they can also be used with other functions.

Each LAB can use two clocks and two clock enable signals. Each LAB's clock and clock enable signals are linked (e.g., any LE in a particular LAB using CLK1 will also use CLKENA1). LEs with the same clock but different clock enable signals either use both clock signals in one LAB or are placed into separate LABs.

If both the rising and falling edges of a clock are used in a LAB, both LABwide clock signals are used.

The LAB-wide control signals can be generated from the LAB local interconnect, global signals, and dedicated clock pins. The inherent low skew of the FastTrack Interconnect enables it to be used for clock distribution. Figure 4 shows the LAB control signal generation circuit.

#### Figure 4. LAB Control Signal Generation

#### Notes to Figure 4:

- APEX 20KE devices have four dedicated clocks. (1)

- The LABCLR1 and LABCLR2 signals also control asynchronous load and asynchronous preset for LEs within the (2) LAB.

- (3)The SYNCCLR signal can be generated by the local interconnect or global signals.

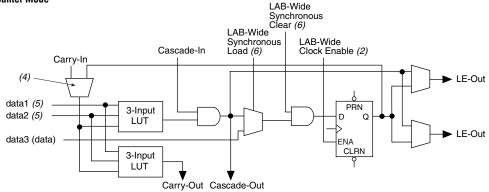

#### LAB-Wide Normal Mode (1) Clock Enable (2) Carry-In (3) Cascade-In LE-Out data1 data2 PRN 4-Input D Q LUT data3 LE-Out ENA data4 CLRN Cascade-Out LAB-Wide Arithmetic Mode Clock Enable (2) Carry-In Cascade-In LE-Out PRN data1 Q D 3-Input data2 LUT LE-Out ENA CLRN 3-Input LUT Cascade-Out Carry-Out

#### Figure 8. APEX 20K LE Operating Modes

#### Notes to Figure 8:

- (1) LEs in normal mode support register packing.

- (2) There are two LAB-wide clock enables per LAB.

- (3) When using the carry-in in normal mode, the packed register feature is unavailable.

- (4) A register feedback multiplexer is available on LE1 of each LAB.

- (5) The DATA1 and DATA2 input signals can supply counter enable, up or down control, or register feedback signals for LEs other than the second LE in an LAB.

- (6) The LAB-wide synchronous clear and LAB wide synchronous load affect all registers in an LAB.

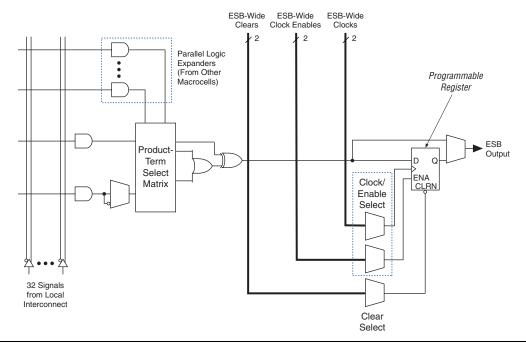

#### Figure 14. APEX 20K Macrocell

For registered functions, each macrocell register can be programmed individually to implement D, T, JK, or SR operation with programmable clock control. The register can be bypassed for combinatorial operation. During design entry, the designer specifies the desired register type; the Quartus II software then selects the most efficient register operation for each registered function to optimize resource utilization. The Quartus II software or other synthesis tools can also select the most efficient register operation automatically when synthesizing HDL designs.

Each programmable register can be clocked by one of two ESB-wide clocks. The ESB-wide clocks can be generated from device dedicated clock pins, global signals, or local interconnect. Each clock also has an associated clock enable, generated from the local interconnect. The clock and clock enable signals are related for a particular ESB; any macrocell using a clock also uses the associated clock enable.

If both the rising and falling edges of a clock are used in an ESB, both ESB-wide clock signals are used.

APEX 20KE devices include an enhanced IOE, which drives the FastRow interconnect. The FastRow interconnect connects a column I/O pin directly to the LAB local interconnect within two MegaLAB structures. This feature provides fast setup times for pins that drive high fan-outs with complex logic, such as PCI designs. For fast bidirectional I/O timing, LE registers using local routing can improve setup times and OE timing. The APEX 20KE IOE also includes direct support for open-drain operation, giving faster clock-to-output for open-drain signals. Some programmable delays in the APEX 20KE IOE offer multiple levels of delay to fine-tune setup and hold time requirements. The Quartus II software compiler can set these delays automatically to minimize setup time while providing a zero hold time.

Table 11 describes the APEX 20KE programmable delays and their logic options in the Quartus II software.

| Table 11. APEX 20KE Programmable Delay Chains |                                         |  |  |  |  |  |

|-----------------------------------------------|-----------------------------------------|--|--|--|--|--|

| Programmable Delays                           | Quartus II Logic Option                 |  |  |  |  |  |

| Input Pin to Core Delay                       | Decrease input delay to internal cells  |  |  |  |  |  |

| Input Pin to Input Register Delay             | Decrease input delay to input registers |  |  |  |  |  |

| Core to Output Register Delay                 | Decrease input delay to output register |  |  |  |  |  |

| Output Register t <sub>CO</sub> Delay         | Increase delay to output pin            |  |  |  |  |  |

| Clock Enable Delay                            | Increase clock enable delay             |  |  |  |  |  |

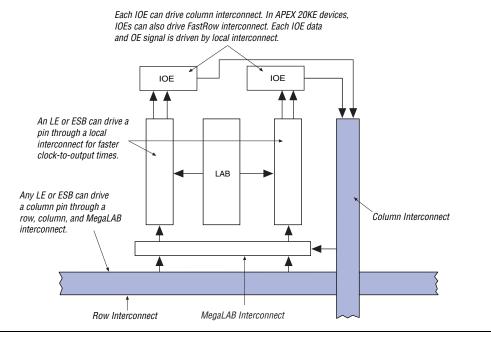

The register in the APEX 20KE IOE can be programmed to power-up high or low after configuration is complete. If it is programmed to power-up low, an asynchronous clear can control the register. If it is programmed to power-up high, an asynchronous preset can control the register. Figure 26 shows how fast bidirectional I/O pins are implemented in APEX 20KE devices. This feature is useful for cases where the APEX 20KE device controls an active-low input or another device; it prevents inadvertent activation of the input upon power-up. Figure 28 shows how a column IOE connects to the interconnect.

#### Figure 28. Column IOE Connection to the Interconnect

### **Dedicated Fast I/O Pins**

APEX 20KE devices incorporate an enhancement to support bidirectional pins with high internal fanout such as PCI control signals. These pins are called Dedicated Fast I/O pins (FAST1, FAST2, FAST3, and FAST4) and replace dedicated inputs. These pins can be used for fast clock, clear, or high fanout logic signal distribution. They also can drive out. The Dedicated Fast I/O pin data output and tri-state control are driven by local interconnect from the adjacent MegaLAB for high speed. The APEX 20K device instruction register length is 10 bits. The APEX 20K device USERCODE register length is 32 bits. Tables 20 and 21 show the boundary-scan register length and device IDCODE information for APEX 20K devices.

| Table 20. APEX 20K Boundary-Sca | n Register Length             |

|---------------------------------|-------------------------------|

| Device                          | Boundary-Scan Register Length |

| EP20K30E                        | 420                           |

| EP20K60E                        | 624                           |

| EP20K100                        | 786                           |

| EP20K100E                       | 774                           |

| EP20K160E                       | 984                           |

| EP20K200                        | 1,176                         |

| EP20K200E                       | 1,164                         |

| EP20K300E                       | 1,266                         |

| EP20K400                        | 1,536                         |

| EP20K400E                       | 1,506                         |

| EP20K600E                       | 1,806                         |

| EP20K1000E                      | 2,190                         |

| EP20K1500E                      | 1 (1)                         |

#### Note to Table 20:

(1) This device does not support JTAG boundary scan testing.

| Symbol            | Parameter                                                                 | Conditions                                                                           | Min | Тур | Мах                  | Unit |

|-------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----|-----|----------------------|------|

| V <sub>OL</sub>   | 3.3-V low-level TTL output voltage                                        | I <sub>OL</sub> = 12 mA DC,<br>V <sub>CCIO</sub> = 3.00 V (11)                       |     |     | 0.45                 | V    |

|                   | 3.3-V low-level CMOS output voltage                                       | I <sub>OL</sub> = 0.1 mA DC,<br>V <sub>CCIO</sub> = 3.00 V (11)                      |     |     | 0.2                  | V    |

|                   | 3.3-V low-level PCI output voltage                                        | I <sub>OL</sub> = 1.5 mA DC,<br>V <sub>CCIO</sub> = 3.00 to 3.60 V<br>(11)           |     |     | $0.1 	imes V_{CCIO}$ | V    |

|                   | 2.5-V low-level output voltage                                            | I <sub>OL</sub> = 0.1 mA DC,<br>V <sub>CCIO</sub> = 2.30 V (11)                      |     |     | 0.2                  | V    |

|                   |                                                                           | I <sub>OL</sub> = 1 mA DC,<br>V <sub>CCIO</sub> = 2.30 V (11)                        |     |     | 0.4                  | V    |

|                   |                                                                           | I <sub>OL</sub> = 2 mA DC,<br>V <sub>CCIO</sub> = 2.30 V (11)                        |     |     | 0.7                  | V    |

| I <sub>I</sub>    | Input pin leakage current                                                 | $V_1 = 5.75$ to $-0.5$ V                                                             | -10 |     | 10                   | μA   |

| I <sub>OZ</sub>   | Tri-stated I/O pin leakage current                                        | V <sub>O</sub> = 5.75 to -0.5 V                                                      | -10 |     | 10                   | μΑ   |

| I <sub>CC0</sub>  | V <sub>CC</sub> supply current (standby)<br>(All ESBs in power-down mode) | $V_1$ = ground, no load, no<br>toggling inputs, -1 speed<br>grade (12)               |     | 10  |                      | mA   |

|                   |                                                                           | V <sub>I</sub> = ground, no load, no<br>toggling inputs,<br>-2, -3 speed grades (12) |     | 5   |                      | mA   |

| R <sub>CONF</sub> | Value of I/O pin pull-up resistor                                         | V <sub>CCIO</sub> = 3.0 V (13)                                                       | 20  |     | 50                   | W    |

|                   | before and during configuration                                           | V <sub>CCIO</sub> = 2.375 V (13)                                                     | 30  |     | 80                   | W    |

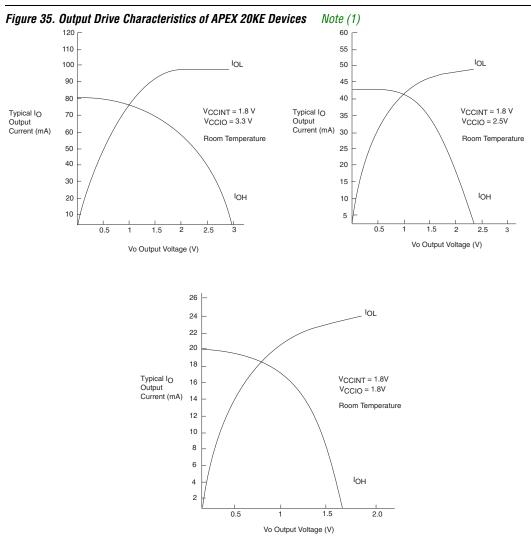

Figure 35 shows the output drive characteristics of APEX 20KE devices.

*Note to Figure 35:*(1) These are transient (AC) currents.

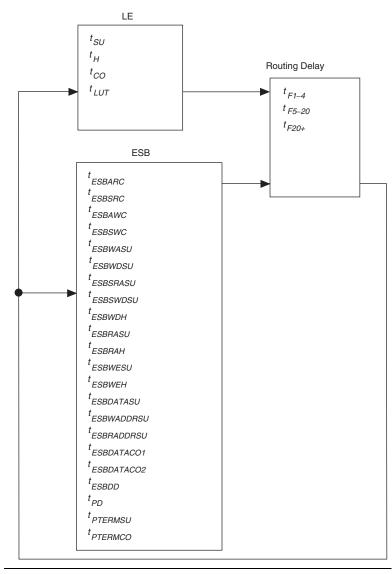

## **Timing Model**

The high-performance FastTrack and MegaLAB interconnect routing resources ensure predictable performance, accurate simulation, and accurate timing analysis. This predictable performance contrasts with that of FPGAs, which use a segmented connection scheme and therefore have unpredictable performance.

Figure 37. APEX 20KE f<sub>MAX</sub> Timing Model

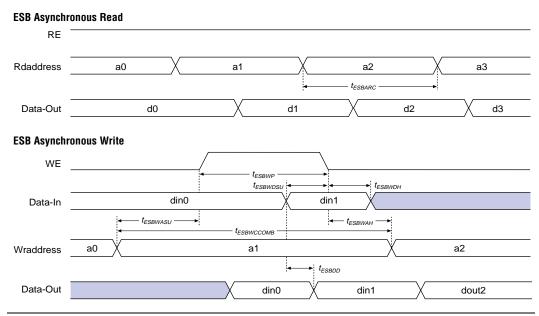

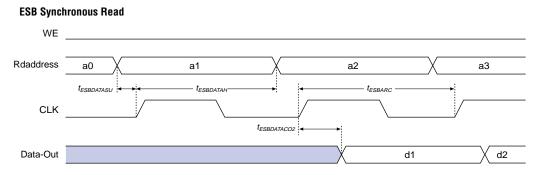

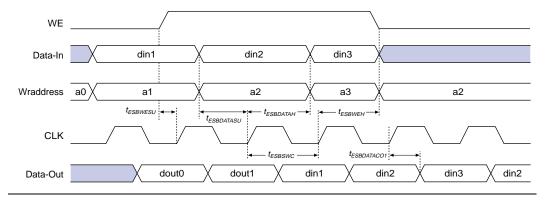

Figures 38 and 39 show the asynchronous and synchronous timing waveforms, respectively, for the ESB macroparameters in Table 31.

Figure 38. ESB Asynchronous Timing Waveforms

Figure 39. ESB Synchronous Timing Waveforms

#### ESB Synchronous Write (ESB Output Registers Used)

Figure 40 shows the timing model for bidirectional I/O pin timing.

| Symbol                  | -    | 1    |      | -2   | 4    | 3    | Unit |

|-------------------------|------|------|------|------|------|------|------|

|                         | Min  | Max  | Min  | Max  | Min  | Max  |      |

| t <sub>ESBARC</sub>     |      | 2.03 |      | 2.86 |      | 4.24 | ns   |

| t <sub>ESBSRC</sub>     |      | 2.58 |      | 3.49 |      | 5.02 | ns   |

| t <sub>ESBAWC</sub>     |      | 3.88 |      | 5.45 |      | 8.08 | ns   |

| t <sub>ESBSWC</sub>     |      | 4.08 |      | 5.35 |      | 7.48 | ns   |

| t <sub>ESBWASU</sub>    | 1.77 |      | 2.49 |      | 3.68 |      | ns   |

| t <sub>ESBWAH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>ESBWDSU</sub>    | 1.95 |      | 2.74 |      | 4.05 |      | ns   |

| t <sub>ESBWDH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>ESBRASU</sub>    | 1.96 |      | 2.75 |      | 4.07 |      | ns   |

| t <sub>ESBRAH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>ESBWESU</sub>    | 1.80 |      | 2.73 |      | 4.28 |      | ns   |

| t <sub>ESBWEH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>ESBDATASU</sub>  | 0.07 |      | 0.48 |      | 1.17 |      | ns   |

| t <sub>ESBDATAH</sub>   | 0.13 |      | 0.13 |      | 0.13 |      | ns   |

| t <sub>ESBWADDRSU</sub> | 0.30 |      | 0.80 |      | 1.64 |      | ns   |

| t <sub>ESBRADDRSU</sub> | 0.37 |      | 0.90 |      | 1.78 |      | ns   |

| t <sub>ESBDATACO1</sub> |      | 1.11 |      | 1.32 |      | 1.67 | ns   |

| t <sub>ESBDATACO2</sub> |      | 2.65 |      | 3.73 |      | 5.53 | ns   |

| t <sub>ESBDD</sub>      |      | 3.88 |      | 5.45 |      | 8.08 | ns   |

| t <sub>PD</sub>         |      | 1.91 |      | 2.69 |      | 3.98 | ns   |

| t <sub>PTERMSU</sub>    | 1.04 |      | 1.71 |      | 2.82 |      | ns   |

| t <sub>PTERMCO</sub>    |      | 1.13 |      | 1.34 |      | 1.69 | ns   |

## Table 51. EP20K30E f<sub>MAX</sub> Routing Delays

| Symbol             | -1  |      |     | -2   |     | -3   |    |

|--------------------|-----|------|-----|------|-----|------|----|

|                    | Min | Max  | Min | Max  | Min | Max  |    |

| t <sub>F1-4</sub>  |     | 0.24 |     | 0.27 |     | 0.31 | ns |

| t <sub>F5-20</sub> |     | 1.03 |     | 1.14 |     | 1.30 | ns |

| t <sub>F20+</sub>  |     | 1.42 |     | 1.54 |     | 1.77 | ns |

| Symbol                    | -1   |      | -    | 2    | -    | Unit |    |

|---------------------------|------|------|------|------|------|------|----|

|                           | Min  | Max  | Min  | Max  | Min  | Max  |    |

| t <sub>insubidir</sub>    | 2.77 |      | 2.91 |      | 3.11 |      | ns |

| t <sub>inhbidir</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns |

| toutcobidir               | 2.00 | 4.84 | 2.00 | 5.31 | 2.00 | 5.81 | ns |

| t <sub>XZBIDIR</sub>      |      | 6.47 |      | 7.44 |      | 8.65 | ns |

| t <sub>ZXBIDIR</sub>      |      | 6.47 |      | 7.44 |      | 8.65 | ns |

| t <sub>insubidirpll</sub> | 3.44 |      | 3.24 |      | -    |      | ns |

| t <sub>inhbidirpll</sub>  | 0.00 |      | 0.00 |      | -    |      | ns |

| toutcobidirpll            | 0.50 | 3.37 | 0.50 | 3.69 | -    | -    | ns |

| t <sub>xzbidirpll</sub>   |      | 5.00 |      | 5.82 |      | -    | ns |

| t <sub>zxbidirpll</sub>   |      | 5.00 |      | 5.82 |      | -    | ns |

Tables 61 through 66 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K100E APEX 20KE devices.

| Table 61. EP2    | OK100E f <sub>max</sub> i | LE Timing Mic | roparameters | 8    |      |      |      |

|------------------|---------------------------|---------------|--------------|------|------|------|------|

| Symbol           | -                         | 1             | -            | 2    | -;   | 3    | Unit |

|                  | Min                       | Max           | Min          | Max  | Min  | Max  |      |

| t <sub>SU</sub>  | 0.25                      |               | 0.25         |      | 0.25 |      | ns   |

| t <sub>H</sub>   | 0.25                      |               | 0.25         |      | 0.25 |      | ns   |

| t <sub>CO</sub>  |                           | 0.28          |              | 0.28 |      | 0.34 | ns   |

| t <sub>LUT</sub> |                           | 0.80          |              | 0.95 |      | 1.13 | ns   |

| Table 69. EP2      | OK160E f <sub>max</sub> i | Routing Delay | s   |      |     |      |      |

|--------------------|---------------------------|---------------|-----|------|-----|------|------|

| Symbol             | -                         | 1             | -2  |      | -;  | 3    | Unit |

|                    | Min                       | Max           | Min | Max  | Min | Max  |      |

| t <sub>F1-4</sub>  |                           | 0.25          |     | 0.26 |     | 0.28 | ns   |

| t <sub>F5-20</sub> |                           | 1.00          |     | 1.18 |     | 1.35 | ns   |

| t <sub>F20+</sub>  |                           | 1.95          |     | 2.19 |     | 2.30 | ns   |

| Symbol             | -    | 1   | -    | 2   | -3   | 3   | Unit |

|--------------------|------|-----|------|-----|------|-----|------|

|                    | Min  | Max | Min  | Max | Min  | Max |      |

| t <sub>CH</sub>    | 1.34 |     | 1.43 |     | 1.55 |     | ns   |

| t <sub>CL</sub>    | 1.34 |     | 1.43 |     | 1.55 |     | ns   |

| t <sub>CLRP</sub>  | 0.18 |     | 0.19 |     | 0.21 |     | ns   |

| t <sub>PREP</sub>  | 0.18 |     | 0.19 |     | 0.21 |     | ns   |

| t <sub>ESBCH</sub> | 1.34 |     | 1.43 |     | 1.55 |     | ns   |

| t <sub>ESBCL</sub> | 1.34 |     | 1.43 |     | 1.55 |     | ns   |

| t <sub>ESBWP</sub> | 1.15 |     | 1.45 |     | 1.73 |     | ns   |

| t <sub>ESBRP</sub> | 0.93 |     | 1.15 |     | 1.38 |     | ns   |

| Table 71. EP20K160E External Timing Parameters |      |      |      |      |      |      |      |  |  |  |

|------------------------------------------------|------|------|------|------|------|------|------|--|--|--|

| Symbol                                         | -    | 1    | -    | -2   | -3   |      | Unit |  |  |  |

|                                                | Min  | Max  | Min  | Max  | Min  | Max  |      |  |  |  |

| t <sub>INSU</sub>                              | 2.23 |      | 2.34 |      | 2.47 |      | ns   |  |  |  |

| t <sub>INH</sub>                               | 0.00 |      | 0.00 |      | 0.00 |      | ns   |  |  |  |

| t <sub>outco</sub>                             | 2.00 | 5.07 | 2.00 | 5.59 | 2.00 | 6.13 | ns   |  |  |  |

| t <sub>INSUPLL</sub>                           | 2.12 |      | 2.07 |      | -    |      | ns   |  |  |  |

| t <sub>INHPLL</sub>                            | 0.00 |      | 0.00 |      | -    |      | ns   |  |  |  |

| toutcopll                                      | 0.50 | 3.00 | 0.50 | 3.35 | -    | -    | ns   |  |  |  |

| Symbol                  | -     | -1   |       | -2   |      | -3   |    |

|-------------------------|-------|------|-------|------|------|------|----|

|                         | Min   | Max  | Min   | Max  | Min  | Max  | 1  |

| t <sub>ESBARC</sub>     |       | 1.68 |       | 2.06 |      | 2.24 | ns |

| t <sub>ESBSRC</sub>     |       | 2.27 |       | 2.77 |      | 3.18 | ns |

| t <sub>ESBAWC</sub>     |       | 3.10 |       | 3.86 |      | 4.50 | ns |

| t <sub>ESBSWC</sub>     |       | 2.90 |       | 3.67 |      | 4.21 | ns |

| t <sub>ESBWASU</sub>    | 0.55  |      | 0.67  |      | 0.74 |      | ns |

| t <sub>ESBWAH</sub>     | 0.36  |      | 0.46  |      | 0.48 |      | ns |

| t <sub>ESBWDSU</sub>    | 0.69  |      | 0.83  |      | 0.95 |      | ns |

| t <sub>ESBWDH</sub>     | 0.36  |      | 0.46  |      | 0.48 |      | ns |

| t <sub>ESBRASU</sub>    | 1.61  |      | 1.90  |      | 2.09 |      | ns |

| t <sub>ESBRAH</sub>     | 0.00  |      | 0.00  |      | 0.01 |      | ns |

| t <sub>ESBWESU</sub>    | 1.42  |      | 1.71  |      | 2.01 |      | ns |

| t <sub>ESBWEH</sub>     | 0.00  |      | 0.00  |      | 0.00 |      | ns |

| t <sub>ESBDATASU</sub>  | -0.06 |      | -0.07 |      | 0.05 |      | ns |

| t <sub>ESBDATAH</sub>   | 0.13  |      | 0.13  |      | 0.13 |      | ns |

| t <sub>ESBWADDRSU</sub> | 0.11  |      | 0.13  |      | 0.31 |      | ns |

| t <sub>ESBRADDRSU</sub> | 0.18  |      | 0.23  |      | 0.39 |      | ns |

| t <sub>ESBDATACO1</sub> |       | 1.09 |       | 1.35 |      | 1.51 | ns |

| t <sub>ESBDATACO2</sub> |       | 2.19 |       | 2.75 |      | 3.22 | ns |

| t <sub>ESBDD</sub>      |       | 2.75 |       | 3.41 |      | 4.03 | ns |

| t <sub>PD</sub>         |       | 1.58 |       | 1.97 |      | 2.33 | ns |

| t <sub>PTERMSU</sub>    | 1.00  |      | 1.22  |      | 1.51 |      | ns |

| t <sub>PTERMCO</sub>    |       | 1.10 |       | 1.37 |      | 1.09 | ns |

| Table 75. EP2      | Table 75. EP20K200E f <sub>MAX</sub> Routing Delays |      |     |      |     |      |    |  |  |  |  |  |  |

|--------------------|-----------------------------------------------------|------|-----|------|-----|------|----|--|--|--|--|--|--|

| Symbol             | -                                                   | ·1   |     | -2   | -:  | Unit |    |  |  |  |  |  |  |

|                    | Min                                                 | Max  | Min | Max  | Min | Max  |    |  |  |  |  |  |  |

| t <sub>F1-4</sub>  |                                                     | 0.25 |     | 0.27 |     | 0.29 | ns |  |  |  |  |  |  |

| t <sub>F5-20</sub> |                                                     | 1.02 |     | 1.20 |     | 1.41 | ns |  |  |  |  |  |  |

| t <sub>F20+</sub>  |                                                     | 1.99 |     | 2.23 |     | 2.53 | ns |  |  |  |  |  |  |

| Symbol             | -1   | -1  |      | -2  |      | -3  |    |  |

|--------------------|------|-----|------|-----|------|-----|----|--|

|                    | Min  | Max | Min  | Max | Min  | Max |    |  |

| t <sub>CH</sub>    | 1.36 |     | 2.44 |     | 2.65 |     | ns |  |

| t <sub>CL</sub>    | 1.36 |     | 2.44 |     | 2.65 |     | ns |  |

| t <sub>CLRP</sub>  | 0.18 |     | 0.19 |     | 0.21 |     | ns |  |

| t <sub>PREP</sub>  | 0.18 |     | 0.19 |     | 0.21 |     | ns |  |

| t <sub>ESBCH</sub> | 1.36 |     | 2.44 |     | 2.65 |     | ns |  |

| t <sub>ESBCL</sub> | 1.36 |     | 2.44 |     | 2.65 |     | ns |  |

| t <sub>ESBWP</sub> | 1.18 |     | 1.48 |     | 1.76 |     | ns |  |

| t <sub>ESBRP</sub> | 0.95 |     | 1.17 |     | 1.41 |     | ns |  |

| Table 77. EP20K200E External Timing Parameters |      |      |      |      |      |      |    |  |  |  |

|------------------------------------------------|------|------|------|------|------|------|----|--|--|--|

| Symbol                                         | -1   |      | -2   |      | -3   | Unit |    |  |  |  |

|                                                | Min  | Max  | Min  | Max  | Min  | Мах  |    |  |  |  |

| t <sub>INSU</sub>                              | 2.24 |      | 2.35 |      | 2.47 |      | ns |  |  |  |

| t <sub>INH</sub>                               | 0.00 |      | 0.00 |      | 0.00 |      | ns |  |  |  |

| t <sub>outco</sub>                             | 2.00 | 5.12 | 2.00 | 5.62 | 2.00 | 6.11 | ns |  |  |  |

| t <sub>INSUPLL</sub>                           | 2.13 |      | 2.07 |      | -    |      | ns |  |  |  |

| t <sub>INHPLL</sub>                            | 0.00 |      | 0.00 |      | -    |      | ns |  |  |  |

| t <sub>outcopll</sub>                          | 0.50 | 3.01 | 0.50 | 3.36 | -    | -    | ns |  |  |  |

| Symbol             | -1 Speed Grade |     | -2 Speed Grade |     | -3 Spee | Unit |    |

|--------------------|----------------|-----|----------------|-----|---------|------|----|

|                    | Min            | Max | Min            | Max | Min     | Max  |    |

| t <sub>CH</sub>    | 2.00           |     | 2.50           |     | 2.75    |      | ns |

| t <sub>CL</sub>    | 2.00           |     | 2.50           |     | 2.75    |      | ns |

| t <sub>CLRP</sub>  | 0.18           |     | 0.26           |     | 0.34    |      | ns |

| t <sub>PREP</sub>  | 0.18           |     | 0.26           |     | 0.34    |      | ns |

| t <sub>ESBCH</sub> | 2.00           |     | 2.50           |     | 2.75    |      | ns |

| t <sub>ESBCL</sub> | 2.00           |     | 2.50           |     | 2.75    |      | ns |

| t <sub>ESBWP</sub> | 1.17           |     | 1.68           |     | 2.18    |      | ns |

| t <sub>ESBRP</sub> | 0.95           |     | 1.35           |     | 1.76    |      | ns |

| Symbol              | -1 Speed Grade |      | -2 Speed Grade |      | -3 Speed | Unit |    |

|---------------------|----------------|------|----------------|------|----------|------|----|

|                     | Min            | Max  | Min            | Max  | Min      | Max  |    |

| t <sub>INSU</sub>   | 2.74           |      | 2.74           |      | 2.87     |      | ns |

| t <sub>INH</sub>    | 0.00           |      | 0.00           |      | 0.00     |      | ns |

| toutco              | 2.00           | 5.51 | 2.00           | 6.06 | 2.00     | 6.61 | ns |

| tINSUPLL            | 1.86           |      | 1.96           |      | -        |      | ns |

| t <sub>INHPLL</sub> | 0.00           |      | 0.00           |      | -        |      | ns |

| toutcopll           | 0.50           | 2.62 | 0.50           | 2.91 | -        | -    | ns |

| Symbol                    | -1 Speed Grade |      | -2 Spee | d Grade | -3 Spee | Unit |    |

|---------------------------|----------------|------|---------|---------|---------|------|----|

|                           | Min            | Max  | Min     | Max     | Min     | Max  |    |

| t <sub>insubidir</sub>    | 0.64           |      | 0.98    |         | 1.08    |      | ns |

| t <sub>inhbidir</sub>     | 0.00           |      | 0.00    |         | 0.00    |      | ns |

| toutcobidir               | 2.00           | 5.51 | 2.00    | 6.06    | 2.00    | 6.61 | ns |

| t <sub>xzbidir</sub>      |                | 6.10 |         | 6.74    |         | 7.10 | ns |

| t <sub>zxbidir</sub>      |                | 6.10 |         | 6.74    |         | 7.10 | ns |

| t <sub>insubidirpll</sub> | 2.26           |      | 2.68    |         | -       |      | ns |

| t <sub>inhbidirpll</sub>  | 0.00           |      | 0.00    |         | -       |      | ns |

| toutcobidirpll            | 0.50           | 2.62 | 0.50    | 2.91    | -       | -    | ns |

| t <sub>xzbidirpll</sub>   |                | 3.21 |         | 3.59    |         | -    | ns |

| t <sub>ZXBIDIRPLL</sub>   |                | 3.21 |         | 3.59    |         | -    | ns |

| Symbol                  | -1 Spee | d Grade | -2 Spee | ed Grade | -3 Spee | d Grade | Unit |

|-------------------------|---------|---------|---------|----------|---------|---------|------|

|                         | Min     | Max     | Min     | Max      | Min     | Мах     |      |

| t <sub>ESBARC</sub>     |         | 1.78    |         | 2.02     |         | 1.95    | ns   |

| t <sub>ESBSRC</sub>     |         | 2.52    |         | 2.91     |         | 3.14    | ns   |

| t <sub>ESBAWC</sub>     |         | 3.52    |         | 4.11     |         | 4.40    | ns   |

| t <sub>ESBSWC</sub>     |         | 3.23    |         | 3.84     |         | 4.16    | ns   |

| t <sub>ESBWASU</sub>    | 0.62    |         | 0.67    |          | 0.61    |         | ns   |

| t <sub>ESBWAH</sub>     | 0.41    |         | 0.55    |          | 0.55    |         | ns   |

| t <sub>ESBWDSU</sub>    | 0.77    |         | 0.79    |          | 0.81    |         | ns   |

| t <sub>ESBWDH</sub>     | 0.41    |         | 0.55    |          | 0.55    |         | ns   |

| t <sub>ESBRASU</sub>    | 1.74    |         | 1.92    |          | 1.85    |         | ns   |

| t <sub>ESBRAH</sub>     | 0.00    |         | 0.01    |          | 0.23    |         | ns   |

| t <sub>ESBWESU</sub>    | 2.07    |         | 2.28    |          | 2.41    |         | ns   |

| t <sub>ESBWEH</sub>     | 0.00    |         | 0.00    |          | 0.00    |         | ns   |

| t <sub>ESBDATASU</sub>  | 0.25    |         | 0.27    |          | 0.29    |         | ns   |

| t <sub>ESBDATAH</sub>   | 0.13    |         | 0.13    |          | 0.13    |         | ns   |

| t <sub>ESBWADDRSU</sub> | 0.11    |         | 0.04    |          | 0.11    |         | ns   |

| t <sub>ESBRADDRSU</sub> | 0.14    |         | 0.11    |          | 0.16    |         | ns   |

| t <sub>ESBDATACO1</sub> |         | 1.29    |         | 1.50     |         | 1.63    | ns   |

| t <sub>ESBDATACO2</sub> |         | 2.55    |         | 2.99     |         | 3.22    | ns   |

| t <sub>ESBDD</sub>      |         | 3.12    |         | 3.57     |         | 3.85    | ns   |

| t <sub>PD</sub>         |         | 1.84    |         | 2.13     |         | 2.32    | ns   |

| t <sub>PTERMSU</sub>    | 1.08    |         | 1.19    |          | 1.32    |         | ns   |

| t <sub>PTERMCO</sub>    |         | 1.31    |         | 1.53     |         | 1.66    | ns   |

| Table 105. EP.     | Table 105. EP20K1500E f <sub>MAX</sub> Routing Delays |          |         |          |                |      |                   |  |      |  |  |  |

|--------------------|-------------------------------------------------------|----------|---------|----------|----------------|------|-------------------|--|------|--|--|--|

| Symbol             | -1 Spee                                               | ed Grade | -2 Spec | ed Grade | -3 Speed Grade |      | ade -3 Speed Grad |  | Unit |  |  |  |

|                    | Min                                                   | Max      | Min     | Мах      | Min            | Max  |                   |  |      |  |  |  |

| t <sub>F1-4</sub>  |                                                       | 0.28     |         | 0.28     |                | 0.28 | ns                |  |      |  |  |  |

| t <sub>F5-20</sub> |                                                       | 1.36     |         | 1.50     |                | 1.62 | ns                |  |      |  |  |  |

| t <sub>F20+</sub>  |                                                       | 4.43     |         | 4.48     |                | 5.07 | ns                |  |      |  |  |  |

| Table 110. Selectab | ole I/O Standa | ord Output De  | lays |                |     |                |     |

|---------------------|----------------|----------------|------|----------------|-----|----------------|-----|

| Symbol              | -1 Spee        | -1 Speed Grade |      | -2 Speed Grade |     | -3 Speed Grade |     |

|                     | Min            | Max            | Min  | Max            | Min | Max            | Min |

| LVCMOS              |                | 0.00           |      | 0.00           |     | 0.00           | ns  |

| LVTTL               |                | 0.00           |      | 0.00           |     | 0.00           | ns  |

| 2.5 V               |                | 0.00           |      | 0.09           |     | 0.10           | ns  |

| 1.8 V               |                | 2.49           |      | 2.98           |     | 3.03           | ns  |

| PCI                 |                | -0.03          |      | 0.17           |     | 0.16           | ns  |

| GTL+                |                | 0.75           |      | 0.75           |     | 0.76           | ns  |

| SSTL-3 Class I      |                | 1.39           |      | 1.51           |     | 1.50           | ns  |

| SSTL-3 Class II     |                | 1.11           |      | 1.23           |     | 1.23           | ns  |

| SSTL-2 Class I      |                | 1.35           |      | 1.48           |     | 1.47           | ns  |

| SSTL-2 Class II     |                | 1.00           |      | 1.12           |     | 1.12           | ns  |

| LVDS                |                | -0.48          |      | -0.48          |     | -0.48          | ns  |

| CTT                 |                | 0.00           |      | 0.00           |     | 0.00           | ns  |

| AGP                 |                | 0.00           |      | 0.00           |     | 0.00           | ns  |

## Power Consumption

To estimate device power consumption, use the interactive power calculator on the Altera web site at **http://www.altera.com**.

# Configuration & Operation

The APEX 20K architecture supports several configuration schemes. This section summarizes the device operating modes and available device configuration schemes.

## **Operating Modes**

The APEX architecture uses SRAM configuration elements that require configuration data to be loaded each time the circuit powers up. The process of physically loading the SRAM data into the device is called configuration. During initialization, which occurs immediately after configuration, the device resets registers, enables I/O pins, and begins to operate as a logic device. The I/O pins are tri-stated during power-up, and before and during configuration. Together, the configuration and initialization processes are called *command mode*; normal device operation is called *user mode*.

Before and during device configuration, all I/O pins are pulled to  $\rm V_{\rm CCIO}$  by a built-in weak pull-up resistor.