Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Obsolete                                                      |

| Number of LABs/CLBs            | 640                                                           |

| Number of Logic Elements/Cells | 6400                                                          |

| Total RAM Bits                 | 81920                                                         |

| Number of I/O                  | 316                                                           |

| Number of Gates                | 404000                                                        |

| Voltage - Supply               | 1.71V ~ 1.89V                                                 |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                               |

| Package / Case                 | 484-BBGA                                                      |

| Supplier Device Package        | 484-FBGA (23x23)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep20k160efc484-1xb |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Logic Array Block**

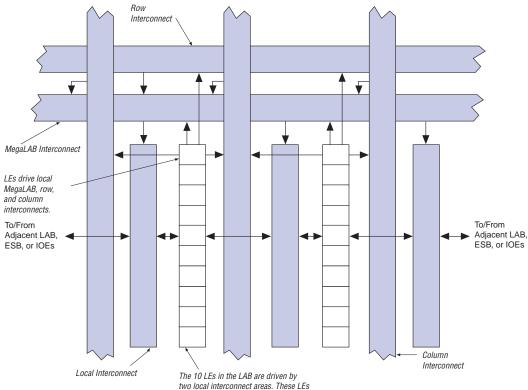

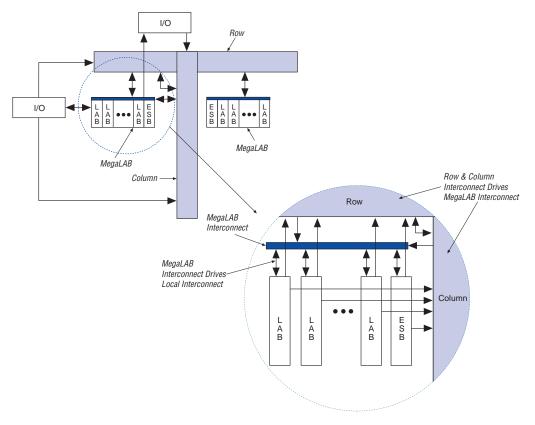

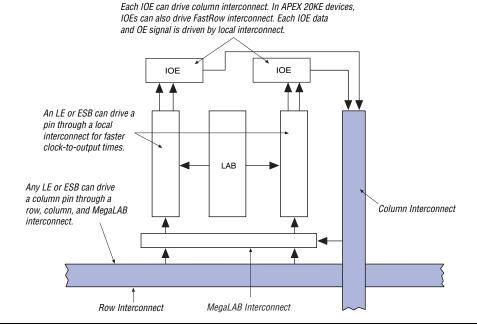

Each LAB consists of 10 LEs, the LEs' associated carry and cascade chains, LAB control signals, and the local interconnect. The local interconnect transfers signals between LEs in the same or adjacent LABs, IOEs, or ESBs. The Quartus II Compiler places associated logic within an LAB or adjacent LABs, allowing the use of a fast local interconnect for high performance. Figure 3 shows the APEX 20K LAB.

APEX 20K devices use an interleaved LAB structure. This structure allows each LE to drive two local interconnect areas. This feature minimizes use of the MegaLAB and FastTrack interconnect, providing higher performance and flexibility. Each LE can drive 29 other LEs through the fast local interconnect.

Altera Corporation 11

can drive two local interconnect areas.

#### Cascade Chain

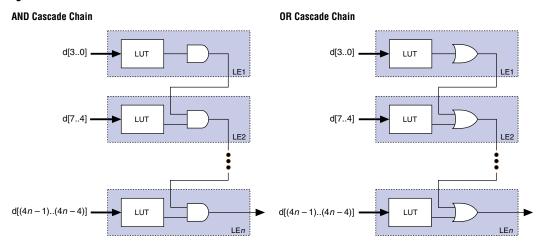

With the cascade chain, the APEX 20K architecture can implement functions with a very wide fan-in. Adjacent LUTs can compute portions of a function in parallel; the cascade chain serially connects the intermediate values. The cascade chain can use a logical AND or logical OR (via De Morgan's inversion) to connect the outputs of adjacent LEs. Each additional LE provides four more inputs to the effective width of a function, with a short cascade delay. Cascade chain logic can be created automatically by the Quartus II software Compiler during design processing, or manually by the designer during design entry.

Cascade chains longer than ten LEs are implemented automatically by linking LABs together. For enhanced fitting, a long cascade chain skips alternate LABs in a MegaLAB structure. A cascade chain longer than one LAB skips either from an even-numbered LAB to the next even-numbered LAB, or from an odd-numbered LAB to the next odd-numbered LAB. For example, the last LE of the first LAB in the upper-left MegaLAB structure carries to the first LE of the third LAB in the MegaLAB structure. Figure 7 shows how the cascade function can connect adjacent LEs to form functions with a wide fan-in.

Figure 7. APEX 20K Cascade Chain

Figure 10. FastTrack Connection to Local Interconnect

Table 10 describes the APEX 20K programmable delays and their logic options in the Quartus II software.

| Table 10. APEX 20K Programmable Delay Chains |                                         |  |  |  |  |

|----------------------------------------------|-----------------------------------------|--|--|--|--|

| Programmable Delays                          | Quartus II Logic Option                 |  |  |  |  |

| Input pin to core delay                      | Decrease input delay to internal cells  |  |  |  |  |

| Input pin to input register delay            | Decrease input delay to input register  |  |  |  |  |

| Core to output register delay                | Decrease input delay to output register |  |  |  |  |

| Output register t <sub>CO</sub> delay        | Increase delay to output pin            |  |  |  |  |

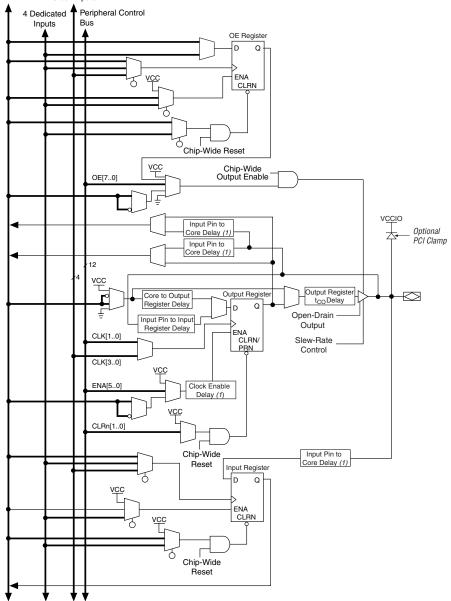

The Quartus II software compiler can program these delays automatically to minimize setup time while providing a zero hold time. Figure 25 shows how fast bidirectional I/Os are implemented in APEX 20K devices.

The register in the APEX 20K IOE can be programmed to power-up high or low after configuration is complete. If it is programmed to power-up low, an asynchronous clear can control the register. If it is programmed to power-up high, the register cannot be asynchronously cleared or preset. This feature is useful for cases where the APEX 20K device controls an active-low input or another device; it prevents inadvertent activation of the input upon power-up.

APEX 20KE devices include an enhanced IOE, which drives the FastRow interconnect. The FastRow interconnect connects a column I/O pin directly to the LAB local interconnect within two MegaLAB structures. This feature provides fast setup times for pins that drive high fan-outs with complex logic, such as PCI designs. For fast bidirectional I/O timing, LE registers using local routing can improve setup times and OE timing. The APEX 20KE IOE also includes direct support for open-drain operation, giving faster clock-to-output for open-drain signals. Some programmable delays in the APEX 20KE IOE offer multiple levels of delay to fine-tune setup and hold time requirements. The Quartus II software compiler can set these delays automatically to minimize setup time while providing a zero hold time.

Table 11 describes the APEX 20KE programmable delays and their logic options in the Quartus II software.

| Table 11. APEX 20KE Programmable Delay Chains |                                         |  |  |  |  |

|-----------------------------------------------|-----------------------------------------|--|--|--|--|

| Programmable Delays                           | Quartus II Logic Option                 |  |  |  |  |

| Input Pin to Core Delay                       | Decrease input delay to internal cells  |  |  |  |  |

| Input Pin to Input Register Delay             | Decrease input delay to input registers |  |  |  |  |

| Core to Output Register Delay                 | Decrease input delay to output register |  |  |  |  |

| Output Register t <sub>CO</sub> Delay         | Increase delay to output pin            |  |  |  |  |

| Clock Enable Delay                            | Increase clock enable delay             |  |  |  |  |

The register in the APEX 20KE IOE can be programmed to power-up high or low after configuration is complete. If it is programmed to power-up low, an asynchronous clear can control the register. If it is programmed to power-up high, an asynchronous preset can control the register. Figure 26 shows how fast bidirectional I/O pins are implemented in APEX 20KE devices. This feature is useful for cases where the APEX 20KE device controls an active-low input or another device; it prevents inadvertent activation of the input upon power-up.

Figure 26. APEX 20KE Bidirectional I/O Registers Notes (1), (2)

Row, Column, FastRow, 4 Dedicated or Local Interconnect Clock Inputs

Notes to Figure 26:

- (1) This programmable delay has four settings: off and three levels of delay.

- (2) The output enable and input registers are LE registers in the LAB adjacent to the bidirectional pin.

Figure 28 shows how a column IOE connects to the interconnect.

Figure 28. Column IOE Connection to the Interconnect

### **Dedicated Fast I/O Pins**

APEX 20KE devices incorporate an enhancement to support bidirectional pins with high internal fanout such as PCI control signals. These pins are called Dedicated Fast I/O pins (FAST1, FAST2, FAST3, and FAST4) and replace dedicated inputs. These pins can be used for fast clock, clear, or high fanout logic signal distribution. They also can drive out. The Dedicated Fast I/O pin data output and tri-state control are driven by local interconnect from the adjacent MegaLAB for high speed.

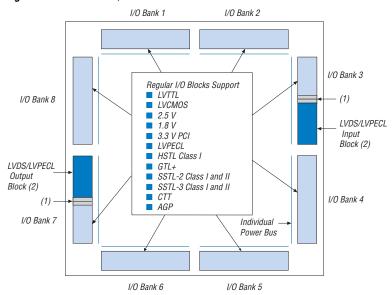

### Advanced I/O Standard Support

APEX 20KE IOEs support the following I/O standards: LVTTL, LVCMOS, 1.8-V I/O, 2.5-V I/O, 3.3-V PCI, PCI-X, 3.3-V AGP, LVDS, LVPECL, GTL+, CTT, HSTL Class I, SSTL-3 Class I and II, and SSTL-2 Class I and II.

For more information on I/O standards supported by APEX 20KE devices, see *Application Note 117 (Using Selectable I/O Standards in Altera Devices)*.

The APEX 20KE device contains eight I/O banks. In QFP packages, the banks are linked to form four I/O banks. The I/O banks directly support all standards except LVDS and LVPECL. All I/O banks can support LVDS and LVPECL with the addition of external resistors. In addition, one block within a bank contains circuitry to support high-speed True-LVDS and LVPECL inputs, and another block within a particular bank supports high-speed True-LVDS and LVPECL outputs. The LVDS blocks support all of the I/O standards. Each I/O bank has its own VCCIO pins. A single device can support 1.8-V, 2.5-V, and 3.3-V interfaces; each bank can support a different standard independently. Each bank can also use a separate V<sub>REF</sub> level so that each bank can support any of the terminated standards (such as SSTL-3) independently. Within a bank, any one of the terminated standards can be supported. EP20K300E and larger APEX 20KE devices support the LVDS interface for data pins (smaller devices support LVDS clock pins, but not data pins). All EP20K300E and larger devices support the LVDS interface for data pins up to 155 Mbit per channel; EP20K400E devices and larger with an X-suffix on the ordering code add a serializer/deserializer circuit and PLL for higher-speed support.

Each bank can support multiple standards with the same VCCIO for output pins. Each bank can support one voltage-referenced I/O standard, but it can support multiple I/O standards with the same VCCIO voltage level. For example, when VCCIO is 3.3 V, a bank can support LVTTL, LVCMOS, 3.3-V PCI, and SSTL-3 for inputs and outputs.

When the LVDS banks are not used as LVDS I/O banks, they support all of the other I/O standards. Figure 29 shows the arrangement of the APEX 20KE I/O banks.

Figure 29. APEX 20KE I/O Banks

#### Notes to Figure 29:

- For more information on placing I/O pins in LVDS blocks, refer to the Guidelines for Using LVDS Blocks section in Application Note 120 (Using LVDS in APEX 20KE Devices).

- (2) If the LVDS input and output blocks are not used for LVDS, they can support all of the I/O standards and can be used as input, output, or bidirectional pins with V<sub>CCIO</sub> set to 3.3 V, 2.5 V, or 1.8 V.

## **Power Sequencing & Hot Socketing**

Because APEX 20K and APEX 20KE devices can be used in a mixed-voltage environment, they have been designed specifically to tolerate any possible power-up sequence. Therefore, the  $V_{\rm CCIO}$  and  $V_{\rm CCINT}$  power supplies may be powered in any order.

For more information, please refer to the "Power Sequencing Considerations" section in the *Configuring APEX 20KE & APEX 20KC Devices* chapter of the *Configuration Devices Handbook*.

Signals can be driven into APEX 20K devices before and during power-up without damaging the device. In addition, APEX 20K devices do not drive out during power-up. Once operating conditions are reached and the device is configured, APEX 20K and APEX 20KE devices operate as specified by the user.

Under hot socketing conditions, APEX 20KE devices will not sustain any damage, but the I/O pins will drive out.

# MultiVolt I/O Interface

The APEX device architecture supports the MultiVolt I/O interface feature, which allows APEX devices in all packages to interface with systems of different supply voltages. The devices have one set of VCC pins for internal operation and input buffers (VCCINT), and another set for I/O output drivers (VCCIO).

The APEX 20K VCCINT pins must always be connected to a 2.5 V power supply. With a 2.5-V  $V_{CCINT}$  level, input pins are 2.5-V, 3.3-V, and 5.0-V tolerant. The VCCIO pins can be connected to either a 2.5-V or 3.3-V power supply, depending on the output requirements. When VCCIO pins are connected to a 2.5-V power supply, the output levels are compatible with 2.5-V systems. When the VCCIO pins are connected to a 3.3-V power supply, the output high is 3.3 V and is compatible with 3.3-V or 5.0-V systems.

| Table 12. 5.0-V Tolerant APEX 20K MultiVolt I/O Support |                                      |              |              |              |     |          |  |  |  |

|---------------------------------------------------------|--------------------------------------|--------------|--------------|--------------|-----|----------|--|--|--|

| V <sub>CCIO</sub> (V)                                   | Input Signals (V) Output Signals (V) |              |              |              |     |          |  |  |  |

|                                                         | 2.5                                  | 3.3          | 5.0          | 2.5          | 3.3 | 5.0      |  |  |  |

| 2.5                                                     | ✓                                    | <b>√</b> (1) | <b>√</b> (1) | ✓            |     |          |  |  |  |

| 3.3                                                     | <b>✓</b>                             | ✓            | <b>√</b> (1) | <b>√</b> (2) | ✓   | <b>✓</b> |  |  |  |

#### Notes to Table 12:

- (1) The PCI clamping diode must be disabled to drive an input with voltages higher than  $V_{\text{CCIO}}$ .

- (2) When  $V_{\rm CCIO}$  = 3.3 V, an APEX 20K device can drive a 2.5-V device with 3.3-V tolerant inputs.

Open-drain output pins on 5.0-V tolerant APEX 20K devices (with a pull-up resistor to the 5.0-V supply) can drive 5.0-V CMOS input pins that require a  $V_{\rm IH}$  of 3.5 V. When the pin is inactive, the trace will be pulled up to 5.0 V by the resistor. The open-drain pin will only drive low or tri-state; it will never drive high. The rise time is dependent on the value of the pull-up resistor and load impedance. The  $I_{\rm OL}$  current specification should be considered when selecting a pull-up resistor.

| Symbol                  | Parameter                                     | I/O Standard      | -1X Speed Grade |     | -2X Speed Grade |                                                                                                                   | Units |

|-------------------------|-----------------------------------------------|-------------------|-----------------|-----|-----------------|-------------------------------------------------------------------------------------------------------------------|-------|

|                         |                                               |                   | Min             | Max | Min             | Max                                                                                                               |       |

| f <sub>VCO</sub> (4)    | Voltage controlled oscillator operating range |                   | 200             | 500 | 200             | 500                                                                                                               | MHz   |

| f <sub>CLOCK0</sub>     | Clock0 PLL output frequency for internal use  |                   | 1.5             | 335 | 1.5             | 200                                                                                                               | MHz   |

| f <sub>CLOCK1</sub>     | Clock1 PLL output frequency for internal use  |                   | 20              | 335 | 20              | 200                                                                                                               | MHz   |

| CLOCKO LXII             | Output clock frequency for                    | 3.3-V LVTTL       | 1.5             | 245 | 1.5             | 226                                                                                                               | MHz   |

|                         | external clock0 output                        | 2.5-V LVTTL       | 1.5             | 234 | 1.5             | 221                                                                                                               | MHz   |

|                         |                                               | 1.8-V LVTTL       | 1.5             | 223 | 1.5             | 216                                                                                                               | MHz   |

|                         |                                               | GTL+              | 1.5             | 205 | 1.5             | 193                                                                                                               | MHz   |

|                         |                                               | SSTL-2 Class      | 1.5             | 158 | 1.5             | 157                                                                                                               | MHz   |

|                         |                                               | SSTL-2 Class      | 1.5             | 142 | 1.5             | 142                                                                                                               | MHz   |

|                         |                                               | SSTL-3 Class      | 1.5             | 166 | 1.5             | 162                                                                                                               | MHz   |

|                         |                                               | SSTL-3 Class      | 1.5             | 149 | 1.5             | 146                                                                                                               | MHz   |

|                         |                                               | LVDS              | 1.5             | 420 | 1.5             | 350                                                                                                               | MHz   |

| f <sub>CLOCK1_EXT</sub> | Output clock frequency for                    | 3.3-V LVTTL       | 20              | 245 | 20              | 226                                                                                                               | MHz   |

|                         | external clock1 output                        | 2.5-V LVTTL       | 20              | 234 | 20              | 5 200 0 200 5 226 5 221 5 216 5 193 5 157 5 142 5 162 5 146 6 350 0 226 0 221 0 216 0 193 0 157 0 142 0 162 0 146 | MHz   |

|                         |                                               | 1.8-V LVTTL       | 20              | 223 | 20              |                                                                                                                   | MHz   |

|                         |                                               | GTL+              | 20              | 205 | 20              | 193                                                                                                               | MHz   |

|                         |                                               | SSTL-2 Class<br>I | 20              | 158 | 20              | 157                                                                                                               | MHz   |

|                         |                                               | SSTL-2 Class      | 20              | 142 | 20              | 142                                                                                                               | MHz   |

|                         |                                               | SSTL-3 Class      | 20              | 166 | 20              | 162                                                                                                               | MHz   |

|                         |                                               | SSTL-3 Class      | 20              | 149 | 20              | 146                                                                                                               | MHz   |

|                         |                                               | LVDS              | 20              | 420 | 20              | 350                                                                                                               | MHz   |

Table 22 shows the JTAG timing parameters and values for APEX 20K devices

| Table 22. APEX 20K JTAG Timing Parameters & Values |                                                |     |     |      |  |  |  |  |

|----------------------------------------------------|------------------------------------------------|-----|-----|------|--|--|--|--|

| Symbol                                             | Parameter                                      | Min | Max | Unit |  |  |  |  |

| t <sub>JCP</sub>                                   | TCK clock period                               | 100 |     | ns   |  |  |  |  |

| t <sub>JCH</sub>                                   | TCK clock high time                            | 50  |     | ns   |  |  |  |  |

| t <sub>JCL</sub>                                   | TCK clock low time                             | 50  |     | ns   |  |  |  |  |

| t <sub>JPSU</sub>                                  | JTAG port setup time                           | 20  |     | ns   |  |  |  |  |

| t <sub>JPH</sub>                                   | JTAG port hold time                            | 45  |     | ns   |  |  |  |  |

| t <sub>JPCO</sub>                                  | JTAG port clock to output                      |     | 25  | ns   |  |  |  |  |

| t <sub>JPZX</sub>                                  | JTAG port high impedance to valid output       |     | 25  | ns   |  |  |  |  |

| t <sub>JPXZ</sub>                                  | JTAG port valid output to high impedance       |     | 25  | ns   |  |  |  |  |

| t <sub>JSSU</sub>                                  | Capture register setup time                    | 20  |     | ns   |  |  |  |  |

| t <sub>JSH</sub>                                   | Capture register hold time                     | 45  |     | ns   |  |  |  |  |

| t <sub>JSCO</sub>                                  | Update register clock to output                |     | 35  | ns   |  |  |  |  |

| t <sub>JSZX</sub>                                  | Update register high impedance to valid output |     | 35  | ns   |  |  |  |  |

| t <sub>JSXZ</sub>                                  | Update register valid output to high impedance |     | 35  | ns   |  |  |  |  |

For more information, see the following documents:

- Application Note 39 (IEEE Std. 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices)

- Jam Programming & Test Language Specification

## **Generic Testing**

Each APEX 20K device is functionally tested. Complete testing of each configurable static random access memory (SRAM) bit and all logic functionality ensures 100% yield. AC test measurements for APEX 20K devices are made under conditions equivalent to those shown in Figure 32. Multiple test patterns can be used to configure devices during all stages of the production flow.

| Table 2            | Table 26. APEX 20K 5.0-V Tolerant Device Capacitance   Notes (2), (14) |                                     |     |     |      |  |  |  |

|--------------------|------------------------------------------------------------------------|-------------------------------------|-----|-----|------|--|--|--|

| Symbol             | Parameter                                                              | Conditions                          | Min | Max | Unit |  |  |  |

| C <sub>IN</sub>    | Input capacitance                                                      | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 8   | pF   |  |  |  |

| C <sub>INCLK</sub> | Input capacitance on dedicated clock pin                               | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 12  | pF   |  |  |  |

| C <sub>OUT</sub>   | Output capacitance                                                     | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 8   | pF   |  |  |  |

#### Notes to Tables 23 through 26:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) All APEX 20K devices are 5.0-V tolerant.

- (3) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to 5.75 V for input currents less than 100 mA and periods shorter than 20 ns.

- (4) Numbers in parentheses are for industrial-temperature-range devices.

- (5) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically.

- (6) All pins, including dedicated inputs, clock I/O, and JTAG pins, may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are powered.

- (7) Typical values are for  $T_A = 25^{\circ}$  C,  $V_{CCINT} = 2.5$  V, and  $V_{CCIO} = 2.5$  or 3.3 V.

- (8) These values are specified in the APEX 20K device recommended operating conditions, shown in Table 26 on page 62.

- (9) The APEX 20K input buffers are compatible with 2.5-V and 3.3-V (LVTTL and LVCMOS) signals. Additionally, the input buffers are 3.3-V PCI compliant when V<sub>CCIO</sub> and V<sub>CCINT</sub> meet the relationship shown in Figure 33 on page 68.

- (10) The I<sub>OH</sub> parameter refers to high-level TTL, PCI or CMOS output current.

- (11) The I<sub>OL</sub> parameter refers to low-level TTL, PCI, or CMOS output current. This parameter applies to open-drain pins as well as output pins.

- (12) This value is specified for normal device operation. The value may vary during power-up.

- (13) Pin pull-up resistance values will be lower if an external source drives the pin higher than V<sub>CCIO</sub>.

- (14) Capacitance is sample-tested only.

Tables 27 through 30 provide information on absolute maximum ratings, recommended operating conditions, DC operating conditions, and capacitance for 1.8-V APEX 20KE devices.

| Table 27. APEX 20KE Device Absolute Maximum Ratings       Note (1) |                            |                                                |      |     |      |  |  |  |

|--------------------------------------------------------------------|----------------------------|------------------------------------------------|------|-----|------|--|--|--|

| Symbol                                                             | Parameter                  | Conditions                                     | Min  | Max | Unit |  |  |  |

| V <sub>CCINT</sub>                                                 | Supply voltage             | With respect to ground (2)                     | -0.5 | 2.5 | ٧    |  |  |  |

| $V_{CCIO}$                                                         |                            |                                                | -0.5 | 4.6 | ٧    |  |  |  |

| VI                                                                 | DC input voltage           |                                                | -0.5 | 4.6 | ٧    |  |  |  |

| I <sub>OUT</sub>                                                   | DC output current, per pin |                                                | -25  | 25  | mA   |  |  |  |

| T <sub>STG</sub>                                                   | Storage temperature        | No bias                                        | -65  | 150 | °C   |  |  |  |

| T <sub>AMB</sub>                                                   | Ambient temperature        | Under bias                                     | -65  | 135 | ° C  |  |  |  |

| TJ                                                                 | Junction temperature       | PQFP, RQFP, TQFP, and BGA packages, under bias |      | 135 | ° C  |  |  |  |

|                                                                    |                            | Ceramic PGA packages, under bias               |      | 150 | °C   |  |  |  |

#### Notes to Tables 43 through 48:

- (1) This parameter is measured without using ClockLock or ClockBoost circuits.

- (2) This parameter is measured using ClockLock or ClockBoost circuits.

Tables 49 through 54 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K30E APEX 20KE devices.

| Table 49. EP20K30E f <sub>MAX</sub> LE Timing Microparameters |      |      |      |      |      |      |      |  |  |  |

|---------------------------------------------------------------|------|------|------|------|------|------|------|--|--|--|

| Symbol                                                        | -1   |      | -2   |      | -3   |      | Unit |  |  |  |

|                                                               | Min  | Max  | Min  | Max  | Min  | Max  | 1    |  |  |  |

| t <sub>SU</sub>                                               | 0.01 |      | 0.02 |      | 0.02 |      | ns   |  |  |  |

| t <sub>H</sub>                                                | 0.11 |      | 0.16 |      | 0.23 |      | ns   |  |  |  |

| t <sub>CO</sub>                                               |      | 0.32 |      | 0.45 |      | 0.67 | ns   |  |  |  |

| t <sub>LUT</sub>                                              |      | 0.85 |      | 1.20 |      | 1.77 | ns   |  |  |  |

| Table 57. EP20K60E f <sub>MAX</sub> Routing Delays |     |      |     |      |     |      |    |  |  |  |

|----------------------------------------------------|-----|------|-----|------|-----|------|----|--|--|--|

| Symbol                                             | -   | -1   |     | -2   |     | -3   |    |  |  |  |

|                                                    | Min | Max  | Min | Max  | Min | Max  |    |  |  |  |

| t <sub>F1-4</sub>                                  |     | 0.24 |     | 0.26 |     | 0.30 | ns |  |  |  |

| t <sub>F5-20</sub>                                 |     | 1.45 |     | 1.58 |     | 1.79 | ns |  |  |  |

| t <sub>F20+</sub>                                  |     | 1.96 |     | 2.14 |     | 2.45 | ns |  |  |  |

| Symbol             | -    | 1   | -    | -2  |      | -3  |    |

|--------------------|------|-----|------|-----|------|-----|----|

|                    | Min  | Max | Min  | Max | Min  | Max |    |

| t <sub>CH</sub>    | 2.00 |     | 2.50 |     | 2.75 |     | ns |

| t <sub>CL</sub>    | 2.00 |     | 2.50 |     | 2.75 |     | ns |

| t <sub>CLRP</sub>  | 0.20 |     | 0.28 |     | 0.41 |     | ns |

| t <sub>PREP</sub>  | 0.20 |     | 0.28 |     | 0.41 |     | ns |

| t <sub>ESBCH</sub> | 2.00 |     | 2.50 |     | 2.75 |     | ns |

| t <sub>ESBCL</sub> | 2.00 |     | 2.50 |     | 2.75 |     | ns |

| t <sub>ESBWP</sub> | 1.29 |     | 1.80 |     | 2.66 |     | ns |

| t <sub>ESBRP</sub> | 1.04 |     | 1.45 |     | 2.14 |     | ns |

| Table 59. EP20K60E External Timing Parameters |      |      |      |      |      |      |    |  |  |  |  |

|-----------------------------------------------|------|------|------|------|------|------|----|--|--|--|--|

| Symbol                                        | -    | -1   |      | -2   |      | -3   |    |  |  |  |  |

|                                               | Min  | Max  | Min  | Max  | Min  | Max  | 1  |  |  |  |  |

| t <sub>INSU</sub>                             | 2.03 |      | 2.12 |      | 2.23 |      | ns |  |  |  |  |

| t <sub>INH</sub>                              | 0.00 |      | 0.00 |      | 0.00 |      | ns |  |  |  |  |

| toutco                                        | 2.00 | 4.84 | 2.00 | 5.31 | 2.00 | 5.81 | ns |  |  |  |  |

| t <sub>INSUPLL</sub>                          | 1.12 |      | 1.15 |      | -    |      | ns |  |  |  |  |

| t <sub>INHPLL</sub>                           | 0.00 |      | 0.00 |      | -    |      | ns |  |  |  |  |

| t <sub>OUTCOPLL</sub>                         | 0.50 | 3.37 | 0.50 | 3.69 | -    | -    | ns |  |  |  |  |

| Symbol                     | -1   |      | -    | 2    | -    | Unit |    |

|----------------------------|------|------|------|------|------|------|----|

|                            | Min  | Max  | Min  | Max  | Min  | Max  |    |

| t <sub>INSUBIDIR</sub>     | 2.77 |      | 2.91 |      | 3.11 |      | ns |

| t <sub>INHBIDIR</sub>      | 0.00 |      | 0.00 |      | 0.00 |      | ns |

| t <sub>OUTCOBIDIR</sub>    | 2.00 | 4.84 | 2.00 | 5.31 | 2.00 | 5.81 | ns |

| t <sub>XZBIDIR</sub>       |      | 6.47 |      | 7.44 |      | 8.65 | ns |

| t <sub>ZXBIDIR</sub>       |      | 6.47 |      | 7.44 |      | 8.65 | ns |

| t <sub>INSUBIDIRPLL</sub>  | 3.44 |      | 3.24 |      | -    |      | ns |

| tinhbidirpll               | 0.00 |      | 0.00 |      | -    |      | ns |

| <sup>t</sup> OUTCOBIDIRPLL | 0.50 | 3.37 | 0.50 | 3.69 | -    | -    | ns |

| txzbidirpll                |      | 5.00 |      | 5.82 |      | -    | ns |

| tzxbidirpll                |      | 5.00 |      | 5.82 |      | -    | ns |

Tables 61 through 66 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K100E APEX 20KE devices.

| Table 61. EP20K100E f <sub>MAX</sub> LE Timing Microparameters |      |      |      |      |      |      |    |  |  |  |  |

|----------------------------------------------------------------|------|------|------|------|------|------|----|--|--|--|--|

| Symbol                                                         | -    | 1    | -    | 2    | -1   | Unit |    |  |  |  |  |

|                                                                | Min  | Max  | Min  | Max  | Min  | Max  | 1  |  |  |  |  |

| t <sub>SU</sub>                                                | 0.25 |      | 0.25 |      | 0.25 |      | ns |  |  |  |  |

| t <sub>H</sub>                                                 | 0.25 |      | 0.25 |      | 0.25 |      | ns |  |  |  |  |

| t <sub>CO</sub>                                                |      | 0.28 |      | 0.28 |      | 0.34 | ns |  |  |  |  |

| t <sub>LUT</sub>                                               |      | 0.80 |      | 0.95 |      | 1.13 | ns |  |  |  |  |

| Table 76. EP20K200E Minimum Pulse Width Timing Parameters |      |     |      |     |      |     |      |  |  |  |  |

|-----------------------------------------------------------|------|-----|------|-----|------|-----|------|--|--|--|--|

| Symbol                                                    | -1   |     | -2   |     | -3   |     | Unit |  |  |  |  |

|                                                           | Min  | Max | Min  | Max | Min  | Max |      |  |  |  |  |

| t <sub>CH</sub>                                           | 1.36 |     | 2.44 |     | 2.65 |     | ns   |  |  |  |  |

| t <sub>CL</sub>                                           | 1.36 |     | 2.44 |     | 2.65 |     | ns   |  |  |  |  |

| t <sub>CLRP</sub>                                         | 0.18 |     | 0.19 |     | 0.21 |     | ns   |  |  |  |  |

| t <sub>PREP</sub>                                         | 0.18 |     | 0.19 |     | 0.21 |     | ns   |  |  |  |  |

| t <sub>ESBCH</sub>                                        | 1.36 |     | 2.44 |     | 2.65 |     | ns   |  |  |  |  |

| t <sub>ESBCL</sub>                                        | 1.36 |     | 2.44 |     | 2.65 |     | ns   |  |  |  |  |

| t <sub>ESBWP</sub>                                        | 1.18 |     | 1.48 |     | 1.76 |     | ns   |  |  |  |  |

| t <sub>ESBRP</sub>                                        | 0.95 |     | 1.17 |     | 1.41 |     | ns   |  |  |  |  |

| Symbol                | -1   |      | -    | -2   |      | -3   |    |

|-----------------------|------|------|------|------|------|------|----|

|                       | Min  | Max  | Min  | Max  | Min  | Max  | 7  |

| t <sub>INSU</sub>     | 2.24 |      | 2.35 |      | 2.47 |      | ns |

| t <sub>INH</sub>      | 0.00 |      | 0.00 |      | 0.00 |      | ns |

| t <sub>outco</sub>    | 2.00 | 5.12 | 2.00 | 5.62 | 2.00 | 6.11 | ns |

| t <sub>INSUPLL</sub>  | 2.13 |      | 2.07 |      | -    |      | ns |

| t <sub>INHPLL</sub>   | 0.00 |      | 0.00 |      | -    |      | ns |

| t <sub>OUTCOPLL</sub> | 0.50 | 3.01 | 0.50 | 3.36 | -    | -    | ns |

| Symbol                  | -1 Spee | d Grade | -2 Spee | ed Grade | -3 Spee | Unit |    |

|-------------------------|---------|---------|---------|----------|---------|------|----|

|                         | Min     | Max     | Min     | Max      | Min     | Max  |    |

| t <sub>ESBARC</sub>     |         | 1.67    |         | 1.91     |         | 1.99 | ns |

| t <sub>ESBSRC</sub>     |         | 2.30    |         | 2.66     |         | 2.93 | ns |

| t <sub>ESBAWC</sub>     |         | 3.09    |         | 3.58     |         | 3.99 | ns |

| t <sub>ESBSWC</sub>     |         | 3.01    |         | 3.65     |         | 4.05 | ns |

| t <sub>ESBWASU</sub>    | 0.54    |         | 0.63    |          | 0.65    |      | ns |

| t <sub>ESBWAH</sub>     | 0.36    |         | 0.43    |          | 0.42    |      | ns |

| t <sub>ESBWDSU</sub>    | 0.69    |         | 0.77    |          | 0.84    |      | ns |

| t <sub>ESBWDH</sub>     | 0.36    |         | 0.43    |          | 0.42    |      | ns |

| t <sub>ESBRASU</sub>    | 1.61    |         | 1.77    |          | 1.86    |      | ns |

| t <sub>ESBRAH</sub>     | 0.00    |         | 0.00    |          | 0.01    |      | ns |

| t <sub>ESBWESU</sub>    | 1.35    |         | 1.47    |          | 1.61    |      | ns |

| t <sub>ESBWEH</sub>     | 0.00    |         | 0.00    |          | 0.00    |      | ns |

| t <sub>ESBDATASU</sub>  | -0.18   |         | -0.30   |          | -0.27   |      | ns |

| t <sub>ESBDATAH</sub>   | 0.13    |         | 0.13    |          | 0.13    |      | ns |

| t <sub>ESBWADDRSU</sub> | -0.02   |         | -0.11   |          | -0.03   |      | ns |

| t <sub>ESBRADDRSU</sub> | 0.06    |         | -0.01   |          | -0.05   |      | ns |

| t <sub>ESBDATACO1</sub> |         | 1.16    |         | 1.40     |         | 1.54 | ns |

| t <sub>ESBDATACO2</sub> |         | 2.18    |         | 2.55     |         | 2.85 | ns |

| t <sub>ESBDD</sub>      |         | 2.73    |         | 3.17     |         | 3.58 | ns |

| t <sub>PD</sub>         |         | 1.57    |         | 1.83     |         | 2.07 | ns |

| t <sub>PTERMSU</sub>    | 0.92    |         | 0.99    |          | 1.18    |      | ns |

| t <sub>PTERMCO</sub>    |         | 1.18    |         | 1.43     |         | 1.17 | ns |

| Table 87. EP20K400E f <sub>MAX</sub> Routing Delays |         |         |        |          |         |         |      |  |  |  |  |

|-----------------------------------------------------|---------|---------|--------|----------|---------|---------|------|--|--|--|--|

| Symbol                                              | -1 Spee | d Grade | -2 Spe | ed Grade | -3 Spee | d Grade | Unit |  |  |  |  |

|                                                     | Min     | Max     | Min    | Max      | Min     | Max     |      |  |  |  |  |

| t <sub>F1-4</sub>                                   |         | 0.25    |        | 0.25     |         | 0.26    | ns   |  |  |  |  |

| t <sub>F5-20</sub>                                  |         | 1.01    |        | 1.12     |         | 1.25    | ns   |  |  |  |  |

| t <sub>F20+</sub>                                   |         | 3.71    |        | 3.92     |         | 4.17    | ns   |  |  |  |  |

| Symbol             | -1 Speed Grade |     | -2 Speed Grade |     | -3 Spee | Unit |    |

|--------------------|----------------|-----|----------------|-----|---------|------|----|

|                    | Min            | Max | Min            | Max | Min     | Max  |    |

| t <sub>CH</sub>    | 1.36           |     | 2.22           |     | 2.35    |      | ns |

| t <sub>CL</sub>    | 1.36           |     | 2.26           |     | 2.35    |      | ns |

| t <sub>CLRP</sub>  | 0.18           |     | 0.18           |     | 0.19    |      | ns |

| t <sub>PREP</sub>  | 0.18           |     | 0.18           |     | 0.19    |      | ns |

| t <sub>ESBCH</sub> | 1.36           |     | 2.26           |     | 2.35    |      | ns |

| t <sub>ESBCL</sub> | 1.36           |     | 2.26           |     | 2.35    |      | ns |

| t <sub>ESBWP</sub> | 1.17           |     | 1.38           |     | 1.56    |      | ns |

| t <sub>ESBRP</sub> | 0.94           |     | 1.09           |     | 1.25    |      | ns |

| Table 89. EP20K400E External Timing Parameters |                |      |         |                |      |                |    |  |  |  |  |

|------------------------------------------------|----------------|------|---------|----------------|------|----------------|----|--|--|--|--|

| Symbol                                         | -1 Speed Grade |      | -2 Spee | -2 Speed Grade |      | -3 Speed Grade |    |  |  |  |  |

|                                                | Min            | Max  | Min     | Max            | Min  | Max            |    |  |  |  |  |

| t <sub>INSU</sub>                              | 2.51           |      | 2.64    |                | 2.77 |                | ns |  |  |  |  |

| t <sub>INH</sub>                               | 0.00           |      | 0.00    |                | 0.00 |                | ns |  |  |  |  |

| t <sub>OUTCO</sub>                             | 2.00           | 5.25 | 2.00    | 5.79           | 2.00 | 6.32           | ns |  |  |  |  |

| t <sub>INSUPLL</sub>                           | 3.221          |      | 3.38    |                | -    |                | ns |  |  |  |  |

| t <sub>INHPLL</sub>                            | 0.00           |      | 0.00    |                | -    |                | ns |  |  |  |  |

| toutcople                                      | 0.50           | 2.25 | 0.50    | 2.45           | -    | -              | ns |  |  |  |  |

| Table 92. EP20K         | 600E f <sub>MAX</sub> ESE | 3 Timing Micr | oparameters |          |         |         |      |

|-------------------------|---------------------------|---------------|-------------|----------|---------|---------|------|

| Symbol                  | -1 Spee                   | d Grade       | -2 Spee     | ed Grade | -3 Spee | d Grade | Unit |

|                         | Min                       | Max           | Min         | Max      | Min     | Max     |      |

| t <sub>ESBARC</sub>     |                           | 1.67          |             | 2.39     |         | 3.11    | ns   |

| t <sub>ESBSRC</sub>     |                           | 2.27          |             | 3.07     |         | 3.86    | ns   |

| t <sub>ESBAWC</sub>     |                           | 3.19          |             | 4.56     |         | 5.93    | ns   |

| t <sub>ESBSWC</sub>     |                           | 3.51          |             | 4.62     |         | 5.72    | ns   |

| t <sub>ESBWASU</sub>    | 1.46                      |               | 2.08        |          | 2.70    |         | ns   |

| t <sub>ESBWAH</sub>     | 0.00                      |               | 0.00        |          | 0.00    |         | ns   |

| t <sub>ESBWDSU</sub>    | 1.60                      |               | 2.29        |          | 2.97    |         | ns   |

| t <sub>ESBWDH</sub>     | 0.00                      |               | 0.00        |          | 0.00    |         | ns   |

| t <sub>ESBRASU</sub>    | 1.61                      |               | 2.30        |          | 2.99    |         | ns   |

| t <sub>ESBRAH</sub>     | 0.00                      |               | 0.00        |          | 0.00    |         | ns   |

| t <sub>ESBWESU</sub>    | 1.49                      |               | 2.30        |          | 3.11    |         | ns   |

| t <sub>ESBWEH</sub>     | 0.00                      |               | 0.00        |          | 0.00    |         | ns   |

| t <sub>ESBDATASU</sub>  | -0.01                     |               | 0.35        |          | 0.71    |         | ns   |

| t <sub>ESBDATAH</sub>   | 0.13                      |               | 0.13        |          | 0.13    |         | ns   |

| t <sub>ESBWADDRSU</sub> | 0.19                      |               | 0.62        |          | 1.06    |         | ns   |

| t <sub>ESBRADDRSU</sub> | 0.25                      |               | 0.71        |          | 1.17    |         | ns   |

| t <sub>ESBDATACO1</sub> |                           | 1.01          |             | 1.19     |         | 1.37    | ns   |

| t <sub>ESBDATACO2</sub> |                           | 2.18          |             | 3.12     |         | 4.05    | ns   |

| t <sub>ESBDD</sub>      |                           | 3.19          |             | 4.56     |         | 5.93    | ns   |

| t <sub>PD</sub>         |                           | 1.57          |             | 2.25     |         | 2.92    | ns   |

| t <sub>PTERMSU</sub>    | 0.85                      |               | 1.43        |          | 2.01    |         | ns   |

| t <sub>PTERMCO</sub>    |                           | 1.03          |             | 1.21     |         | 1.39    | ns   |

| Table 93. EP20K600E f <sub>MAX</sub> Routing Delays |                |      |                |      |                |      |      |  |  |  |  |

|-----------------------------------------------------|----------------|------|----------------|------|----------------|------|------|--|--|--|--|

| Symbol                                              | -1 Speed Grade |      | -2 Speed Grade |      | -3 Speed Grade |      | Unit |  |  |  |  |

|                                                     | Min            | Max  | Min            | Max  | Min            | Max  |      |  |  |  |  |

| t <sub>F1-4</sub>                                   |                | 0.22 |                | 0.25 |                | 0.26 | ns   |  |  |  |  |

| t <sub>F5-20</sub>                                  |                | 1.26 |                | 1.39 |                | 1.52 | ns   |  |  |  |  |

| t <sub>F20+</sub>                                   |                | 3.51 |                | 3.88 |                | 4.26 | ns   |  |  |  |  |