# E·XFL

# Intel - EP20K160EQC240-3 Datasheet

Welcome to E-XFL.COM

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 640                                                         |

| Number of Logic Elements/Cells | 6400                                                        |

| Total RAM Bits                 | 81920                                                       |

| Number of I/O                  | 175                                                         |

| Number of Gates                | 404000                                                      |

| Voltage - Supply               | 1.71V ~ 1.89V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 240-BFQFP                                                   |

| Supplier Device Package        | 240-PQFP (32x32)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep20k160eqc240-3 |

|                                |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 5. APEX 20K FineLine BGA Package Options & I/O Count   Notes (1), (2) |         |         |         |                |           |  |

|-----------------------------------------------------------------------------|---------|---------|---------|----------------|-----------|--|

| Device                                                                      | 144 Pin | 324 Pin | 484 Pin | 672 Pin        | 1,020 Pin |  |

| EP20K30E                                                                    | 93      | 128     |         |                |           |  |

| EP20K60E                                                                    | 93      | 196     |         |                |           |  |

| EP20K100                                                                    |         | 252     |         |                |           |  |

| EP20K100E                                                                   | 93      | 246     |         |                |           |  |

| EP20K160E                                                                   |         |         | 316     |                |           |  |

| EP20K200                                                                    |         |         | 382     |                |           |  |

| EP20K200E                                                                   |         |         | 376     | 376            |           |  |

| EP20K300E                                                                   |         |         |         | 408            |           |  |

| EP20K400                                                                    |         |         |         | 502 <i>(3)</i> |           |  |

| EP20K400E                                                                   |         |         |         | 488 <i>(3)</i> |           |  |

| EP20K600E                                                                   |         |         |         | 508 <i>(3)</i> | 588       |  |

| EP20K1000E                                                                  |         |         |         | 508 <i>(3)</i> | 708       |  |

| EP20K1500E                                                                  |         |         |         |                | 808       |  |

### Notes to Tables 4 and 5:

Г

- (1) I/O counts include dedicated input and clock pins.

- (2) APEX 20K device package types include thin quad flat pack (TQFP), plastic quad flat pack (PQFP), power quad flat pack (RQFP), 1.27-mm pitch ball-grid array (BGA), 1.00-mm pitch FineLine BGA, and pin-grid array (PGA) packages.

- (3) This device uses a thermally enhanced package, which is taller than the regular package. Consult the *Altera Device Package Information Data Sheet* for detailed package size information.

| Table 6. APEX 20K QFP, BGA & PGA Package Sizes                                                   |              |             |             |             |             |             |  |

|--------------------------------------------------------------------------------------------------|--------------|-------------|-------------|-------------|-------------|-------------|--|

| Feature                                                                                          | 144-Pin TQFP | 208-Pin QFP | 240-Pin QFP | 356-Pin BGA | 652-Pin BGA | 655-Pin PGA |  |

| Pitch (mm)                                                                                       | 0.50         | 0.50        | 0.50        | 1.27        | 1.27        | -           |  |

| Area (mm <sup>2</sup> )                                                                          | 484          | 924         | 1,218       | 1,225       | 2,025       | 3,906       |  |

| $\begin{array}{l} \text{Length} \times \text{Width} \\ \text{(mm} \times \text{mm)} \end{array}$ | 22 × 22      | 30.4 × 30.4 | 34.9×34.9   | 35 × 35     | 45 × 45     | 62.5 × 62.5 |  |

| Table 7. APEX 20K FineLine BGA Package Sizes                      |         |         |         |         |           |  |

|-------------------------------------------------------------------|---------|---------|---------|---------|-----------|--|

| Feature                                                           | 144 Pin | 324 Pin | 484 Pin | 672 Pin | 1,020 Pin |  |

| Pitch (mm)                                                        | 1.00    | 1.00    | 1.00    | 1.00    | 1.00      |  |

| Area (mm <sup>2</sup> )                                           | 169     | 361     | 529     | 729     | 1,089     |  |

| $\text{Length} \times \text{Width} \text{ (mm} \times \text{mm)}$ | 13 × 13 | 19×19   | 23 × 23 | 27 × 27 | 33 × 33   |  |

1

# Functional Description

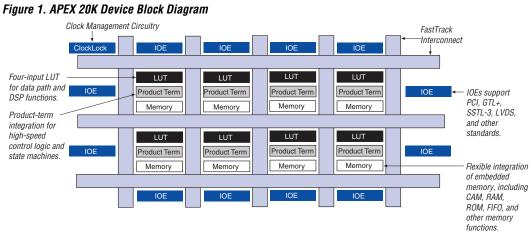

APEX 20K devices incorporate LUT-based logic, product-term-based logic, and memory into one device. Signal interconnections within APEX 20K devices (as well as to and from device pins) are provided by the FastTrack<sup>®</sup> Interconnect—a series of fast, continuous row and column channels that run the entire length and width of the device.

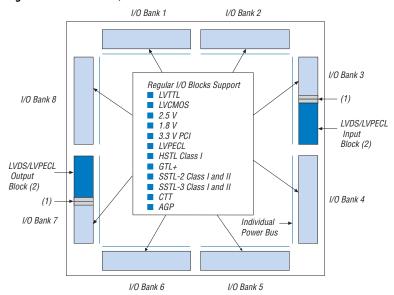

Each I/O pin is fed by an I/O element (IOE) located at the end of each row and column of the FastTrack Interconnect. Each IOE contains a bidirectional I/O buffer and a register that can be used as either an input or output register to feed input, output, or bidirectional signals. When used with a dedicated clock pin, these registers provide exceptional performance. IOEs provide a variety of features, such as 3.3-V, 64-bit, 66-MHz PCI compliance; JTAG BST support; slew-rate control; and tri-state buffers. APEX 20KE devices offer enhanced I/O support, including support for 1.8-V I/O, 2.5-V I/O, LVCMOS, LVTTL, LVPECL, 3.3-V PCI, PCI-X, LVDS, GTL+, SSTL-2, SSTL-3, HSTL, CTT, and 3.3-V AGP I/O standards.

The ESB can implement a variety of memory functions, including CAM, RAM, dual-port RAM, ROM, and FIFO functions. Embedding the memory directly into the die improves performance and reduces die area compared to distributed-RAM implementations. Moreover, the abundance of cascadable ESBs ensures that the APEX 20K device can implement multiple wide memory blocks for high-density designs. The ESB's high speed ensures it can implement small memory blocks without any speed penalty. The abundance of ESBs ensures that designers can create as many different-sized memory blocks as the system requires. Figure 1 shows an overview of the APEX 20K device.

# **Logic Array Block**

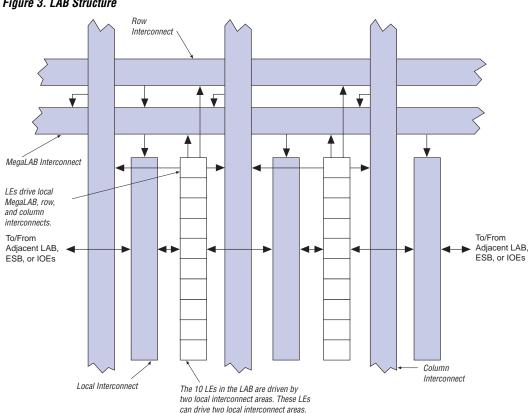

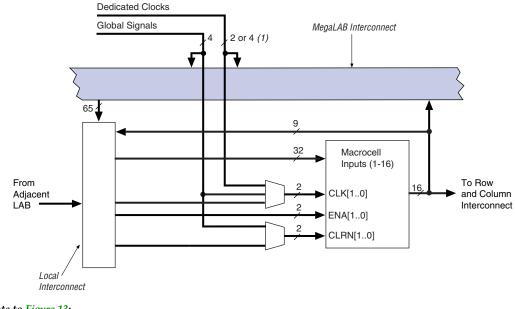

Each LAB consists of 10 LEs, the LEs' associated carry and cascade chains, LAB control signals, and the local interconnect. The local interconnect transfers signals between LEs in the same or adjacent LABs, IOEs, or ESBs. The Quartus II Compiler places associated logic within an LAB or adjacent LABs, allowing the use of a fast local interconnect for high performance. Figure 3 shows the APEX 20K LAB.

APEX 20K devices use an interleaved LAB structure. This structure allows each LE to drive two local interconnect areas. This feature minimizes use of the MegaLAB and FastTrack interconnect, providing higher performance and flexibility. Each LE can drive 29 other LEs through the fast local interconnect.

### Cascade Chain

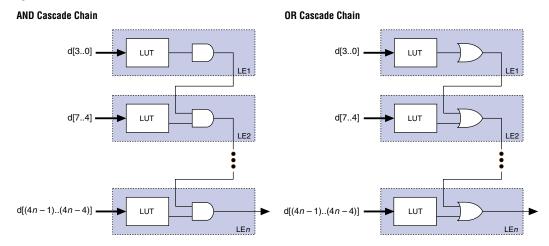

With the cascade chain, the APEX 20K architecture can implement functions with a very wide fan-in. Adjacent LUTs can compute portions of a function in parallel; the cascade chain serially connects the intermediate values. The cascade chain can use a logical AND or logical OR (via De Morgan's inversion) to connect the outputs of adjacent LEs. Each additional LE provides four more inputs to the effective width of a function, with a short cascade delay. Cascade chain logic can be created automatically by the Quartus II software Compiler during design processing, or manually by the designer during design entry.

Cascade chains longer than ten LEs are implemented automatically by linking LABs together. For enhanced fitting, a long cascade chain skips alternate LABs in a MegaLAB structure. A cascade chain longer than one LAB skips either from an even-numbered LAB to the next even-numbered LAB, or from an odd-numbered LAB to the next odd-numbered LAB. For example, the last LE of the first LAB in the upper-left MegaLAB structure carries to the first LE of the third LAB in the MegaLAB structure. Figure 7 shows how the cascade function can connect adjacent LEs to form functions with a wide fan-in.

Figure 7. APEX 20K Cascade Chain

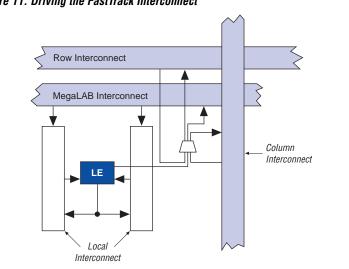

Figure 11 shows the intersection of a row and column interconnect, and how these forms of interconnects and LEs drive each other.

Figure 11. Driving the FastTrack Interconnect

APEX 20KE devices include an enhanced interconnect structure for faster routing of input signals with high fan-out. Column I/O pins can drive the FastRow<sup>™</sup> interconnect, which routes signals directly into the local interconnect without having to drive through the MegaLAB interconnect. FastRow lines traverse two MegaLAB structures. Also, these pins can drive the local interconnect directly for fast setup times. On EP20K300E and larger devices, the FastRow interconnect drives the two MegaLABs in the top left corner, the two MegaLABs in the top right corner, the two MegaLABS in the bottom left corner, and the two MegaLABs in the bottom right corner. On EP20K200E and smaller devices, FastRow interconnect drives the two MegaLABs on the top and the two MegaLABs on the bottom of the device. On all devices, the FastRow interconnect drives all local interconnect in the appropriate MegaLABs except the local interconnect on the side of the MegaLAB opposite the ESB. Pins using the FastRow interconnect achieve a faster set-up time, as the signal does not need to use a MegaLAB interconnect line to reach the destination LE. Figure 12 shows the FastRow interconnect.

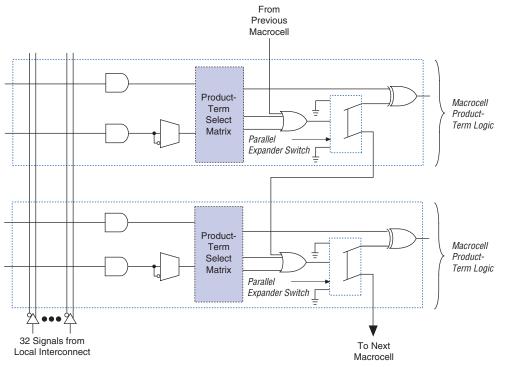

#### Figure 13. Product-Term Logic in ESB

# Note to Figure 13:

(1) APEX 20KE devices have four dedicated clocks.

### Macrocells

APEX 20K macrocells can be configured individually for either sequential or combinatorial logic operation. The macrocell consists of three functional blocks: the logic array, the product-term select matrix, and the programmable register.

Combinatorial logic is implemented in the product terms. The productterm select matrix allocates these product terms for use as either primary logic inputs (to the OR and XOR gates) to implement combinatorial functions, or as parallel expanders to be used to increase the logic available to another macrocell. One product term can be inverted; the Quartus II software uses this feature to perform DeMorgan's inversion for more efficient implementation of wide OR functions. The Quartus II software Compiler can use a NOT-gate push-back technique to emulate an asynchronous preset. Figure 14 shows the APEX 20K macrocell.

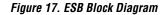

# Embedded System Block

The ESB can implement various types of memory blocks, including dual-port RAM, ROM, FIFO, and CAM blocks. The ESB includes input and output registers; the input registers synchronize writes, and the output registers can pipeline designs to improve system performance. The ESB offers a dual-port mode, which supports simultaneous reads and writes at two different clock frequencies. Figure 17 shows the ESB block diagram.

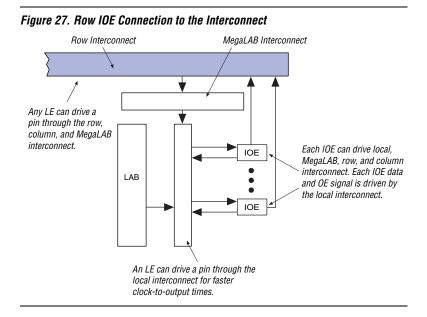

Each IOE drives a row, column, MegaLAB, or local interconnect when used as an input or bidirectional pin. A row IOE can drive a local, MegaLAB, row, and column interconnect; a column IOE can drive the column interconnect. Figure 27 shows how a row IOE connects to the interconnect.

#### Figure 29. APEX 20KE I/O Banks

#### Notes to Figure 29:

- For more information on placing I/O pins in LVDS blocks, refer to the Guidelines for Using LVDS Blocks section in Application Note 120 (Using LVDS in APEX 20KE Devices).

- (2) If the LVDS input and output blocks are not used for LVDS, they can support all of the I/O standards and can be used as input, output, or bidirectional pins with V<sub>CCIO</sub> set to 3.3 V, 2.5 V, or 1.8 V.

# Power Sequencing & Hot Socketing

Because APEX 20K and APEX 20KE devices can be used in a mixedvoltage environment, they have been designed specifically to tolerate any possible power-up sequence. Therefore, the  $V_{CCIO}$  and  $V_{CCINT}$  power supplies may be powered in any order.

For more information, please refer to the "Power Sequencing Considerations" section in the *Configuring APEX 20KE & APEX 20KC Devices* chapter of the *Configuration Devices Handbook*.

Signals can be driven into APEX 20K devices before and during power-up without damaging the device. In addition, APEX 20K devices do not drive out during power-up. Once operating conditions are reached and the device is configured, APEX 20K and APEX 20KE devices operate as specified by the user.

For designs that require both a multiplied and non-multiplied clock, the clock trace on the board can be connected to CLK2p. Table 14 shows the combinations supported by the ClockLock and ClockBoost circuitry. The CLK2p pin can feed both the ClockLock and ClockBoost circuitry in the APEX 20K device. However, when both circuits are used, the other clock pin (CLK1p) cannot be used.

| Table 14. Multiplication Factor Combinations |    |  |  |  |

|----------------------------------------------|----|--|--|--|

| Clock 1 Clock 2                              |    |  |  |  |

| ×1                                           | ×1 |  |  |  |

| ×1, ×2                                       | ×2 |  |  |  |

| ×1, ×2, ×4                                   | ×4 |  |  |  |

# APEX 20KE ClockLock Feature

APEX 20KE devices include an enhanced ClockLock feature set. These devices include up to four PLLs, which can be used independently. Two PLLs are designed for either general-purpose use or LVDS use (on devices that support LVDS I/O pins). The remaining two PLLs are designed for general-purpose use. The EP20K200E and smaller devices have two PLLs; the EP20K300E and larger devices have four PLLs.

The following sections describe some of the features offered by the APEX 20KE PLLs.

# External PLL Feedback

The ClockLock circuit's output can be driven off-chip to clock other devices in the system; further, the feedback loop of the PLL can be routed off-chip. This feature allows the designer to exercise fine control over the I/O interface between the APEX 20KE device and another high-speed device, such as SDRAM.

# Clock Multiplication

The APEX 20KE ClockBoost circuit can multiply or divide clocks by a programmable number. The clock can be multiplied by  $m/(n \times k)$  or  $m/(n \times v)$ , where *m* and *k* range from 2 to 160, and *n* and *v* range from 1 to 16. Clock multiplication and division can be used for time-domain multiplexing and other functions, which can reduce design LE requirements.

| Symbol                | Parameter                                                           | Min | Max | Unit |

|-----------------------|---------------------------------------------------------------------|-----|-----|------|

| t <sub>SKEW</sub>     | Skew delay between related<br>ClockLock/ClockBoost-generated clocks |     | 500 | ps   |

| JITTER                | Jitter on ClockLock/ClockBoost-generated clock (5)                  |     | 200 | ps   |

| t <sub>INCLKSTB</sub> | Input clock stability (measured between adjacent clocks)            |     | 50  | ps   |

Notes to Table 15:

- (1) The PLL input frequency range for the EP20K100-1X device for 1x multiplication is 25 MHz to 175 MHz.

- (2) All input clock specifications must be met. The PLL may not lock onto an incoming clock if the clock specifications are not met, creating an erroneous clock within the device.

- (3) During device configuration, the ClockLock and ClockBoost circuitry is configured first. If the incoming clock is supplied during configuration, the ClockLock and ClockBoost circuitry locks during configuration, because the lock time is less than the configuration time.

- (4) The jitter specification is measured under long-term observation.

- (5) If the input clock stability is 100 ps,  $t_{JITTER}$  is 250 ps.

# Table 16 summarizes the APEX 20K ClockLock and ClockBoost parameters for -2 speed grade devices.

| Symbol                | Parameter                                                                                                                  | Min | Max        | Unit |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------|-----|------------|------|

| f <sub>out</sub>      | Output frequency                                                                                                           | 25  | 170        | MHz  |

| f <sub>CLK1</sub>     | Input clock frequency (ClockBoost clock multiplication factor equals 1)                                                    | 25  | 170        | MHz  |

| f <sub>CLK2</sub>     | Input clock frequency (ClockBoost clock multiplication 16 80 factor equals 2)                                              |     | MHz        |      |

| f <sub>CLK4</sub>     | Input clock frequency (ClockBoost clock multiplication factor equals 4)                                                    | 10  | 34         | MHz  |

| t <sub>OUTDUTY</sub>  | Duty cycle for ClockLock/ClockBoost-generated clock                                                                        | 40  | 60         | %    |

| f <sub>CLKDEV</sub>   | Input deviation from user specification in the Quartus II software (ClockBoost clock multiplication factor equals one) (1) |     | 25,000 (2) | PPM  |

| t <sub>R</sub>        | Input rise time                                                                                                            |     | 5          | ns   |

| t <sub>F</sub>        | Input fall time                                                                                                            |     | 5          | ns   |

| t <sub>LOCK</sub>     | Time required for ClockLock/ ClockBoost to acquire lock (3)                                                                |     | 10         | μs   |

| t <sub>SKEW</sub>     | Skew delay between related ClockLock/ ClockBoost-<br>generated clock                                                       | 500 | 500        | ps   |

| t <sub>JITTER</sub>   | Jitter on ClockLock/ ClockBoost-generated clock (4)                                                                        |     | 200        | ps   |

| t <sub>INCLKSTB</sub> | Input clock stability (measured between adjacent clocks)                                                                   |     | 50         | ps   |

# Table 16. APEX 20K ClockLock & ClockBoost Parameters for -2 Speed Grade Devices

| Device     |                     | <b>IDCODE (32 Bits)</b> (1) |                                    |                      |  |  |  |  |

|------------|---------------------|-----------------------------|------------------------------------|----------------------|--|--|--|--|

|            | Version<br>(4 Bits) | Part Number (16 Bits)       | Manufacturer<br>Identity (11 Bits) | <b>1 (1 Bit)</b> (2) |  |  |  |  |

| EP20K30E   | 0000                | 1000 0000 0011 0000         | 000 0110 1110                      | 1                    |  |  |  |  |

| EP20K60E   | 0000                | 1000 0000 0110 0000         | 000 0110 1110                      | 1                    |  |  |  |  |

| EP20K100   | 0000                | 0000 0100 0001 0110         | 000 0110 1110                      | 1                    |  |  |  |  |

| EP20K100E  | 0000                | 1000 0001 0000 0000         | 000 0110 1110                      | 1                    |  |  |  |  |

| EP20K160E  | 0000                | 1000 0001 0110 0000         | 000 0110 1110                      | 1                    |  |  |  |  |

| EP20K200   | 0000                | 0000 1000 0011 0010         | 000 0110 1110                      | 1                    |  |  |  |  |

| EP20K200E  | 0000                | 1000 0010 0000 0000         | 000 0110 1110                      | 1                    |  |  |  |  |

| EP20K300E  | 0000                | 1000 0011 0000 0000         | 000 0110 1110                      | 1                    |  |  |  |  |

| EP20K400   | 0000                | 0001 0110 0110 0100         | 000 0110 1110                      | 1                    |  |  |  |  |

| EP20K400E  | 0000                | 1000 0100 0000 0000         | 000 0110 1110                      | 1                    |  |  |  |  |

| EP20K600E  | 0000                | 1000 0110 0000 0000         | 000 0110 1110                      | 1                    |  |  |  |  |

| EP20K1000E | 0000                | 1001 0000 0000 0000         | 000 0110 1110                      | 1                    |  |  |  |  |

#### - -- -\_ \_ .

Notes to Table 21:

The most significant bit (MSB) is on the left. (1)

(2) The IDCODE's least significant bit (LSB) is always 1.

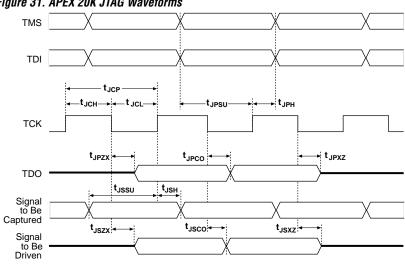

# Figure 31 shows the timing requirements for the JTAG signals.

**Altera Corporation**

| Table 26. APEX 20K 5.0-V Tolerant Device Capacitance   Notes (2), (14) |                                          |                                     |     |     |      |  |  |  |

|------------------------------------------------------------------------|------------------------------------------|-------------------------------------|-----|-----|------|--|--|--|

| Symbol                                                                 | Parameter                                | Conditions                          | Min | Мах | Unit |  |  |  |

| C <sub>IN</sub>                                                        | Input capacitance                        | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 8   | pF   |  |  |  |

| C <sub>INCLK</sub>                                                     | Input capacitance on dedicated clock pin | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 12  | pF   |  |  |  |

| C <sub>OUT</sub>                                                       | Output capacitance                       | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 8   | pF   |  |  |  |

#### Notes to Tables 23 through 26:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- All APEX 20K devices are 5.0-V tolerant. (2)

- (3) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to 5.75 V for input currents less than 100 mA and periods shorter than 20 ns.

- Numbers in parentheses are for industrial-temperature-range devices. (4)

- Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically. (5)

- All pins, including dedicated inputs, clock I/O, and JTAG pins, may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are (6) powered.

- (7)Typical values are for  $T_A = 25^{\circ}$  C,  $V_{CCINT} = 2.5$  V, and  $V_{CCIO} = 2.5$  or 3.3 V.

- These values are specified in the APEX 20K device recommended operating conditions, shown in Table 26 on (8)page 62.

- (9) The APEX 20K input buffers are compatible with 2.5-V and 3.3-V (LVTTL and LVCMOS) signals. Additionally, the input buffers are 3.3-V PCI compliant when V<sub>CCIO</sub> and V<sub>CCINT</sub> meet the relationship shown in Figure 33 on page 68.

- (10) The I<sub>OH</sub> parameter refers to high-level TTL, PCI or CMOS output current.

- (11) The I<sub>OL</sub> parameter refers to low-level TTL, PCI, or CMOS output current. This parameter applies to open-drain pins as well as output pins.

- (12) This value is specified for normal device operation. The value may vary during power-up.

- (13) Pin pull-up resistance values will be lower if an external source drives the pin higher than  $V_{CCIO}$ .

- (14) Capacitance is sample-tested only.

Tables 27 through 30 provide information on absolute maximum ratings, recommended operating conditions, DC operating conditions, and capacitance for 1.8-V APEX 20KE devices.

| Symbol             | Parameter                  | Conditions                                        | Min  | Max | Unit |

|--------------------|----------------------------|---------------------------------------------------|------|-----|------|

| V <sub>CCINT</sub> | Supply voltage             | With respect to ground (2)                        | -0.5 | 2.5 | V    |

| V <sub>CCIO</sub>  |                            |                                                   | -0.5 | 4.6 | V    |

| VI                 | DC input voltage           |                                                   | -0.5 | 4.6 | V    |

| I <sub>OUT</sub>   | DC output current, per pin |                                                   | -25  | 25  | mA   |

| T <sub>STG</sub>   | Storage temperature        | No bias                                           | -65  | 150 | °C   |

| T <sub>AMB</sub>   | Ambient temperature        | Under bias                                        | -65  | 135 | °C   |

| ΤJ                 | Junction temperature       | PQFP, RQFP, TQFP, and BGA packages,<br>under bias |      | 135 | °C   |

|                    |                            | Ceramic PGA packages, under bias                  |      | 150 | °C   |

| Table 28. APEX 20KE Device Recommended Operating Conditions |                                                     |                    |                  |                   |      |  |  |

|-------------------------------------------------------------|-----------------------------------------------------|--------------------|------------------|-------------------|------|--|--|

| Symbol                                                      | Parameter                                           | Conditions         | Min              | Max               | Unit |  |  |

| V <sub>CCINT</sub>                                          | Supply voltage for internal logic and input buffers | (3), (4)           | 1.71 (1.71)      | 1.89 (1.89)       | V    |  |  |

| V <sub>CCIO</sub>                                           | Supply voltage for output buffers, 3.3-V operation  | (3), (4)           | 3.00 (3.00)      | 3.60 (3.60)       | V    |  |  |

|                                                             | Supply voltage for output buffers, 2.5-V operation  | (3), (4)           | 2.375<br>(2.375) | 2.625<br>(2.625)  | V    |  |  |

|                                                             | Supply voltage for output buffers, 1.8-V operation  | (3), (4)           | 1.71 (1.71)      | 1.89 (1.89)       | V    |  |  |

| VI                                                          | Input voltage                                       | (5), (6)           | -0.5             | 4.0               | V    |  |  |

| Vo                                                          | Output voltage                                      |                    | 0                | V <sub>CCIO</sub> | V    |  |  |

| ТJ                                                          | Junction temperature                                | For commercial use | 0                | 85                | °C   |  |  |

|                                                             |                                                     | For industrial use | -40              | 100               | °C   |  |  |

| t <sub>R</sub>                                              | Input rise time                                     |                    |                  | 40                | ns   |  |  |

| t <sub>F</sub>                                              | Input fall time                                     |                    |                  | 40                | ns   |  |  |

P

For DC Operating Specifications on APEX 20KE I/O standards, please refer to *Application Note 117 (Using Selectable I/O Standards in Altera Devices).*

| Table 30. APEX 20KE Device Capacitance Note (15) |                                             |                                     |     |     |      |  |  |

|--------------------------------------------------|---------------------------------------------|-------------------------------------|-----|-----|------|--|--|

| Symbol                                           | Parameter                                   | Conditions                          | Min | Max | Unit |  |  |

| C <sub>IN</sub>                                  | Input capacitance                           | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 8   | pF   |  |  |

| CINCLK                                           | Input capacitance on<br>dedicated clock pin | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 12  | pF   |  |  |

| C <sub>OUT</sub>                                 | Output capacitance                          | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 8   | pF   |  |  |

#### Notes to Tables 27 through 30:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to 5.75 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Numbers in parentheses are for industrial-temperature-range devices.

- (4) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically.

- (5) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to the voltage shown in the following table based on input duty cycle for input currents less than 100 mA. The overshoot is dependent upon duty cycle of the signal. The DC case is equivalent to 100% duty cycle.

| Vin  | Max. Duty Cycle |

|------|-----------------|

| 4.0V | 100% (DC)       |

| 4.1  | 90%             |

- 4.2 50%

- 4.3 30%

- 4.4 17%

- 4.5 10%

- (6) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are powered.

- (7) Typical values are for  $T_A = 25^\circ$  C,  $V_{CCINT} = 1.8$  V, and  $V_{CCIO} = 1.8$  V, 2.5 V or 3.3 V.

- (8) These values are specified under the APEX 20KE device recommended operating conditions, shown in Table 24 on page 60.

- (9) Refer to Application Note 117 (Using Selectable I/O Standards in Altera Devices) for the V<sub>IH</sub>, V<sub>IL</sub>, V<sub>OH</sub>, V<sub>OL</sub>, and I<sub>I</sub> parameters when VCCIO = 1.8 V.

- (10) The APEX 20KE input buffers are compatible with 1.8-V, 2.5-V and 3.3-V (LVTTL and LVCMOS) signals. Additionally, the input buffers are 3.3-V PCI compliant. Input buffers also meet specifications for GTL+, CTT, AGP, SSTL-2, SSTL-3, and HSTL.

- (11) The I<sub>OH</sub> parameter refers to high-level TTL, PCI, or CMOS output current.

- (12) The I<sub>OL</sub> parameter refers to low-level TTL, PCI, or CMOS output current. This parameter applies to open-drain pins as well as output pins.

- (13) This value is specified for normal device operation. The value may vary during power-up.

- (14) Pin pull-up resistance values will be lower if an external source drives the pin higher than V<sub>CCIO</sub>.

- (15) Capacitance is sample-tested only.

Figure 33 shows the relationship between  $\rm V_{CCIO}$  and  $\rm V_{CCINT}$  for 3.3-V PCI compliance on APEX 20K devices.

Tables 40 through 42 show the  $f_{MAX}$  timing parameters for EP20K100, EP20K200, and EP20K400 APEX 20K devices.

| Symbol                  | -1 Spee | d Grade | -2 Speed Grade |     | -3 Speed Grade |     | Units |  |

|-------------------------|---------|---------|----------------|-----|----------------|-----|-------|--|

|                         | Min     | Max     | Min            | Max | Min            | Max |       |  |

| t <sub>SU</sub>         | 0.5     |         | 0.6            |     | 0.8            |     | ns    |  |

| t <sub>H</sub>          | 0.7     |         | 0.8            |     | 1.0            |     | ns    |  |

| t <sub>CO</sub>         |         | 0.3     |                | 0.4 |                | 0.5 | ns    |  |

| t <sub>lut</sub>        |         | 0.8     |                | 1.0 |                | 1.3 | ns    |  |

| t <sub>ESBRC</sub>      |         | 1.7     |                | 2.1 |                | 2.4 | ns    |  |

| t <sub>ESBWC</sub>      |         | 5.7     |                | 6.9 |                | 8.1 | ns    |  |

| t <sub>ESBWESU</sub>    | 3.3     |         | 3.9            |     | 4.6            |     | ns    |  |

| t <sub>ESBDATASU</sub>  | 2.2     |         | 2.7            |     | 3.1            |     | ns    |  |

| t <sub>ESBDATAH</sub>   | 0.6     |         | 0.8            |     | 0.9            |     | ns    |  |

| t <sub>ESBADDRSU</sub>  | 2.4     |         | 2.9            |     | 3.3            |     | ns    |  |

| t <sub>ESBDATACO1</sub> |         | 1.3     |                | 1.6 |                | 1.8 | ns    |  |

| t <sub>ESBDATACO2</sub> |         | 2.6     |                | 3.1 |                | 3.6 | ns    |  |

| t <sub>ESBDD</sub>      |         | 2.5     |                | 3.3 |                | 3.6 | ns    |  |

| t <sub>PD</sub>         |         | 2.5     |                | 3.0 |                | 3.6 | ns    |  |

| <b>TERMSU</b>           | 2.3     |         | 2.6            |     | 3.2            |     | ns    |  |

| t <sub>PTERMCO</sub>    |         | 1.5     |                | 1.8 |                | 2.1 | ns    |  |

| t <sub>F1-4</sub>       |         | 0.5     |                | 0.6 |                | 0.7 | ns    |  |

| t <sub>F5-20</sub>      |         | 1.6     |                | 1.7 |                | 1.8 | ns    |  |

| t <sub>F20+</sub>       |         | 2.2     |                | 2.2 |                | 2.3 | ns    |  |

| t <sub>CH</sub>         | 2.0     |         | 2.5            |     | 3.0            |     | ns    |  |

| t <sub>CL</sub>         | 2.0     |         | 2.5            |     | 3.0            |     | ns    |  |

| t <sub>CLRP</sub>       | 0.3     |         | 0.4            |     | 0.4            |     | ns    |  |

| t <sub>PREP</sub>       | 0.5     |         | 0.5            |     | 0.5            |     | ns    |  |

| t <sub>ESBCH</sub>      | 2.0     |         | 2.5            |     | 3.0            |     | ns    |  |

| t <sub>ESBCL</sub>      | 2.0     |         | 2.5            |     | 3.0            |     | ns    |  |

| t <sub>ESBWP</sub>      | 1.6     |         | 1.9            |     | 2.2            |     | ns    |  |

| t <sub>ESBRP</sub>      | 1.0     |         | 1.3            |     | 1.4            |     | ns    |  |

| Symbol                        | -1 Spee | ed Grade | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|-------------------------------|---------|----------|----------------|-----|----------------|-----|------|

|                               | Min     | Max      | Min            | Мах | Min            | Мах |      |

| t <sub>INSU</sub> (1)         | 2.3     |          | 2.8            |     | 3.2            |     | ns   |

| t <sub>INH</sub> (1)          | 0.0     |          | 0.0            |     | 0.0            |     | ns   |

| t <sub>OUTCO</sub> (1)        | 2.0     | 4.5      | 2.0            | 4.9 | 2.0            | 6.6 | ns   |

| t <sub>INSU</sub> (2)         | 1.1     |          | 1.2            |     | -              |     | ns   |

| t <sub>INH</sub> (2)          | 0.0     |          | 0.0            |     | -              |     | ns   |

| t <sub>оитсо</sub> <i>(2)</i> | 0.5     | 2.7      | 0.5            | 3.1 | _              | 4.8 | ns   |

| Table 44. EP20K100 External Bidirectional Timing Parameters |                |     |                |     |                |     |      |  |  |  |

|-------------------------------------------------------------|----------------|-----|----------------|-----|----------------|-----|------|--|--|--|

| Symbol                                                      | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |  |  |  |

|                                                             | Min            | Max | Min            | Max | Min            | Max |      |  |  |  |

| t <sub>INSUBIDIR</sub> (1)                                  | 2.3            |     | 2.8            |     | 3.2            |     | ns   |  |  |  |

| t <sub>INHBIDIR</sub> (1)                                   | 0.0            |     | 0.0            |     | 0.0            |     | ns   |  |  |  |

| toutcobidir<br>(1)                                          | 2.0            | 4.5 | 2.0            | 4.9 | 2.0            | 6.6 | ns   |  |  |  |

| t <sub>XZBIDIR</sub> (1)                                    |                | 5.0 |                | 5.9 |                | 6.9 | ns   |  |  |  |

| t <sub>ZXBIDIR</sub> (1)                                    |                | 5.0 |                | 5.9 |                | 6.9 | ns   |  |  |  |

| t <sub>insubidir</sub> (2)                                  | 1.0            |     | 1.2            |     | -              |     | ns   |  |  |  |

| t <sub>INHBIDIR</sub> (2)                                   | 0.0            |     | 0.0            |     | -              |     | ns   |  |  |  |

| toutcobidir<br>(2)                                          | 0.5            | 2.7 | 0.5            | 3.1 | -              | -   | ns   |  |  |  |

| t <sub>XZBIDIR</sub> (2)                                    |                | 4.3 |                | 5.0 |                | -   | ns   |  |  |  |

| t <sub>ZXBIDIR</sub> (2)                                    |                | 4.3 |                | 5.0 |                | -   | ns   |  |  |  |

| Table 45. EP20K200 External Timing Parameters |         |          |                |     |                |     |      |  |  |  |  |

|-----------------------------------------------|---------|----------|----------------|-----|----------------|-----|------|--|--|--|--|

| Symbol                                        | -1 Spee | ed Grade | -2 Speed Grade |     | -3 Speed Grade |     | Unit |  |  |  |  |

|                                               | Min     | Max      | Min            | Max | Min            | Max |      |  |  |  |  |

| t <sub>INSU</sub> (1)                         | 1.9     |          | 2.3            |     | 2.6            |     | ns   |  |  |  |  |

| t <sub>INH</sub> (1)                          | 0.0     |          | 0.0            |     | 0.0            |     | ns   |  |  |  |  |

| t <sub>OUTCO</sub> (1)                        | 2.0     | 4.6      | 2.0            | 5.6 | 2.0            | 6.8 | ns   |  |  |  |  |

| t <sub>INSU</sub> (2)                         | 1.1     |          | 1.2            |     | -              |     | ns   |  |  |  |  |

| t <sub>INH</sub> (2)                          | 0.0     |          | 0.0            |     | -              |     | ns   |  |  |  |  |

| t <sub>оитсо</sub> <i>(2)</i>                 | 0.5     | 2.7      | 0.5            | 3.1 | -              | -   | ns   |  |  |  |  |

| Symbol                  | -1   |      | -2   |      | -3   |      | Unit |

|-------------------------|------|------|------|------|------|------|------|

|                         | Min  | Max  | Min  | Max  | Min  | Max  | 1    |

| t <sub>ESBARC</sub>     |      | 1.83 |      | 2.57 |      | 3.79 | ns   |

| t <sub>ESBSRC</sub>     |      | 2.46 |      | 3.26 |      | 4.61 | ns   |

| t <sub>ESBAWC</sub>     |      | 3.50 |      | 4.90 |      | 7.23 | ns   |

| t <sub>ESBSWC</sub>     |      | 3.77 |      | 4.90 |      | 6.79 | ns   |

| t <sub>ESBWASU</sub>    | 1.59 |      | 2.23 |      | 3.29 |      | ns   |

| t <sub>ESBWAH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>ESBWDSU</sub>    | 1.75 |      | 2.46 |      | 3.62 |      | ns   |

| t <sub>ESBWDH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>ESBRASU</sub>    | 1.76 |      | 2.47 |      | 3.64 |      | ns   |

| t <sub>ESBRAH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>ESBWESU</sub>    | 1.68 |      | 2.49 |      | 3.87 |      | ns   |

| t <sub>ESBWEH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>ESBDATASU</sub>  | 0.08 |      | 0.43 |      | 1.04 |      | ns   |

| t <sub>ESBDATAH</sub>   | 0.13 |      | 0.13 |      | 0.13 |      | ns   |

| t <sub>ESBWADDRSU</sub> | 0.29 |      | 0.72 |      | 1.46 |      | ns   |

| t <sub>ESBRADDRSU</sub> | 0.36 |      | 0.81 |      | 1.58 |      | ns   |

| t <sub>ESBDATACO1</sub> |      | 1.06 |      | 1.24 |      | 1.55 | ns   |

| t <sub>ESBDATACO2</sub> |      | 2.39 |      | 3.35 |      | 4.94 | ns   |

| t <sub>ESBDD</sub>      |      | 3.50 |      | 4.90 |      | 7.23 | ns   |

| t <sub>PD</sub>         |      | 1.72 |      | 2.41 |      | 3.56 | ns   |

| <b>TERMSU</b>           | 0.99 |      | 1.56 |      | 2.55 |      | ns   |

| t <sub>PTERMCO</sub>    |      | 1.07 |      | 1.26 |      | 1.08 | ns   |

| Symbol                  | -1 Speed Grade |      | -2 Speed Grade |      | -3 Speed Grade |      | Unit |

|-------------------------|----------------|------|----------------|------|----------------|------|------|

|                         | Min            | Max  | Min            | Max  | Min            | Max  | 1    |

| t <sub>ESBARC</sub>     |                | 1.67 |                | 1.91 |                | 1.99 | ns   |

| t <sub>ESBSRC</sub>     |                | 2.30 |                | 2.66 |                | 2.93 | ns   |

| t <sub>ESBAWC</sub>     |                | 3.09 |                | 3.58 |                | 3.99 | ns   |

| t <sub>ESBSWC</sub>     |                | 3.01 |                | 3.65 |                | 4.05 | ns   |

| t <sub>ESBWASU</sub>    | 0.54           |      | 0.63           |      | 0.65           |      | ns   |

| t <sub>ESBWAH</sub>     | 0.36           |      | 0.43           |      | 0.42           |      | ns   |

| t <sub>ESBWDSU</sub>    | 0.69           |      | 0.77           |      | 0.84           |      | ns   |

| t <sub>ESBWDH</sub>     | 0.36           |      | 0.43           |      | 0.42           |      | ns   |

| t <sub>ESBRASU</sub>    | 1.61           |      | 1.77           |      | 1.86           |      | ns   |

| t <sub>ESBRAH</sub>     | 0.00           |      | 0.00           |      | 0.01           |      | ns   |

| t <sub>ESBWESU</sub>    | 1.35           |      | 1.47           |      | 1.61           |      | ns   |

| t <sub>ESBWEH</sub>     | 0.00           |      | 0.00           |      | 0.00           |      | ns   |

| t <sub>ESBDATASU</sub>  | -0.18          |      | -0.30          |      | -0.27          |      | ns   |

| t <sub>ESBDATAH</sub>   | 0.13           |      | 0.13           |      | 0.13           |      | ns   |

| t <sub>ESBWADDRSU</sub> | -0.02          |      | -0.11          |      | -0.03          |      | ns   |

| t <sub>ESBRADDRSU</sub> | 0.06           |      | -0.01          |      | -0.05          |      | ns   |

| t <sub>ESBDATACO1</sub> |                | 1.16 |                | 1.40 |                | 1.54 | ns   |

| t <sub>ESBDATACO2</sub> |                | 2.18 |                | 2.55 |                | 2.85 | ns   |

| t <sub>ESBDD</sub>      |                | 2.73 |                | 3.17 |                | 3.58 | ns   |

| t <sub>PD</sub>         |                | 1.57 |                | 1.83 |                | 2.07 | ns   |

| t <sub>PTERMSU</sub>    | 0.92           |      | 0.99           |      | 1.18           |      | ns   |

| t <sub>PTERMCO</sub>    |                | 1.18 |                | 1.43 |                | 1.17 | ns   |

## APEX 20K Programmable Logic Device Family Data Sheet

| Table 99. EP2      | OK1000E f <sub>MAX</sub> | Routing Dela | ys     |          |         |         |      |

|--------------------|--------------------------|--------------|--------|----------|---------|---------|------|

| Symbol             | -1 Spee                  | d Grade      | -2 Spe | ed Grade | -3 Spee | d Grade | Unit |

|                    | Min                      | Max          | Min    | Max      | Min     | Max     |      |

| t <sub>F1-4</sub>  |                          | 0.27         |        | 0.27     |         | 0.27    | ns   |

| t <sub>F5-20</sub> |                          | 1.45         |        | 1.63     |         | 1.75    | ns   |

| t <sub>F20+</sub>  |                          | 4.15         |        | 4.33     |         | 4.97    | ns   |

| Symbol             | -1 Spee | d Grade | -2 Spee | -2 Speed Grade |      | -3 Speed Grade |    |  |

|--------------------|---------|---------|---------|----------------|------|----------------|----|--|

|                    | Min     | Max     | Min     | Max            | Min  | Max            | 1  |  |

| t <sub>CH</sub>    | 1.25    |         | 1.43    |                | 1.67 |                | ns |  |

| t <sub>CL</sub>    | 1.25    |         | 1.43    |                | 1.67 |                | ns |  |

| t <sub>CLRP</sub>  | 0.20    |         | 0.20    |                | 0.20 |                | ns |  |

| t <sub>PREP</sub>  | 0.20    |         | 0.20    |                | 0.20 |                | ns |  |

| t <sub>ESBCH</sub> | 1.25    |         | 1.43    |                | 1.67 |                | ns |  |

| t <sub>ESBCL</sub> | 1.25    |         | 1.43    |                | 1.67 |                | ns |  |

| t <sub>ESBWP</sub> | 1.28    |         | 1.51    |                | 1.65 |                | ns |  |

| t <sub>ESBRP</sub> | 1.11    |         | 1.29    |                | 1.41 |                | ns |  |

| Table 101. EP20K1000E External Timing Parameters |                |      |                |      |                |      |      |  |  |  |  |

|--------------------------------------------------|----------------|------|----------------|------|----------------|------|------|--|--|--|--|

| Symbol                                           | -1 Speed Grade |      | -2 Speed Grade |      | -3 Speed Grade |      | Unit |  |  |  |  |

|                                                  | Min            | Max  | Min            | Max  | Min            | Max  |      |  |  |  |  |

| t <sub>INSU</sub>                                | 2.70           |      | 2.84           |      | 2.97           |      | ns   |  |  |  |  |

| t <sub>INH</sub>                                 | 0.00           |      | 0.00           |      | 0.00           |      | ns   |  |  |  |  |

| t <sub>outco</sub>                               | 2.00           | 5.75 | 2.00           | 6.33 | 2.00           | 6.90 | ns   |  |  |  |  |

| t <sub>INSUPLL</sub>                             | 1.64           |      | 2.09           |      | -              |      | ns   |  |  |  |  |

| t <sub>INHPLL</sub>                              | 0.00           |      | 0.00           |      | -              |      | ns   |  |  |  |  |

| t <sub>outcopll</sub>                            | 0.50           | 2.25 | 0.50           | 2.99 | -              | -    | ns   |  |  |  |  |