Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 832                                                         |

| Number of Logic Elements/Cells | 8320                                                        |

| Total RAM Bits                 | 106496                                                      |

| Number of I/O                  | 376                                                         |

| Number of Gates                | 526000                                                      |

| Voltage - Supply               | 1.71V ~ 1.89V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 484-BBGA                                                    |

| Supplier Device Package        | 484-FBGA (23x23)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep20k200efc484-1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 2. Additiona    | al APEX 20K De | vice Features | Note (1)  |           |            |            |

|-----------------------|----------------|---------------|-----------|-----------|------------|------------|

| Feature               | EP20K300E      | EP20K400      | EP20K400E | EP20K600E | EP20K1000E | EP20K1500E |

| Maximum system gates  | 728,000        | 1,052,000     | 1,052,000 | 1,537,000 | 1,772,000  | 2,392,000  |

| Typical gates         | 300,000        | 400,000       | 400,000   | 600,000   | 1,000,000  | 1,500,000  |

| LEs                   | 11,520         | 16,640        | 16,640    | 24,320    | 38,400     | 51,840     |

| ESBs                  | 72             | 104           | 104       | 152       | 160        | 216        |

| Maximum<br>RAM bits   | 147,456        | 212,992       | 212,992   | 311,296   | 327,680    | 442,368    |

| Maximum macrocells    | 1,152          | 1,664         | 1,664     | 2,432     | 2,560      | 3,456      |

| Maximum user I/O pins | 408            | 502           | 488       | 588       | 708        | 808        |

#### Note to Tables 1 and 2:

(1) The embedded IEEE Std. 1149.1 Joint Test Action Group (JTAG) boundary-scan circuitry contributes up to 57,000 additional gates.

# Additional Features

- Designed for low-power operation

- 1.8-V and 2.5-V supply voltage (see Table 3)

- MultiVolt<sup>TM</sup> I/O interface support to interface with 1.8-V, 2.5-V, 3.3-V, and 5.0-V devices (see Table 3)

- ESB offering programmable power-saving mode

| Feature                                                     |                                  | Device                                                                                   |

|-------------------------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------|

|                                                             | EP20K100<br>EP20K200<br>EP20K400 | EP20K30E EP20K60E EP20K100E EP20K160E EP20K200E EP20K300E EP20K400E EP20K600E EP20K1000E |

| Internal supply voltage (V <sub>CCINT</sub> )               | 2.5 V                            | 1.8 V                                                                                    |

| MultiVolt I/O interface voltage levels (V <sub>CCIO</sub> ) | 2.5 V, 3.3 V, 5.0 V              | 1.8 V, 2.5 V, 3.3 V, 5.0 V (1)                                                           |

Note to Table 3:

(1) APEX 20KE devices can be 5.0-V tolerant by using an external resistor.

# Functional Description

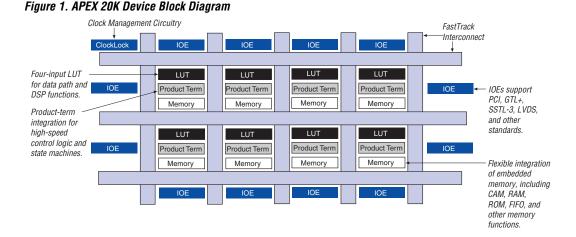

APEX 20K devices incorporate LUT-based logic, product-term-based logic, and memory into one device. Signal interconnections within APEX 20K devices (as well as to and from device pins) are provided by the FastTrack<sup>®</sup> Interconnect—a series of fast, continuous row and column channels that run the entire length and width of the device.

Each I/O pin is fed by an I/O element (IOE) located at the end of each row and column of the FastTrack Interconnect. Each IOE contains a bidirectional I/O buffer and a register that can be used as either an input or output register to feed input, output, or bidirectional signals. When used with a dedicated clock pin, these registers provide exceptional performance. IOEs provide a variety of features, such as 3.3-V, 64-bit, 66-MHz PCI compliance; JTAG BST support; slew-rate control; and tri-state buffers. APEX 20KE devices offer enhanced I/O support, including support for 1.8-V I/O, 2.5-V I/O, LVCMOS, LVTTL, LVPECL, 3.3-V PCI, PCI-X, LVDS, GTL+, SSTL-2, SSTL-3, HSTL, CTT, and 3.3-V AGP I/O standards.

The ESB can implement a variety of memory functions, including CAM, RAM, dual-port RAM, ROM, and FIFO functions. Embedding the memory directly into the die improves performance and reduces die area compared to distributed-RAM implementations. Moreover, the abundance of cascadable ESBs ensures that the APEX 20K device can implement multiple wide memory blocks for high-density designs. The ESB's high speed ensures it can implement small memory blocks without any speed penalty. The abundance of ESBs ensures that designers can create as many different-sized memory blocks as the system requires. Figure 1 shows an overview of the APEX 20K device.

Altera Corporation 9

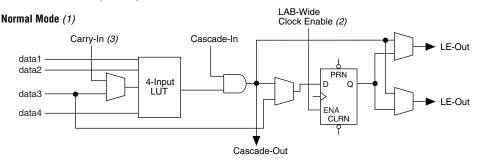

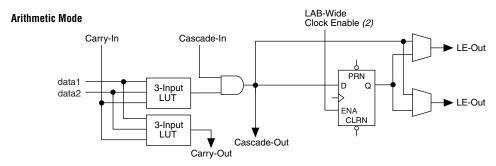

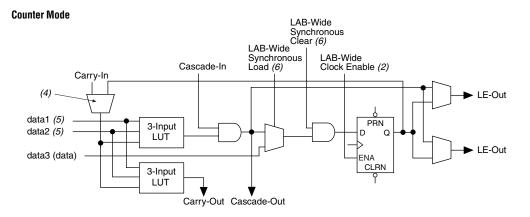

Figure 8. APEX 20K LE Operating Modes

### Notes to Figure 8:

- (1) LEs in normal mode support register packing.

- (2) There are two LAB-wide clock enables per LAB.

- (3) When using the carry-in in normal mode, the packed register feature is unavailable.

- (4) A register feedback multiplexer is available on LE1 of each LAB.

- (5) The DATA1 and DATA2 input signals can supply counter enable, up or down control, or register feedback signals for LEs other than the second LE in an LAB.

- (6) The LAB-wide synchronous clear and LAB wide synchronous load affect all registers in an LAB.

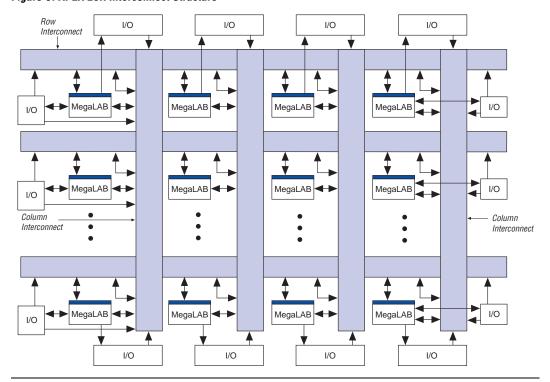

Figure 9. APEX 20K Interconnect Structure

A row line can be driven directly by LEs, IOEs, or ESBs in that row. Further, a column line can drive a row line, allowing an LE, IOE, or ESB to drive elements in a different row via the column and row interconnect. The row interconnect drives the MegaLAB interconnect to drive LEs, IOEs, or ESBs in a particular MegaLAB structure.

A column line can be directly driven by LEs, IOEs, or ESBs in that column. A column line on a device's left or right edge can also be driven by row IOEs. The column line is used to route signals from one row to another. A column line can drive a row line; it can also drive the MegaLAB interconnect directly, allowing faster connections between rows.

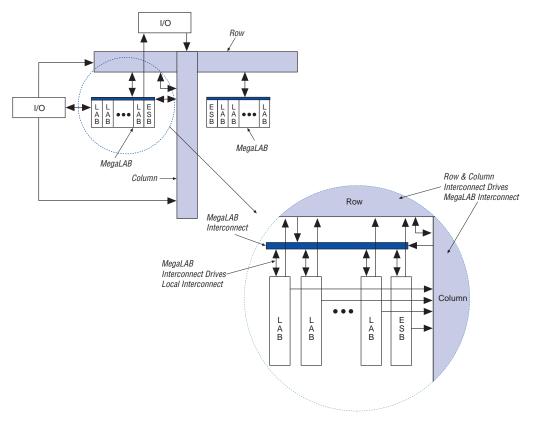

Figure 10 shows how the FastTrack Interconnect uses the local interconnect to drive LEs within MegaLAB structures.

Figure 10. FastTrack Connection to Local Interconnect

Select Vertical I/O Pins IOE IOE FastRow Interconnect IOE IOE Drive Local Interconnect FastRow Drives Local Interconnect and FastRow Interconnect in Two MegaLAB Structures Interconnect Local Interconnect LEs MegaLAB MegaLAB *LABs*

Figure 12. APEX 20KE FastRow Interconnect

Table 9 summarizes how various elements of the APEX 20K architecture drive each other.

ESBs can implement synchronous RAM, which is easier to use than asynchronous RAM. A circuit using asynchronous RAM must generate the RAM write enable (WE) signal, while ensuring that its data and address signals meet setup and hold time specifications relative to the WE signal. In contrast, the ESB's synchronous RAM generates its own WE signal and is self-timed with respect to the global clock. Circuits using the ESB's self-timed RAM must only meet the setup and hold time specifications of the global clock.

ESB inputs are driven by the adjacent local interconnect, which in turn can be driven by the MegaLAB or FastTrack Interconnect. Because the ESB can be driven by the local interconnect, an adjacent LE can drive it directly for fast memory access. ESB outputs drive the MegaLAB and FastTrack Interconnect. In addition, ten ESB outputs, nine of which are unique output lines, drive the local interconnect for fast connection to adjacent LEs or for fast feedback product-term logic.

When implementing memory, each ESB can be configured in any of the following sizes:  $128 \times 16$ ,  $256 \times 8$ ,  $512 \times 4$ ,  $1,024 \times 2$ , or  $2,048 \times 1$ . By combining multiple ESBs, the Quartus II software implements larger memory blocks automatically. For example, two  $128 \times 16$  RAM blocks can be combined to form a  $128 \times 32$  RAM block, and two  $512 \times 4$  RAM blocks can be combined to form a  $512 \times 8$  RAM block. Memory performance does not degrade for memory blocks up to 2,048 words deep. Each ESB can implement a 2,048-word-deep memory; the ESBs are used in parallel, eliminating the need for any external control logic and its associated delays.

To create a high-speed memory block that is more than 2,048 words deep, ESBs drive tri-state lines. Each tri-state line connects all ESBs in a column of MegaLAB structures, and drives the MegaLAB interconnect and row and column FastTrack Interconnect throughout the column. Each ESB incorporates a programmable decoder to activate the tri-state driver appropriately. For instance, to implement 8,192-word-deep memory, four ESBs are used. Eleven address lines drive the ESB memory, and two more drive the tri-state decoder. Depending on which 2,048-word memory page is selected, the appropriate ESB driver is turned on, driving the output to the tri-state line. The Quartus II software automatically combines ESBs with tri-state lines to form deeper memory blocks. The internal tri-state control logic is designed to avoid internal contention and floating lines. See Figure 18.

| Symbol                  | Parameter                                     | I/O Standard      | -1X Speed Grade |     | -2X Speed Grade |     | Units |

|-------------------------|-----------------------------------------------|-------------------|-----------------|-----|-----------------|-----|-------|

|                         |                                               |                   | Min             | Max | Min             | Max |       |

| f <sub>VCO</sub> (4)    | Voltage controlled oscillator operating range |                   | 200             | 500 | 200             | 500 | MHz   |

| f <sub>CLOCK0</sub>     | Clock0 PLL output frequency for internal use  |                   | 1.5             | 335 | 1.5             | 200 | MHz   |

| f <sub>CLOCK1</sub>     | Clock1 PLL output frequency for internal use  |                   | 20              | 335 | 20              | 200 | MHz   |

| f <sub>CLOCK0_EXT</sub> | Output clock frequency for                    | 3.3-V LVTTL       | 1.5             | 245 | 1.5             | 226 | MHz   |

| external clock0 outpu   | external clock0 output                        | 2.5-V LVTTL       | 1.5             | 234 | 1.5             | 221 | MHz   |

|                         |                                               | 1.8-V LVTTL       | 1.5             | 223 | 1.5             | 216 | MHz   |

|                         |                                               | GTL+              | 1.5             | 205 | 1.5             | 193 | MHz   |

|                         |                                               | SSTL-2 Class      | 1.5             | 158 | 1.5             | 157 | MHz   |

|                         |                                               | SSTL-2 Class      | 1.5             | 142 | 1.5             | 142 | MHz   |

|                         |                                               | SSTL-3 Class      | 1.5             | 166 | 1.5             | 162 | MHz   |

|                         |                                               | SSTL-3 Class      | 1.5             | 149 | 1.5             | 146 | MHz   |

|                         |                                               | LVDS              | 1.5             | 420 | 1.5             | 350 | MHz   |

| f <sub>CLOCK1_EXT</sub> | Output clock frequency for                    | 3.3-V LVTTL       | 20              | 245 | 20              | 226 | MHz   |

|                         | external clock1 output                        | 2.5-V LVTTL       | 20              | 234 | 20              | 221 | MHz   |

|                         |                                               | 1.8-V LVTTL       | 20              | 223 | 20              | 216 | MHz   |

|                         |                                               | GTL+              | 20              | 205 | 20              | 193 | MHz   |

|                         |                                               | SSTL-2 Class<br>I | 20              | 158 | 20              | 157 | MHz   |

|                         |                                               | SSTL-2 Class      | 20              | 142 | 20              | 142 | MHz   |

|                         |                                               | SSTL-3 Class      | 20              | 166 | 20              | 162 | MHz   |

|                         |                                               | SSTL-3 Class      | 20              | 149 | 20              | 146 | MHz   |

|                         |                                               | LVDS              | 20              | 420 | 20              | 350 | MHz   |

| Symbol            | Parameter                                                                         | Conditions                                                                 | Min | Тур | Max                     | Unit |

|-------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----|-----|-------------------------|------|

| V <sub>OL</sub>   | 3.3-V low-level TTL output voltage                                                | I <sub>OL</sub> = 12 mA DC,<br>V <sub>CCIO</sub> = 3.00 V (11)             |     |     | 0.45                    | V    |

|                   | 3.3-V low-level CMOS output voltage                                               | I <sub>OL</sub> = 0.1 mA DC,<br>V <sub>CCIO</sub> = 3.00 V (11)            |     |     | 0.2                     | V    |

|                   | 3.3-V low-level PCI output voltage                                                | I <sub>OL</sub> = 1.5 mA DC,<br>V <sub>CCIO</sub> = 3.00 to 3.60 V<br>(11) |     |     | 0.1 × V <sub>CCIO</sub> | V    |

|                   | 2.5-V low-level output voltage                                                    | I <sub>OL</sub> = 0.1 mA DC,<br>V <sub>CCIO</sub> = 2.30 V (11)            |     |     | 0.2                     | ٧    |

|                   | I <sub>OL</sub> = 1 mA DC,<br>V <sub>CCIO</sub> = 2.30 V (11)                     |                                                                            |     | 0.4 | ٧                       |      |

|                   | I <sub>OL</sub> = 2 mA DC,<br>V <sub>CCIO</sub> = 2.30 V (11)                     |                                                                            |     | 0.7 | ٧                       |      |

| I <sub>I</sub>    | Input pin leakage current                                                         | $V_1 = 5.75 \text{ to } -0.5 \text{ V}$                                    | -10 |     | 10                      | μΑ   |

| I <sub>OZ</sub>   | Tri-stated I/O pin leakage current                                                | $V_O = 5.75 \text{ to } -0.5 \text{ V}$                                    | -10 |     | 10                      | μΑ   |

| I <sub>CC0</sub>  | V <sub>CC</sub> supply current (standby)<br>(All ESBs in power-down mode)         | V <sub>I</sub> = ground, no load, no toggling inputs, -1 speed grade (12)  |     | 10  |                         | mA   |

|                   | V <sub>I</sub> = ground, no load, no toggling inputs,<br>-2, -3 speed grades (12) |                                                                            | 5   |     | mA                      |      |

| R <sub>CONF</sub> | Value of I/O pin pull-up resistor                                                 | V <sub>CCIO</sub> = 3.0 V (13)                                             | 20  |     | 50                      | W    |

|                   | before and during configuration                                                   | V <sub>CCIO</sub> = 2.375 V (13)                                           | 30  |     | 80                      | W    |

For DC Operating Specifications on APEX 20KE I/O standards, please refer to *Application Note 117 (Using Selectable I/O Standards in Altera Devices).*

| Table 30. APEX 20KE Device Capacitance   Note (15) |                                          |                                     |     |     |      |  |  |  |

|----------------------------------------------------|------------------------------------------|-------------------------------------|-----|-----|------|--|--|--|

| Symbol                                             | Parameter                                | Conditions                          | Min | Max | Unit |  |  |  |

| C <sub>IN</sub>                                    | Input capacitance                        | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 8   | pF   |  |  |  |

| C <sub>INCLK</sub>                                 | Input capacitance on dedicated clock pin | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 12  | pF   |  |  |  |

| C <sub>OUT</sub>                                   | Output capacitance                       | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 8   | pF   |  |  |  |

#### Notes to Tables 27 through 30:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to 5.75 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Numbers in parentheses are for industrial-temperature-range devices.

- (4) Maximum V<sub>CC</sub> rise time is 100 ms, and V<sub>CC</sub> must rise monotonically.

- (5) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to the voltage shown in the following table based on input duty cycle for input currents less than 100 mA. The overshoot is dependent upon duty cycle of the signal. The DC case is equivalent to 100% duty cycle.

Vin Max. Duty Cycle 4.0V 100% (DC) 4.1 90% 4.2 50% 4.3 30% 4.4 17% 4.5 10%

- (6) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are powered.

- Typical values are for  $T_A = 25^{\circ}$  C,  $V_{CCINT} = 1.8$  V, and  $V_{CCIO} = 1.8$  V, 2.5 V or 3.3 V.

- (8) These values are specified under the APEX 20KE device recommended operating conditions, shown in Table 24 on page 60.

- (9) Refer to Application Note 117 (Using Selectable I/O Standards in Altera Devices) for the V<sub>IH</sub>, V<sub>IL</sub>, V<sub>OH</sub>, V<sub>OL</sub>, and I<sub>I</sub> parameters when VCCIO = 1.8 V.

- (10) The APEX 20KE input buffers are compatible with 1.8-V, 2.5-V and 3.3-V (LVTTL and LVCMOS) signals. Additionally, the input buffers are 3.3-V PCI compliant. Input buffers also meet specifications for GTL+, CTT, AGP, SSTL-2, SSTL-3, and HSTL.

- (11) The I<sub>OH</sub> parameter refers to high-level TTL, PCI, or CMOS output current.

- (12) The I<sub>OL</sub> parameter refers to low-level TTL, PCI, or CMOS output current. This parameter applies to open-drain pins as well as output pins.

- (13) This value is specified for normal device operation. The value may vary during power-up.

- (14) Pin pull-up resistance values will be lower if an external source drives the pin higher than V<sub>CCIO</sub>.

- (15) Capacitance is sample-tested only.

Figure 33 shows the relationship between  $V_{CCIO}$  and  $V_{CCINT}$  for 3.3-V PCI compliance on APEX 20K devices.

8

4 2

0.5

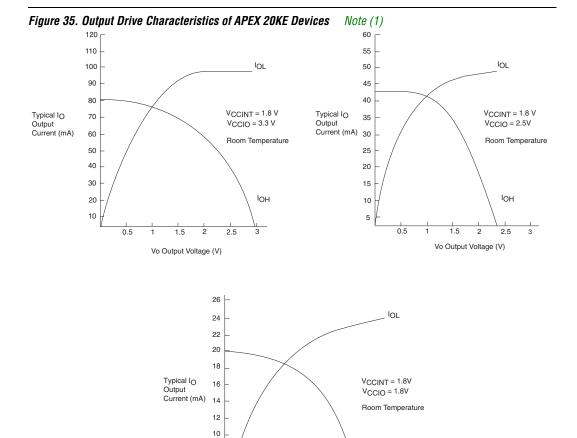

Figure 35 shows the output drive characteristics of APEX 20KE devices.

Note to Figure 35:

(1) These are transient (AC) currents.

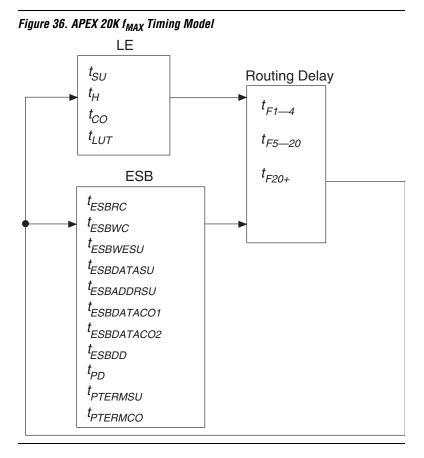

### **Timing Model**

The high-performance FastTrack and MegaLAB interconnect routing resources ensure predictable performance, accurate simulation, and accurate timing analysis. This predictable performance contrasts with that of FPGAs, which use a segmented connection scheme and therefore have unpredictable performance.

Vo Output Voltage (V)

IOH

2.0

All specifications are always representative of worst-case supply voltage and junction temperature conditions. All output-pin-timing specifications are reported for maximum driver strength.

Figure 36 shows the  $f_{MAX}$  timing model for APEX 20K devices.

Figure 37 shows the  $f_{MAX}$  timing model for APEX 20KE devices. These parameters can be used to estimate  $f_{MAX}$  for multiple levels of logic. Quartus II software timing analysis should be used for more accurate timing information.

Note to Tables 32 and 33:

(1) These timing parameters are sample-tested only.

Tables 34 through 37 show APEX 20KE LE, ESB, routing, and functional timing microparameters for the  $f_{MAX}$  timing model.

| Table 34. APEX 20KE LE Timing Microparameters |                                     |  |  |  |  |  |  |

|-----------------------------------------------|-------------------------------------|--|--|--|--|--|--|

| Symbol Parameter                              |                                     |  |  |  |  |  |  |

| t <sub>SU</sub>                               | LE register setup time before clock |  |  |  |  |  |  |

| t <sub>H</sub>                                | LE register hold time after clock   |  |  |  |  |  |  |

| t <sub>CO</sub>                               | LE register clock-to-output delay   |  |  |  |  |  |  |

| t <sub>LUT</sub>                              | LUT delay for data-in to data-out   |  |  |  |  |  |  |

| Table 35. APE.          | X 20KE ESB Timing Microparameters                                    |

|-------------------------|----------------------------------------------------------------------|

| Symbol                  | Parameter                                                            |

| t <sub>ESBARC</sub>     | ESB Asynchronous read cycle time                                     |

| t <sub>ESBSRC</sub>     | ESB Synchronous read cycle time                                      |

| t <sub>ESBAWC</sub>     | ESB Asynchronous write cycle time                                    |

| t <sub>ESBSWC</sub>     | ESB Synchronous write cycle time                                     |

| t <sub>ESBWASU</sub>    | ESB write address setup time with respect to WE                      |

| t <sub>ESBWAH</sub>     | ESB write address hold time with respect to WE                       |

| t <sub>ESBWDSU</sub>    | ESB data setup time with respect to WE                               |

| t <sub>ESBWDH</sub>     | ESB data hold time with respect to WE                                |

| t <sub>ESBRASU</sub>    | ESB read address setup time with respect to RE                       |

| t <sub>ESBRAH</sub>     | ESB read address hold time with respect to RE                        |

| t <sub>ESBWESU</sub>    | ESB WE setup time before clock when using input register             |

| t <sub>ESBWEH</sub>     | ESB WE hold time after clock when using input register               |

| t <sub>ESBDATASU</sub>  | ESB data setup time before clock when using input register           |

| t <sub>ESBDATAH</sub>   | ESB data hold time after clock when using input register             |

| t <sub>ESBWADDRSU</sub> | ESB write address setup time before clock when using input registers |

| t <sub>ESBRADDRSU</sub> | ESB read address setup time before clock when using input registers  |

| t <sub>ESBDATACO1</sub> | ESB clock-to-output delay when using output registers                |

| t <sub>ESBDATACO2</sub> | ESB clock-to-output delay without output registers                   |

| t <sub>ESBDD</sub>      | ESB data-in to data-out delay for RAM mode                           |

| t <sub>PD</sub>         | ESB Macrocell input to non-registered output                         |

| t <sub>PTERMSU</sub>    | ESB Macrocell register setup time before clock                       |

| t <sub>PTERMCO</sub>    | ESB Macrocell register clock-to-output delay                         |

### Notes to Tables 43 through 48:

- (1) This parameter is measured without using ClockLock or ClockBoost circuits.

- (2) This parameter is measured using ClockLock or ClockBoost circuits.

Tables 49 through 54 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K30E APEX 20KE devices.

| Table 49. EP20K30E f <sub>MAX</sub> LE Timing Microparameters |      |      |      |      |      |      |      |  |  |  |

|---------------------------------------------------------------|------|------|------|------|------|------|------|--|--|--|

| Symbol                                                        | -1   |      | -2   |      | -3   |      | Unit |  |  |  |

|                                                               | Min  | Max  | Min  | Max  | Min  | Max  |      |  |  |  |

| t <sub>SU</sub>                                               | 0.01 |      | 0.02 |      | 0.02 |      | ns   |  |  |  |

| t <sub>H</sub>                                                | 0.11 |      | 0.16 |      | 0.23 |      | ns   |  |  |  |

| t <sub>CO</sub>                                               |      | 0.32 |      | 0.45 |      | 0.67 | ns   |  |  |  |

| t <sub>LUT</sub>                                              |      | 0.85 |      | 1.20 |      | 1.77 | ns   |  |  |  |

| Symbol                  | -1   |      |      | -2   |      | 3    | Unit |

|-------------------------|------|------|------|------|------|------|------|

|                         | Min  | Max  | Min  | Max  | Min  | Max  |      |

| t <sub>ESBARC</sub>     |      | 1.83 |      | 2.57 |      | 3.79 | ns   |

| t <sub>ESBSRC</sub>     |      | 2.46 |      | 3.26 |      | 4.61 | ns   |

| t <sub>ESBAWC</sub>     |      | 3.50 |      | 4.90 |      | 7.23 | ns   |

| t <sub>ESBSWC</sub>     |      | 3.77 |      | 4.90 |      | 6.79 | ns   |

| t <sub>ESBWASU</sub>    | 1.59 |      | 2.23 |      | 3.29 |      | ns   |

| t <sub>ESBWAH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>ESBWDSU</sub>    | 1.75 |      | 2.46 |      | 3.62 |      | ns   |

| t <sub>ESBWDH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>ESBRASU</sub>    | 1.76 |      | 2.47 |      | 3.64 |      | ns   |

| t <sub>ESBRAH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>ESBWESU</sub>    | 1.68 |      | 2.49 |      | 3.87 |      | ns   |

| t <sub>ESBWEH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>ESBDATASU</sub>  | 0.08 |      | 0.43 |      | 1.04 |      | ns   |

| t <sub>ESBDATAH</sub>   | 0.13 |      | 0.13 |      | 0.13 |      | ns   |

| t <sub>ESBWADDRSU</sub> | 0.29 |      | 0.72 |      | 1.46 |      | ns   |

| t <sub>ESBRADDRSU</sub> | 0.36 |      | 0.81 |      | 1.58 |      | ns   |

| t <sub>ESBDATACO1</sub> |      | 1.06 |      | 1.24 |      | 1.55 | ns   |

| t <sub>ESBDATACO2</sub> |      | 2.39 |      | 3.35 |      | 4.94 | ns   |

| t <sub>ESBDD</sub>      |      | 3.50 |      | 4.90 |      | 7.23 | ns   |

| t <sub>PD</sub>         |      | 1.72 |      | 2.41 |      | 3.56 | ns   |

| t <sub>PTERMSU</sub>    | 0.99 |      | 1.56 |      | 2.55 |      | ns   |

| t <sub>PTERMCO</sub>    |      | 1.07 |      | 1.26 |      | 1.08 | ns   |

| Table 57. EP20K60E f <sub>MAX</sub> Routing Delays |     |      |     |      |     |      |    |  |  |  |  |

|----------------------------------------------------|-----|------|-----|------|-----|------|----|--|--|--|--|

| Symbol                                             | -1  |      | -2  |      |     | Unit |    |  |  |  |  |

|                                                    | Min | Max  | Min | Max  | Min | Max  |    |  |  |  |  |

| t <sub>F1-4</sub>                                  |     | 0.24 |     | 0.26 |     | 0.30 | ns |  |  |  |  |

| t <sub>F5-20</sub>                                 |     | 1.45 |     | 1.58 |     | 1.79 | ns |  |  |  |  |

| t <sub>F20+</sub>                                  |     | 1.96 |     | 2.14 |     | 2.45 | ns |  |  |  |  |

| Symbol             | -    | -1  |      | -2  |      | -3  |    |

|--------------------|------|-----|------|-----|------|-----|----|

|                    | Min  | Max | Min  | Max | Min  | Max | 1  |

| t <sub>CH</sub>    | 2.00 |     | 2.50 |     | 2.75 |     | ns |

| t <sub>CL</sub>    | 2.00 |     | 2.50 |     | 2.75 |     | ns |

| t <sub>CLRP</sub>  | 0.20 |     | 0.28 |     | 0.41 |     | ns |

| t <sub>PREP</sub>  | 0.20 |     | 0.28 |     | 0.41 |     | ns |

| t <sub>ESBCH</sub> | 2.00 |     | 2.50 |     | 2.75 |     | ns |

| t <sub>ESBCL</sub> | 2.00 |     | 2.50 |     | 2.75 |     | ns |

| t <sub>ESBWP</sub> | 1.29 |     | 1.80 |     | 2.66 |     | ns |

| t <sub>ESBRP</sub> | 1.04 |     | 1.45 |     | 2.14 |     | ns |

| Table 59. EP20K60E External Timing Parameters |      |      |      |      |      |      |      |  |  |

|-----------------------------------------------|------|------|------|------|------|------|------|--|--|

| Symbol                                        | -    | 1    | -    | 2    | -3   |      | Unit |  |  |

|                                               | Min  | Max  | Min  | Max  | Min  | Max  | 7    |  |  |

| t <sub>INSU</sub>                             | 2.03 |      | 2.12 |      | 2.23 |      | ns   |  |  |

| t <sub>INH</sub>                              | 0.00 |      | 0.00 |      | 0.00 |      | ns   |  |  |

| toutco                                        | 2.00 | 4.84 | 2.00 | 5.31 | 2.00 | 5.81 | ns   |  |  |

| t <sub>INSUPLL</sub>                          | 1.12 |      | 1.15 |      | -    |      | ns   |  |  |

| t <sub>INHPLL</sub>                           | 0.00 |      | 0.00 |      | -    |      | ns   |  |  |

| t <sub>OUTCOPLL</sub>                         | 0.50 | 3.37 | 0.50 | 3.69 | -    | -    | ns   |  |  |

| Symbol                    | -1   |      | -2   |      | -3   |      | Unit |

|---------------------------|------|------|------|------|------|------|------|

|                           | Min  | Max  | Min  | Max  | Min  | Max  |      |

| t <sub>INSUBIDIR</sub>    | 2.81 |      | 3.19 |      | 3.54 |      | ns   |

| t <sub>INHBIDIR</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| toutcobidir               | 2.00 | 5.12 | 2.00 | 5.62 | 2.00 | 6.11 | ns   |

| t <sub>XZBIDIR</sub>      |      | 7.51 |      | 8.32 |      | 8.67 | ns   |

| tzxbidir                  |      | 7.51 |      | 8.32 |      | 8.67 | ns   |

| t <sub>INSUBIDIRPLL</sub> | 3.30 |      | 3.64 |      | -    |      | ns   |

| t <sub>INHBIDIRPLL</sub>  | 0.00 |      | 0.00 |      | -    |      | ns   |

| toutcobidirpll            | 0.50 | 3.01 | 0.50 | 3.36 | -    | -    | ns   |

| txzbidirpll               |      | 5.40 |      | 6.05 |      | -    | ns   |

| tzxbidirpll               |      | 5.40 |      | 6.05 |      | -    | ns   |

Tables 79 through 84 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K300E APEX 20KE devices.

| Table 79. EP20K300E f <sub>MAX</sub> LE Timing Microparameters |      |      |      |      |      |      |    |  |  |  |

|----------------------------------------------------------------|------|------|------|------|------|------|----|--|--|--|

| Symbol                                                         | -    | 1    |      | -2   | -3   |      |    |  |  |  |

|                                                                | Min  | Max  | Min  | Max  | Min  | Max  |    |  |  |  |

| t <sub>SU</sub>                                                | 0.16 |      | 0.17 |      | 0.18 |      | ns |  |  |  |

| t <sub>H</sub>                                                 | 0.31 |      | 0.33 |      | 0.38 |      | ns |  |  |  |

| t <sub>CO</sub>                                                |      | 0.28 |      | 0.38 |      | 0.51 | ns |  |  |  |

| t <sub>LUT</sub>                                               |      | 0.79 |      | 1.07 |      | 1.43 | ns |  |  |  |

| Symbol             | -1   | 1   | -    | 2   | -3   |     | Unit |

|--------------------|------|-----|------|-----|------|-----|------|

|                    | Min  | Max | Min  | Max | Min  | Max |      |

| t <sub>CH</sub>    | 1.25 |     | 1.43 |     | 1.67 |     | ns   |

| t <sub>CL</sub>    | 1.25 |     | 1.43 |     | 1.67 |     | ns   |

| t <sub>CLRP</sub>  | 0.19 |     | 0.26 |     | 0.35 |     | ns   |

| t <sub>PREP</sub>  | 0.19 |     | 0.26 |     | 0.35 |     | ns   |

| t <sub>ESBCH</sub> | 1.25 |     | 1.43 |     | 1.67 |     | ns   |

| t <sub>ESBCL</sub> | 1.25 |     | 1.43 |     | 1.67 |     | ns   |

| t <sub>ESBWP</sub> | 1.25 |     | 1.71 |     | 2.28 |     | ns   |

| t <sub>ESBRP</sub> | 1.01 |     | 1.38 |     | 1.84 |     | ns   |

| Table 83. EP20K300E External Timing Parameters |      |      |      |      |      |      |    |  |  |

|------------------------------------------------|------|------|------|------|------|------|----|--|--|

| Symbol                                         | -    | 1    |      | -2   | -3   | Unit |    |  |  |

|                                                | Min  | Max  | Min  | Max  | Min  | Max  |    |  |  |

| t <sub>INSU</sub>                              | 2.31 |      | 2.44 |      | 2.57 |      | ns |  |  |

| t <sub>INH</sub>                               | 0.00 |      | 0.00 |      | 0.00 |      | ns |  |  |

| toutco                                         | 2.00 | 5.29 | 2.00 | 5.82 | 2.00 | 6.24 | ns |  |  |

| t <sub>INSUPLL</sub>                           | 1.76 |      | 1.85 |      | -    |      | ns |  |  |

| t <sub>INHPLL</sub>                            | 0.00 |      | 0.00 |      | -    |      | ns |  |  |

| t <sub>OUTCOPLL</sub>                          | 0.50 | 2.65 | 0.50 | 2.95 | -    | -    | ns |  |  |

| Symbol                    | -    | 1    | -    | 2    | -3   |      | Unit |

|---------------------------|------|------|------|------|------|------|------|

|                           | Min  | Max  | Min  | Max  | Min  | Max  | 1    |

| t <sub>INSUBIDIR</sub>    | 2.77 |      | 2.85 |      | 3.11 |      | ns   |

| t <sub>INHBIDIR</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>OUTCOBIDIR</sub>   | 2.00 | 5.29 | 2.00 | 5.82 | 2.00 | 6.24 | ns   |

| t <sub>XZBIDIR</sub>      |      | 7.59 |      | 8.30 |      | 9.09 | ns   |

| t <sub>ZXBIDIR</sub>      |      | 7.59 |      | 8.30 |      | 9.09 | ns   |

| t <sub>INSUBIDIRPLL</sub> | 2.50 |      | 2.76 |      | -    |      | ns   |

| t <sub>INHBIDIRPLL</sub>  | 0.00 |      | 0.00 |      | -    |      | ns   |

| toutcobidirpll            | 0.50 | 2.65 | 0.50 | 2.95 | -    | -    | ns   |

| t <sub>XZBIDIRPLL</sub>   |      | 5.00 |      | 5.43 |      | -    | ns   |

| tzxbidirpll               |      | 5.00 |      | 5.43 |      | -    | ns   |

Tables 97 through 102 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K1000E APEX 20KE devices.

| Table 97. EP20K1000E f <sub>MAX</sub> LE Timing Microparameters |         |         |         |          |         |      |    |  |  |

|-----------------------------------------------------------------|---------|---------|---------|----------|---------|------|----|--|--|

| Symbol                                                          | -1 Spee | d Grade | -2 Spee | ed Grade | -3 Spee | Unit |    |  |  |

|                                                                 | Min     | Max     | Min     | Max      | Min     | Max  | 7  |  |  |

| t <sub>SU</sub>                                                 | 0.25    |         | 0.25    |          | 0.25    |      | ns |  |  |

| t <sub>H</sub>                                                  | 0.25    |         | 0.25    |          | 0.25    |      | ns |  |  |

| t <sub>CO</sub>                                                 |         | 0.28    |         | 0.32     |         | 0.33 | ns |  |  |

| t <sub>LUT</sub>                                                |         | 0.80    |         | 0.95     |         | 1.13 | ns |  |  |

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 http://www.altera.com Applications Hotline: (800) 800-EPLD Customer Marketing: (408) 544-7104 Literature Services: lit\_req@altera.com Copyright © 2004 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, mask work rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes

to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.