# E·XFL

# Intel - EP20K200EFC484-1N Datasheet

Welcome to <u>E-XFL.COM</u>

# Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

# Details

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 832                                                          |

| Number of Logic Elements/Cells | 8320                                                         |

| Total RAM Bits                 | 106496                                                       |

| Number of I/O                  | 376                                                          |

| Number of Gates                | 526000                                                       |

| Voltage - Supply               | 1.71V ~ 1.89V                                                |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                              |

| Package / Case                 | 484-BBGA                                                     |

| Supplier Device Package        | 484-FBGA (23x23)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep20k200efc484-1n |

|                                |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 2. Additional APEX 20K Device Features |           |           | Note (1)  |           |            |            |

|----------------------------------------------|-----------|-----------|-----------|-----------|------------|------------|

| Feature                                      | EP20K300E | EP20K400  | EP20K400E | EP20K600E | EP20K1000E | EP20K1500E |

| Maximum system gates                         | 728,000   | 1,052,000 | 1,052,000 | 1,537,000 | 1,772,000  | 2,392,000  |

| Typical gates                                | 300,000   | 400,000   | 400,000   | 600,000   | 1,000,000  | 1,500,000  |

| LEs                                          | 11,520    | 16,640    | 16,640    | 24,320    | 38,400     | 51,840     |

| ESBs                                         | 72        | 104       | 104       | 152       | 160        | 216        |

| Maximum<br>RAM bits                          | 147,456   | 212,992   | 212,992   | 311,296   | 327,680    | 442,368    |

| Maximum<br>macrocells                        | 1,152     | 1,664     | 1,664     | 2,432     | 2,560      | 3,456      |

| Maximum user I/O<br>pins                     | 408       | 502       | 488       | 588       | 708        | 808        |

#### Note to Tables 1 and 2:

The embedded IEEE Std. 1149.1 Joint Test Action Group (JTAG) boundary-scan circuitry contributes up to 57,000 additional gates.

Additional Features

- Designed for low-power operation

- 1.8-V and 2.5-V supply voltage (see Table 3)

- MultiVolt<sup>™</sup> I/O interface support to interface with 1.8-V, 2.5-V, 3.3-V, and 5.0-V devices (see Table 3)

- ESB offering programmable power-saving mode

| Feature                                                     | Device                           |                                                                                                                                |  |

|-------------------------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|

|                                                             | EP20K100<br>EP20K200<br>EP20K400 | EP20K30E<br>EP20K60E<br>EP20K100E<br>EP20K160E<br>EP20K200E<br>EP20K300E<br>EP20K400E<br>EP20K600E<br>EP20K1000E<br>EP20K1500E |  |

| Internal supply voltage (V <sub>CCINT</sub> )               | 2.5 V                            | 1.8 V                                                                                                                          |  |

| MultiVolt I/O interface voltage levels (V <sub>CCIO</sub> ) | 2.5 V, 3.3 V, 5.0 V              | 1.8 V, 2.5 V, 3.3 V, 5.0 V (1)                                                                                                 |  |

#### Note to Table 3:

(1) APEX 20KE devices can be 5.0-V tolerant by using an external resistor.

- Flexible clock management circuitry with up to four phase-locked loops (PLLs)

- Built-in low-skew clock tree

- Up to eight global clock signals

- ClockLock<sup>®</sup> feature reducing clock delay and skew

- ClockBoost<sup>®</sup> feature providing clock multiplication and division

- ClockShift<sup>TM</sup> programmable clock phase and delay shifting

- Powerful I/O features

- Compliant with peripheral component interconnect Special Interest Group (PCI SIG) *PCI Local Bus Specification, Revision 2.2* for 3.3-V operation at 33 or 66 MHz and 32 or 64 bits

- Support for high-speed external memories, including DDR SDRAM and ZBT SRAM (ZBT is a trademark of Integrated Device Technology, Inc.)

- Bidirectional I/O performance  $(t_{CO} + t_{SU})$  up to 250 MHz

- LVDS performance up to 840 Mbits per channel

- Direct connection from I/O pins to local interconnect providing fast t<sub>CO</sub> and t<sub>SU</sub> times for complex logic

- MultiVolt I/O interface support to interface with 1.8-V, 2.5-V, 3.3-V, and 5.0-V devices (see Table 3)

- Programmable clamp to V<sub>CCIO</sub>

- Individual tri-state output enable control for each pin

- Programmable output slew-rate control to reduce switching noise

- Support for advanced I/O standards, including low-voltage differential signaling (LVDS), LVPECL, PCI-X, AGP, CTT, stubseries terminated logic (SSTL-3 and SSTL-2), Gunning transceiver logic plus (GTL+), and high-speed terminated logic (HSTL Class I)

- Pull-up on I/O pins before and during configuration

- Advanced interconnect structure

- Four-level hierarchical FastTrack<sup>®</sup> Interconnect structure providing fast, predictable interconnect delays

- Dedicated carry chain that implements arithmetic functions such as fast adders, counters, and comparators (automatically used by software tools and megafunctions)

- Dedicated cascade chain that implements high-speed, high-fan-in logic functions (automatically used by software tools and megafunctions)

- Interleaved local interconnect allows one LE to drive 29 other LEs through the fast local interconnect

- Advanced packaging options

- Available in a variety of packages with 144 to 1,020 pins (see Tables 4 through 7)

- FineLine BGA<sup>®</sup> packages maximize board space efficiency

- Advanced software support

- Software design support and automatic place-and-route provided by the Altera<sup>®</sup> Quartus<sup>®</sup> II development system for

# Functional Description

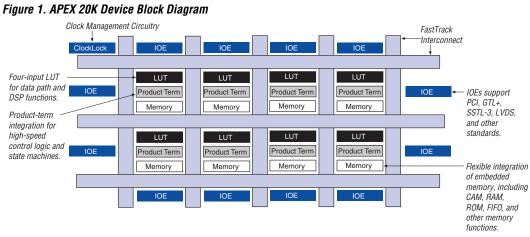

APEX 20K devices incorporate LUT-based logic, product-term-based logic, and memory into one device. Signal interconnections within APEX 20K devices (as well as to and from device pins) are provided by the FastTrack<sup>®</sup> Interconnect—a series of fast, continuous row and column channels that run the entire length and width of the device.

Each I/O pin is fed by an I/O element (IOE) located at the end of each row and column of the FastTrack Interconnect. Each IOE contains a bidirectional I/O buffer and a register that can be used as either an input or output register to feed input, output, or bidirectional signals. When used with a dedicated clock pin, these registers provide exceptional performance. IOEs provide a variety of features, such as 3.3-V, 64-bit, 66-MHz PCI compliance; JTAG BST support; slew-rate control; and tri-state buffers. APEX 20KE devices offer enhanced I/O support, including support for 1.8-V I/O, 2.5-V I/O, LVCMOS, LVTTL, LVPECL, 3.3-V PCI, PCI-X, LVDS, GTL+, SSTL-2, SSTL-3, HSTL, CTT, and 3.3-V AGP I/O standards.

The ESB can implement a variety of memory functions, including CAM, RAM, dual-port RAM, ROM, and FIFO functions. Embedding the memory directly into the die improves performance and reduces die area compared to distributed-RAM implementations. Moreover, the abundance of cascadable ESBs ensures that the APEX 20K device can implement multiple wide memory blocks for high-density designs. The ESB's high speed ensures it can implement small memory blocks without any speed penalty. The abundance of ESBs ensures that designers can create as many different-sized memory blocks as the system requires. Figure 1 shows an overview of the APEX 20K device.

#### Normal Mode

The normal mode is suitable for general logic applications, combinatorial functions, or wide decoding functions that can take advantage of a cascade chain. In normal mode, four data inputs from the LAB local interconnect and the carry-in are inputs to a four-input LUT. The Quartus II software Compiler automatically selects the carry-in or the DATA3 signal as one of the inputs to the LUT. The LUT output can be combined with the cascade-in signal to form a cascade chain through the cascade-out signal. LEs in normal mode support packed registers.

### **Arithmetic Mode**

The arithmetic mode is ideal for implementing adders, accumulators, and comparators. An LE in arithmetic mode uses two 3-input LUTs. One LUT computes a three-input function; the other generates a carry output. As shown in Figure 8, the first LUT uses the carry-in signal and two data inputs from the LAB local interconnect to generate a combinatorial or registered output. For example, when implementing an adder, this output is the sum of three signals: DATA1, DATA2, and carry-in. The second LUT uses the same three signals to generate a carry-out signal, thereby creating a carry chain. The arithmetic mode also supports simultaneous use of the cascade chain. LEs in arithmetic mode can drive out registered and unregistered versions of the LUT output.

The Quartus II software implements parameterized functions that use the arithmetic mode automatically where appropriate; the designer does not need to specify how the carry chain will be used.

### **Counter Mode**

The counter mode offers clock enable, counter enable, synchronous up/down control, synchronous clear, and synchronous load options. The counter enable and synchronous up/down control signals are generated from the data inputs of the LAB local interconnect. The synchronous clear and synchronous load options are LAB-wide signals that affect all registers in the LAB. Consequently, if any of the LEs in an LAB use the counter mode, other LEs in that LAB must be used as part of the same counter or be used for a combinatorial function. The Quartus II software automatically places any registers that are not used by the counter into other LABs.

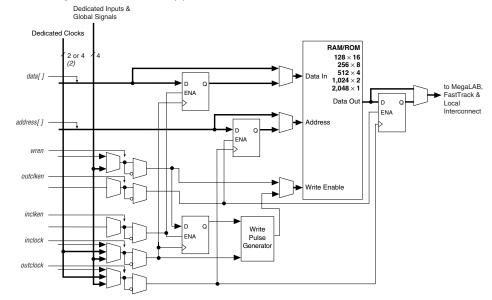

# Figure 22. ESB in Single-Port Mode Note (1)

#### Notes to Figure 22:

All registers can be asynchronously cleared by ESB local interconnect signals, global signals, or the chip-wide reset.

APEX 20KE devices have four dedicated clocks.

# **Content-Addressable Memory**

In APEX 20KE devices, the ESB can implement CAM. CAM can be thought of as the inverse of RAM. When read, RAM outputs the data for a given address. Conversely, CAM outputs an address for a given data word. For example, if the data FA12 is stored in address 14, the CAM outputs 14 when FA12 is driven into it.

CAM is used for high-speed search operations. When searching for data within a RAM block, the search is performed serially. Thus, finding a particular data word can take many cycles. CAM searches all addresses in parallel and outputs the address storing a particular word. When a match is found, a match flag is set high. Figure 23 shows the CAM block diagram.

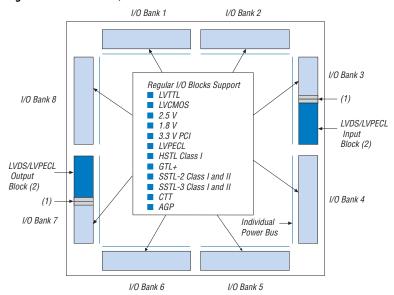

# Advanced I/O Standard Support

APEX 20KE IOEs support the following I/O standards: LVTTL, LVCMOS, 1.8-V I/O, 2.5-V I/O, 3.3-V PCI, PCI-X, 3.3-V AGP, LVDS, LVPECL, GTL+, CTT, HSTL Class I, SSTL-3 Class I and II, and SSTL-2 Class I and II.

For more information on I/O standards supported by APEX 20KE devices, see *Application Note* 117 (*Using Selectable I/O Standards in Altera Devices*).

The APEX 20KE device contains eight I/O banks. In QFP packages, the banks are linked to form four I/O banks. The I/O banks directly support all standards except LVDS and LVPECL. All I/O banks can support LVDS and LVPECL with the addition of external resistors. In addition, one block within a bank contains circuitry to support high-speed True-LVDS and LVPECL inputs, and another block within a particular bank supports high-speed True-LVDS and LVPECL outputs. The LVDS blocks support all of the I/O standards. Each I/O bank has its own VCCIO pins. A single device can support 1.8-V, 2.5-V, and 3.3-V interfaces; each bank can support a different standard independently. Each bank can also use a separate V<sub>REF</sub> level so that each bank can support any of the terminated standards (such as SSTL-3) independently. Within a bank, any one of the terminated standards can be supported. EP20K300E and larger APEX 20KE devices support the LVDS interface for data pins (smaller devices support LVDS clock pins, but not data pins). All EP20K300E and larger devices support the LVDS interface for data pins up to 155 Mbit per channel; EP20K400E devices and larger with an X-suffix on the ordering code add a serializer/deserializer circuit and PLL for higher-speed support.

Each bank can support multiple standards with the same VCCIO for output pins. Each bank can support one voltage-referenced I/O standard, but it can support multiple I/O standards with the same VCCIO voltage level. For example, when VCCIO is 3.3 V, a bank can support LVTTL, LVCMOS, 3.3-V PCI, and SSTL-3 for inputs and outputs.

When the LVDS banks are not used as LVDS I/O banks, they support all of the other I/O standards. Figure 29 shows the arrangement of the APEX 20KE I/O banks.

#### Figure 29. APEX 20KE I/O Banks

#### Notes to Figure 29:

- For more information on placing I/O pins in LVDS blocks, refer to the Guidelines for Using LVDS Blocks section in Application Note 120 (Using LVDS in APEX 20KE Devices).

- (2) If the LVDS input and output blocks are not used for LVDS, they can support all of the I/O standards and can be used as input, output, or bidirectional pins with V<sub>CCIO</sub> set to 3.3 V, 2.5 V, or 1.8 V.

# Power Sequencing & Hot Socketing

Because APEX 20K and APEX 20KE devices can be used in a mixedvoltage environment, they have been designed specifically to tolerate any possible power-up sequence. Therefore, the  $V_{CCIO}$  and  $V_{CCINT}$  power supplies may be powered in any order.

For more information, please refer to the "Power Sequencing Considerations" section in the *Configuring APEX 20KE & APEX 20KC Devices* chapter of the *Configuration Devices Handbook*.

Signals can be driven into APEX 20K devices before and during power-up without damaging the device. In addition, APEX 20K devices do not drive out during power-up. Once operating conditions are reached and the device is configured, APEX 20K and APEX 20KE devices operate as specified by the user.

For designs that require both a multiplied and non-multiplied clock, the clock trace on the board can be connected to CLK2p. Table 14 shows the combinations supported by the ClockLock and ClockBoost circuitry. The CLK2p pin can feed both the ClockLock and ClockBoost circuitry in the APEX 20K device. However, when both circuits are used, the other clock pin (CLK1p) cannot be used.

| Table 14. Multiplication Factor Combinations |    |  |  |

|----------------------------------------------|----|--|--|

| Clock 1 Clock 2                              |    |  |  |

| ×1                                           | ×1 |  |  |

| ×1, ×2 ×2                                    |    |  |  |

| ×1, ×2, ×4                                   | ×4 |  |  |

# APEX 20KE ClockLock Feature

APEX 20KE devices include an enhanced ClockLock feature set. These devices include up to four PLLs, which can be used independently. Two PLLs are designed for either general-purpose use or LVDS use (on devices that support LVDS I/O pins). The remaining two PLLs are designed for general-purpose use. The EP20K200E and smaller devices have two PLLs; the EP20K300E and larger devices have four PLLs.

The following sections describe some of the features offered by the APEX 20KE PLLs.

# External PLL Feedback

The ClockLock circuit's output can be driven off-chip to clock other devices in the system; further, the feedback loop of the PLL can be routed off-chip. This feature allows the designer to exercise fine control over the I/O interface between the APEX 20KE device and another high-speed device, such as SDRAM.

# Clock Multiplication

The APEX 20KE ClockBoost circuit can multiply or divide clocks by a programmable number. The clock can be multiplied by  $m/(n \times k)$  or  $m/(n \times v)$ , where *m* and *k* range from 2 to 160, and *n* and *v* range from 1 to 16. Clock multiplication and division can be used for time-domain multiplexing and other functions, which can reduce design LE requirements.

| Symbol                  | Parameter                                        | I/O Standard       | -1X Speed Grade |     | I/O Standard -1X Speed Grade -2X Speed Grade |     | d Grade | Units |

|-------------------------|--------------------------------------------------|--------------------|-----------------|-----|----------------------------------------------|-----|---------|-------|

|                         |                                                  |                    | Min             | Max | Min                                          | Max |         |       |

| f <sub>VCO</sub> (4)    | Voltage controlled oscillator<br>operating range |                    | 200             | 500 | 200                                          | 500 | MHz     |       |

| f <sub>CLOCK0</sub>     | Clock0 PLL output frequency for internal use     |                    | 1.5             | 335 | 1.5                                          | 200 | MHz     |       |

| f <sub>CLOCK1</sub>     | Clock1 PLL output frequency for internal use     |                    | 20              | 335 | 20                                           | 200 | MHz     |       |

| fCLOCK0_EXT             | Output clock frequency for                       | 3.3-V LVTTL        | 1.5             | 245 | 1.5                                          | 226 | MHz     |       |

|                         | external clock0 output                           | 2.5-V LVTTL        | 1.5             | 234 | 1.5                                          | 221 | MHz     |       |

|                         |                                                  | 1.8-V LVTTL        | 1.5             | 223 | 1.5                                          | 216 | MHz     |       |

|                         |                                                  | GTL+               | 1.5             | 205 | 1.5                                          | 193 | MHz     |       |

|                         |                                                  | SSTL-2 Class<br>I  | 1.5             | 158 | 1.5                                          | 157 | MHz     |       |

|                         |                                                  | SSTL-2 Class<br>II | 1.5             | 142 | 1.5                                          | 142 | MHz     |       |

|                         |                                                  | SSTL-3 Class<br>I  | 1.5             | 166 | 1.5                                          | 162 | MHz     |       |

|                         |                                                  | SSTL-3 Class<br>II | 1.5             | 149 | 1.5                                          | 146 | MHz     |       |

|                         |                                                  | LVDS               | 1.5             | 420 | 1.5                                          | 350 | MHz     |       |

| f <sub>CLOCK1_EXT</sub> | Output clock frequency for                       | 3.3-V LVTTL        | 20              | 245 | 20                                           | 226 | MHz     |       |

|                         | external clock1 output                           | 2.5-V LVTTL        | 20              | 234 | 20                                           | 221 | MHz     |       |

|                         |                                                  | 1.8-V LVTTL        | 20              | 223 | 20                                           | 216 | MHz     |       |

|                         |                                                  | GTL+               | 20              | 205 | 20                                           | 193 | MHz     |       |

|                         |                                                  | SSTL-2 Class<br>I  | 20              | 158 | 20                                           | 157 | MHz     |       |

|                         |                                                  | SSTL-2 Class<br>II | 20              | 142 | 20                                           | 142 | MHz     |       |

|                         |                                                  | SSTL-3 Class<br>I  | 20              | 166 | 20                                           | 162 | MHz     |       |

|                         |                                                  | SSTL-3 Class<br>II | 20              | 149 | 20                                           | 146 | MHz     |       |

|                         |                                                  | LVDS               | 20              | 420 | 20                                           | 350 | MHz     |       |

| Table 26. APEX 20K 5.0-V Tolerant Device Capacitance   Notes (2), (14) |                                          |                                     |     |     |      |

|------------------------------------------------------------------------|------------------------------------------|-------------------------------------|-----|-----|------|

| Symbol                                                                 | Parameter                                | Conditions                          | Min | Мах | Unit |

| C <sub>IN</sub>                                                        | Input capacitance                        | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 8   | pF   |

| C <sub>INCLK</sub>                                                     | Input capacitance on dedicated clock pin | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 12  | pF   |

| C <sub>OUT</sub>                                                       | Output capacitance                       | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 8   | pF   |

# Notes to Tables 23 through 26:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- All APEX 20K devices are 5.0-V tolerant. (2)

- (3) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to 5.75 V for input currents less than 100 mA and periods shorter than 20 ns.

- Numbers in parentheses are for industrial-temperature-range devices. (4)

- Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically. (5)

- All pins, including dedicated inputs, clock I/O, and JTAG pins, may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are (6) powered.

- (7)Typical values are for  $T_A = 25^{\circ}$  C,  $V_{CCINT} = 2.5$  V, and  $V_{CCIO} = 2.5$  or 3.3 V.

- These values are specified in the APEX 20K device recommended operating conditions, shown in Table 26 on (8)page 62.

- (9) The APEX 20K input buffers are compatible with 2.5-V and 3.3-V (LVTTL and LVCMOS) signals. Additionally, the input buffers are 3.3-V PCI compliant when V<sub>CCIO</sub> and V<sub>CCINT</sub> meet the relationship shown in Figure 33 on page 68.

- (10) The I<sub>OH</sub> parameter refers to high-level TTL, PCI or CMOS output current.

- (11) The I<sub>OL</sub> parameter refers to low-level TTL, PCI, or CMOS output current. This parameter applies to open-drain pins as well as output pins.

- (12) This value is specified for normal device operation. The value may vary during power-up.

- (13) Pin pull-up resistance values will be lower if an external source drives the pin higher than  $V_{CCIO}$ .

- (14) Capacitance is sample-tested only.

Tables 27 through 30 provide information on absolute maximum ratings, recommended operating conditions, DC operating conditions, and capacitance for 1.8-V APEX 20KE devices.

| Symbol             | Parameter                  | Conditions                                        | Min  | Max | Unit |

|--------------------|----------------------------|---------------------------------------------------|------|-----|------|

| V <sub>CCINT</sub> | Supply voltage             | With respect to ground (2)                        | -0.5 | 2.5 | V    |

| V <sub>CCIO</sub>  |                            |                                                   | -0.5 | 4.6 | V    |

| VI                 | DC input voltage           |                                                   | -0.5 | 4.6 | V    |

| I <sub>OUT</sub>   | DC output current, per pin |                                                   | -25  | 25  | mA   |

| T <sub>STG</sub>   | Storage temperature        | No bias                                           | -65  | 150 | °C   |

| T <sub>AMB</sub>   | Ambient temperature        | Under bias                                        | -65  | 135 | °C   |

| ΤJ                 | Junction temperature       | PQFP, RQFP, TQFP, and BGA packages,<br>under bias |      | 135 | °C   |

|                    |                            | Ceramic PGA packages, under bias                  |      | 150 | °C   |

P

For DC Operating Specifications on APEX 20KE I/O standards, please refer to *Application Note 117 (Using Selectable I/O Standards in Altera Devices).*

| Table 30. APEX 20KE Device Capacitance Note (15) |                                             |                                     |     |     |      |

|--------------------------------------------------|---------------------------------------------|-------------------------------------|-----|-----|------|

| Symbol                                           | Parameter                                   | Conditions                          | Min | Max | Unit |

| C <sub>IN</sub>                                  | Input capacitance                           | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 8   | pF   |

| CINCLK                                           | Input capacitance on<br>dedicated clock pin | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 12  | pF   |

| C <sub>OUT</sub>                                 | Output capacitance                          | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 8   | pF   |

#### Notes to Tables 27 through 30:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to 5.75 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Numbers in parentheses are for industrial-temperature-range devices.

- (4) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically.

- (5) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to the voltage shown in the following table based on input duty cycle for input currents less than 100 mA. The overshoot is dependent upon duty cycle of the signal. The DC case is equivalent to 100% duty cycle.

| Vin  | Max. Duty Cycle |

|------|-----------------|

| 4.0V | 100% (DC)       |

| 4.1  | 90%             |

- 4.2 50%

- 4.3 30%

- 4.4 17%

- 4.5 10%

- (6) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are powered.

- (7) Typical values are for  $T_A = 25^\circ$  C,  $V_{CCINT} = 1.8$  V, and  $V_{CCIO} = 1.8$  V, 2.5 V or 3.3 V.

- (8) These values are specified under the APEX 20KE device recommended operating conditions, shown in Table 24 on page 60.

- (9) Refer to Application Note 117 (Using Selectable I/O Standards in Altera Devices) for the V<sub>IH</sub>, V<sub>IL</sub>, V<sub>OH</sub>, V<sub>OL</sub>, and I<sub>I</sub> parameters when VCCIO = 1.8 V.

- (10) The APEX 20KE input buffers are compatible with 1.8-V, 2.5-V and 3.3-V (LVTTL and LVCMOS) signals. Additionally, the input buffers are 3.3-V PCI compliant. Input buffers also meet specifications for GTL+, CTT, AGP, SSTL-2, SSTL-3, and HSTL.

- (11) The I<sub>OH</sub> parameter refers to high-level TTL, PCI, or CMOS output current.

- (12) The I<sub>OL</sub> parameter refers to low-level TTL, PCI, or CMOS output current. This parameter applies to open-drain pins as well as output pins.

- (13) This value is specified for normal device operation. The value may vary during power-up.

- (14) Pin pull-up resistance values will be lower if an external source drives the pin higher than V<sub>CCIO</sub>.

- (15) Capacitance is sample-tested only.

Figure 33 shows the relationship between  $\rm V_{CCIO}$  and  $\rm V_{CCINT}$  for 3.3-V PCI compliance on APEX 20K devices.

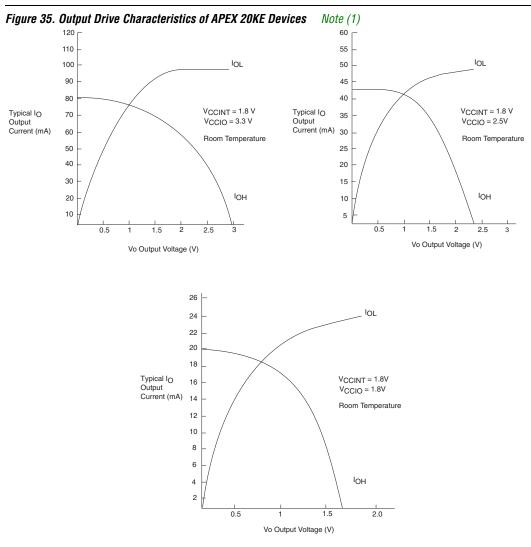

Figure 35 shows the output drive characteristics of APEX 20KE devices.

*Note to Figure 35:*(1) These are transient (AC) currents.

# **Timing Model**

The high-performance FastTrack and MegaLAB interconnect routing resources ensure predictable performance, accurate simulation, and accurate timing analysis. This predictable performance contrasts with that of FPGAs, which use a segmented connection scheme and therefore have unpredictable performance.

| Table 36. APEX 20KE Routing Timing Microparameters     Note (1) |                                                    |  |  |  |

|-----------------------------------------------------------------|----------------------------------------------------|--|--|--|

| Symbol                                                          | Parameter                                          |  |  |  |

| t <sub>F1-4</sub>                                               | Fanout delay using Local Interconnect              |  |  |  |

| t <sub>F5-20</sub>                                              | Fanout delay estimate using MegaLab Interconnect   |  |  |  |

| t <sub>F20+</sub>                                               | Fanout delay estimate using FastTrack Interconnect |  |  |  |

#### Note to Table 36:

These parameters are worst-case values for typical applications. Post-compilation timing simulation and timing analysis are required to determine actual worst-case performance.

| Table 37. APEX 20KE Functional Timing Microparameters |                                        |  |

|-------------------------------------------------------|----------------------------------------|--|

| Symbol                                                | Parameter                              |  |

| ТСН                                                   | Minimum clock high time from clock pin |  |

| TCL                                                   | Minimum clock low time from clock pin  |  |

| TCLRP                                                 | LE clear Pulse Width                   |  |

| TPREP                                                 | LE preset pulse width                  |  |

| TESBCH                                                | Clock high time for ESB                |  |

| TESBCL                                                | Clock low time for ESB                 |  |

| TESBWP                                                | Write pulse width                      |  |

| TESBRP                                                | Read pulse width                       |  |

# Table 37. APEX 20KE Functional Timing Microparameters

Tables 38 and 39 describe the APEX 20KE external timing parameters.

| Table 38. APEX 20KE External Timing Parameters   Note (1) |                                                                           |            |  |  |

|-----------------------------------------------------------|---------------------------------------------------------------------------|------------|--|--|

| Symbol                                                    | Clock Parameter                                                           | Conditions |  |  |

| t <sub>INSU</sub>                                         | Setup time with global clock at IOE input register                        |            |  |  |

| t <sub>INH</sub>                                          | Hold time with global clock at IOE input register                         |            |  |  |

| t <sub>оитсо</sub>                                        | Clock-to-output delay with global clock at IOE output register C1 = 10 pF |            |  |  |

| t <sub>INSUPLL</sub>                                      | Setup time with PLL clock at IOE input register                           |            |  |  |

| t <sub>INHPLL</sub>                                       | Hold time with PLL clock at IOE input register                            |            |  |  |

| t <sub>OUTCOPLL</sub>                                     | Clock-to-output delay with PLL clock at IOE output register               | C1 = 10 pF |  |  |

| Symbol                  | -     | 1    | -     | 2    | -    | 3    | Unit |

|-------------------------|-------|------|-------|------|------|------|------|

|                         | Min   | Max  | Min   | Max  | Min  | Max  |      |

| t <sub>ESBARC</sub>     |       | 1.68 |       | 2.06 |      | 2.24 | ns   |

| t <sub>ESBSRC</sub>     |       | 2.27 |       | 2.77 |      | 3.18 | ns   |

| t <sub>ESBAWC</sub>     |       | 3.10 |       | 3.86 |      | 4.50 | ns   |

| t <sub>ESBSWC</sub>     |       | 2.90 |       | 3.67 |      | 4.21 | ns   |

| t <sub>ESBWASU</sub>    | 0.55  |      | 0.67  |      | 0.74 |      | ns   |

| t <sub>ESBWAH</sub>     | 0.36  |      | 0.46  |      | 0.48 |      | ns   |

| t <sub>ESBWDSU</sub>    | 0.69  |      | 0.83  |      | 0.95 |      | ns   |

| t <sub>ESBWDH</sub>     | 0.36  |      | 0.46  |      | 0.48 |      | ns   |

| t <sub>ESBRASU</sub>    | 1.61  |      | 1.90  |      | 2.09 |      | ns   |

| t <sub>ESBRAH</sub>     | 0.00  |      | 0.00  |      | 0.01 |      | ns   |

| t <sub>ESBWESU</sub>    | 1.42  |      | 1.71  |      | 2.01 |      | ns   |

| t <sub>ESBWEH</sub>     | 0.00  |      | 0.00  |      | 0.00 |      | ns   |

| t <sub>ESBDATASU</sub>  | -0.06 |      | -0.07 |      | 0.05 |      | ns   |

| t <sub>ESBDATAH</sub>   | 0.13  |      | 0.13  |      | 0.13 |      | ns   |

| t <sub>ESBWADDRSU</sub> | 0.11  |      | 0.13  |      | 0.31 |      | ns   |

| t <sub>ESBRADDRSU</sub> | 0.18  |      | 0.23  |      | 0.39 |      | ns   |

| t <sub>ESBDATACO1</sub> |       | 1.09 |       | 1.35 |      | 1.51 | ns   |

| t <sub>ESBDATACO2</sub> |       | 2.19 |       | 2.75 |      | 3.22 | ns   |

| t <sub>ESBDD</sub>      |       | 2.75 |       | 3.41 |      | 4.03 | ns   |

| t <sub>PD</sub>         |       | 1.58 |       | 1.97 |      | 2.33 | ns   |

| t <sub>PTERMSU</sub>    | 1.00  |      | 1.22  |      | 1.51 |      | ns   |

| t <sub>PTERMCO</sub>    |       | 1.10 |       | 1.37 |      | 1.09 | ns   |

| Table 75. EP2      | OK200E f <sub>max</sub> | Routing Delay | 'S  |      |     |      |      |

|--------------------|-------------------------|---------------|-----|------|-----|------|------|

| Symbol             | -                       | ·1            |     | -2   | -:  | 3    | Unit |

|                    | Min                     | Max           | Min | Max  | Min | Max  |      |

| t <sub>F1-4</sub>  |                         | 0.25          |     | 0.27 |     | 0.29 | ns   |

| t <sub>F5-20</sub> |                         | 1.02          |     | 1.20 |     | 1.41 | ns   |

| t <sub>F20+</sub>  |                         | 1.99          |     | 2.23 |     | 2.53 | ns   |

| Symbol             | -1   | l   | -    | 2   | -3   | 3   | Unit |

|--------------------|------|-----|------|-----|------|-----|------|

|                    | Min  | Max | Min  | Max | Min  | Max |      |

| t <sub>CH</sub>    | 1.36 |     | 2.44 |     | 2.65 |     | ns   |

| t <sub>CL</sub>    | 1.36 |     | 2.44 |     | 2.65 |     | ns   |

| t <sub>CLRP</sub>  | 0.18 |     | 0.19 |     | 0.21 |     | ns   |

| t <sub>PREP</sub>  | 0.18 |     | 0.19 |     | 0.21 |     | ns   |

| t <sub>ESBCH</sub> | 1.36 |     | 2.44 |     | 2.65 |     | ns   |

| t <sub>ESBCL</sub> | 1.36 |     | 2.44 |     | 2.65 |     | ns   |

| t <sub>ESBWP</sub> | 1.18 |     | 1.48 |     | 1.76 |     | ns   |

| t <sub>ESBRP</sub> | 0.95 |     | 1.17 |     | 1.41 |     | ns   |

| Table 77. EP20K200E External Timing Parameters |      |      |      |      |      |      |    |  |  |  |  |

|------------------------------------------------|------|------|------|------|------|------|----|--|--|--|--|

| Symbol                                         | -    | -1   |      | -2   |      | -3   |    |  |  |  |  |

|                                                | Min  | Max  | Min  | Max  | Min  | Max  |    |  |  |  |  |

| t <sub>INSU</sub>                              | 2.24 |      | 2.35 |      | 2.47 |      | ns |  |  |  |  |

| t <sub>INH</sub>                               | 0.00 |      | 0.00 |      | 0.00 |      | ns |  |  |  |  |

| t <sub>outco</sub>                             | 2.00 | 5.12 | 2.00 | 5.62 | 2.00 | 6.11 | ns |  |  |  |  |

| t <sub>INSUPLL</sub>                           | 2.13 |      | 2.07 |      | -    |      | ns |  |  |  |  |

| t <sub>INHPLL</sub>                            | 0.00 |      | 0.00 |      | -    |      | ns |  |  |  |  |

| t <sub>outcopll</sub>                          | 0.50 | 3.01 | 0.50 | 3.36 | -    | -    | ns |  |  |  |  |

| Table 78. EP20K200         | DE External B | idirectional Ti | ming Paramo | eters |      |      |      |  |

|----------------------------|---------------|-----------------|-------------|-------|------|------|------|--|

| Symbol                     | -1            |                 | -2          |       | -3   |      | Unit |  |

|                            | Min           | Мах             | Min         | Max   | Min  | Max  |      |  |

| t <sub>insubidir</sub>     | 2.81          |                 | 3.19        |       | 3.54 |      | ns   |  |

| t <sub>INHBIDIR</sub>      | 0.00          |                 | 0.00        |       | 0.00 |      | ns   |  |

| t <sub>outcobidir</sub>    | 2.00          | 5.12            | 2.00        | 5.62  | 2.00 | 6.11 | ns   |  |

| t <sub>XZBIDIR</sub>       |               | 7.51            |             | 8.32  |      | 8.67 | ns   |  |

| t <sub>ZXBIDIR</sub>       |               | 7.51            |             | 8.32  |      | 8.67 | ns   |  |

| t <sub>insubidirpll</sub>  | 3.30          |                 | 3.64        |       | -    |      | ns   |  |

| t <sub>inhbidirpll</sub>   | 0.00          |                 | 0.00        |       | -    |      | ns   |  |

| t <sub>outcobidirpll</sub> | 0.50          | 3.01            | 0.50        | 3.36  | -    | -    | ns   |  |

| t <sub>XZBIDIRPLL</sub>    |               | 5.40            |             | 6.05  |      | -    | ns   |  |

| t <sub>ZXBIDIRPLL</sub>    |               | 5.40            |             | 6.05  |      | -    | ns   |  |

Tables 79 through 84 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K300E APEX 20KE devices.

| Table 79. EP20K300E f <sub>MAX</sub> LE Timing Microparameters |          |      |      |      |      |      |      |  |  |  |

|----------------------------------------------------------------|----------|------|------|------|------|------|------|--|--|--|

| Symbol                                                         | Symbol · |      | -    | 2    | -;   | 3    | Unit |  |  |  |

|                                                                | Min      | Max  | Min  | Max  | Min  | Max  |      |  |  |  |

| t <sub>SU</sub>                                                | 0.16     |      | 0.17 |      | 0.18 |      | ns   |  |  |  |

| t <sub>H</sub>                                                 | 0.31     |      | 0.33 |      | 0.38 |      | ns   |  |  |  |

| t <sub>CO</sub>                                                |          | 0.28 |      | 0.38 |      | 0.51 | ns   |  |  |  |

| t <sub>LUT</sub>                                               |          | 0.79 |      | 1.07 |      | 1.43 | ns   |  |  |  |

| Symbol                     | -1 Speed Grade |      | -2 Spee | d Grade | -3 Spee | Unit |    |

|----------------------------|----------------|------|---------|---------|---------|------|----|

| -                          | Min            | Max  | Min     | Max     | Min     | Max  | 1  |

| t <sub>insubidir</sub>     | 2.93           |      | 3.23    |         | 3.44    |      | ns |

| t <sub>inhbidir</sub>      | 0.00           |      | 0.00    |         | 0.00    |      | ns |

| toutcobidir                | 2.00           | 5.25 | 2.00    | 5.79    | 2.00    | 6.32 | ns |

| t <sub>XZBIDIR</sub>       |                | 5.95 |         | 6.77    |         | 7.12 | ns |

| t <sub>zxbidir</sub>       |                | 5.95 |         | 6.77    |         | 7.12 | ns |

| t <sub>insubidirpll</sub>  | 4.31           |      | 4.76    |         | -       |      | ns |

| t <sub>inhbidirpll</sub>   | 0.00           |      | 0.00    |         | -       |      | ns |

| t <sub>outcobidirpll</sub> | 0.50           | 2.25 | 0.50    | 2.45    | -       | -    | ns |

| t <sub>xzbidirpll</sub>    |                | 2.94 |         | 3.43    |         | -    | ns |

| t <sub>zxbidirpll</sub>    |                | 2.94 |         | 3.43    |         | -    | ns |

Tables 91 through 96 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K600E APEX 20KE devices.

| Table 91. EP20K600E f <sub>MAX</sub> LE Timing Microparameters |         |         |                    |      |         |         |      |  |  |  |

|----------------------------------------------------------------|---------|---------|--------------------|------|---------|---------|------|--|--|--|

| Symbol                                                         | -1 Spee | d Grade | ade -2 Speed Grade |      | -3 Spee | d Grade | Unit |  |  |  |

|                                                                | Min     | Max     | Min                | Max  | Min     | Max     |      |  |  |  |

| t <sub>SU</sub>                                                | 0.16    |         | 0.16               |      | 0.17    |         | ns   |  |  |  |

| t <sub>H</sub>                                                 | 0.29    |         | 0.33               |      | 0.37    |         | ns   |  |  |  |

| t <sub>CO</sub>                                                |         | 0.65    |                    | 0.38 |         | 0.49    | ns   |  |  |  |

| t <sub>LUT</sub>                                               |         | 0.70    |                    | 1.00 |         | 1.30    | ns   |  |  |  |

Т

| Symbol                  | -1 Spee | d Grade | -2 Spee | ed Grade | -3 Spee | d Grade | Unit |

|-------------------------|---------|---------|---------|----------|---------|---------|------|

|                         | Min     | Max     | Min     | Max      | Min     | Max     |      |

| t <sub>ESBARC</sub>     |         | 1.67    |         | 2.39     |         | 3.11    | ns   |

| t <sub>ESBSRC</sub>     |         | 2.27    |         | 3.07     |         | 3.86    | ns   |

| t <sub>ESBAWC</sub>     |         | 3.19    |         | 4.56     |         | 5.93    | ns   |

| t <sub>ESBSWC</sub>     |         | 3.51    |         | 4.62     |         | 5.72    | ns   |

| t <sub>ESBWASU</sub>    | 1.46    |         | 2.08    |          | 2.70    |         | ns   |

| t <sub>ESBWAH</sub>     | 0.00    |         | 0.00    |          | 0.00    |         | ns   |

| t <sub>ESBWDSU</sub>    | 1.60    |         | 2.29    |          | 2.97    |         | ns   |

| t <sub>ESBWDH</sub>     | 0.00    |         | 0.00    |          | 0.00    |         | ns   |

| t <sub>ESBRASU</sub>    | 1.61    |         | 2.30    |          | 2.99    |         | ns   |

| t <sub>ESBRAH</sub>     | 0.00    |         | 0.00    |          | 0.00    |         | ns   |

| t <sub>ESBWESU</sub>    | 1.49    |         | 2.30    |          | 3.11    |         | ns   |

| t <sub>ESBWEH</sub>     | 0.00    |         | 0.00    |          | 0.00    |         | ns   |

| t <sub>ESBDATASU</sub>  | -0.01   |         | 0.35    |          | 0.71    |         | ns   |

| t <sub>ESBDATAH</sub>   | 0.13    |         | 0.13    |          | 0.13    |         | ns   |

| t <sub>ESBWADDRSU</sub> | 0.19    |         | 0.62    |          | 1.06    |         | ns   |

| t <sub>ESBRADDRSU</sub> | 0.25    |         | 0.71    |          | 1.17    |         | ns   |

| t <sub>ESBDATACO1</sub> |         | 1.01    |         | 1.19     |         | 1.37    | ns   |

| t <sub>ESBDATACO2</sub> |         | 2.18    |         | 3.12     |         | 4.05    | ns   |

| t <sub>ESBDD</sub>      |         | 3.19    |         | 4.56     |         | 5.93    | ns   |

| t <sub>PD</sub>         |         | 1.57    |         | 2.25     |         | 2.92    | ns   |

| t <sub>PTERMSU</sub>    | 0.85    |         | 1.43    |          | 2.01    |         | ns   |

| t <sub>PTERMCO</sub>    |         | 1.03    |         | 1.21     |         | 1.39    | ns   |

| Table 93. EP2      | Table 93. EP20K600E f <sub>MAX</sub> Routing Delays |          |        |          |         |         |      |  |  |  |  |  |

|--------------------|-----------------------------------------------------|----------|--------|----------|---------|---------|------|--|--|--|--|--|

| Symbol             | -1 Spee                                             | ed Grade | -2 Spe | ed Grade | -3 Spee | d Grade | Unit |  |  |  |  |  |

|                    | Min                                                 | Max      | Min    | Max      | Min     | Мах     |      |  |  |  |  |  |

| t <sub>F1-4</sub>  |                                                     | 0.22     |        | 0.25     |         | 0.26    | ns   |  |  |  |  |  |

| t <sub>F5-20</sub> |                                                     | 1.26     |        | 1.39     |         | 1.52    | ns   |  |  |  |  |  |

| t <sub>F20+</sub>  |                                                     | 3.51     |        | 3.88     |         | 4.26    | ns   |  |  |  |  |  |

| Symbol                     | -1 Speed Grade |      | -2 Spee | d Grade | -3 Spee | Unit |    |

|----------------------------|----------------|------|---------|---------|---------|------|----|

|                            | Min            | Max  | Min     | Max     | Min     | Max  |    |

| t <sub>insubidir</sub>     | 3.22           |      | 3.33    |         | 3.51    |      | ns |

| t <sub>inhbidir</sub>      | 0.00           |      | 0.00    |         | 0.00    |      | ns |

| t <sub>outcobidir</sub>    | 2.00           | 5.75 | 2.00    | 6.33    | 2.00    | 6.90 | ns |

| t <sub>xzbidir</sub>       |                | 6.31 |         | 7.09    |         | 7.76 | ns |

| t <sub>ZXBIDIR</sub>       |                | 6.31 |         | 7.09    |         | 7.76 | ns |

| t <sub>insubidirpl</sub> L | 3.25           |      | 3.26    |         |         |      | ns |

| t <sub>inhbidirpll</sub>   | 0.00           |      | 0.00    |         |         |      | ns |

| toutcobidirpll             | 0.50           | 2.25 | 0.50    | 2.99    |         |      | ns |

| t <sub>xzbidirpll</sub>    |                | 2.81 |         | 3.80    |         |      | ns |

| t <sub>zxbidirpll</sub>    |                | 2.81 |         | 3.80    |         |      | ns |

Tables 103 through 108 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K1500E APEX 20KE devices.

| Table 103. EP20K1500E f <sub>MAX</sub> LE Timing Microparameters |         |         |                      |      |         |         |      |  |  |  |

|------------------------------------------------------------------|---------|---------|----------------------|------|---------|---------|------|--|--|--|

| Symbol                                                           | -1 Spee | d Grade | Grade -2 Speed Grade |      | -3 Spee | d Grade | Unit |  |  |  |

|                                                                  | Min     | Max     | Min                  | Max  | Min     | Max     |      |  |  |  |

| t <sub>SU</sub>                                                  | 0.25    |         | 0.25                 |      | 0.25    |         | ns   |  |  |  |

| t <sub>H</sub>                                                   | 0.25    |         | 0.25                 |      | 0.25    |         | ns   |  |  |  |

| t <sub>co</sub>                                                  |         | 0.28    |                      | 0.32 |         | 0.33    | ns   |  |  |  |

| t <sub>LUT</sub>                                                 |         | 0.80    |                      | 0.95 |         | 1.13    | ns   |  |  |  |

Т

# Version 4.1

APEX 20K Programmable Logic Device Family Data Sheet version 4.1 contains the following changes:

- *t*<sub>ESBWEH</sub> added to Figure 37 and Tables 35, 50, 56, 62, 68, 74, 86, 92, 97, and 104.

- Updated EP20K300E device internal and external timing numbers in Tables 79 through 84.