Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 832                                                         |

| Number of Logic Elements/Cells | 8320                                                        |

| Total RAM Bits                 | 106496                                                      |

| Number of I/O                  | 382                                                         |

| Number of Gates                | 526000                                                      |

| Voltage - Supply               | 2.375V ~ 2.625V                                             |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 484-BBGA                                                    |

| Supplier Device Package        | 484-FBGA (23x23)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep20k200fc484-3v |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# General Description

APEX<sup>TM</sup> 20K devices are the first PLDs designed with the MultiCore architecture, which combines the strengths of LUT-based and product-term-based devices with an enhanced memory structure. LUT-based logic provides optimized performance and efficiency for data-path, register-intensive, mathematical, or digital signal processing (DSP) designs. Product-term-based logic is optimized for complex combinatorial paths, such as complex state machines. LUT- and product-term-based logic combined with memory functions and a wide variety of MegaCore and AMPP functions make the APEX 20K device architecture uniquely suited for system-on-a-programmable-chip designs. Applications historically requiring a combination of LUT-, product-term-, and memory-based devices can now be integrated into one APEX 20K device.

APEX 20KE devices are a superset of APEX 20K devices and include additional features such as advanced I/O standard support, CAM, additional global clocks, and enhanced ClockLock clock circuitry. In addition, APEX 20KE devices extend the APEX 20K family to 1.5 million gates. APEX 20KE devices are denoted with an "E" suffix in the device name (e.g., the EP20K1000E device is an APEX 20KE device). Table 8 compares the features included in APEX 20K and APEX 20KE devices.

APEX 20K devices provide two dedicated clock pins and four dedicated input pins that drive register control inputs. These signals ensure efficient distribution of high-speed, low-skew control signals. These signals use dedicated routing channels to provide short delays and low skews. Four of the dedicated inputs drive four global signals. These four global signals can also be driven by internal logic, providing an ideal solution for a clock divider or internally generated asynchronous clear signals with high fan-out. The dedicated clock pins featured on the APEX 20K devices can also feed logic. The devices also feature ClockLock and ClockBoost clock management circuitry. APEX 20KE devices provide two additional dedicated clock pins, for a total of four dedicated clock pins.

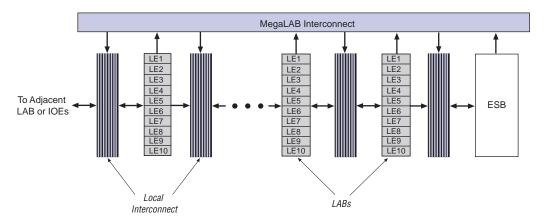

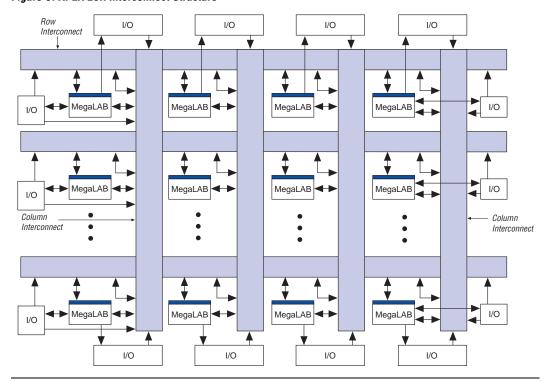

### MegaLAB Structure

APEX 20K devices are constructed from a series of MegaLAB<sup>TM</sup> structures. Each MegaLAB structure contains a group of logic array blocks (LABs), one ESB, and a MegaLAB interconnect, which routes signals within the MegaLAB structure. The EP20K30E device has 10 LABs, EP20K60E through EP20K600E devices have 16 LABs, and the EP20K1000E and EP20K1500E devices have 24 LABs. Signals are routed between MegaLAB structures and I/O pins via the FastTrack Interconnect. In addition, edge LABs can be driven by I/O pins through the local interconnect. Figure 2 shows the MegaLAB structure.

Figure 2. MegaLAB Structure

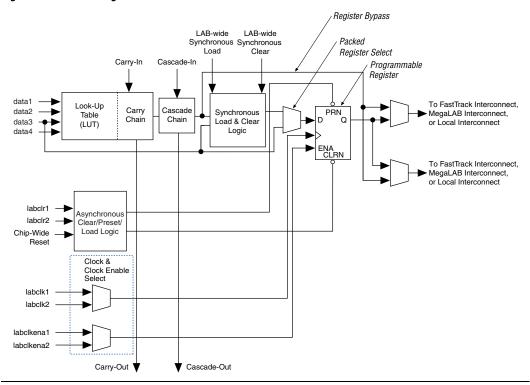

### Logic Element

The LE, the smallest unit of logic in the APEX 20K architecture, is compact and provides efficient logic usage. Each LE contains a four-input LUT, which is a function generator that can quickly implement any function of four variables. In addition, each LE contains a programmable register and carry and cascade chains. Each LE drives the local interconnect, MegaLAB interconnect, and FastTrack Interconnect routing structures. See Figure 5.

Figure 5. APEX 20K Logic Element

Each LE's programmable register can be configured for D, T, JK, or SR operation. The register's clock and clear control signals can be driven by global signals, general-purpose I/O pins, or any internal logic. For combinatorial functions, the register is bypassed and the output of the LUT drives the outputs of the LE.

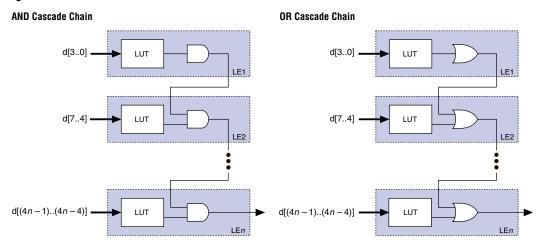

#### Cascade Chain

With the cascade chain, the APEX 20K architecture can implement functions with a very wide fan-in. Adjacent LUTs can compute portions of a function in parallel; the cascade chain serially connects the intermediate values. The cascade chain can use a logical AND or logical OR (via De Morgan's inversion) to connect the outputs of adjacent LEs. Each additional LE provides four more inputs to the effective width of a function, with a short cascade delay. Cascade chain logic can be created automatically by the Quartus II software Compiler during design processing, or manually by the designer during design entry.

Cascade chains longer than ten LEs are implemented automatically by linking LABs together. For enhanced fitting, a long cascade chain skips alternate LABs in a MegaLAB structure. A cascade chain longer than one LAB skips either from an even-numbered LAB to the next even-numbered LAB, or from an odd-numbered LAB to the next odd-numbered LAB. For example, the last LE of the first LAB in the upper-left MegaLAB structure carries to the first LE of the third LAB in the MegaLAB structure. Figure 7 shows how the cascade function can connect adjacent LEs to form functions with a wide fan-in.

Figure 7. APEX 20K Cascade Chain

Figure 9. APEX 20K Interconnect Structure

A row line can be driven directly by LEs, IOEs, or ESBs in that row. Further, a column line can drive a row line, allowing an LE, IOE, or ESB to drive elements in a different row via the column and row interconnect. The row interconnect drives the MegaLAB interconnect to drive LEs, IOEs, or ESBs in a particular MegaLAB structure.

A column line can be directly driven by LEs, IOEs, or ESBs in that column. A column line on a device's left or right edge can also be driven by row IOEs. The column line is used to route signals from one row to another. A column line can drive a row line; it can also drive the MegaLAB interconnect directly, allowing faster connections between rows.

Figure 10 shows how the FastTrack Interconnect uses the local interconnect to drive LEs within MegaLAB structures.

Select Vertical I/O Pins IOE IOE FastRow Interconnect IOE IOE Drive Local Interconnect FastRow Drives Local Interconnect and FastRow Interconnect in Two MegaLAB Structures Interconnect Local Interconnect LEs MegaLAB MegaLAB *LABs*

Figure 12. APEX 20KE FastRow Interconnect

Table 9 summarizes how various elements of the APEX 20K architecture drive each other.

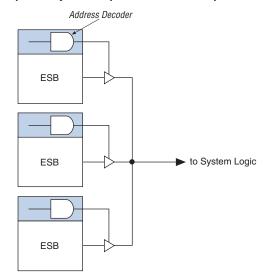

Figure 18. Deep Memory Block Implemented with Multiple ESBs

The ESB implements two forms of dual-port memory: read/write clock mode and input/output clock mode. The ESB can also be used for bidirectional, dual-port memory applications in which two ports read or write simultaneously. To implement this type of dual-port memory, two or four ESBs are used to support two simultaneous reads or writes. This functionality is shown in Figure 19.

Figure 19. APEX 20K ESB Implementing Dual-Port RAM

#### Read/Write Clock Mode

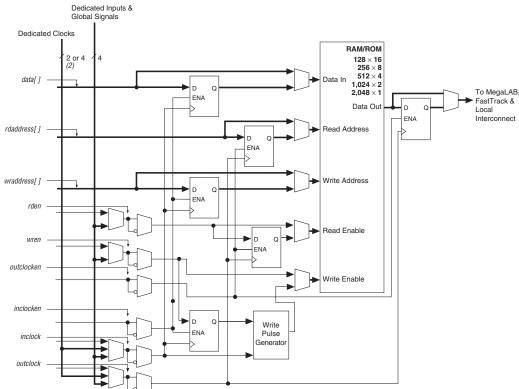

The read/write clock mode contains two clocks. One clock controls all registers associated with writing: data input, WE, and write address. The other clock controls all registers associated with reading: read enable (RE), read address, and data output. The ESB also supports clock enable and asynchronous clear signals; these signals also control the read and write registers independently. Read/write clock mode is commonly used for applications where reads and writes occur at different system frequencies. Figure 20 shows the ESB in read/write clock mode.

Figure 20. ESB in Read/Write Clock Mode Note (1)

Notes to Figure 20:

(1) All registers can be cleared asynchronously by ESB local interconnect signals, global signals, or the chip-wide reset.

(2) APEX 20KE devices have four dedicated clocks.

Under hot socketing conditions, APEX 20KE devices will not sustain any damage, but the I/O pins will drive out.

# MultiVolt I/O Interface

The APEX device architecture supports the MultiVolt I/O interface feature, which allows APEX devices in all packages to interface with systems of different supply voltages. The devices have one set of VCC pins for internal operation and input buffers (VCCINT), and another set for I/O output drivers (VCCIO).

The APEX 20K VCCINT pins must always be connected to a 2.5 V power supply. With a 2.5-V  $V_{CCINT}$  level, input pins are 2.5-V, 3.3-V, and 5.0-V tolerant. The VCCIO pins can be connected to either a 2.5-V or 3.3-V power supply, depending on the output requirements. When VCCIO pins are connected to a 2.5-V power supply, the output levels are compatible with 2.5-V systems. When the VCCIO pins are connected to a 3.3-V power supply, the output high is 3.3 V and is compatible with 3.3-V or 5.0-V systems.

| Table 12. 5.0-V Tolerant APEX 20K MultiVolt I/O Support |                                      |              |              |              |     |     |  |  |  |

|---------------------------------------------------------|--------------------------------------|--------------|--------------|--------------|-----|-----|--|--|--|

| V <sub>CCIO</sub> (V)                                   | Input Signals (V) Output Signals (V) |              |              |              |     |     |  |  |  |

|                                                         | 2.5                                  | 3.3          | 5.0          | 2.5          | 3.3 | 5.0 |  |  |  |

| 2.5                                                     | ✓                                    | <b>√</b> (1) | <b>√</b> (1) | ✓            |     |     |  |  |  |

| 3.3                                                     | <b>✓</b>                             | ✓            | <b>√</b> (1) | <b>√</b> (2) | ✓   | ✓   |  |  |  |

#### Notes to Table 12:

- (1) The PCI clamping diode must be disabled to drive an input with voltages higher than  $V_{\text{CCIO}}$ .

- (2) When  $V_{\rm CCIO}$  = 3.3 V, an APEX 20K device can drive a 2.5-V device with 3.3-V tolerant inputs.

Open-drain output pins on 5.0-V tolerant APEX 20K devices (with a pull-up resistor to the 5.0-V supply) can drive 5.0-V CMOS input pins that require a  $V_{\rm IH}$  of 3.5 V. When the pin is inactive, the trace will be pulled up to 5.0 V by the resistor. The open-drain pin will only drive low or tri-state; it will never drive high. The rise time is dependent on the value of the pull-up resistor and load impedance. The  $I_{\rm OL}$  current specification should be considered when selecting a pull-up resistor.

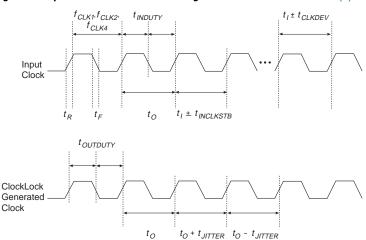

Figure 30. Specifications for the Incoming & Generated Clocks Note (1)

*Note to Figure 30:*

(1) The tl parameter refers to the nominal input clock period; the tO parameter refers to the nominal output clock period.

Table 15 summarizes the APEX 20K ClockLock and ClockBoost parameters for -1 speed-grade devices.

| Symbol                | Symbol Parameter                                                                                                         |    | Max        | Unit |  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------|----|------------|------|--|

| f <sub>OUT</sub>      | Output frequency                                                                                                         | 25 | 180        | MHz  |  |

| f <sub>CLK1</sub> (1) | Input clock frequency (ClockBoost clock multiplication factor equals 1)                                                  | 25 | 180 (1)    | MHz  |  |

| f <sub>CLK2</sub>     | Input clock frequency (ClockBoost clock multiplication factor equals 2)                                                  | 16 | 90         | MHz  |  |

| f <sub>CLK4</sub>     | Input clock frequency (ClockBoost clock multiplication factor equals 4)                                                  | 10 | 48         | MHz  |  |

| <sup>t</sup> OUTDUTY  | Duty cycle for ClockLock/ClockBoost-generated clock                                                                      | 40 | 60         | %    |  |

| f <sub>CLKDEV</sub>   | Input deviation from user specification in the Quartus II software (ClockBoost clock multiplication factor equals 1) (2) |    | 25,000 (3) | PPM  |  |

| t <sub>R</sub>        | Input rise time                                                                                                          |    | 5          | ns   |  |

| t <sub>F</sub>        | Input fall time                                                                                                          |    | 5          | ns   |  |

| t <sub>LOCK</sub>     | Time required for ClockLock/ClockBoost to acquire lock (4)                                                               |    | 10         | μs   |  |

## IEEE Std. 1149.1 (JTAG) Boundary-Scan Support

All APEX 20K devices provide JTAG BST circuitry that complies with the IEEE Std. 1149.1-1990 specification. JTAG boundary-scan testing can be performed before or after configuration, but not during configuration. APEX 20K devices can also use the JTAG port for configuration with the Quartus II software or with hardware using either Jam Files (.jam) or Jam Byte-Code Files (.jbc). Finally, APEX 20K devices use the JTAG port to monitor the logic operation of the device with the SignalTap embedded logic analyzer. APEX 20K devices support the JTAG instructions shown in Table 19. Although EP20K1500E devices support the JTAG BYPASS and SignalTap instructions, they do not support boundary-scan testing or the use of the JTAG port for configuration.

| Table 19. APEX 20K JT      | AG Instructions                                                                                                                                                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTAG Instruction           | Description                                                                                                                                                                                                                          |

| SAMPLE/PRELOAD             | Allows a snapshot of signals at the device pins to be captured and examined during normal device operation, and permits an initial data pattern to be output at the device pins. Also used by the SignalTap embedded logic analyzer. |

| EXTEST                     | Allows the external circuitry and board-level interconnections to be tested by forcing a test pattern at the output pins and capturing test results at the input pins.                                                               |

| BYPASS (1)                 | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation.                                          |

| USERCODE                   | Selects the 32-bit USERCODE register and places it between the TDI and TDO pins, allowing the USERCODE to be serially shifted out of TDO.                                                                                            |

| IDCODE                     | Selects the IDCODE register and places it between TDI and TDO, allowing the IDCODE to be serially shifted out of TDO.                                                                                                                |

| ICR Instructions           | Used when configuring an APEX 20K device via the JTAG port with a MasterBlaster <sup>TM</sup> or ByteBlasterMV <sup>TM</sup> download cable, or when using a Jam File or Jam Byte-Code File via an embedded processor.               |

| SignalTap Instructions (1) | Monitors internal device operation with the SignalTap embedded logic analyzer.                                                                                                                                                       |

#### Note to Table 19:

(1) The EP20K1500E device supports the JTAG BYPASS instruction and the SignalTap instructions.

Table 22 shows the JTAG timing parameters and values for APEX 20K devices

| Table 2           | 2. APEX 20K JTAG Timing Parameters & Values    |     |     |      |

|-------------------|------------------------------------------------|-----|-----|------|

| Symbol            | Parameter                                      | Min | Max | Unit |

| t <sub>JCP</sub>  | TCK clock period                               | 100 |     | ns   |

| t <sub>JCH</sub>  | TCK clock high time                            | 50  |     | ns   |

| $t_{JCL}$         | TCK clock low time                             | 50  |     | ns   |

| t <sub>JPSU</sub> | JTAG port setup time                           | 20  |     | ns   |

| t <sub>JPH</sub>  | JTAG port hold time                            | 45  |     | ns   |

| t <sub>JPCO</sub> | JTAG port clock to output                      |     | 25  | ns   |

| t <sub>JPZX</sub> | JTAG port high impedance to valid output       |     | 25  | ns   |

| t <sub>JPXZ</sub> | JTAG port valid output to high impedance       |     | 25  | ns   |

| t <sub>JSSU</sub> | Capture register setup time                    | 20  |     | ns   |

| t <sub>JSH</sub>  | Capture register hold time                     | 45  |     | ns   |

| t <sub>JSCO</sub> | Update register clock to output                |     | 35  | ns   |

| t <sub>JSZX</sub> | Update register high impedance to valid output |     | 35  | ns   |

| t <sub>JSXZ</sub> | Update register valid output to high impedance |     | 35  | ns   |

For more information, see the following documents:

- Application Note 39 (IEEE Std. 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices)

- Jam Programming & Test Language Specification

## **Generic Testing**

Each APEX 20K device is functionally tested. Complete testing of each configurable static random access memory (SRAM) bit and all logic functionality ensures 100% yield. AC test measurements for APEX 20K devices are made under conditions equivalent to those shown in Figure 32. Multiple test patterns can be used to configure devices during all stages of the production flow.

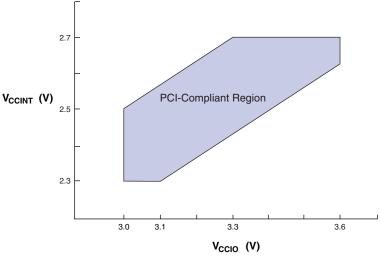

Figure 33. Relationship between  $V_{CCIO}$  &  $V_{CCINT}$  for 3.3-V PCI Compliance

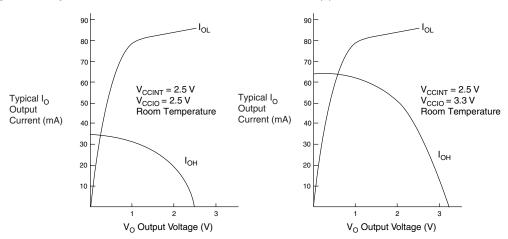

Figure 34 shows the typical output drive characteristics of APEX 20K devices with 3.3-V and 2.5-V  $V_{\rm CCIO}$ . The output driver is compatible with the 3.3-V *PCI Local Bus Specification, Revision 2.2* (when VCCIO pins are connected to 3.3 V). 5-V tolerant APEX 20K devices in the -1 speed grade are 5-V PCI compliant over all operating conditions.

Figure 34. Output Drive Characteristics of APEX 20K Device Note (1)

Note to Figure 34:

(1) These are transient (AC) currents.

#### Notes to Tables 43 through 48:

- (1) This parameter is measured without using ClockLock or ClockBoost circuits.

- (2) This parameter is measured using ClockLock or ClockBoost circuits.

Tables 49 through 54 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K30E APEX 20KE devices.

| Table 49. EP20K30E f <sub>MAX</sub> LE Timing Microparameters |      |      |      |      |      |      |      |  |  |  |

|---------------------------------------------------------------|------|------|------|------|------|------|------|--|--|--|

| Symbol                                                        | _    | 1    | -    | 2    | -3   |      | Unit |  |  |  |

|                                                               | Min  | Max  | Min  | Max  | Min  | Max  | 7    |  |  |  |

| t <sub>SU</sub>                                               | 0.01 |      | 0.02 |      | 0.02 |      | ns   |  |  |  |

| t <sub>H</sub>                                                | 0.11 |      | 0.16 |      | 0.23 |      | ns   |  |  |  |

| t <sub>CO</sub>                                               |      | 0.32 |      | 0.45 |      | 0.67 | ns   |  |  |  |

| t <sub>LUT</sub>                                              |      | 0.85 |      | 1.20 |      | 1.77 | ns   |  |  |  |

| Symbol                  | -    | 1    | -    | -2   | -3   |      | Unit |

|-------------------------|------|------|------|------|------|------|------|

|                         | Min  | Max  | Min  | Max  | Min  | Max  |      |

| t <sub>ESBARC</sub>     |      | 1.83 |      | 2.57 |      | 3.79 | ns   |

| t <sub>ESBSRC</sub>     |      | 2.46 |      | 3.26 |      | 4.61 | ns   |

| t <sub>ESBAWC</sub>     |      | 3.50 |      | 4.90 |      | 7.23 | ns   |

| t <sub>ESBSWC</sub>     |      | 3.77 |      | 4.90 |      | 6.79 | ns   |

| t <sub>ESBWASU</sub>    | 1.59 |      | 2.23 |      | 3.29 |      | ns   |

| t <sub>ESBWAH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>ESBWDSU</sub>    | 1.75 |      | 2.46 |      | 3.62 |      | ns   |

| t <sub>ESBWDH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>ESBRASU</sub>    | 1.76 |      | 2.47 |      | 3.64 |      | ns   |

| t <sub>ESBRAH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>ESBWESU</sub>    | 1.68 |      | 2.49 |      | 3.87 |      | ns   |

| t <sub>ESBWEH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>ESBDATASU</sub>  | 0.08 |      | 0.43 |      | 1.04 |      | ns   |

| t <sub>ESBDATAH</sub>   | 0.13 |      | 0.13 |      | 0.13 |      | ns   |

| t <sub>ESBWADDRSU</sub> | 0.29 |      | 0.72 |      | 1.46 |      | ns   |

| t <sub>ESBRADDRSU</sub> | 0.36 |      | 0.81 |      | 1.58 |      | ns   |

| t <sub>ESBDATACO1</sub> |      | 1.06 |      | 1.24 |      | 1.55 | ns   |

| t <sub>ESBDATACO2</sub> |      | 2.39 |      | 3.35 |      | 4.94 | ns   |

| t <sub>ESBDD</sub>      |      | 3.50 |      | 4.90 |      | 7.23 | ns   |

| t <sub>PD</sub>         |      | 1.72 |      | 2.41 |      | 3.56 | ns   |

| t <sub>PTERMSU</sub>    | 0.99 |      | 1.56 |      | 2.55 |      | ns   |

| t <sub>PTERMCO</sub>    |      | 1.07 |      | 1.26 |      | 1.08 | ns   |

| Table 62. EP20K         | I GOL IMAX LOL | , iming mid | 1     |      | Ī     |      | 1    |

|-------------------------|----------------|-------------|-------|------|-------|------|------|

| Symbol                  | -              | 1           |       | -2   |       | 3    | Unit |

|                         | Min            | Max         | Min   | Max  | Min   | Max  |      |

| t <sub>ESBARC</sub>     |                | 1.61        |       | 1.84 |       | 1.97 | ns   |

| t <sub>ESBSRC</sub>     |                | 2.57        |       | 2.97 |       | 3.20 | ns   |

| t <sub>ESBAWC</sub>     |                | 0.52        |       | 4.09 |       | 4.39 | ns   |

| t <sub>ESBSWC</sub>     |                | 3.17        |       | 3.78 |       | 4.09 | ns   |

| t <sub>ESBWASU</sub>    | 0.56           |             | 6.41  |      | 0.63  |      | ns   |

| t <sub>ESBWAH</sub>     | 0.48           |             | 0.54  |      | 0.55  |      | ns   |

| t <sub>ESBWDSU</sub>    | 0.71           |             | 0.80  |      | 0.81  |      | ns   |

| t <sub>ESBWDH</sub>     | .048           |             | 0.54  |      | 0.55  |      | ns   |

| t <sub>ESBRASU</sub>    | 1.57           |             | 1.75  |      | 1.87  |      | ns   |

| t <sub>ESBRAH</sub>     | 0.00           |             | 0.00  |      | 0.20  |      | ns   |

| t <sub>ESBWESU</sub>    | 1.54           |             | 1.72  |      | 1.80  |      | ns   |

| t <sub>ESBWEH</sub>     | 0.00           |             | 0.00  |      | 0.00  |      | ns   |

| t <sub>ESBDATASU</sub>  | -0.16          |             | -0.20 |      | -0.20 |      | ns   |

| t <sub>ESBDATAH</sub>   | 0.13           |             | 0.13  |      | 0.13  |      | ns   |

| t <sub>ESBWADDRSU</sub> | 0.12           |             | 0.08  |      | 0.13  |      | ns   |

| t <sub>ESBRADDRSU</sub> | 0.17           |             | 0.15  |      | 0.19  |      | ns   |

| t <sub>ESBDATACO1</sub> |                | 1.20        |       | 1.39 |       | 1.52 | ns   |

| t <sub>ESBDATACO2</sub> |                | 2.54        |       | 2.99 |       | 3.22 | ns   |

| t <sub>ESBDD</sub>      |                | 3.06        |       | 3.56 |       | 3.85 | ns   |

| t <sub>PD</sub>         |                | 1.73        |       | 2.02 |       | 2.20 | ns   |

| t <sub>PTERMSU</sub>    | 1.11           |             | 1.26  |      | 1.38  |      | ns   |

| t <sub>PTERMCO</sub>    |                | 1.19        |       | 1.40 |       | 1.08 | ns   |

| Table 63. EP20K100E f <sub>MAX</sub> Routing Delays |     |      |     |      |     |      |      |  |  |  |

|-----------------------------------------------------|-----|------|-----|------|-----|------|------|--|--|--|

| Symbol                                              | -   | 1    | -2  |      |     | 3    | Unit |  |  |  |

|                                                     | Min | Max  | Min | Max  | Min | Max  |      |  |  |  |

| t <sub>F1-4</sub>                                   |     | 0.24 |     | 0.27 |     | 0.29 | ns   |  |  |  |

| t <sub>F5-20</sub>                                  |     | 1.04 |     | 1.26 |     | 1.52 | ns   |  |  |  |

| t <sub>F20+</sub>                                   |     | 1.12 |     | 1.36 |     | 1.86 | ns   |  |  |  |

| Symbol                    | -1   |      | -2   |      | -3   |      | Unit |

|---------------------------|------|------|------|------|------|------|------|

|                           | Min  | Max  | Min  | Max  | Min  | Max  |      |

| t <sub>INSUBIDIR</sub>    | 2.81 |      | 3.19 |      | 3.54 |      | ns   |

| t <sub>INHBIDIR</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| toutcobidir               | 2.00 | 5.12 | 2.00 | 5.62 | 2.00 | 6.11 | ns   |

| t <sub>XZBIDIR</sub>      |      | 7.51 |      | 8.32 |      | 8.67 | ns   |

| tzxbidir                  |      | 7.51 |      | 8.32 |      | 8.67 | ns   |

| t <sub>INSUBIDIRPLL</sub> | 3.30 |      | 3.64 |      | -    |      | ns   |

| t <sub>INHBIDIRPLL</sub>  | 0.00 |      | 0.00 |      | -    |      | ns   |

| toutcobidirpll            | 0.50 | 3.01 | 0.50 | 3.36 | -    | -    | ns   |

| t <sub>XZBIDIRPLL</sub>   |      | 5.40 |      | 6.05 |      | -    | ns   |

| tzxbidirpll               |      | 5.40 |      | 6.05 |      | -    | ns   |

Tables 79 through 84 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K300E APEX 20KE devices.

| Table 79. EP20K300E f <sub>MAX</sub> LE Timing Microparameters |      |      |      |      |      |      |      |  |  |  |

|----------------------------------------------------------------|------|------|------|------|------|------|------|--|--|--|

| Symbol                                                         | -    | 1    | -2   |      | -3   |      | Unit |  |  |  |

|                                                                | Min  | Max  | Min  | Max  | Min  | Max  |      |  |  |  |

| t <sub>SU</sub>                                                | 0.16 |      | 0.17 |      | 0.18 |      | ns   |  |  |  |

| t <sub>H</sub>                                                 | 0.31 |      | 0.33 |      | 0.38 |      | ns   |  |  |  |

| t <sub>CO</sub>                                                |      | 0.28 |      | 0.38 |      | 0.51 | ns   |  |  |  |

| t <sub>LUT</sub>                                               |      | 0.79 |      | 1.07 |      | 1.43 | ns   |  |  |  |

| Symbol             | -1 Speed Grade |     | -2 Speed | d Grade | -3 Speed | Unit |    |

|--------------------|----------------|-----|----------|---------|----------|------|----|

|                    | Min            | Max | Min      | Max     | Min      | Max  |    |

| t <sub>CH</sub>    | 1.25           |     | 1.43     |         | 1.67     |      | ns |

| t <sub>CL</sub>    | 1.25           |     | 1.43     |         | 1.67     |      | ns |

| t <sub>CLRP</sub>  | 0.20           |     | 0.20     |         | 0.20     |      | ns |

| t <sub>PREP</sub>  | 0.20           |     | 0.20     |         | 0.20     |      | ns |

| t <sub>ESBCH</sub> | 1.25           |     | 1.43     |         | 1.67     |      | ns |

| t <sub>ESBCL</sub> | 1.25           |     | 1.43     |         | 1.67     |      | ns |

| t <sub>ESBWP</sub> | 1.28           |     | 1.51     |         | 1.65     |      | ns |

| t <sub>ESBRP</sub> | 1.11           |     | 1.29     |         | 1.41     |      | ns |

| Symbol                | -1 Speed Grade |      | -2 Speed Grade |      | -3 Speed Grade |      | Unit |

|-----------------------|----------------|------|----------------|------|----------------|------|------|

|                       | Min            | Max  | Min            | Max  | Min            | Max  | 1    |

| t <sub>INSU</sub>     | 3.09           |      | 3.30           |      | 3.58           |      | ns   |

| t <sub>INH</sub>      | 0.00           |      | 0.00           |      | 0.00           |      | ns   |

| t <sub>OUTCO</sub>    | 2.00           | 6.18 | 2.00           | 6.81 | 2.00           | 7.36 | ns   |

| t <sub>INSUPLL</sub>  | 1.94           |      | 2.08           |      | -              |      | ns   |

| t <sub>INHPLL</sub>   | 0.00           |      | 0.00           |      | -              |      | ns   |

| t <sub>OUTCOPLL</sub> | 0.50           | 2.67 | 0.50           | 2.99 | -              | -    | ns   |

| Symbol                    | -1 Speed Grade |      | -2 Spee | d Grade | -3 Spee | Unit |    |

|---------------------------|----------------|------|---------|---------|---------|------|----|

|                           | Min            | Max  | Min     | Max     | Min     | Max  | 1  |

| t <sub>INSUBIDIR</sub>    | 3.47           |      | 3.68    |         | 3.99    |      | ns |

| t <sub>INHBIDIR</sub>     | 0.00           |      | 0.00    |         | 0.00    |      | ns |

| toutcobidir               | 2.00           | 6.18 | 2.00    | 6.81    | 2.00    | 7.36 | ns |

| t <sub>XZBIDIR</sub>      |                | 6.91 |         | 7.62    |         | 8.38 | ns |

| t <sub>ZXBIDIR</sub>      |                | 6.91 |         | 7.62    |         | 8.38 | ns |

| t <sub>INSUBIDIRPLL</sub> | 3.05           |      | 3.26    |         |         |      | ns |

| t <sub>INHBIDIRPLL</sub>  | 0.00           |      | 0.00    |         |         |      | ns |

| toutcobidirpll            | 0.50           | 2.67 | 0.50    | 2.99    |         |      | ns |

| t <sub>XZBIDIRPLL</sub>   |                | 3.41 |         | 3.80    |         |      | ns |

| tzxbidirpll               |                | 3.41 |         | 3.80    |         |      | ns |

Tables 109 and 110 show selectable I/O standard input and output delays for APEX 20KE devices. If you select an I/O standard input or output delay other than LVCMOS, add or subtract the selected speed grade to or from the LVCMOS value.

| Table 109. Selectab | le I/O Standa  | ard Input Dela | ays            |       |                |       |      |  |

|---------------------|----------------|----------------|----------------|-------|----------------|-------|------|--|

| Symbol              | -1 Speed Grade |                | -2 Speed Grade |       | -3 Speed Grade |       | Unit |  |

|                     | Min            | Max            | Min            | Max   | Min            | Max   | Min  |  |

| LVCMOS              |                | 0.00           |                | 0.00  |                | 0.00  | ns   |  |

| LVTTL               |                | 0.00           |                | 0.00  |                | 0.00  | ns   |  |

| 2.5 V               |                | 0.00           |                | 0.04  |                | 0.05  | ns   |  |

| 1.8 V               |                | -0.11          |                | 0.03  |                | 0.04  | ns   |  |

| PCI                 |                | 0.01           |                | 0.09  |                | 0.10  | ns   |  |

| GTL+                |                | -0.24          |                | -0.23 |                | -0.19 | ns   |  |

| SSTL-3 Class I      |                | -0.32          |                | -0.21 |                | -0.47 | ns   |  |

| SSTL-3 Class II     |                | -0.08          |                | 0.03  |                | -0.23 | ns   |  |

| SSTL-2 Class I      |                | -0.17          |                | -0.06 |                | -0.32 | ns   |  |

| SSTL-2 Class II     |                | -0.16          |                | -0.05 |                | -0.31 | ns   |  |

| LVDS                |                | -0.12          |                | -0.12 |                | -0.12 | ns   |  |

| CTT                 |                | 0.00           |                | 0.00  |                | 0.00  | ns   |  |

| AGP                 |                | 0.00           |                | 0.00  |                | 0.00  | ns   |  |

| Table 110. Selectab | le I/O Standa  | ard Output De | lays           |       |                |       |      |  |

|---------------------|----------------|---------------|----------------|-------|----------------|-------|------|--|

| Symbol              | -1 Speed Grade |               | -2 Speed Grade |       | -3 Speed Grade |       | Unit |  |

|                     | Min            | Max           | Min            | Max   | Min            | Max   | Min  |  |

| LVCMOS              |                | 0.00          |                | 0.00  |                | 0.00  | ns   |  |

| LVTTL               |                | 0.00          |                | 0.00  |                | 0.00  | ns   |  |

| 2.5 V               |                | 0.00          |                | 0.09  |                | 0.10  | ns   |  |

| 1.8 V               |                | 2.49          |                | 2.98  |                | 3.03  | ns   |  |

| PCI                 |                | -0.03         |                | 0.17  |                | 0.16  | ns   |  |

| GTL+                |                | 0.75          |                | 0.75  |                | 0.76  | ns   |  |

| SSTL-3 Class I      |                | 1.39          |                | 1.51  |                | 1.50  | ns   |  |

| SSTL-3 Class II     |                | 1.11          |                | 1.23  |                | 1.23  | ns   |  |

| SSTL-2 Class I      |                | 1.35          |                | 1.48  |                | 1.47  | ns   |  |

| SSTL-2 Class II     |                | 1.00          |                | 1.12  |                | 1.12  | ns   |  |

| LVDS                |                | -0.48         |                | -0.48 |                | -0.48 | ns   |  |

| CTT                 |                | 0.00          |                | 0.00  |                | 0.00  | ns   |  |

| AGP                 |                | 0.00          |                | 0.00  |                | 0.00  | ns   |  |

# Power Consumption

To estimate device power consumption, use the interactive power calculator on the Altera web site at http://www.altera.com.

# Configuration & Operation

The APEX 20K architecture supports several configuration schemes. This section summarizes the device operating modes and available device configuration schemes.

### **Operating Modes**

The APEX architecture uses SRAM configuration elements that require configuration data to be loaded each time the circuit powers up. The process of physically loading the SRAM data into the device is called configuration. During initialization, which occurs immediately after configuration, the device resets registers, enables I/O pins, and begins to operate as a logic device. The I/O pins are tri-stated during power-up, and before and during configuration. Together, the configuration and initialization processes are called *command mode*; normal device operation is called *user mode*.

Before and during device configuration, all I/O pins are pulled to  $V_{\mbox{\scriptsize CCIO}}$  by a built-in weak pull-up resistor.