# E·XFL

# Intel - EP20K300EFC672-2X Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

## Details

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 1152                                                         |

| Number of Logic Elements/Cells | 11520                                                        |

| Total RAM Bits                 | 147456                                                       |

| Number of I/O                  | 408                                                          |

| Number of Gates                | 728000                                                       |

| Voltage - Supply               | $1.71V \sim 1.89V$                                           |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                              |

| Package / Case                 | 672-BBGA                                                     |

| Supplier Device Package        | 672-FBGA (27x27)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep20k300efc672-2x |

|                                |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 2. Additiona       | al APEX 20K De | vice Features | Note (1)  |           |            |            |

|--------------------------|----------------|---------------|-----------|-----------|------------|------------|

| Feature                  | EP20K300E      | EP20K400      | EP20K400E | EP20K600E | EP20K1000E | EP20K1500E |

| Maximum system gates     | 728,000        | 1,052,000     | 1,052,000 | 1,537,000 | 1,772,000  | 2,392,000  |

| Typical gates            | 300,000        | 400,000       | 400,000   | 600,000   | 1,000,000  | 1,500,000  |

| LEs                      | 11,520         | 16,640        | 16,640    | 24,320    | 38,400     | 51,840     |

| ESBs                     | 72             | 104           | 104       | 152       | 160        | 216        |

| Maximum<br>RAM bits      | 147,456        | 212,992       | 212,992   | 311,296   | 327,680    | 442,368    |

| Maximum<br>macrocells    | 1,152          | 1,664         | 1,664     | 2,432     | 2,560      | 3,456      |

| Maximum user I/O<br>pins | 408            | 502           | 488       | 588       | 708        | 808        |

#### Note to Tables 1 and 2:

The embedded IEEE Std. 1149.1 Joint Test Action Group (JTAG) boundary-scan circuitry contributes up to 57,000 additional gates.

Additional Features

- Designed for low-power operation

- 1.8-V and 2.5-V supply voltage (see Table 3)

- MultiVolt<sup>™</sup> I/O interface support to interface with 1.8-V, 2.5-V, 3.3-V, and 5.0-V devices (see Table 3)

- ESB offering programmable power-saving mode

| Feature                                                     | De                               | vice                                                                                                                           |

|-------------------------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

|                                                             | EP20K100<br>EP20K200<br>EP20K400 | EP20K30E<br>EP20K60E<br>EP20K100E<br>EP20K160E<br>EP20K200E<br>EP20K300E<br>EP20K400E<br>EP20K600E<br>EP20K1000E<br>EP20K1500E |

| Internal supply voltage (V <sub>CCINT</sub> )               | 2.5 V                            | 1.8 V                                                                                                                          |

| MultiVolt I/O interface voltage levels (V <sub>CCIO</sub> ) | 2.5 V, 3.3 V, 5.0 V              | 1.8 V, 2.5 V, 3.3 V, 5.0 V (1)                                                                                                 |

#### Note to Table 3:

(1) APEX 20KE devices can be 5.0-V tolerant by using an external resistor.

- Flexible clock management circuitry with up to four phase-locked loops (PLLs)

- Built-in low-skew clock tree

- Up to eight global clock signals

- ClockLock<sup>®</sup> feature reducing clock delay and skew

- ClockBoost<sup>®</sup> feature providing clock multiplication and division

- ClockShift<sup>TM</sup> programmable clock phase and delay shifting

- Powerful I/O features

- Compliant with peripheral component interconnect Special Interest Group (PCI SIG) *PCI Local Bus Specification, Revision 2.2* for 3.3-V operation at 33 or 66 MHz and 32 or 64 bits

- Support for high-speed external memories, including DDR SDRAM and ZBT SRAM (ZBT is a trademark of Integrated Device Technology, Inc.)

- Bidirectional I/O performance  $(t_{CO} + t_{SU})$  up to 250 MHz

- LVDS performance up to 840 Mbits per channel

- Direct connection from I/O pins to local interconnect providing fast t<sub>CO</sub> and t<sub>SU</sub> times for complex logic

- MultiVolt I/O interface support to interface with 1.8-V, 2.5-V, 3.3-V, and 5.0-V devices (see Table 3)

- Programmable clamp to V<sub>CCIO</sub>

- Individual tri-state output enable control for each pin

- Programmable output slew-rate control to reduce switching noise

- Support for advanced I/O standards, including low-voltage differential signaling (LVDS), LVPECL, PCI-X, AGP, CTT, stubseries terminated logic (SSTL-3 and SSTL-2), Gunning transceiver logic plus (GTL+), and high-speed terminated logic (HSTL Class I)

- Pull-up on I/O pins before and during configuration

- Advanced interconnect structure

- Four-level hierarchical FastTrack<sup>®</sup> Interconnect structure providing fast, predictable interconnect delays

- Dedicated carry chain that implements arithmetic functions such as fast adders, counters, and comparators (automatically used by software tools and megafunctions)

- Dedicated cascade chain that implements high-speed, high-fan-in logic functions (automatically used by software tools and megafunctions)

- Interleaved local interconnect allows one LE to drive 29 other LEs through the fast local interconnect

- Advanced packaging options

- Available in a variety of packages with 144 to 1,020 pins (see Tables 4 through 7)

- FineLine BGA<sup>®</sup> packages maximize board space efficiency

- Advanced software support

- Software design support and automatic place-and-route provided by the Altera<sup>®</sup> Quartus<sup>®</sup> II development system for

#### Normal Mode

The normal mode is suitable for general logic applications, combinatorial functions, or wide decoding functions that can take advantage of a cascade chain. In normal mode, four data inputs from the LAB local interconnect and the carry-in are inputs to a four-input LUT. The Quartus II software Compiler automatically selects the carry-in or the DATA3 signal as one of the inputs to the LUT. The LUT output can be combined with the cascade-in signal to form a cascade chain through the cascade-out signal. LEs in normal mode support packed registers.

#### **Arithmetic Mode**

The arithmetic mode is ideal for implementing adders, accumulators, and comparators. An LE in arithmetic mode uses two 3-input LUTs. One LUT computes a three-input function; the other generates a carry output. As shown in Figure 8, the first LUT uses the carry-in signal and two data inputs from the LAB local interconnect to generate a combinatorial or registered output. For example, when implementing an adder, this output is the sum of three signals: DATA1, DATA2, and carry-in. The second LUT uses the same three signals to generate a carry-out signal, thereby creating a carry chain. The arithmetic mode also supports simultaneous use of the cascade chain. LEs in arithmetic mode can drive out registered and unregistered versions of the LUT output.

The Quartus II software implements parameterized functions that use the arithmetic mode automatically where appropriate; the designer does not need to specify how the carry chain will be used.

#### **Counter Mode**

The counter mode offers clock enable, counter enable, synchronous up/down control, synchronous clear, and synchronous load options. The counter enable and synchronous up/down control signals are generated from the data inputs of the LAB local interconnect. The synchronous clear and synchronous load options are LAB-wide signals that affect all registers in the LAB. Consequently, if any of the LEs in an LAB use the counter mode, other LEs in that LAB must be used as part of the same counter or be used for a combinatorial function. The Quartus II software automatically places any registers that are not used by the counter into other LABs.

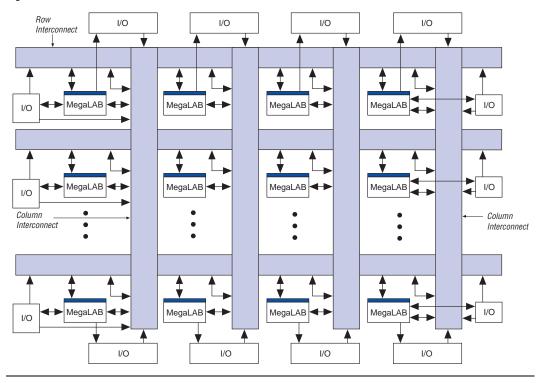

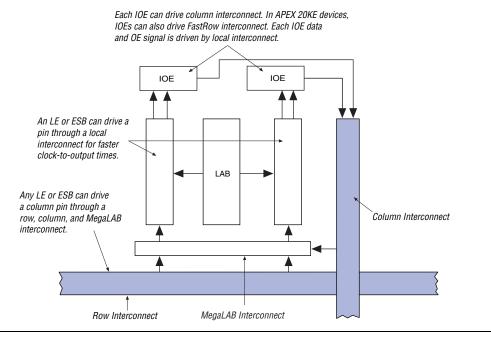

A row line can be driven directly by LEs, IOEs, or ESBs in that row. Further, a column line can drive a row line, allowing an LE, IOE, or ESB to drive elements in a different row via the column and row interconnect. The row interconnect drives the MegaLAB interconnect to drive LEs, IOEs, or ESBs in a particular MegaLAB structure.

A column line can be directly driven by LEs, IOEs, or ESBs in that column. A column line on a device's left or right edge can also be driven by row IOEs. The column line is used to route signals from one row to another. A column line can drive a row line; it can also drive the MegaLAB interconnect directly, allowing faster connections between rows.

Figure 10 shows how the FastTrack Interconnect uses the local interconnect to drive LEs within MegaLAB structures.

| Table 9. APEX 20K Routing Scheme    |                |   |   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |              |              |          |  |

|-------------------------------------|----------------|---|---|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|--------------|----------|--|

| Source                              | Destination    |   |   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |              |              |          |  |

|                                     | Row<br>I/O Pin |   |   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |              |              |          |  |

| Row I/O Pin                         |                |   |   |   | ✓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $\checkmark$ | $\checkmark$ | ✓            |          |  |

| Column I/O<br>Pin                   |                |   |   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |              | ~            | ✓<br>(1) |  |

| LE                                  |                |   |   |   | $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $\checkmark$ | $\checkmark$ | $\checkmark$ |          |  |

| ESB                                 |                |   |   |   | <ul> <li>Image: A set of the set of the</li></ul> | $\checkmark$ | ~            | ~            |          |  |

| Local<br>Interconnect               | ~              | ~ | ~ | ~ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |              |              |          |  |

| MegaLAB<br>Interconnect             |                |   |   |   | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |              |              |          |  |

| Row<br>FastTrack<br>Interconnect    |                |   |   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ~            |              | ~            |          |  |

| Column<br>FastTrack<br>Interconnect |                |   |   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ~            | ~            |              |          |  |

| FastRow<br>Interconnect             |                |   |   |   | ✓<br>(1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |              |              |          |  |

#### Note to Table 9:

(1) This connection is supported in APEX 20KE devices only.

## Product-Term Logic

The product-term portion of the MultiCore architecture is implemented with the ESB. The ESB can be configured to act as a block of macrocells on an ESB-by-ESB basis. Each ESB is fed by 32 inputs from the adjacent local interconnect; therefore, it can be driven by the MegaLAB interconnect or the adjacent LAB. Also, nine ESB macrocells feed back into the ESB through the local interconnect for higher performance. Dedicated clock pins, global signals, and additional inputs from the local interconnect drive the ESB control signals.

In product-term mode, each ESB contains 16 macrocells. Each macrocell consists of two product terms and a programmable register. Figure 13 shows the ESB in product-term mode.

Figure 28 shows how a column IOE connects to the interconnect.

#### Figure 28. Column IOE Connection to the Interconnect

# **Dedicated Fast I/O Pins**

APEX 20KE devices incorporate an enhancement to support bidirectional pins with high internal fanout such as PCI control signals. These pins are called Dedicated Fast I/O pins (FAST1, FAST2, FAST3, and FAST4) and replace dedicated inputs. These pins can be used for fast clock, clear, or high fanout logic signal distribution. They also can drive out. The Dedicated Fast I/O pin data output and tri-state control are driven by local interconnect from the adjacent MegaLAB for high speed. APEX 20KE devices also support the MultiVolt I/O interface feature. The APEX 20KE VCCINT pins must always be connected to a 1.8-V power supply. With a 1.8-V V<sub>CCINT</sub> level, input pins are 1.8-V, 2.5-V, and 3.3-V tolerant. The VCCIO pins can be connected to either a 1.8-V, 2.5-V, or 3.3-V power supply, depending on the I/O standard requirements. When the VCCIO pins are connected to a 1.8-V power supply, the output levels are compatible with 1.8-V systems. When VCCIO pins are connected to a 2.5-V power supply, the output levels are compatible with 2.5-V systems. When VCCIO pins are connected to a 3.3-V power supply, the output levels are sometime with 2.5-V systems. When VCCIO pins are connected to a 3.3-V power supply, the output high is 3.3 V and compatible with 3.3-V or 5.0-V systems. An APEX 20KE device is 5.0-V tolerant with the addition of a resistor.

## Table 13 summarizes APEX 20KE MultiVolt I/O support.

| Table 13. APEX 20KE MultiVolt I/O Support     Note (1)                     |              |              |              |     |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |     |

|----------------------------------------------------------------------------|--------------|--------------|--------------|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----|

| V <sub>CCIO</sub> (V)         Input Signals (V)         Output Signals (V) |              |              |              |     |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |     |

|                                                                            | 1.8          | 2.5          | 3.3          | 5.0 | 1.8          | 2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.3          | 5.0 |

| 1.8                                                                        | ~            | $\checkmark$ | <b>&gt;</b>  |     | $\checkmark$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |     |

| 2.5                                                                        | $\checkmark$ | $\checkmark$ | $\checkmark$ |     |              | <ul> <li>Image: A start of the start of</li></ul> |              |     |

| 3.3                                                                        | ~            | $\checkmark$ | >            | (2) |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>√</b> (3) |     |

#### Notes to Table 13:

The PCI clamping diode must be disabled to drive an input with voltages higher than V<sub>CCIO</sub>, except for the 5.0-V input case.

(2) An APEX 20KE device can be made 5.0-V tolerant with the addition of an external resistor. You also need a PCI clamp and series resistor.

(3) When V<sub>CCIO</sub> = 3.3 V, an APEX 20KE device can drive a 2.5-V device with 3.3-V tolerant inputs.

# ClockLock & ClockBoost Features

APEX 20K devices support the ClockLock and ClockBoost clock management features, which are implemented with PLLs. The ClockLock circuitry uses a synchronizing PLL that reduces the clock delay and skew within a device. This reduction minimizes clock-to-output and setup times while maintaining zero hold times. The ClockBoost circuitry, which provides a clock multiplier, allows the designer to enhance device area efficiency by sharing resources within the device. The ClockBoost circuitry allows the designer to distribute a low-speed clock and multiply that clock on-device. APEX 20K devices include a high-speed clock tree; unlike ASICs, the user does not have to design and optimize the clock tree. The ClockLock and ClockBoost features work in conjunction with the APEX 20K device's high-speed clock to provide significant improvements in system performance and band-width. Devices with an X-suffix on the ordering code include the ClockLock circuit.

The ClockLock and ClockBoost features in APEX 20K devices are enabled through the Quartus II software. External devices are not required to use these features.

#### Notes to Table 16:

- (1) To implement the ClockLock and ClockBoost circuitry with the Quartus II software, designers must specify the input frequency. The Quartus II software tunes the PLL in the ClockLock and ClockBoost circuitry to this frequency. The *f<sub>CLKDEV</sub>* parameter specifies how much the incoming clock can differ from the specified frequency during device operation. Simulation does not reflect this parameter.

- (2) Twenty-five thousand parts per million (PPM) equates to 2.5% of input clock period.

- (3) During device configuration, the ClockLock and ClockBoost circuitry is configured before the rest of the device. If the incoming clock is supplied during configuration, the ClockLock and ClockBoost circuitry locks during configuration because the t<sub>LOCK</sub> value is less than the time required for configuration.

- (4) The  $t_{IITTER}$  specification is measured under long-term observation.

Tables 17 and 18 summarize the ClockLock and ClockBoost parameters for APEX 20KE devices.

| Table 17. APEX 20KE ClockLock & ClockBoost Parameters       Note (1) |                                                              |            |     |     |                        |                  |

|----------------------------------------------------------------------|--------------------------------------------------------------|------------|-----|-----|------------------------|------------------|

| Symbol                                                               | Parameter                                                    | Conditions | Min | Тур | Мах                    | Unit             |

| t <sub>R</sub>                                                       | Input rise time                                              |            |     |     | 5                      | ns               |

| t <sub>F</sub>                                                       | Input fall time                                              |            |     |     | 5                      | ns               |

| t <sub>INDUTY</sub>                                                  | Input duty cycle                                             |            | 40  |     | 60                     | %                |

| t <sub>INJITTER</sub>                                                | Input jitter peak-to-peak                                    |            |     |     | 2% of input<br>period  | peak-to-<br>peak |

|                                                                      | Jitter on ClockLock or ClockBoost-<br>generated clock        |            |     |     | 0.35% of output period | RMS              |

| t <sub>OUTDUTY</sub>                                                 | Duty cycle for ClockLock or<br>ClockBoost-generated clock    |            | 45  |     | 55                     | %                |

| t <sub>LOCK</sub> (2) <sub>,</sub> (3)                               | Time required for ClockLock or<br>ClockBoost to acquire lock |            |     |     | 40                     | μs               |

# IEEE Std. 1149.1 (JTAG) Boundary-Scan Support

All APEX 20K devices provide JTAG BST circuitry that complies with the IEEE Std. 1149.1-1990 specification. JTAG boundary-scan testing can be performed before or after configuration, but not during configuration. APEX 20K devices can also use the JTAG port for configuration with the Quartus II software or with hardware using either Jam Files (.jam) or Jam Byte-Code Files (.jbc). Finally, APEX 20K devices use the JTAG port to monitor the logic operation of the device with the SignalTap embedded logic analyzer. APEX 20K devices support the JTAG instructions shown in Table 19. Although EP20K1500E devices support the JTAG BYPASS and SignalTap instructions, they do not support boundary-scan testing or the use of the JTAG port for configuration.

| Table 19. APEX 20K J       | FAG Instructions                                                                                                                                                                                                                     |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTAG Instruction           | Description                                                                                                                                                                                                                          |

| SAMPLE/PRELOAD             | Allows a snapshot of signals at the device pins to be captured and examined during normal device operation, and permits an initial data pattern to be output at the device pins. Also used by the SignalTap embedded logic analyzer. |

| EXTEST                     | Allows the external circuitry and board-level interconnections to be tested by forcing a test pattern at the output pins and capturing test results at the input pins.                                                               |

| BYPASS (1)                 | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation.                                          |

| USERCODE                   | Selects the 32-bit USERCODE register and places it between the TDI and TDO pins, allowing the USERCODE to be serially shifted out of TDO.                                                                                            |

| IDCODE                     | Selects the IDCODE register and places it between TDI and TDO, allowing the IDCODE to be serially shifted out of TDO.                                                                                                                |

| ICR Instructions           | Used when configuring an APEX 20K device via the JTAG port with a MasterBlaster <sup>™</sup> or ByteBlasterMV <sup>™</sup> download cable, or when using a Jam File or Jam Byte-Code File via an embedded processor.                 |

| SignalTap Instructions (1) | Monitors internal device operation with the SignalTap embedded logic analyzer.                                                                                                                                                       |

## able 19 APFX 20K .ITAG Instruction

#### Note to Table 19:

(1) The EP20K1500E device supports the JTAG BYPASS instruction and the SignalTap instructions.

Table 22 shows the JTAG timing parameters and values for APEX 20K devices.

| Table 22. AFEX 20K JIAG Tilling Falameters & Values |                                                |     |     |      |  |  |

|-----------------------------------------------------|------------------------------------------------|-----|-----|------|--|--|

| Symbol                                              | Parameter                                      | Min | Max | Unit |  |  |

| t <sub>JCP</sub>                                    | TCK clock period                               | 100 |     | ns   |  |  |

| t <sub>JCH</sub>                                    | TCK clock high time                            | 50  |     | ns   |  |  |

| t <sub>JCL</sub>                                    | TCK clock low time                             | 50  |     | ns   |  |  |

| t <sub>JPSU</sub>                                   | JTAG port setup time                           | 20  |     | ns   |  |  |

| t <sub>JPH</sub>                                    | JTAG port hold time                            | 45  |     | ns   |  |  |

| t <sub>JPCO</sub>                                   | JTAG port clock to output                      |     | 25  | ns   |  |  |

| t <sub>JPZX</sub>                                   | JTAG port high impedance to valid output       |     | 25  | ns   |  |  |

| t <sub>JPXZ</sub>                                   | JTAG port valid output to high impedance       |     | 25  | ns   |  |  |

| t <sub>JSSU</sub>                                   | Capture register setup time                    | 20  |     | ns   |  |  |

| t <sub>JSH</sub>                                    | Capture register hold time                     | 45  |     | ns   |  |  |

| t <sub>JSCO</sub>                                   | Update register clock to output                |     | 35  | ns   |  |  |

| t <sub>JSZX</sub>                                   | Update register high impedance to valid output |     | 35  | ns   |  |  |

| t <sub>JSXZ</sub>                                   | Update register valid output to high impedance |     | 35  | ns   |  |  |

Table 22. APEX 20K JTAG Timing Parameters & Values

For more information, see the following documents:

- Application Note 39 (IEEE Std. 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices)

- Jam Programming & Test Language Specification

# **Generic Testing**

Each APEX 20K device is functionally tested. Complete testing of each configurable static random access memory (SRAM) bit and all logic functionality ensures 100% yield. AC test measurements for APEX 20K devices are made under conditions equivalent to those shown in Figure 32. Multiple test patterns can be used to configure devices during all stages of the production flow.

P

For DC Operating Specifications on APEX 20KE I/O standards, please refer to *Application Note 117 (Using Selectable I/O Standards in Altera Devices).*

| Table 30. APEX 20KE Device Capacitance     Note (15) |                                             |                                     |     |     |      |

|------------------------------------------------------|---------------------------------------------|-------------------------------------|-----|-----|------|

| Symbol                                               | Parameter                                   | Conditions                          | Min | Max | Unit |

| C <sub>IN</sub>                                      | Input capacitance                           | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 8   | pF   |

| CINCLK                                               | Input capacitance on<br>dedicated clock pin | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 12  | pF   |

| C <sub>OUT</sub>                                     | Output capacitance                          | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 8   | pF   |

#### Notes to Tables 27 through 30:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to 5.75 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Numbers in parentheses are for industrial-temperature-range devices.

- (4) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically.

- (5) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to the voltage shown in the following table based on input duty cycle for input currents less than 100 mA. The overshoot is dependent upon duty cycle of the signal. The DC case is equivalent to 100% duty cycle.

| Vin  | Max. Duty Cycle |

|------|-----------------|

| 4.0V | 100% (DC)       |

| 4.1  | 90%             |

- 4.2 50%

- 4.3 30%

- 4.4 17%

- 4.5 10%

- (6) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are powered.

- (7) Typical values are for  $T_A = 25^\circ$  C,  $V_{CCINT} = 1.8$  V, and  $V_{CCIO} = 1.8$  V, 2.5 V or 3.3 V.

- (8) These values are specified under the APEX 20KE device recommended operating conditions, shown in Table 24 on page 60.

- (9) Refer to Application Note 117 (Using Selectable I/O Standards in Altera Devices) for the V<sub>IH</sub>, V<sub>IL</sub>, V<sub>OH</sub>, V<sub>OL</sub>, and I<sub>I</sub> parameters when VCCIO = 1.8 V.

- (10) The APEX 20KE input buffers are compatible with 1.8-V, 2.5-V and 3.3-V (LVTTL and LVCMOS) signals. Additionally, the input buffers are 3.3-V PCI compliant. Input buffers also meet specifications for GTL+, CTT, AGP, SSTL-2, SSTL-3, and HSTL.

- (11) The I<sub>OH</sub> parameter refers to high-level TTL, PCI, or CMOS output current.

- (12) The I<sub>OL</sub> parameter refers to low-level TTL, PCI, or CMOS output current. This parameter applies to open-drain pins as well as output pins.

- (13) This value is specified for normal device operation. The value may vary during power-up.

- (14) Pin pull-up resistance values will be lower if an external source drives the pin higher than V<sub>CCIO</sub>.

- (15) Capacitance is sample-tested only.

Figure 33 shows the relationship between  $\rm V_{CCIO}$  and  $\rm V_{CCINT}$  for 3.3-V PCI compliance on APEX 20K devices.

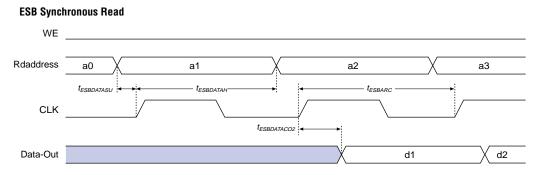

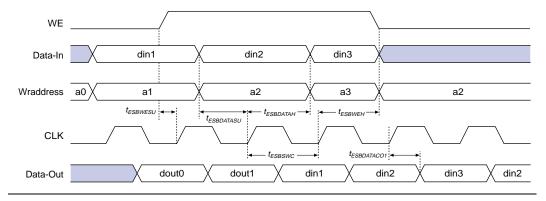

Figure 39. ESB Synchronous Timing Waveforms

#### ESB Synchronous Write (ESB Output Registers Used)

Figure 40 shows the timing model for bidirectional I/O pin timing.

#### Note to Tables 32 and 33:

(1) These timing parameters are sample-tested only.

Tables 34 through 37 show APEX 20KE LE, ESB, routing, and functional timing microparameters for the  $f_{MAX}$  timing model.

| Table 34. APEX 20KE LE Timing Microparameters |                                     |  |  |  |

|-----------------------------------------------|-------------------------------------|--|--|--|

| Symbol Parameter                              |                                     |  |  |  |

| t <sub>SU</sub>                               | LE register setup time before clock |  |  |  |

| t <sub>H</sub>                                | LE register hold time after clock   |  |  |  |

| t <sub>CO</sub>                               | LE register clock-to-output delay   |  |  |  |

| t <sub>LUT</sub>                              | LUT delay for data-in to data-out   |  |  |  |

| Table 35. APEX 20KE ESB Timing Microparameters |                                                                      |  |  |

|------------------------------------------------|----------------------------------------------------------------------|--|--|

| Symbol                                         | Parameter                                                            |  |  |

| t <sub>ESBARC</sub>                            | ESB Asynchronous read cycle time                                     |  |  |

| t <sub>ESBSRC</sub>                            | ESB Synchronous read cycle time                                      |  |  |

| t <sub>ESBAWC</sub>                            | ESB Asynchronous write cycle time                                    |  |  |

| t <sub>ESBSWC</sub>                            | ESB Synchronous write cycle time                                     |  |  |

| t <sub>ESBWASU</sub>                           | ESB write address setup time with respect to WE                      |  |  |

| t <sub>ESBWAH</sub>                            | ESB write address hold time with respect to WE                       |  |  |

| t <sub>ESBWDSU</sub>                           | ESB data setup time with respect to WE                               |  |  |

| t <sub>ESBWDH</sub>                            | ESB data hold time with respect to WE                                |  |  |

| t <sub>ESBRASU</sub>                           | ESB read address setup time with respect to RE                       |  |  |

| t <sub>ESBRAH</sub>                            | ESB read address hold time with respect to RE                        |  |  |

| t <sub>ESBWESU</sub>                           | ESB WE setup time before clock when using input register             |  |  |

| t <sub>ESBWEH</sub>                            | ESB WE hold time after clock when using input register               |  |  |

| t <sub>ESBDATASU</sub>                         | ESB data setup time before clock when using input register           |  |  |

| t <sub>ESBDATAH</sub>                          | ESB data hold time after clock when using input register             |  |  |

| <sup>t</sup> ESBWADDRSU                        | ESB write address setup time before clock when using input registers |  |  |

| t <sub>ESBRADDRSU</sub>                        | ESB read address setup time before clock when using input registers  |  |  |

| t <sub>ESBDATACO1</sub>                        | ESB clock-to-output delay when using output registers                |  |  |

| t <sub>ESBDATACO2</sub>                        | ESB clock-to-output delay without output registers                   |  |  |

| t <sub>ESBDD</sub>                             | ESB data-in to data-out delay for RAM mode                           |  |  |

| t <sub>PD</sub>                                | ESB Macrocell input to non-registered output                         |  |  |

| t <sub>PTERMSU</sub>                           | ESB Macrocell register setup time before clock                       |  |  |

| t <sub>PTERMCO</sub>                           | ESB Macrocell register clock-to-output delay                         |  |  |

| Table 36. APEX 20KE Routing Timing Microparameters         Note (1) |                                                    |  |  |  |  |  |  |  |

|---------------------------------------------------------------------|----------------------------------------------------|--|--|--|--|--|--|--|

| Symbol                                                              | Parameter                                          |  |  |  |  |  |  |  |

| t <sub>F1-4</sub>                                                   | Fanout delay using Local Interconnect              |  |  |  |  |  |  |  |

| t <sub>F5-20</sub>                                                  | Fanout delay estimate using MegaLab Interconnect   |  |  |  |  |  |  |  |

| t <sub>F20+</sub>                                                   | Fanout delay estimate using FastTrack Interconnect |  |  |  |  |  |  |  |

#### Note to Table 36:

These parameters are worst-case values for typical applications. Post-compilation timing simulation and timing analysis are required to determine actual worst-case performance.

| Table 37. APEX 20KE Functional Timing Microparameters |                                        |  |  |  |  |  |

|-------------------------------------------------------|----------------------------------------|--|--|--|--|--|

| Symbol                                                | Parameter                              |  |  |  |  |  |

| ТСН                                                   | Minimum clock high time from clock pin |  |  |  |  |  |

| TCL                                                   | Minimum clock low time from clock pin  |  |  |  |  |  |

| TCLRP                                                 | LE clear Pulse Width                   |  |  |  |  |  |

| TPREP                                                 | LE preset pulse width                  |  |  |  |  |  |

| TESBCH                                                | Clock high time for ESB                |  |  |  |  |  |

| TESBCL                                                | Clock low time for ESB                 |  |  |  |  |  |

| TESBWP                                                | Write pulse width                      |  |  |  |  |  |

| TESBRP                                                | Read pulse width                       |  |  |  |  |  |

# Table 37. APEX 20KE Functional Timing Microparameters

Tables 38 and 39 describe the APEX 20KE external timing parameters.

| Table 38. APEX 20KE External Timing Parameters       Note (1) |                                                                |            |  |  |  |  |  |  |

|---------------------------------------------------------------|----------------------------------------------------------------|------------|--|--|--|--|--|--|

| Symbol                                                        | Clock Parameter                                                | Conditions |  |  |  |  |  |  |

| t <sub>INSU</sub>                                             | Setup time with global clock at IOE input register             |            |  |  |  |  |  |  |

| t <sub>INH</sub>                                              | Hold time with global clock at IOE input register              |            |  |  |  |  |  |  |

| t <sub>оитсо</sub>                                            | Clock-to-output delay with global clock at IOE output register | C1 = 10 pF |  |  |  |  |  |  |

| t <sub>INSUPLL</sub>                                          | Setup time with PLL clock at IOE input register                |            |  |  |  |  |  |  |

| t <sub>INHPLL</sub>                                           | Hold time with PLL clock at IOE input register                 |            |  |  |  |  |  |  |

| t <sub>OUTCOPLL</sub>                                         | Clock-to-output delay with PLL clock at IOE output register    | C1 = 10 pF |  |  |  |  |  |  |

| Symbol                  | -'    | 1    | -     | 2    | -:    | 3    | Unit |

|-------------------------|-------|------|-------|------|-------|------|------|

|                         | Min   | Max  | Min   | Max  | Min   | Max  |      |

| t <sub>ESBARC</sub>     |       | 1.61 |       | 1.84 |       | 1.97 | ns   |

| t <sub>ESBSRC</sub>     |       | 2.57 |       | 2.97 |       | 3.20 | ns   |

| t <sub>ESBAWC</sub>     |       | 0.52 |       | 4.09 |       | 4.39 | ns   |

| t <sub>ESBSWC</sub>     |       | 3.17 |       | 3.78 |       | 4.09 | ns   |

| t <sub>ESBWASU</sub>    | 0.56  |      | 6.41  |      | 0.63  |      | ns   |

| t <sub>ESBWAH</sub>     | 0.48  |      | 0.54  |      | 0.55  |      | ns   |

| t <sub>ESBWDSU</sub>    | 0.71  |      | 0.80  |      | 0.81  |      | ns   |

| t <sub>ESBWDH</sub>     | .048  |      | 0.54  |      | 0.55  |      | ns   |

| t <sub>ESBRASU</sub>    | 1.57  |      | 1.75  |      | 1.87  |      | ns   |

| t <sub>ESBRAH</sub>     | 0.00  |      | 0.00  |      | 0.20  |      | ns   |

| t <sub>ESBWESU</sub>    | 1.54  |      | 1.72  |      | 1.80  |      | ns   |

| t <sub>ESBWEH</sub>     | 0.00  |      | 0.00  |      | 0.00  |      | ns   |

| t <sub>ESBDATASU</sub>  | -0.16 |      | -0.20 |      | -0.20 |      | ns   |

| t <sub>ESBDATAH</sub>   | 0.13  |      | 0.13  |      | 0.13  |      | ns   |

| t <sub>ESBWADDRSU</sub> | 0.12  |      | 0.08  |      | 0.13  |      | ns   |

| t <sub>ESBRADDRSU</sub> | 0.17  |      | 0.15  |      | 0.19  |      | ns   |

| t <sub>ESBDATACO1</sub> |       | 1.20 |       | 1.39 |       | 1.52 | ns   |

| t <sub>ESBDATACO2</sub> |       | 2.54 |       | 2.99 |       | 3.22 | ns   |

| t <sub>ESBDD</sub>      |       | 3.06 |       | 3.56 |       | 3.85 | ns   |

| t <sub>PD</sub>         |       | 1.73 |       | 2.02 |       | 2.20 | ns   |

| t <sub>PTERMSU</sub>    | 1.11  |      | 1.26  |      | 1.38  |      | ns   |

| t <sub>PTERMCO</sub>    |       | 1.19 |       | 1.40 |       | 1.08 | ns   |

| Table 63. EP20K100E f <sub>MAX</sub> Routing Delays |     |      |     |      |     |      |    |  |  |  |

|-----------------------------------------------------|-----|------|-----|------|-----|------|----|--|--|--|

| Symbol                                              | -   | -1   |     | -2   |     | -3   |    |  |  |  |

|                                                     | Min | Max  | Min | Max  | Min | Мах  |    |  |  |  |

| t <sub>F1-4</sub>                                   |     | 0.24 |     | 0.27 |     | 0.29 | ns |  |  |  |

| t <sub>F5-20</sub>                                  |     | 1.04 |     | 1.26 |     | 1.52 | ns |  |  |  |