Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Obsolete                                                      |

| Number of LABs/CLBs            | 1152                                                          |

| Number of Logic Elements/Cells | 11520                                                         |

| Total RAM Bits                 | 147456                                                        |

| Number of I/O                  | 408                                                           |

| Number of Gates                | 728000                                                        |

| Voltage - Supply               | 1.71V ~ 1.89V                                                 |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                               |

| Package / Case                 | 672-BBGA                                                      |

| Supplier Device Package        | 672-FBGA (27x27)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep20k300efc672-2xa |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 2. Additiona    | Note (1)  |           |           |           |            |            |

|-----------------------|-----------|-----------|-----------|-----------|------------|------------|

| Feature               | EP20K300E | EP20K400  | EP20K400E | EP20K600E | EP20K1000E | EP20K1500E |

| Maximum system gates  | 728,000   | 1,052,000 | 1,052,000 | 1,537,000 | 1,772,000  | 2,392,000  |

| Typical gates         | 300,000   | 400,000   | 400,000   | 600,000   | 1,000,000  | 1,500,000  |

| LEs                   | 11,520    | 16,640    | 16,640    | 24,320    | 38,400     | 51,840     |

| ESBs                  | 72        | 104       | 104       | 152       | 160        | 216        |

| Maximum<br>RAM bits   | 147,456   | 212,992   | 212,992   | 311,296   | 327,680    | 442,368    |

| Maximum macrocells    | 1,152     | 1,664     | 1,664     | 2,432     | 2,560      | 3,456      |

| Maximum user I/O pins | 408       | 502       | 488       | 588       | 708        | 808        |

#### Note to Tables 1 and 2:

(1) The embedded IEEE Std. 1149.1 Joint Test Action Group (JTAG) boundary-scan circuitry contributes up to 57,000 additional gates.

# Additional Features

- Designed for low-power operation

- 1.8-V and 2.5-V supply voltage (see Table 3)

- MultiVolt<sup>TM</sup> I/O interface support to interface with 1.8-V, 2.5-V, 3.3-V, and 5.0-V devices (see Table 3)

- ESB offering programmable power-saving mode

| Feature                                                     |                                  | Device                                                                                   |

|-------------------------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------|

|                                                             | EP20K100<br>EP20K200<br>EP20K400 | EP20K30E EP20K60E EP20K100E EP20K160E EP20K200E EP20K300E EP20K400E EP20K600E EP20K1000E |

| Internal supply voltage (V <sub>CCINT</sub> )               | 2.5 V                            | 1.8 V                                                                                    |

| MultiVolt I/O interface voltage levels (V <sub>CCIO</sub> ) | 2.5 V, 3.3 V, 5.0 V              | 1.8 V, 2.5 V, 3.3 V, 5.0 V (1)                                                           |

Note to Table 3:

(1) APEX 20KE devices can be 5.0-V tolerant by using an external resistor.

- Flexible clock management circuitry with up to four phase-locked loops (PLLs)

- Built-in low-skew clock tree

- Up to eight global clock signals

- ClockLock<sup>®</sup> feature reducing clock delay and skew

- ClockBoost<sup>®</sup> feature providing clock multiplication and division

- ClockShift™ programmable clock phase and delay shifting

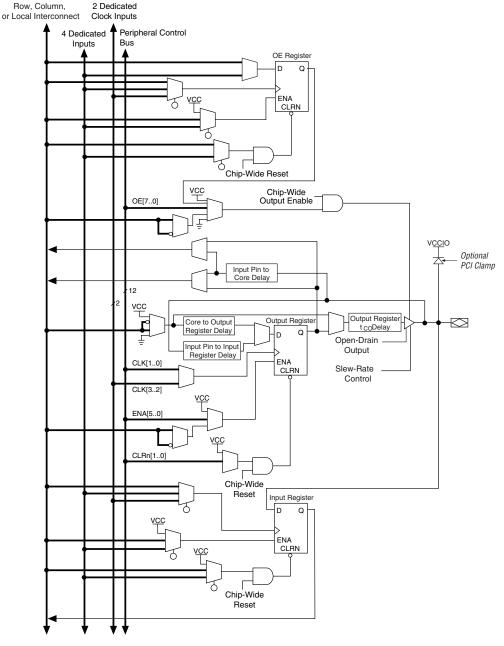

#### Powerful I/O features

- Compliant with peripheral component interconnect Special Interest Group (PCI SIG) PCI Local Bus Specification, Revision 2.2 for 3.3-V operation at 33 or 66 MHz and 32 or 64 bits

- Support for high-speed external memories, including DDR SDRAM and ZBT SRAM (ZBT is a trademark of Integrated Device Technology, Inc.)

- Bidirectional I/O performance ( $t_{CO} + t_{SU}$ ) up to 250 MHz

- LVDS performance up to 840 Mbits per channel

- Direct connection from I/O pins to local interconnect providing fast t<sub>CO</sub> and t<sub>SU</sub> times for complex logic

- MultiVolt I/O interface support to interface with 1.8-V, 2.5-V, 3.3-V, and 5.0-V devices (see Table 3)

- Programmable clamp to V<sub>CCIO</sub>

- Individual tri-state output enable control for each pin

- Programmable output slew-rate control to reduce switching noise

- Support for advanced I/O standards, including low-voltage differential signaling (LVDS), LVPECL, PCI-X, AGP, CTT, stubseries terminated logic (SSTL-3 and SSTL-2), Gunning transceiver logic plus (GTL+), and high-speed terminated logic (HSTL Class I)

- Pull-up on I/O pins before and during configuration

#### Advanced interconnect structure

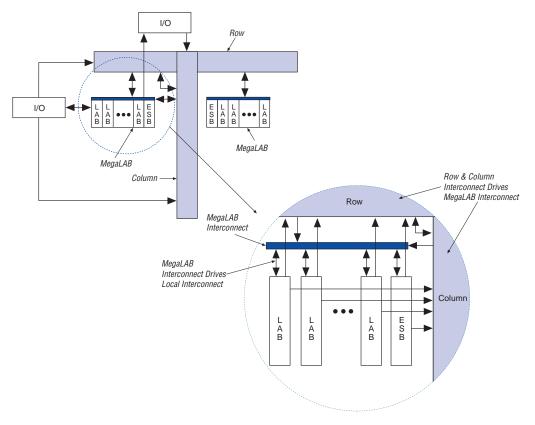

- Four-level hierarchical FastTrack<sup>®</sup> Interconnect structure providing fast, predictable interconnect delays

- Dedicated carry chain that implements arithmetic functions such as fast adders, counters, and comparators (automatically used by software tools and megafunctions)

- Dedicated cascade chain that implements high-speed, high-fan-in logic functions (automatically used by software tools and megafunctions)

- Interleaved local interconnect allows one LE to drive 29 other LEs through the fast local interconnect

#### Advanced packaging options

- Available in a variety of packages with 144 to 1,020 pins (see Tables 4 through 7)

- FineLine BGA® packages maximize board space efficiency

#### Advanced software support

Software design support and automatic place-and-route provided by the Altera® Quartus® II development system for

| Table 5. APEX 20K FineLine BGA Package Options & I/O Count       Notes (1), (2) |         |         |         |                |           |  |  |  |

|---------------------------------------------------------------------------------|---------|---------|---------|----------------|-----------|--|--|--|

| Device                                                                          | 144 Pin | 324 Pin | 484 Pin | 672 Pin        | 1,020 Pin |  |  |  |

| EP20K30E                                                                        | 93      | 128     |         |                |           |  |  |  |

| EP20K60E                                                                        | 93      | 196     |         |                |           |  |  |  |

| EP20K100                                                                        |         | 252     |         |                |           |  |  |  |

| EP20K100E                                                                       | 93      | 246     |         |                |           |  |  |  |

| EP20K160E                                                                       |         |         | 316     |                |           |  |  |  |

| EP20K200                                                                        |         |         | 382     |                |           |  |  |  |

| EP20K200E                                                                       |         |         | 376     | 376            |           |  |  |  |

| EP20K300E                                                                       |         |         |         | 408            |           |  |  |  |

| EP20K400                                                                        |         |         |         | 502 <i>(3)</i> |           |  |  |  |

| EP20K400E                                                                       |         |         |         | 488 (3)        |           |  |  |  |

| EP20K600E                                                                       |         |         |         | 508 (3)        | 588       |  |  |  |

| EP20K1000E                                                                      |         |         |         | 508 (3)        | 708       |  |  |  |

| EP20K1500E                                                                      |         |         |         |                | 808       |  |  |  |

#### Notes to Tables 4 and 5:

- (1) I/O counts include dedicated input and clock pins.

- (2) APEX 20K device package types include thin quad flat pack (TQFP), plastic quad flat pack (PQFP), power quad flat pack (RQFP), 1.27-mm pitch ball-grid array (BGA), 1.00-mm pitch FineLine BGA, and pin-grid array (PGA) packages.

- (3) This device uses a thermally enhanced package, which is taller than the regular package. Consult the *Altera Device Package Information Data Sheet* for detailed package size information.

| Table 6. APEX 20K QFP, BGA & PGA Package Sizes                                                   |              |             |             |             |             |             |  |  |  |  |

|--------------------------------------------------------------------------------------------------|--------------|-------------|-------------|-------------|-------------|-------------|--|--|--|--|

| Feature                                                                                          | 144-Pin TQFP | 208-Pin QFP | 240-Pin QFP | 356-Pin BGA | 652-Pin BGA | 655-Pin PGA |  |  |  |  |

| Pitch (mm)                                                                                       | 0.50         | 0.50        | 0.50        | 1.27        | 1.27        | _           |  |  |  |  |

| Area (mm <sup>2</sup> )                                                                          | 484          | 924         | 1,218       | 1,225       | 2,025       | 3,906       |  |  |  |  |

| $\begin{array}{c} \text{Length} \times \text{Width} \\ \text{(mm} \times \text{mm)} \end{array}$ | 22 × 22      | 30.4 × 30.4 | 34.9 × 34.9 | 35 × 35     | 45 × 45     | 62.5 × 62.5 |  |  |  |  |

| Table 7. APEX 20K FineLine BGA Package Sizes |         |         |         |         |           |  |  |  |  |

|----------------------------------------------|---------|---------|---------|---------|-----------|--|--|--|--|

| Feature                                      | 144 Pin | 324 Pin | 484 Pin | 672 Pin | 1,020 Pin |  |  |  |  |

| Pitch (mm)                                   | 1.00    | 1.00    | 1.00    | 1.00    | 1.00      |  |  |  |  |

| Area (mm <sup>2</sup> )                      | 169     | 361     | 529     | 729     | 1,089     |  |  |  |  |

| $Length \times Width (mm \times mm)$         | 13 × 13 | 19×19   | 23 × 23 | 27 × 27 | 33 × 33   |  |  |  |  |

#### LE Operating Modes

The APEX 20K LE can operate in one of the following three modes:

- Normal mode

- Arithmetic mode

- Counter mode

Each mode uses LE resources differently. In each mode, seven available inputs to the LE—the four data inputs from the LAB local interconnect, the feedback from the programmable register, and the carry-in and cascade-in from the previous LE—are directed to different destinations to implement the desired logic function. LAB-wide signals provide clock, asynchronous clear, asynchronous preset, asynchronous load, synchronous clear, synchronous load, and clock enable control for the register. These LAB-wide signals are available in all LE modes.

The Quartus II software, in conjunction with parameterized functions such as LPM and DesignWare functions, automatically chooses the appropriate mode for common functions such as counters, adders, and multipliers. If required, the designer can also create special-purpose functions that specify which LE operating mode to use for optimal performance. Figure 8 shows the LE operating modes.

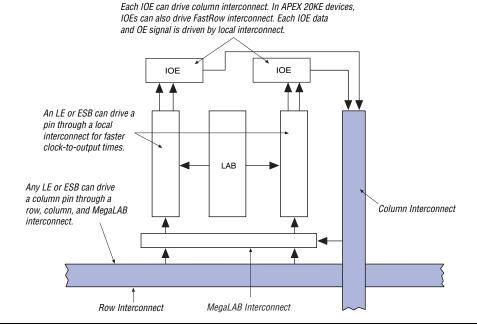

Figure 10. FastTrack Connection to Local Interconnect

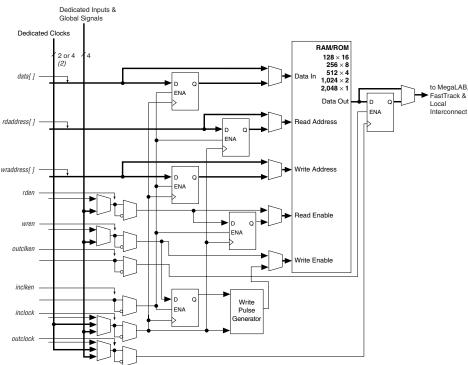

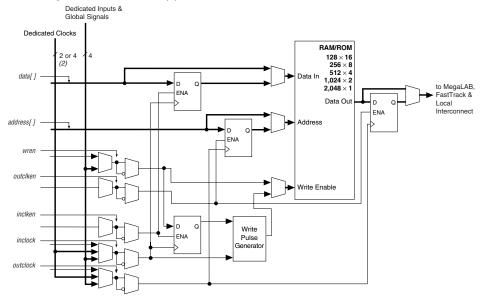

ESBs can implement synchronous RAM, which is easier to use than asynchronous RAM. A circuit using asynchronous RAM must generate the RAM write enable (WE) signal, while ensuring that its data and address signals meet setup and hold time specifications relative to the WE signal. In contrast, the ESB's synchronous RAM generates its own WE signal and is self-timed with respect to the global clock. Circuits using the ESB's self-timed RAM must only meet the setup and hold time specifications of the global clock.

ESB inputs are driven by the adjacent local interconnect, which in turn can be driven by the MegaLAB or FastTrack Interconnect. Because the ESB can be driven by the local interconnect, an adjacent LE can drive it directly for fast memory access. ESB outputs drive the MegaLAB and FastTrack Interconnect. In addition, ten ESB outputs, nine of which are unique output lines, drive the local interconnect for fast connection to adjacent LEs or for fast feedback product-term logic.

When implementing memory, each ESB can be configured in any of the following sizes:  $128 \times 16$ ,  $256 \times 8$ ,  $512 \times 4$ ,  $1,024 \times 2$ , or  $2,048 \times 1$ . By combining multiple ESBs, the Quartus II software implements larger memory blocks automatically. For example, two  $128 \times 16$  RAM blocks can be combined to form a  $128 \times 32$  RAM block, and two  $512 \times 4$  RAM blocks can be combined to form a  $512 \times 8$  RAM block. Memory performance does not degrade for memory blocks up to 2,048 words deep. Each ESB can implement a 2,048-word-deep memory; the ESBs are used in parallel, eliminating the need for any external control logic and its associated delays.

To create a high-speed memory block that is more than 2,048 words deep, ESBs drive tri-state lines. Each tri-state line connects all ESBs in a column of MegaLAB structures, and drives the MegaLAB interconnect and row and column FastTrack Interconnect throughout the column. Each ESB incorporates a programmable decoder to activate the tri-state driver appropriately. For instance, to implement 8,192-word-deep memory, four ESBs are used. Eleven address lines drive the ESB memory, and two more drive the tri-state decoder. Depending on which 2,048-word memory page is selected, the appropriate ESB driver is turned on, driving the output to the tri-state line. The Quartus II software automatically combines ESBs with tri-state lines to form deeper memory blocks. The internal tri-state control logic is designed to avoid internal contention and floating lines. See Figure 18.

#### Input/Output Clock Mode

The input/output clock mode contains two clocks. One clock controls all registers for inputs into the ESB: data input, WE, RE, read address, and write address. The other clock controls the ESB data output registers. The ESB also supports clock enable and asynchronous clear signals; these signals also control the reading and writing of registers independently. Input/output clock mode is commonly used for applications where the reads and writes occur at the same system frequency, but require different clock enable signals for the input and output registers. Figure 21 shows the ESB in input/output clock mode.

Figure 21. ESB in Input/Output Clock Mode Note (1)

Notes to Figure 21:

- (1) All registers can be cleared asynchronously by ESB local interconnect signals, global signals, or the chip-wide reset.

- (2) APEX 20KE devices have four dedicated clocks.

## Single-Port Mode

The APEX 20K ESB also supports a single-port mode, which is used when simultaneous reads and writes are not required. See Figure 22.

Figure 22. ESB in Single-Port Mode Note (1)

Notes to Figure 22:

- (1) All registers can be asynchronously cleared by ESB local interconnect signals, global signals, or the chip-wide reset.

- (2) APEX 20KE devices have four dedicated clocks.

## **Content-Addressable Memory**

In APEX 20KE devices, the ESB can implement CAM. CAM can be thought of as the inverse of RAM. When read, RAM outputs the data for a given address. Conversely, CAM outputs an address for a given data word. For example, if the data FA12 is stored in address 14, the CAM outputs 14 when FA12 is driven into it.

CAM is used for high-speed search operations. When searching for data within a RAM block, the search is performed serially. Thus, finding a particular data word can take many cycles. CAM searches all addresses in parallel and outputs the address storing a particular word. When a match is found, a match flag is set high. Figure 23 shows the CAM block diagram.

Figure 25. APEX 20K Bidirectional I/O Registers Note (1)

Note to Figure 25:

(1) The output enable and input registers are LE registers in the LAB adjacent to the bidirectional pin.

Figure 28 shows how a column IOE connects to the interconnect.

Figure 28. Column IOE Connection to the Interconnect

#### **Dedicated Fast I/O Pins**

APEX 20KE devices incorporate an enhancement to support bidirectional pins with high internal fanout such as PCI control signals. These pins are called Dedicated Fast I/O pins (FAST1, FAST2, FAST3, and FAST4) and replace dedicated inputs. These pins can be used for fast clock, clear, or high fanout logic signal distribution. They also can drive out. The Dedicated Fast I/O pin data output and tri-state control are driven by local interconnect from the adjacent MegaLAB for high speed.

For designs that require both a multiplied and non-multiplied clock, the clock trace on the board can be connected to CLK2p. Table 14 shows the combinations supported by the ClockLock and ClockBoost circuitry. The CLK2p pin can feed both the ClockLock and ClockBoost circuitry in the APEX 20K device. However, when both circuits are used, the other clock pin (CLK1p) cannot be used.

| Table 14. Multiplication Factor Combinations |         |  |  |  |

|----------------------------------------------|---------|--|--|--|

| Clock 1                                      | Clock 2 |  |  |  |

| ×1                                           | ×1      |  |  |  |

| ×1,×2                                        | ×2      |  |  |  |

| ×1, ×2, ×4                                   | ×4      |  |  |  |

#### **APEX 20KE ClockLock Feature**

APEX 20KE devices include an enhanced ClockLock feature set. These devices include up to four PLLs, which can be used independently. Two PLLs are designed for either general-purpose use or LVDS use (on devices that support LVDS I/O pins). The remaining two PLLs are designed for general-purpose use. The EP20K200E and smaller devices have two PLLs; the EP20K300E and larger devices have four PLLs.

The following sections describe some of the features offered by the APEX 20KE PLLs.

#### External PLL Feedback

The ClockLock circuit's output can be driven off-chip to clock other devices in the system; further, the feedback loop of the PLL can be routed off-chip. This feature allows the designer to exercise fine control over the I/O interface between the APEX 20KE device and another high-speed device, such as SDRAM.

#### Clock Multiplication

The APEX 20KE ClockBoost circuit can multiply or divide clocks by a programmable number. The clock can be multiplied by  $m/(n \times k)$  or  $m/(n \times v)$ , where m and k range from 2 to 160, and n and v range from 1 to 16. Clock multiplication and division can be used for time-domain multiplexing and other functions, which can reduce design LE requirements.

#### Clock Phase & Delay Adjustment

The APEX 20KE ClockShift feature allows the clock phase and delay to be adjusted. The clock phase can be adjusted by 90° steps. The clock delay can be adjusted to increase or decrease the clock delay by an arbitrary amount, up to one clock period.

#### LVDS Support

Two PLLs are designed to support the LVDS interface. When using LVDS, the I/O clock runs at a slower rate than the data transfer rate. Thus, PLLs are used to multiply the I/O clock internally to capture the LVDS data. For example, an I/O clock may run at 105 MHz to support 840 megabits per second (Mbps) LVDS data transfer. In this example, the PLL multiplies the incoming clock by eight to support the high-speed data transfer. You can use PLLs in EP20K400E and larger devices for high-speed LVDS interfacing.

#### Lock Signals

The APEX 20KE ClockLock circuitry supports individual LOCK signals. The LOCK signal drives high when the ClockLock circuit has locked onto the input clock. The LOCK signals are optional for each ClockLock circuit; when not used, they are I/O pins.

### ClockLock & ClockBoost Timing Parameters

For the ClockLock and ClockBoost circuitry to function properly, the incoming clock must meet certain requirements. If these specifications are not met, the circuitry may not lock onto the incoming clock, which generates an erroneous clock within the device. The clock generated by the ClockLock and ClockBoost circuitry must also meet certain specifications. If the incoming clock meets these requirements during configuration, the APEX 20K ClockLock and ClockBoost circuitry will lock onto the clock during configuration. The circuit will be ready for use immediately after configuration. In APEX 20KE devices, the clock input standard is programmable, so the PLL cannot respond to the clock until the device is configured. The PLL locks onto the input clock as soon as configuration is complete. Figure 30 shows the incoming and generated clock specifications.

For more information on ClockLock and ClockBoost circuitry, see *Application Note 115: Using the ClockLock and ClockBoost PLL Features in APEX Devices*.

| Symbol          | Parameter             | I/O Standard | -1X Speed Grade |     | -2X Speed Grade |     | Units |

|-----------------|-----------------------|--------------|-----------------|-----|-----------------|-----|-------|

|                 |                       |              | Min             | Max | Min             | Max |       |

| f <sub>IN</sub> | Input clock frequency | 3.3-V LVTTL  | 1.5             | 290 | 1.5             | 257 | MHz   |

|                 |                       | 2.5-V LVTTL  | 1.5             | 281 | 1.5             | 250 | MHz   |

|                 |                       | 1.8-V LVTTL  | 1.5             | 272 | 1.5             | 243 | MHz   |

|                 |                       | GTL+         | 1.5             | 303 | 1.5             | 261 | MHz   |

|                 |                       | SSTL-2 Class | 1.5             | 291 | 1.5             | 253 | MHz   |

|                 |                       | SSTL-2 Class | 1.5             | 291 | 1.5             | 253 | MHz   |

|                 |                       | SSTL-3 Class | 1.5             | 300 | 1.5             | 260 | MHz   |

|                 |                       | SSTL-3 Class | 1.5             | 300 | 1.5             | 260 | MHz   |

|                 |                       | LVDS         | 1.5             | 420 | 1.5             | 350 | MHz   |

#### Notes to Tables 17 and 18:

- All input clock specifications must be met. The PLL may not lock onto an incoming clock if the clock specifications

are not met, creating an erroneous clock within the device.

- (2) The maximum lock time is 40 µs or 2000 input clock cycles, whichever occurs first.

- (3) Before configuration, the PLL circuits are disable and powered down. During configuration, the PLLs are still disabled. The PLLs begin to lock once the device is in the user mode. If the clock enable feature is used, lock begins once the CLKLK ENA pin goes high in user mode.

- (4) The PLL VCO operating range is 200 MHz  $\delta$  f<sub>VCO</sub>  $\delta$  840 MHz for LVDS mode.

# SignalTap Embedded Logic Analyzer

APEX 20K devices include device enhancements to support the SignalTap embedded logic analyzer. By including this circuitry, the APEX 20K device provides the ability to monitor design operation over a period of time through the IEEE Std. 1149.1 (JTAG) circuitry; a designer can analyze internal logic at speed without bringing internal signals to the I/O pins. This feature is particularly important for advanced packages such as FineLine BGA packages because adding a connection to a pin during the debugging process can be difficult after a board is designed and manufactured.

| Device     |                     | IDCODE (32 Bits) (1)  |                                    |           |  |  |  |  |  |  |  |

|------------|---------------------|-----------------------|------------------------------------|-----------|--|--|--|--|--|--|--|

|            | Version<br>(4 Bits) | Part Number (16 Bits) | Manufacturer<br>Identity (11 Bits) | 1 (1 Bit) |  |  |  |  |  |  |  |

| EP20K30E   | 0000                | 1000 0000 0011 0000   | 000 0110 1110                      | 1         |  |  |  |  |  |  |  |

| EP20K60E   | 0000                | 1000 0000 0110 0000   | 000 0110 1110                      | 1         |  |  |  |  |  |  |  |

| EP20K100   | 0000                | 0000 0100 0001 0110   | 000 0110 1110                      | 1         |  |  |  |  |  |  |  |

| EP20K100E  | 0000                | 1000 0001 0000 0000   | 000 0110 1110                      | 1         |  |  |  |  |  |  |  |

| EP20K160E  | 0000                | 1000 0001 0110 0000   | 000 0110 1110                      | 1         |  |  |  |  |  |  |  |

| EP20K200   | 0000                | 0000 1000 0011 0010   | 000 0110 1110                      | 1         |  |  |  |  |  |  |  |

| EP20K200E  | 0000                | 1000 0010 0000 0000   | 000 0110 1110                      | 1         |  |  |  |  |  |  |  |

| EP20K300E  | 0000                | 1000 0011 0000 0000   | 000 0110 1110                      | 1         |  |  |  |  |  |  |  |

| EP20K400   | 0000                | 0001 0110 0110 0100   | 000 0110 1110                      | 1         |  |  |  |  |  |  |  |

| EP20K400E  | 0000                | 1000 0100 0000 0000   | 000 0110 1110                      | 1         |  |  |  |  |  |  |  |

| EP20K600E  | 0000                | 1000 0110 0000 0000   | 000 0110 1110                      | 1         |  |  |  |  |  |  |  |

| EP20K1000E | 0000                | 1001 0000 0000 0000   | 000 0110 1110                      | 1         |  |  |  |  |  |  |  |

#### Notes to Table 21:

- (1) The most significant bit (MSB) is on the left.

- (2) The IDCODE's least significant bit (LSB) is always 1.

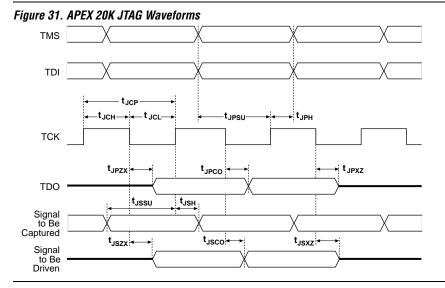

Figure 31 shows the timing requirements for the JTAG signals.

Tables 40 through 42 show the  $f_{\mbox{\scriptsize MAX}}$  timing parameters for EP20K100, EP20K200, and EP20K400 APEX 20K devices.

| Symbol                  | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Units |

|-------------------------|----------------|-----|----------------|-----|----------------|-----|-------|

|                         | Min            | Max | Min            | Max | Min            | Max |       |

| t <sub>SU</sub>         | 0.5            |     | 0.6            |     | 0.8            |     | ns    |

| t <sub>H</sub>          | 0.7            |     | 0.8            |     | 1.0            |     | ns    |

| t <sub>CO</sub>         |                | 0.3 |                | 0.4 |                | 0.5 | ns    |

| t <sub>LUT</sub>        |                | 0.8 |                | 1.0 |                | 1.3 | ns    |

| t <sub>ESBRC</sub>      |                | 1.7 |                | 2.1 |                | 2.4 | ns    |

| t <sub>ESBWC</sub>      |                | 5.7 |                | 6.9 |                | 8.1 | ns    |

| t <sub>ESBWESU</sub>    | 3.3            |     | 3.9            |     | 4.6            |     | ns    |

| t <sub>ESBDATASU</sub>  | 2.2            |     | 2.7            |     | 3.1            |     | ns    |

| t <sub>ESBDATAH</sub>   | 0.6            |     | 0.8            |     | 0.9            |     | ns    |

| t <sub>ESBADDRSU</sub>  | 2.4            |     | 2.9            |     | 3.3            |     | ns    |

| t <sub>ESBDATACO1</sub> |                | 1.3 |                | 1.6 |                | 1.8 | ns    |

| t <sub>ESBDATACO2</sub> |                | 2.6 |                | 3.1 |                | 3.6 | ns    |

| t <sub>ESBDD</sub>      |                | 2.5 |                | 3.3 |                | 3.6 | ns    |

| t <sub>PD</sub>         |                | 2.5 |                | 3.0 |                | 3.6 | ns    |

| t <sub>PTERMSU</sub>    | 2.3            |     | 2.6            |     | 3.2            |     | ns    |

| t <sub>PTERMCO</sub>    |                | 1.5 |                | 1.8 |                | 2.1 | ns    |

| t <sub>F1-4</sub>       |                | 0.5 |                | 0.6 |                | 0.7 | ns    |

| t <sub>F5-20</sub>      |                | 1.6 |                | 1.7 |                | 1.8 | ns    |

| t <sub>F20+</sub>       |                | 2.2 |                | 2.2 |                | 2.3 | ns    |

| t <sub>CH</sub>         | 2.0            |     | 2.5            |     | 3.0            |     | ns    |

| t <sub>CL</sub>         | 2.0            |     | 2.5            |     | 3.0            |     | ns    |

| t <sub>CLRP</sub>       | 0.3            |     | 0.4            |     | 0.4            |     | ns    |

| t <sub>PREP</sub>       | 0.5            |     | 0.5            |     | 0.5            |     | ns    |

| t <sub>ESBCH</sub>      | 2.0            |     | 2.5            |     | 3.0            |     | ns    |

| t <sub>ESBCL</sub>      | 2.0            |     | 2.5            |     | 3.0            |     | ns    |

| t <sub>ESBWP</sub>      | 1.6            |     | 1.9            |     | 2.2            |     | ns    |

| t <sub>ESBRP</sub>      | 1.0            |     | 1.3            |     | 1.4            |     | ns    |

| Symbol                     | -1   |      | -2   |      | -3   |      | Unit |

|----------------------------|------|------|------|------|------|------|------|

|                            | Min  | Max  | Min  | Max  | Min  | Max  | 1    |

| t <sub>INSUBIDIR</sub>     | 2.77 |      | 2.91 |      | 3.11 |      | ns   |

| t <sub>INHBIDIR</sub>      | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>OUTCOBIDIR</sub>    | 2.00 | 4.84 | 2.00 | 5.31 | 2.00 | 5.81 | ns   |

| t <sub>XZBIDIR</sub>       |      | 6.47 |      | 7.44 |      | 8.65 | ns   |

| t <sub>ZXBIDIR</sub>       |      | 6.47 |      | 7.44 |      | 8.65 | ns   |

| t <sub>INSUBIDIRPLL</sub>  | 3.44 |      | 3.24 |      | -    |      | ns   |

| tinhbidirpll               | 0.00 |      | 0.00 |      | -    |      | ns   |

| <sup>t</sup> OUTCOBIDIRPLL | 0.50 | 3.37 | 0.50 | 3.69 | -    | -    | ns   |

| txzbidirpll                |      | 5.00 |      | 5.82 |      | -    | ns   |

| tzxbidirpll                |      | 5.00 |      | 5.82 |      | -    | ns   |

Tables 61 through 66 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K100E APEX 20KE devices.

| Table 61. EP20K100E f <sub>MAX</sub> LE Timing Microparameters |      |      |      |      |      |      |      |  |  |  |

|----------------------------------------------------------------|------|------|------|------|------|------|------|--|--|--|

| Symbol                                                         | -    | 1    | -2   |      | -3   |      | Unit |  |  |  |

|                                                                | Min  | Max  | Min  | Max  | Min  | Max  |      |  |  |  |

| t <sub>SU</sub>                                                | 0.25 |      | 0.25 |      | 0.25 |      | ns   |  |  |  |

| t <sub>H</sub>                                                 | 0.25 |      | 0.25 |      | 0.25 |      | ns   |  |  |  |

| t <sub>CO</sub>                                                |      | 0.28 |      | 0.28 |      | 0.34 | ns   |  |  |  |

| t <sub>LUT</sub>                                               |      | 0.80 |      | 0.95 |      | 1.13 | ns   |  |  |  |

| Symbol                  | -1    |      | -2    |      | -3   |      | Unit |

|-------------------------|-------|------|-------|------|------|------|------|

|                         | Min   | Max  | Min   | Max  | Min  | Max  |      |

| t <sub>ESBARC</sub>     |       | 1.68 |       | 2.06 |      | 2.24 | ns   |

| t <sub>ESBSRC</sub>     |       | 2.27 |       | 2.77 |      | 3.18 | ns   |

| t <sub>ESBAWC</sub>     |       | 3.10 |       | 3.86 |      | 4.50 | ns   |

| t <sub>ESBSWC</sub>     |       | 2.90 |       | 3.67 |      | 4.21 | ns   |

| t <sub>ESBWASU</sub>    | 0.55  |      | 0.67  |      | 0.74 |      | ns   |

| t <sub>ESBWAH</sub>     | 0.36  |      | 0.46  |      | 0.48 |      | ns   |

| t <sub>ESBWDSU</sub>    | 0.69  |      | 0.83  |      | 0.95 |      | ns   |

| t <sub>ESBWDH</sub>     | 0.36  |      | 0.46  |      | 0.48 |      | ns   |

| t <sub>ESBRASU</sub>    | 1.61  |      | 1.90  |      | 2.09 |      | ns   |

| t <sub>ESBRAH</sub>     | 0.00  |      | 0.00  |      | 0.01 |      | ns   |

| t <sub>ESBWESU</sub>    | 1.42  |      | 1.71  |      | 2.01 |      | ns   |

| t <sub>ESBWEH</sub>     | 0.00  |      | 0.00  |      | 0.00 |      | ns   |

| t <sub>ESBDATASU</sub>  | -0.06 |      | -0.07 |      | 0.05 |      | ns   |

| t <sub>ESBDATAH</sub>   | 0.13  |      | 0.13  |      | 0.13 |      | ns   |

| t <sub>ESBWADDRSU</sub> | 0.11  |      | 0.13  |      | 0.31 |      | ns   |

| t <sub>ESBRADDRSU</sub> | 0.18  |      | 0.23  |      | 0.39 |      | ns   |

| t <sub>ESBDATACO1</sub> |       | 1.09 |       | 1.35 |      | 1.51 | ns   |

| t <sub>ESBDATACO2</sub> |       | 2.19 |       | 2.75 |      | 3.22 | ns   |

| t <sub>ESBDD</sub>      |       | 2.75 |       | 3.41 |      | 4.03 | ns   |

| t <sub>PD</sub>         |       | 1.58 |       | 1.97 |      | 2.33 | ns   |

| t <sub>PTERMSU</sub>    | 1.00  |      | 1.22  |      | 1.51 |      | ns   |

| t <sub>PTERMCO</sub>    |       | 1.10 |       | 1.37 |      | 1.09 | ns   |

| Table 75. EP20K200E f <sub>MAX</sub> Routing Delays |     |      |     |      |     |      |    |

|-----------------------------------------------------|-----|------|-----|------|-----|------|----|

| Symbol                                              | -   | 1    | -2  |      | -:  | Unit |    |

|                                                     | Min | Max  | Min | Max  | Min | Max  |    |

| t <sub>F1-4</sub>                                   |     | 0.25 |     | 0.27 |     | 0.29 | ns |

| t <sub>F5-20</sub>                                  |     | 1.02 |     | 1.20 |     | 1.41 | ns |

| t <sub>F20+</sub>                                   |     | 1.99 |     | 2.23 |     | 2.53 | ns |

| Symbol                    | -1 Speed Grade |      | -2 Speed Grade |      | -3 Speed Grade |      | Unit |

|---------------------------|----------------|------|----------------|------|----------------|------|------|

|                           | Min            | Max  | Min            | Max  | Min            | Max  |      |

| t <sub>INSUBIDIR</sub>    | 2.93           |      | 3.23           |      | 3.44           |      | ns   |

| t <sub>INHBIDIR</sub>     | 0.00           |      | 0.00           |      | 0.00           |      | ns   |

| toutcobidir               | 2.00           | 5.25 | 2.00           | 5.79 | 2.00           | 6.32 | ns   |

| t <sub>XZBIDIR</sub>      |                | 5.95 |                | 6.77 |                | 7.12 | ns   |

| tzxbidir                  |                | 5.95 |                | 6.77 |                | 7.12 | ns   |

| t <sub>INSUBIDIRPLL</sub> | 4.31           |      | 4.76           |      | -              |      | ns   |

| tinhbidirpll              | 0.00           |      | 0.00           |      | -              |      | ns   |

| toutcobidirpll            | 0.50           | 2.25 | 0.50           | 2.45 | -              | -    | ns   |

| txzbidirpll               |                | 2.94 |                | 3.43 |                | -    | ns   |

| tzxbidirpll               |                | 2.94 |                | 3.43 |                | -    | ns   |

Tables 91 through 96 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K600E APEX 20KE devices.

| Table 91. EP20K600E f <sub>MAX</sub> LE Timing Microparameters |      |                  |      |          |         |                |    |  |

|----------------------------------------------------------------|------|------------------|------|----------|---------|----------------|----|--|

| Symbol -1 S                                                    |      | ed Grade -2 Spee |      | ed Grade | -3 Spee | -3 Speed Grade |    |  |

|                                                                | Min  | Max              | Min  | Max      | Min     | Max            |    |  |

| t <sub>SU</sub>                                                | 0.16 |                  | 0.16 |          | 0.17    |                | ns |  |

| t <sub>H</sub>                                                 | 0.29 |                  | 0.33 |          | 0.37    |                | ns |  |

| t <sub>CO</sub>                                                |      | 0.65             |      | 0.38     |         | 0.49           | ns |  |

| t <sub>LUT</sub>                                               |      | 0.70             |      | 1.00     |         | 1.30           | ns |  |

| Symbol                    | -1 Speed Grade |      | -2 Speed Grade |      | -3 Speed Grade |      | Unit |

|---------------------------|----------------|------|----------------|------|----------------|------|------|

|                           | Min            | Max  | Min            | Max  | Min            | Max  | 1    |

| t <sub>INSUBIDIR</sub>    | 3.47           |      | 3.68           |      | 3.99           |      | ns   |

| t <sub>INHBIDIR</sub>     | 0.00           |      | 0.00           |      | 0.00           |      | ns   |

| toutcobidir               | 2.00           | 6.18 | 2.00           | 6.81 | 2.00           | 7.36 | ns   |

| t <sub>XZBIDIR</sub>      |                | 6.91 |                | 7.62 |                | 8.38 | ns   |

| t <sub>ZXBIDIR</sub>      |                | 6.91 |                | 7.62 |                | 8.38 | ns   |

| t <sub>INSUBIDIRPLL</sub> | 3.05           |      | 3.26           |      |                |      | ns   |

| t <sub>INHBIDIRPLL</sub>  | 0.00           |      | 0.00           |      |                |      | ns   |

| toutcobidirpll            | 0.50           | 2.67 | 0.50           | 2.99 |                |      | ns   |

| t <sub>XZBIDIRPLL</sub>   |                | 3.41 |                | 3.80 |                |      | ns   |

| tzxbidirpll               |                | 3.41 |                | 3.80 |                |      | ns   |

Tables 109 and 110 show selectable I/O standard input and output delays for APEX 20KE devices. If you select an I/O standard input or output delay other than LVCMOS, add or subtract the selected speed grade to or from the LVCMOS value.

| Table 109. Selectable I/O Standard Input Delays |                |       |                |       |                |       |      |  |

|-------------------------------------------------|----------------|-------|----------------|-------|----------------|-------|------|--|

| Symbol                                          | -1 Speed Grade |       | -2 Speed Grade |       | -3 Speed Grade |       | Unit |  |

|                                                 | Min            | Max   | Min            | Max   | Min            | Max   | Min  |  |

| LVCMOS                                          |                | 0.00  |                | 0.00  |                | 0.00  | ns   |  |

| LVTTL                                           |                | 0.00  |                | 0.00  |                | 0.00  | ns   |  |

| 2.5 V                                           |                | 0.00  |                | 0.04  |                | 0.05  | ns   |  |

| 1.8 V                                           |                | -0.11 |                | 0.03  |                | 0.04  | ns   |  |

| PCI                                             |                | 0.01  |                | 0.09  |                | 0.10  | ns   |  |

| GTL+                                            |                | -0.24 |                | -0.23 |                | -0.19 | ns   |  |

| SSTL-3 Class I                                  |                | -0.32 |                | -0.21 |                | -0.47 | ns   |  |

| SSTL-3 Class II                                 |                | -0.08 |                | 0.03  |                | -0.23 | ns   |  |

| SSTL-2 Class I                                  |                | -0.17 |                | -0.06 |                | -0.32 | ns   |  |

| SSTL-2 Class II                                 |                | -0.16 |                | -0.05 |                | -0.31 | ns   |  |

| LVDS                                            |                | -0.12 |                | -0.12 |                | -0.12 | ns   |  |

| CTT                                             |                | 0.00  |                | 0.00  |                | 0.00  | ns   |  |

| AGP                                             |                | 0.00  |                | 0.00  |                | 0.00  | ns   |  |

SRAM configuration elements allow APEX 20K devices to be reconfigured in-circuit by loading new configuration data into the device. Real-time reconfiguration is performed by forcing the device into command mode with a device pin, loading different configuration data, reinitializing the device, and resuming usermode operation. In-field upgrades can be performed by distributing new configuration files.

#### **Configuration Schemes**

The configuration data for an APEX 20K device can be loaded with one of five configuration schemes (see Table 111), chosen on the basis of the target application. An EPC2 or EPC16 configuration device, intelligent controller, or the JTAG port can be used to control the configuration of an APEX 20K device. When a configuration device is used, the system can configure automatically at system power-up.

Multiple APEX 20K devices can be configured in any of five configuration schemes by connecting the configuration enable (nCE) and configuration enable output (nCEO) pins on each device.

| Table 111. Data Sources for Configuration |                                                                                          |  |  |  |  |

|-------------------------------------------|------------------------------------------------------------------------------------------|--|--|--|--|

| Configuration Scheme                      | Data Source                                                                              |  |  |  |  |

| Configuration device                      | EPC1, EPC2, EPC16 configuration devices                                                  |  |  |  |  |

| Passive serial (PS)                       | MasterBlaster or ByteBlasterMV download cable or serial data source                      |  |  |  |  |

| Passive parallel asynchronous (PPA)       | Parallel data source                                                                     |  |  |  |  |

| Passive parallel synchronous (PPS)        | Parallel data source                                                                     |  |  |  |  |

| JTAG                                      | MasterBlaster or ByteBlasterMV download cable or a microprocessor with a Jam or JBC File |  |  |  |  |

For more information on configuration, see *Application Note* 116 (*Configuring APEX 20K, FLEX 10K, & FLEX 6000 Devices.*)

# **Device Pin-Outs**

See the Altera web site (http://www.altera.com) or the *Altera Digital Library* for pin-out information