## E·XFL

### Altera - EP20K300EQC240-2X Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                |

|--------------------------------|----------------------------------------------------------------|

| Product Status                 | Active                                                         |

| Number of LABs/CLBs            | -                                                              |

| Number of Logic Elements/Cells | -                                                              |

| Total RAM Bits                 | -                                                              |

| Number of I/O                  | 152                                                            |

| Number of Gates                | -                                                              |

| Voltage - Supply               | 1.71V ~ 1.89V                                                  |

| Mounting Type                  | Surface Mount                                                  |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                |

| Package / Case                 | 240-BQFP                                                       |

| Supplier Device Package        | 240-PQFP (32x32)                                               |

| Purchase URL                   | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=ep20k300eqc240-2x |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Functional Description

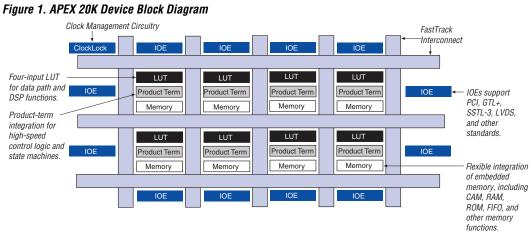

APEX 20K devices incorporate LUT-based logic, product-term-based logic, and memory into one device. Signal interconnections within APEX 20K devices (as well as to and from device pins) are provided by the FastTrack<sup>®</sup> Interconnect—a series of fast, continuous row and column channels that run the entire length and width of the device.

Each I/O pin is fed by an I/O element (IOE) located at the end of each row and column of the FastTrack Interconnect. Each IOE contains a bidirectional I/O buffer and a register that can be used as either an input or output register to feed input, output, or bidirectional signals. When used with a dedicated clock pin, these registers provide exceptional performance. IOEs provide a variety of features, such as 3.3-V, 64-bit, 66-MHz PCI compliance; JTAG BST support; slew-rate control; and tri-state buffers. APEX 20KE devices offer enhanced I/O support, including support for 1.8-V I/O, 2.5-V I/O, LVCMOS, LVTTL, LVPECL, 3.3-V PCI, PCI-X, LVDS, GTL+, SSTL-2, SSTL-3, HSTL, CTT, and 3.3-V AGP I/O standards.

The ESB can implement a variety of memory functions, including CAM, RAM, dual-port RAM, ROM, and FIFO functions. Embedding the memory directly into the die improves performance and reduces die area compared to distributed-RAM implementations. Moreover, the abundance of cascadable ESBs ensures that the APEX 20K device can implement multiple wide memory blocks for high-density designs. The ESB's high speed ensures it can implement small memory blocks without any speed penalty. The abundance of ESBs ensures that designers can create as many different-sized memory blocks as the system requires. Figure 1 shows an overview of the APEX 20K device.

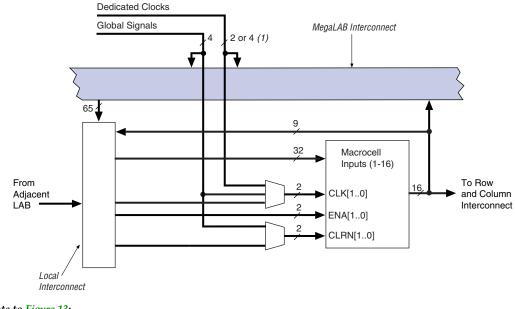

#### Figure 13. Product-Term Logic in ESB

#### Note to Figure 13:

(1) APEX 20KE devices have four dedicated clocks.

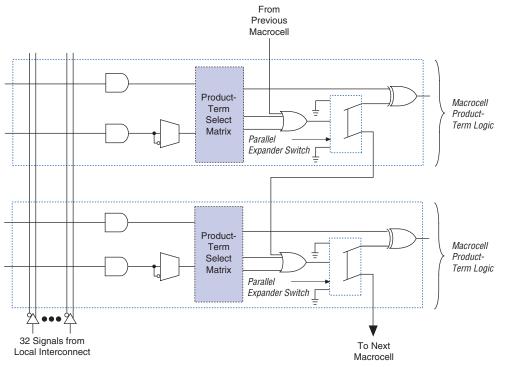

#### Macrocells

APEX 20K macrocells can be configured individually for either sequential or combinatorial logic operation. The macrocell consists of three functional blocks: the logic array, the product-term select matrix, and the programmable register.

Combinatorial logic is implemented in the product terms. The productterm select matrix allocates these product terms for use as either primary logic inputs (to the OR and XOR gates) to implement combinatorial functions, or as parallel expanders to be used to increase the logic available to another macrocell. One product term can be inverted; the Quartus II software uses this feature to perform DeMorgan's inversion for more efficient implementation of wide OR functions. The Quartus II software Compiler can use a NOT-gate push-back technique to emulate an asynchronous preset. Figure 14 shows the APEX 20K macrocell.

## Embedded System Block

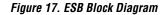

The ESB can implement various types of memory blocks, including dual-port RAM, ROM, FIFO, and CAM blocks. The ESB includes input and output registers; the input registers synchronize writes, and the output registers can pipeline designs to improve system performance. The ESB offers a dual-port mode, which supports simultaneous reads and writes at two different clock frequencies. Figure 17 shows the ESB block diagram.

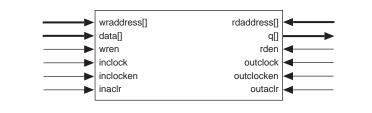

#### Figure 23. APEX 20KE CAM Block Diagram

CAM can be used in any application requiring high-speed searches, such as networking, communications, data compression, and cache management.

The APEX 20KE on-chip CAM provides faster system performance than traditional discrete CAM. Integrating CAM and logic into the APEX 20KE device eliminates off-chip and on-chip delays, improving system performance.

When in CAM mode, the ESB implements 32-word, 32-bit CAM. Wider or deeper CAM can be implemented by combining multiple CAMs with some ancillary logic implemented in LEs. The Quartus II software combines ESBs and LEs automatically to create larger CAMs.

CAM supports writing "don't care" bits into words of the memory. The "don't-care" bit can be used as a mask for CAM comparisons; any bit set to "don't-care" has no effect on matches.

The output of the CAM can be encoded or unencoded. When encoded, the ESB outputs an encoded address of the data's location. For instance, if the data is located in address 12, the ESB output is 12. When unencoded, the ESB uses its 16 outputs to show the location of the data over two clock cycles. In this case, if the data is located in address 12, the 12th output line goes high. When using unencoded outputs, two clock cycles are required to read the output because a 16-bit output bus is used to show the status of 32 words.

The encoded output is better suited for designs that ensure duplicate data is not written into the CAM. If duplicate data is written into two locations, the CAM's output will be incorrect. If the CAM may contain duplicate data, the unencoded output is a better solution; CAM with unencoded outputs can distinguish multiple data locations.

CAM can be pre-loaded with data during configuration, or it can be written during system operation. In most cases, two clock cycles are required to write each word into CAM. When "don't-care" bits are used, a third clock cycle is required.

#### Advanced I/O Standard Support

APEX 20KE IOEs support the following I/O standards: LVTTL, LVCMOS, 1.8-V I/O, 2.5-V I/O, 3.3-V PCI, PCI-X, 3.3-V AGP, LVDS, LVPECL, GTL+, CTT, HSTL Class I, SSTL-3 Class I and II, and SSTL-2 Class I and II.

For more information on I/O standards supported by APEX 20KE devices, see *Application Note* 117 (*Using Selectable I/O Standards in Altera Devices*).

The APEX 20KE device contains eight I/O banks. In QFP packages, the banks are linked to form four I/O banks. The I/O banks directly support all standards except LVDS and LVPECL. All I/O banks can support LVDS and LVPECL with the addition of external resistors. In addition, one block within a bank contains circuitry to support high-speed True-LVDS and LVPECL inputs, and another block within a particular bank supports high-speed True-LVDS and LVPECL outputs. The LVDS blocks support all of the I/O standards. Each I/O bank has its own VCCIO pins. A single device can support 1.8-V, 2.5-V, and 3.3-V interfaces; each bank can support a different standard independently. Each bank can also use a separate V<sub>REF</sub> level so that each bank can support any of the terminated standards (such as SSTL-3) independently. Within a bank, any one of the terminated standards can be supported. EP20K300E and larger APEX 20KE devices support the LVDS interface for data pins (smaller devices support LVDS clock pins, but not data pins). All EP20K300E and larger devices support the LVDS interface for data pins up to 155 Mbit per channel; EP20K400E devices and larger with an X-suffix on the ordering code add a serializer/deserializer circuit and PLL for higher-speed support.

Each bank can support multiple standards with the same VCCIO for output pins. Each bank can support one voltage-referenced I/O standard, but it can support multiple I/O standards with the same VCCIO voltage level. For example, when VCCIO is 3.3 V, a bank can support LVTTL, LVCMOS, 3.3-V PCI, and SSTL-3 for inputs and outputs.

When the LVDS banks are not used as LVDS I/O banks, they support all of the other I/O standards. Figure 29 shows the arrangement of the APEX 20KE I/O banks.

Under hot socketing conditions, APEX 20KE devices will not sustain any damage, but the I/O pins will drive out.

## MultiVolt I/O Interface

The APEX device architecture supports the MultiVolt I/O interface feature, which allows APEX devices in all packages to interface with systems of different supply voltages. The devices have one set of VCC pins for internal operation and input buffers (VCCINT), and another set for I/O output drivers (VCCIO).

The APEX 20K VCCINT pins must always be connected to a 2.5 V power supply. With a 2.5-V V<sub>CCINT</sub> level, input pins are 2.5-V, 3.3-V, and 5.0-V tolerant. The VCCIO pins can be connected to either a 2.5-V or 3.3-V power supply, depending on the output requirements. When VCCIO pins are connected to a 2.5-V power supply, the output levels are compatible with 2.5-V systems. When the VCCIO pins are connected to a 3.3-V power supply, the output high is 3.3 V and is compatible with 3.3-V or 5.0-V systems.

| Table 12.             | 5.0-V Tolei  | rant APEX 20 | OK MultiVolt       | I/O Support           |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------|--------------|--------------|--------------------|-----------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CCIO</sub> (V) | Ir           | put Signals  | Output Signals (V) |                       |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| -                     | 2.5          | 3.3          | 5.0                | 2.5                   | 3.3          | 5.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.5                   | $\checkmark$ | √(1)         | <b>√</b> (1)       | <ul> <li>✓</li> </ul> |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.3                   | $\checkmark$ | $\checkmark$ | <b>√</b> (1)       | <b>√</b> (2)          | $\checkmark$ | <ul> <li>Image: A start of the start of</li></ul> |

Table 12 summarizes 5.0-V tolerant APEX 20K MultiVolt I/O support.

#### Notes to Table 12:

- The PCI clamping diode must be disabled to drive an input with voltages higher than V<sub>CCIO</sub>.

- (2) When  $V_{CCIO} = 3.3 \text{ V}$ , an APEX 20K device can drive a 2.5-V device with 3.3-V tolerant inputs.

Open-drain output pins on 5.0-V tolerant APEX 20K devices (with a pullup resistor to the 5.0-V supply) can drive 5.0-V CMOS input pins that require a V<sub>IH</sub> of 3.5 V. When the pin is inactive, the trace will be pulled up to 5.0 V by the resistor. The open-drain pin will only drive low or tri-state; it will never drive high. The rise time is dependent on the value of the pullup resistor and load impedance. The I<sub>OL</sub> current specification should be considered when selecting a pull-up resistor.

#### Clock Phase & Delay Adjustment

The APEX 20KE ClockShift feature allows the clock phase and delay to be adjusted. The clock phase can be adjusted by 90° steps. The clock delay can be adjusted to increase or decrease the clock delay by an arbitrary amount, up to one clock period.

#### LVDS Support

Two PLLs are designed to support the LVDS interface. When using LVDS, the I/O clock runs at a slower rate than the data transfer rate. Thus, PLLs are used to multiply the I/O clock internally to capture the LVDS data. For example, an I/O clock may run at 105 MHz to support 840 megabits per second (Mbps) LVDS data transfer. In this example, the PLL multiplies the incoming clock by eight to support the high-speed data transfer. You can use PLLs in EP20K400E and larger devices for high-speed LVDS interfacing.

#### Lock Signals

The APEX 20KE ClockLock circuitry supports individual LOCK signals. The LOCK signal drives high when the ClockLock circuit has locked onto the input clock. The LOCK signals are optional for each ClockLock circuit; when not used, they are I/O pins.

#### ClockLock & ClockBoost Timing Parameters

For the ClockLock and ClockBoost circuitry to function properly, the incoming clock must meet certain requirements. If these specifications are not met, the circuitry may not lock onto the incoming clock, which generates an erroneous clock within the device. The clock generated by the ClockLock and ClockBoost circuitry must also meet certain specifications. If the incoming clock meets these requirements during configuration, the APEX 20K ClockLock and ClockBoost circuitry will lock onto the clock during configuration. The circuit will be ready for use immediately after configuration. In APEX 20KE devices, the clock input standard is programmable, so the PLL cannot respond to the clock until the device is configured. The PLL locks onto the input clock as soon as configuration is complete. Figure 30 shows the incoming and generated clock specifications.

For more information on ClockLock and ClockBoost circuitry, see Application Note 115: Using the ClockLock and ClockBoost PLL Features in APEX Devices.

#### Notes to Table 16:

- (1) To implement the ClockLock and ClockBoost circuitry with the Quartus II software, designers must specify the input frequency. The Quartus II software tunes the PLL in the ClockLock and ClockBoost circuitry to this frequency. The *f<sub>CLKDEV</sub>* parameter specifies how much the incoming clock can differ from the specified frequency during device operation. Simulation does not reflect this parameter.

- (2) Twenty-five thousand parts per million (PPM) equates to 2.5% of input clock period.

- (3) During device configuration, the ClockLock and ClockBoost circuitry is configured before the rest of the device. If the incoming clock is supplied during configuration, the ClockLock and ClockBoost circuitry locks during configuration because the t<sub>LOCK</sub> value is less than the time required for configuration.

- (4) The  $t_{IITTER}$  specification is measured under long-term observation.

Tables 17 and 18 summarize the ClockLock and ClockBoost parameters for APEX 20KE devices.

| Table 17. APEX 20KE ClockLock & ClockBoost Parameters       Note (1) |                                                              |            |     |     |                        |                  |  |

|----------------------------------------------------------------------|--------------------------------------------------------------|------------|-----|-----|------------------------|------------------|--|

| Symbol                                                               | Parameter                                                    | Conditions | Min | Тур | Мах                    | Unit             |  |

| t <sub>R</sub>                                                       | Input rise time                                              |            |     |     | 5                      | ns               |  |

| t <sub>F</sub>                                                       | Input fall time                                              |            |     |     | 5                      | ns               |  |

| t <sub>INDUTY</sub>                                                  | Input duty cycle                                             |            | 40  |     | 60                     | %                |  |

| t <sub>INJITTER</sub>                                                | Input jitter peak-to-peak                                    |            |     |     | 2% of input<br>period  | peak-to-<br>peak |  |

|                                                                      | Jitter on ClockLock or ClockBoost-<br>generated clock        |            |     |     | 0.35% of output period | RMS              |  |

| t <sub>OUTDUTY</sub>                                                 | Duty cycle for ClockLock or<br>ClockBoost-generated clock    |            | 45  |     | 55                     | %                |  |

| t <sub>LOCK</sub> (2) <sub>,</sub> (3)                               | Time required for ClockLock or<br>ClockBoost to acquire lock |            |     |     | 40                     | μs               |  |

| Table 2            | 8. APEX 20KE Device Recommende                      | ed Operating Conditions |                  |                   |      |

|--------------------|-----------------------------------------------------|-------------------------|------------------|-------------------|------|

| Symbol             | Parameter                                           | Conditions              | Min              | Max               | Unit |

| V <sub>CCINT</sub> | Supply voltage for internal logic and input buffers | (3), (4)                | 1.71 (1.71)      | 1.89 (1.89)       | V    |

| V <sub>CCIO</sub>  | Supply voltage for output buffers, 3.3-V operation  | (3), (4)                | 3.00 (3.00)      | 3.60 (3.60)       | V    |

|                    | Supply voltage for output buffers, 2.5-V operation  | (3), (4)                | 2.375<br>(2.375) | 2.625<br>(2.625)  | V    |

|                    | Supply voltage for output buffers, 1.8-V operation  | (3), (4)                | 1.71 (1.71)      | 1.89 (1.89)       | V    |

| VI                 | Input voltage                                       | (5), (6)                | -0.5             | 4.0               | V    |

| Vo                 | Output voltage                                      |                         | 0                | V <sub>CCIO</sub> | V    |

| ТJ                 | Junction temperature                                | For commercial use      | 0                | 85                | °C   |

|                    |                                                     | For industrial use      | -40              | 100               | °C   |

| t <sub>R</sub>     | Input rise time                                     |                         |                  | 40                | ns   |

| t <sub>F</sub>     | Input fall time                                     |                         |                  | 40                | ns   |

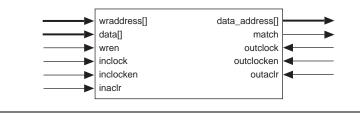

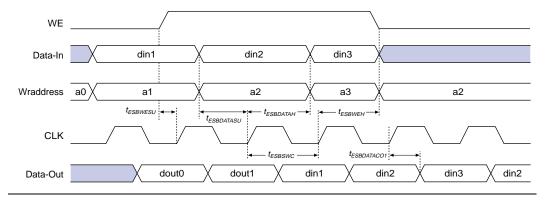

Figure 39. ESB Synchronous Timing Waveforms

#### ESB Synchronous Write (ESB Output Registers Used)

Figure 40 shows the timing model for bidirectional I/O pin timing.

| Table 36. APEX 20KE Routing Timing Microparameters         Note (1) |                                                    |  |  |  |  |  |

|---------------------------------------------------------------------|----------------------------------------------------|--|--|--|--|--|

| Symbol                                                              | Parameter                                          |  |  |  |  |  |

| t <sub>F1-4</sub>                                                   | Fanout delay using Local Interconnect              |  |  |  |  |  |

| t <sub>F5-20</sub>                                                  | Fanout delay estimate using MegaLab Interconnect   |  |  |  |  |  |

| t <sub>F20+</sub>                                                   | Fanout delay estimate using FastTrack Interconnect |  |  |  |  |  |

#### Note to Table 36:

These parameters are worst-case values for typical applications. Post-compilation timing simulation and timing analysis are required to determine actual worst-case performance.

| Table 37. APEX 20KE Functional Timing Microparameters         Symbol       Parameter |                                        |  |  |  |  |  |

|--------------------------------------------------------------------------------------|----------------------------------------|--|--|--|--|--|

| Symbol                                                                               | i alainetei                            |  |  |  |  |  |

| тсн                                                                                  | Minimum clock high time from clock pin |  |  |  |  |  |

| TCL                                                                                  | Minimum clock low time from clock pin  |  |  |  |  |  |

| TCLRP                                                                                | LE clear Pulse Width                   |  |  |  |  |  |

| TPREP                                                                                | LE preset pulse width                  |  |  |  |  |  |

| TESBCH                                                                               | Clock high time for ESB                |  |  |  |  |  |

| TESBCL                                                                               | Clock low time for ESB                 |  |  |  |  |  |

| TESBWP                                                                               | Write pulse width                      |  |  |  |  |  |

| TESBRP                                                                               | Read pulse width                       |  |  |  |  |  |

## Table 37. APEX 20KE Functional Timing Microparameters

Tables 38 and 39 describe the APEX 20KE external timing parameters.

| Table 38. APEX 20KE External Timing Parameters       Note (1) |                                                                |            |  |  |  |  |  |

|---------------------------------------------------------------|----------------------------------------------------------------|------------|--|--|--|--|--|

| Symbol                                                        | nbol Clock Parameter                                           |            |  |  |  |  |  |

| t <sub>INSU</sub>                                             | Setup time with global clock at IOE input register             |            |  |  |  |  |  |

| t <sub>INH</sub>                                              | Hold time with global clock at IOE input register              |            |  |  |  |  |  |

| t <sub>оитсо</sub>                                            | Clock-to-output delay with global clock at IOE output register | C1 = 10 pF |  |  |  |  |  |

| t <sub>INSUPLL</sub>                                          | Setup time with PLL clock at IOE input register                |            |  |  |  |  |  |

| t <sub>INHPLL</sub>                                           | Hold time with PLL clock at IOE input register                 |            |  |  |  |  |  |

| t <sub>OUTCOPLL</sub>                                         | Clock-to-output delay with PLL clock at IOE output register    | C1 = 10 pF |  |  |  |  |  |

| Symbol                        | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|-------------------------------|----------------|-----|----------------|-----|----------------|-----|------|

|                               | Min            | Max | Min            | Max | Min            | Мах |      |

| t <sub>INSU</sub> (1)         | 2.3            |     | 2.8            |     | 3.2            |     | ns   |

| t <sub>INH</sub> (1)          | 0.0            |     | 0.0            |     | 0.0            |     | ns   |

| t <sub>OUTCO</sub> (1)        | 2.0            | 4.5 | 2.0            | 4.9 | 2.0            | 6.6 | ns   |

| t <sub>INSU</sub> (2)         | 1.1            |     | 1.2            |     | -              |     | ns   |

| t <sub>INH</sub> (2)          | 0.0            |     | 0.0            |     | -              |     | ns   |

| t <sub>оитсо</sub> <i>(2)</i> | 0.5            | 2.7 | 0.5            | 3.1 | _              | 4.8 | ns   |

| Table 44. EP20K100 External Bidirectional Timing Parameters |                |     |                |     |                |     |      |  |

|-------------------------------------------------------------|----------------|-----|----------------|-----|----------------|-----|------|--|

| Symbol                                                      | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |  |

|                                                             | Min            | Max | Min            | Max | Min            | Max |      |  |

| t <sub>INSUBIDIR</sub> (1)                                  | 2.3            |     | 2.8            |     | 3.2            |     | ns   |  |

| t <sub>INHBIDIR</sub> (1)                                   | 0.0            |     | 0.0            |     | 0.0            |     | ns   |  |

| toutcobidir<br>(1)                                          | 2.0            | 4.5 | 2.0            | 4.9 | 2.0            | 6.6 | ns   |  |

| t <sub>XZBIDIR</sub> (1)                                    |                | 5.0 |                | 5.9 |                | 6.9 | ns   |  |

| t <sub>ZXBIDIR</sub> (1)                                    |                | 5.0 |                | 5.9 |                | 6.9 | ns   |  |

| t <sub>insubidir</sub> (2)                                  | 1.0            |     | 1.2            |     | -              |     | ns   |  |

| t <sub>INHBIDIR</sub> (2)                                   | 0.0            |     | 0.0            |     | -              |     | ns   |  |

| toutcobidir<br>(2)                                          | 0.5            | 2.7 | 0.5            | 3.1 | -              | -   | ns   |  |

| t <sub>XZBIDIR</sub> (2)                                    |                | 4.3 |                | 5.0 |                | -   | ns   |  |

| t <sub>ZXBIDIR</sub> (2)                                    |                | 4.3 |                | 5.0 |                | -   | ns   |  |

| Table 45. EP20K200 External Timing Parameters |                |     |                |     |                |     |      |  |

|-----------------------------------------------|----------------|-----|----------------|-----|----------------|-----|------|--|

| Symbol                                        | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |  |

|                                               | Min            | Max | Min            | Мах | Min            | Max |      |  |

| t <sub>INSU</sub> (1)                         | 1.9            |     | 2.3            |     | 2.6            |     | ns   |  |

| t <sub>INH</sub> (1)                          | 0.0            |     | 0.0            |     | 0.0            |     | ns   |  |

| t <sub>OUTCO</sub> (1)                        | 2.0            | 4.6 | 2.0            | 5.6 | 2.0            | 6.8 | ns   |  |

| t <sub>INSU</sub> (2)                         | 1.1            |     | 1.2            |     | -              |     | ns   |  |

| t <sub>INH</sub> (2)                          | 0.0            |     | 0.0            |     | -              |     | ns   |  |

| t <sub>оитсо</sub> <i>(2)</i>                 | 0.5            | 2.7 | 0.5            | 3.1 | -              | -   | ns   |  |

| Symbol             | -1   |     | -2   |     | -3   |     | Unit |

|--------------------|------|-----|------|-----|------|-----|------|

|                    | Min  | Max | Min  | Max | Min  | Мах |      |

| t <sub>CH</sub>    | 0.55 |     | 0.78 |     | 1.15 |     | ns   |

| t <sub>CL</sub>    | 0.55 |     | 0.78 |     | 1.15 |     | ns   |

| t <sub>CLRP</sub>  | 0.22 |     | 0.31 |     | 0.46 |     | ns   |

| t <sub>PREP</sub>  | 0.22 |     | 0.31 |     | 0.46 |     | ns   |

| t <sub>ESBCH</sub> | 0.55 |     | 0.78 |     | 1.15 |     | ns   |

| t <sub>ESBCL</sub> | 0.55 |     | 0.78 |     | 1.15 |     | ns   |

| t <sub>ESBWP</sub> | 1.43 |     | 2.01 |     | 2.97 |     | ns   |

| t <sub>ESBRP</sub> | 1.15 |     | 1.62 |     | 2.39 |     | ns   |

| Symbol               | -1   |      | -2   |      | -3   |      | Unit |

|----------------------|------|------|------|------|------|------|------|

|                      | Min  | Мах  | Min  | Max  | Min  | Max  |      |

| t <sub>INSU</sub>    | 2.02 |      | 2.13 |      | 2.24 |      | ns   |

| t <sub>INH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>outco</sub>   | 2.00 | 4.88 | 2.00 | 5.36 | 2.00 | 5.88 | ns   |

| t <sub>INSUPLL</sub> | 2.11 |      | 2.23 |      | -    |      | ns   |

| t <sub>INHPLL</sub>  | 0.00 |      | 0.00 |      | -    |      | ns   |

| toutcopll            | 0.50 | 2.60 | 0.50 | 2.88 | -    | -    | ns   |

| Symbol                    | -1   |      | -    | 2    | -3   |      | Unit |

|---------------------------|------|------|------|------|------|------|------|

|                           | Min  | Max  | Min  | Max  | Min  | Max  |      |

| t <sub>insubidir</sub>    | 1.85 |      | 1.77 |      | 1.54 |      | ns   |

| t <sub>inhbidir</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>outcobidir</sub>   | 2.00 | 4.88 | 2.00 | 5.36 | 2.00 | 5.88 | ns   |

| t <sub>XZBIDIR</sub>      |      | 7.48 |      | 8.46 |      | 9.83 | ns   |

| t <sub>ZXBIDIR</sub>      |      | 7.48 |      | 8.46 |      | 9.83 | ns   |

| t <sub>insubidirpll</sub> | 4.12 |      | 4.24 |      | -    |      | ns   |

| t <sub>inhbidirpll</sub>  | 0.00 |      | 0.00 |      | -    |      | ns   |

| toutcobidirpll            | 0.50 | 2.60 | 0.50 | 2.88 | -    | -    | ns   |

| t <sub>XZBIDIRPLL</sub>   |      | 5.21 |      | 5.99 |      | -    | ns   |

| t <sub>ZXBIDIRPLL</sub>   |      | 5.21 |      | 5.99 |      | -    | ns   |

| Symbol             | Symbol -1 | 1   | -    | 2   | -;   | Unit |    |

|--------------------|-----------|-----|------|-----|------|------|----|

|                    | Min       | Max | Min  | Max | Min  | Max  | _  |

| t <sub>CH</sub>    | 2.00      |     | 2.00 |     | 2.00 |      | ns |

| t <sub>CL</sub>    | 2.00      |     | 2.00 |     | 2.00 |      | ns |

| t <sub>CLRP</sub>  | 0.20      |     | 0.20 |     | 0.20 |      | ns |

| t <sub>PREP</sub>  | 0.20      |     | 0.20 |     | 0.20 |      | ns |

| t <sub>ESBCH</sub> | 2.00      |     | 2.00 |     | 2.00 |      | ns |

| t <sub>ESBCL</sub> | 2.00      |     | 2.00 |     | 2.00 |      | ns |

| t <sub>ESBWP</sub> | 1.29      |     | 1.53 |     | 1.66 |      | ns |

| t <sub>ESBRP</sub> | 1.11      |     | 1.29 |     | 1.41 |      | ns |

| Table 65. EP20K100E External Timing Parameters |      |      |      |      |      |      |      |  |  |  |

|------------------------------------------------|------|------|------|------|------|------|------|--|--|--|

| Symbol                                         | -1   |      |      | -2   | -3   |      | Unit |  |  |  |

|                                                | Min  | Max  | Min  | Max  | Min  | Max  |      |  |  |  |

| t <sub>INSU</sub>                              | 2.23 |      | 2.32 |      | 2.43 |      | ns   |  |  |  |

| t <sub>INH</sub>                               | 0.00 |      | 0.00 |      | 0.00 |      | ns   |  |  |  |

| t <sub>outco</sub>                             | 2.00 | 4.86 | 2.00 | 5.35 | 2.00 | 5.84 | ns   |  |  |  |

| t <sub>INSUPLL</sub>                           | 1.58 |      | 1.66 |      | -    |      | ns   |  |  |  |

| t <sub>INHPLL</sub>                            | 0.00 |      | 0.00 |      | -    |      | ns   |  |  |  |

| t <sub>outcopll</sub>                          | 0.50 | 2.96 | 0.50 | 3.29 | -    | -    | ns   |  |  |  |

| Symbol                     | -    | 1    | -    | 2    | -    | Unit |    |

|----------------------------|------|------|------|------|------|------|----|

| Γ                          | Min  | Max  | Min  | Max  | Min  | Max  |    |

| t <sub>insubidir</sub>     | 2.74 |      | 2.96 |      | 3.19 |      | ns |

| t <sub>inhbidir</sub>      | 0.00 |      | 0.00 |      | 0.00 |      | ns |

| t <sub>оитсовідія</sub>    | 2.00 | 4.86 | 2.00 | 5.35 | 2.00 | 5.84 | ns |

| t <sub>xzbidir</sub>       |      | 5.00 |      | 5.48 |      | 5.89 | ns |

| t <sub>zxbidir</sub>       |      | 5.00 |      | 5.48 |      | 5.89 | ns |

| t <sub>insubidirpll</sub>  | 4.64 |      | 5.03 |      | -    |      | ns |

| t <sub>inhbidirpll</sub>   | 0.00 |      | 0.00 |      | -    |      | ns |

| t <sub>outcobidirpll</sub> | 0.50 | 2.96 | 0.50 | 3.29 | -    | -    | ns |

| t <sub>xzbidirpll</sub>    |      | 3.10 |      | 3.42 |      | -    | ns |

| t <sub>ZXBIDIRPLL</sub>    |      | 3.10 |      | 3.42 |      | -    | ns |

Tables 85 through 90 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K400E APEX 20KE devices.

| Table 85. EP2    | Table 85. EP20K400E f <sub>MAX</sub> LE Timing Microparameters |      |          |         |      |      |    |  |  |  |  |  |

|------------------|----------------------------------------------------------------|------|----------|---------|------|------|----|--|--|--|--|--|

| Symbol           | l -1 Speed Grade -2 Speed Grade                                |      | ed Grade | -3 Spee | Unit |      |    |  |  |  |  |  |

|                  | Min                                                            | Max  | Min      | Max     | Min  | Max  |    |  |  |  |  |  |

| t <sub>SU</sub>  | 0.23                                                           |      | 0.23     |         | 0.23 |      | ns |  |  |  |  |  |

| t <sub>H</sub>   | 0.23                                                           |      | 0.23     |         | 0.23 |      | ns |  |  |  |  |  |

| t <sub>CO</sub>  |                                                                | 0.25 |          | 0.29    |      | 0.32 | ns |  |  |  |  |  |

| t <sub>LUT</sub> |                                                                | 0.70 |          | 0.83    |      | 1.01 | ns |  |  |  |  |  |

| Symbol                  | -1 Spee | d Grade | -2 Spee | ed Grade | -3 Spee | d Grade | Unit |

|-------------------------|---------|---------|---------|----------|---------|---------|------|

|                         | Min     | Max     | Min     | Max      | Min     | Max     |      |

| t <sub>ESBARC</sub>     |         | 1.67    |         | 1.91     |         | 1.99    | ns   |

| t <sub>ESBSRC</sub>     |         | 2.30    |         | 2.66     |         | 2.93    | ns   |

| t <sub>ESBAWC</sub>     |         | 3.09    |         | 3.58     |         | 3.99    | ns   |

| t <sub>ESBSWC</sub>     |         | 3.01    |         | 3.65     |         | 4.05    | ns   |

| t <sub>ESBWASU</sub>    | 0.54    |         | 0.63    |          | 0.65    |         | ns   |

| t <sub>ESBWAH</sub>     | 0.36    |         | 0.43    |          | 0.42    |         | ns   |

| t <sub>ESBWDSU</sub>    | 0.69    |         | 0.77    |          | 0.84    |         | ns   |

| t <sub>ESBWDH</sub>     | 0.36    |         | 0.43    |          | 0.42    |         | ns   |

| t <sub>ESBRASU</sub>    | 1.61    |         | 1.77    |          | 1.86    |         | ns   |

| t <sub>ESBRAH</sub>     | 0.00    |         | 0.00    |          | 0.01    |         | ns   |

| t <sub>ESBWESU</sub>    | 1.35    |         | 1.47    |          | 1.61    |         | ns   |

| t <sub>ESBWEH</sub>     | 0.00    |         | 0.00    |          | 0.00    |         | ns   |

| t <sub>ESBDATASU</sub>  | -0.18   |         | -0.30   |          | -0.27   |         | ns   |

| t <sub>ESBDATAH</sub>   | 0.13    |         | 0.13    |          | 0.13    |         | ns   |

| t <sub>ESBWADDRSU</sub> | -0.02   |         | -0.11   |          | -0.03   |         | ns   |

| t <sub>ESBRADDRSU</sub> | 0.06    |         | -0.01   |          | -0.05   |         | ns   |

| t <sub>ESBDATACO1</sub> |         | 1.16    |         | 1.40     |         | 1.54    | ns   |

| t <sub>ESBDATACO2</sub> |         | 2.18    |         | 2.55     |         | 2.85    | ns   |

| t <sub>ESBDD</sub>      |         | 2.73    |         | 3.17     |         | 3.58    | ns   |

| t <sub>PD</sub>         |         | 1.57    |         | 1.83     |         | 2.07    | ns   |

| t <sub>PTERMSU</sub>    | 0.92    |         | 0.99    |          | 1.18    |         | ns   |

| t <sub>PTERMCO</sub>    |         | 1.18    |         | 1.43     |         | 1.17    | ns   |

| Symbol                  | -1 Speed Grade |      | -2 Spee | ed Grade | -3 Spee | Unit |    |

|-------------------------|----------------|------|---------|----------|---------|------|----|

|                         | Min            | Max  | Min     | Max      | Min     | Max  |    |

| t <sub>ESBARC</sub>     |                | 1.67 |         | 2.39     |         | 3.11 | ns |

| t <sub>ESBSRC</sub>     |                | 2.27 |         | 3.07     |         | 3.86 | ns |

| t <sub>ESBAWC</sub>     |                | 3.19 |         | 4.56     |         | 5.93 | ns |

| t <sub>ESBSWC</sub>     |                | 3.51 |         | 4.62     |         | 5.72 | ns |

| t <sub>ESBWASU</sub>    | 1.46           |      | 2.08    |          | 2.70    |      | ns |

| t <sub>ESBWAH</sub>     | 0.00           |      | 0.00    |          | 0.00    |      | ns |

| t <sub>ESBWDSU</sub>    | 1.60           |      | 2.29    |          | 2.97    |      | ns |

| t <sub>ESBWDH</sub>     | 0.00           |      | 0.00    |          | 0.00    |      | ns |

| t <sub>ESBRASU</sub>    | 1.61           |      | 2.30    |          | 2.99    |      | ns |

| t <sub>ESBRAH</sub>     | 0.00           |      | 0.00    |          | 0.00    |      | ns |

| t <sub>ESBWESU</sub>    | 1.49           |      | 2.30    |          | 3.11    |      | ns |

| t <sub>ESBWEH</sub>     | 0.00           |      | 0.00    |          | 0.00    |      | ns |

| t <sub>ESBDATASU</sub>  | -0.01          |      | 0.35    |          | 0.71    |      | ns |

| t <sub>ESBDATAH</sub>   | 0.13           |      | 0.13    |          | 0.13    |      | ns |

| t <sub>ESBWADDRSU</sub> | 0.19           |      | 0.62    |          | 1.06    |      | ns |

| t <sub>ESBRADDRSU</sub> | 0.25           |      | 0.71    |          | 1.17    |      | ns |

| t <sub>ESBDATACO1</sub> |                | 1.01 |         | 1.19     |         | 1.37 | ns |

| t <sub>ESBDATACO2</sub> |                | 2.18 |         | 3.12     |         | 4.05 | ns |

| t <sub>ESBDD</sub>      |                | 3.19 |         | 4.56     |         | 5.93 | ns |

| t <sub>PD</sub>         |                | 1.57 |         | 2.25     |         | 2.92 | ns |

| t <sub>PTERMSU</sub>    | 0.85           |      | 1.43    |          | 2.01    |      | ns |

| t <sub>PTERMCO</sub>    |                | 1.03 |         | 1.21     |         | 1.39 | ns |

| Table 93. EP2      | Table 93. EP20K600E f <sub>MAX</sub> Routing Delays |          |        |          |         |         |      |  |  |  |  |

|--------------------|-----------------------------------------------------|----------|--------|----------|---------|---------|------|--|--|--|--|

| Symbol             | -1 Spee                                             | ed Grade | -2 Spe | ed Grade | -3 Spee | d Grade | Unit |  |  |  |  |

|                    | Min                                                 | Max      | Min    | Max      | Min     | Мах     |      |  |  |  |  |

| t <sub>F1-4</sub>  |                                                     | 0.22     |        | 0.25     |         | 0.26    | ns   |  |  |  |  |

| t <sub>F5-20</sub> |                                                     | 1.26     |        | 1.39     |         | 1.52    | ns   |  |  |  |  |

| t <sub>F20+</sub>  |                                                     | 3.51     |        | 3.88     |         | 4.26    | ns   |  |  |  |  |

| Table 110. Selectable I/O Standard Output Delays |         |                |     |                |     |                |     |

|--------------------------------------------------|---------|----------------|-----|----------------|-----|----------------|-----|

| Symbol                                           | -1 Spee | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     |

|                                                  | Min     | Max            | Min | Max            | Min | Max            | Min |

| LVCMOS                                           |         | 0.00           |     | 0.00           |     | 0.00           | ns  |

| LVTTL                                            |         | 0.00           |     | 0.00           |     | 0.00           | ns  |

| 2.5 V                                            |         | 0.00           |     | 0.09           |     | 0.10           | ns  |

| 1.8 V                                            |         | 2.49           |     | 2.98           |     | 3.03           | ns  |

| PCI                                              |         | -0.03          |     | 0.17           |     | 0.16           | ns  |

| GTL+                                             |         | 0.75           |     | 0.75           |     | 0.76           | ns  |

| SSTL-3 Class I                                   |         | 1.39           |     | 1.51           |     | 1.50           | ns  |

| SSTL-3 Class II                                  |         | 1.11           |     | 1.23           |     | 1.23           | ns  |

| SSTL-2 Class I                                   |         | 1.35           |     | 1.48           |     | 1.47           | ns  |

| SSTL-2 Class II                                  |         | 1.00           |     | 1.12           |     | 1.12           | ns  |

| LVDS                                             |         | -0.48          |     | -0.48          |     | -0.48          | ns  |

| CTT                                              |         | 0.00           |     | 0.00           |     | 0.00           | ns  |

| AGP                                              |         | 0.00           |     | 0.00           |     | 0.00           | ns  |

## Power Consumption

To estimate device power consumption, use the interactive power calculator on the Altera web site at **http://www.altera.com**.

# Configuration & Operation

The APEX 20K architecture supports several configuration schemes. This section summarizes the device operating modes and available device configuration schemes.

### **Operating Modes**

The APEX architecture uses SRAM configuration elements that require configuration data to be loaded each time the circuit powers up. The process of physically loading the SRAM data into the device is called configuration. During initialization, which occurs immediately after configuration, the device resets registers, enables I/O pins, and begins to operate as a logic device. The I/O pins are tri-stated during power-up, and before and during configuration. Together, the configuration and initialization processes are called *command mode*; normal device operation is called *user mode*.

Before and during device configuration, all I/O pins are pulled to  $\rm V_{\rm CCIO}$  by a built-in weak pull-up resistor.

SRAM configuration elements allow APEX 20K devices to be reconfigured in-circuit by loading new configuration data into the device. Real-time reconfiguration is performed by forcing the device into command mode with a device pin, loading different configuration data, reinitializing the device, and resuming usermode operation. In-field upgrades can be performed by distributing new configuration files.

### **Configuration Schemes**

The configuration data for an APEX 20K device can be loaded with one of five configuration schemes (see Table 111), chosen on the basis of the target application. An EPC2 or EPC16 configuration device, intelligent controller, or the JTAG port can be used to control the configuration of an APEX 20K device. When a configuration device is used, the system can configure automatically at system power-up.

Multiple APEX 20K devices can be configured in any of five configuration schemes by connecting the configuration enable (nCE) and configuration enable output (nCEO) pins on each device.

| Table 111. Data Sources for Configuration |                                                                     |  |  |  |  |  |

|-------------------------------------------|---------------------------------------------------------------------|--|--|--|--|--|

| Configuration Scheme                      | Data Source                                                         |  |  |  |  |  |

| Configuration device                      | EPC1, EPC2, EPC16 configuration devices                             |  |  |  |  |  |

| Passive serial (PS)                       | MasterBlaster or ByteBlasterMV download cable or serial data source |  |  |  |  |  |

| Passive parallel asynchronous (PPA)       | Parallel data source                                                |  |  |  |  |  |

| Passive parallel synchronous (PPS)        | Parallel data source                                                |  |  |  |  |  |

| JTAG                                      | MasterBlaster or ByteBlasterMV download cable or a microprocessor   |  |  |  |  |  |

|                                           | with a Jam or JBC File                                              |  |  |  |  |  |

For more information on configuration, see *Application Note* 116 (*Configuring APEX 20K, FLEX 10K, & FLEX 6000 Devices.*)

## **Device Pin-Outs**

See the Altera web site (http://www.altera.com) or the *Altera Digital Library* for pin-out information

#### Version 4.1

APEX 20K Programmable Logic Device Family Data Sheet version 4.1 contains the following changes:

- *t*<sub>ESBWEH</sub> added to Figure 37 and Tables 35, 50, 56, 62, 68, 74, 86, 92, 97, and 104.

- Updated EP20K300E device internal and external timing numbers in Tables 79 through 84.