# E·XFL

## Intel - EP20K300EQC240-3N Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 1152                                                         |

| Number of Logic Elements/Cells | 11520                                                        |

| Total RAM Bits                 | 147456                                                       |

| Number of I/O                  | 152                                                          |

| Number of Gates                | 728000                                                       |

| Voltage - Supply               | 1.71V ~ 1.89V                                                |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                              |

| Package / Case                 | 240-BFQFP                                                    |

| Supplier Device Package        | 240-PQFP (32x32)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep20k300eqc240-3n |

|                                |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Flexible clock management circuitry with up to four phase-locked loops (PLLs)

- Built-in low-skew clock tree

- Up to eight global clock signals

- ClockLock<sup>®</sup> feature reducing clock delay and skew

- ClockBoost<sup>®</sup> feature providing clock multiplication and division

- ClockShift<sup>TM</sup> programmable clock phase and delay shifting

- Powerful I/O features

- Compliant with peripheral component interconnect Special Interest Group (PCI SIG) *PCI Local Bus Specification, Revision 2.2* for 3.3-V operation at 33 or 66 MHz and 32 or 64 bits

- Support for high-speed external memories, including DDR SDRAM and ZBT SRAM (ZBT is a trademark of Integrated Device Technology, Inc.)

- Bidirectional I/O performance  $(t_{CO} + t_{SU})$  up to 250 MHz

- LVDS performance up to 840 Mbits per channel

- Direct connection from I/O pins to local interconnect providing fast t<sub>CO</sub> and t<sub>SU</sub> times for complex logic

- MultiVolt I/O interface support to interface with 1.8-V, 2.5-V, 3.3-V, and 5.0-V devices (see Table 3)

- Programmable clamp to V<sub>CCIO</sub>

- Individual tri-state output enable control for each pin

- Programmable output slew-rate control to reduce switching noise

- Support for advanced I/O standards, including low-voltage differential signaling (LVDS), LVPECL, PCI-X, AGP, CTT, stubseries terminated logic (SSTL-3 and SSTL-2), Gunning transceiver logic plus (GTL+), and high-speed terminated logic (HSTL Class I)

- Pull-up on I/O pins before and during configuration

- Advanced interconnect structure

- Four-level hierarchical FastTrack<sup>®</sup> Interconnect structure providing fast, predictable interconnect delays

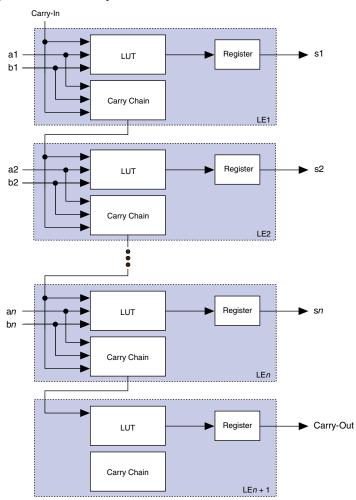

- Dedicated carry chain that implements arithmetic functions such as fast adders, counters, and comparators (automatically used by software tools and megafunctions)

- Dedicated cascade chain that implements high-speed, high-fan-in logic functions (automatically used by software tools and megafunctions)

- Interleaved local interconnect allows one LE to drive 29 other LEs through the fast local interconnect

- Advanced packaging options

- Available in a variety of packages with 144 to 1,020 pins (see Tables 4 through 7)

- FineLine BGA<sup>®</sup> packages maximize board space efficiency

- Advanced software support

- Software design support and automatic place-and-route provided by the Altera<sup>®</sup> Quartus<sup>®</sup> II development system for

Windows-based PCs, Sun SPARCstations, and HP 9000 Series 700/800 workstations

- Altera MegaCore<sup>®</sup> functions and Altera Megafunction Partners Program (AMPP<sup>SM</sup>) megafunctions

- NativeLink<sup>™</sup> integration with popular synthesis, simulation, and timing analysis tools

- Quartus II SignalTap<sup>®</sup> embedded logic analyzer simplifies in-system design evaluation by giving access to internal nodes during device operation

- Supports popular revision-control software packages including PVCS, Revision Control System (RCS), and Source Code Control System (SCCS)

Table 4. APEX 20K QFP, BGA & PGA Package Options & I/O Count

Notes (1), (2)

| Device     | 144-Pin<br>TQFP | 208-Pin<br>PQFP<br>RQFP | 240-Pin<br>PQFP<br>RQFP | 356-Pin BGA | 652-Pin BGA | 655-Pin PGA |

|------------|-----------------|-------------------------|-------------------------|-------------|-------------|-------------|

| EP20K30E   | 92              | 125                     |                         |             |             |             |

| EP20K60E   | 92              | 148                     | 151                     | 196         |             |             |

| EP20K100   | 101             | 159                     | 189                     | 252         |             |             |

| EP20K100E  | 92              | 151                     | 183                     | 246         |             |             |

| EP20K160E  | 88              | 143                     | 175                     | 271         |             |             |

| EP20K200   |                 | 144                     | 174                     | 277         |             |             |

| EP20K200E  |                 | 136                     | 168                     | 271         | 376         |             |

| EP20K300E  |                 |                         | 152                     |             | 408         |             |

| EP20K400   |                 |                         |                         |             | 502         | 502         |

| EP20K400E  |                 |                         |                         |             | 488         |             |

| EP20K600E  |                 |                         |                         |             | 488         |             |

| EP20K1000E |                 |                         |                         |             | 488         |             |

| EP20K1500E |                 |                         |                         |             | 488         |             |

Figure 6. APEX 20K Carry Chain

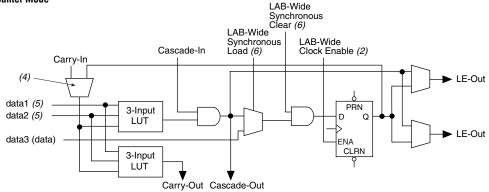

#### LAB-Wide Normal Mode (1) Clock Enable (2) Carry-In (3) Cascade-In LE-Out data1 data2 PRN 4-Input D Q LUT data3 LE-Out ENA data4 CLRN Cascade-Out LAB-Wide Arithmetic Mode Clock Enable (2) Carry-In Cascade-In LE-Out PRN data1 Q D 3-Input data2 LUT LE-Out ENA CLRN 3-Input LUT Cascade-Out Carry-Out

#### Figure 8. APEX 20K LE Operating Modes

#### Notes to Figure 8:

- (1) LEs in normal mode support register packing.

- (2) There are two LAB-wide clock enables per LAB.

- (3) When using the carry-in in normal mode, the packed register feature is unavailable.

- (4) A register feedback multiplexer is available on LE1 of each LAB.

- (5) The DATA1 and DATA2 input signals can supply counter enable, up or down control, or register feedback signals for LEs other than the second LE in an LAB.

- (6) The LAB-wide synchronous clear and LAB wide synchronous load affect all registers in an LAB.

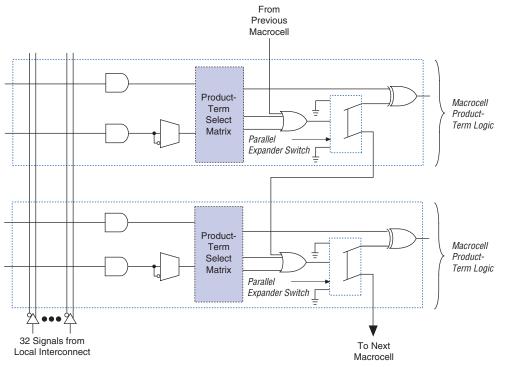

# Embedded System Block

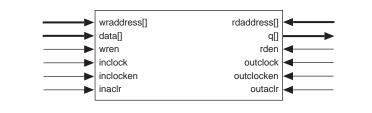

The ESB can implement various types of memory blocks, including dual-port RAM, ROM, FIFO, and CAM blocks. The ESB includes input and output registers; the input registers synchronize writes, and the output registers can pipeline designs to improve system performance. The ESB offers a dual-port mode, which supports simultaneous reads and writes at two different clock frequencies. Figure 17 shows the ESB block diagram.

For more information on APEX 20KE devices and CAM, see *Application* Note 119 (Implementing High-Speed Search Applications with APEX CAM).

## **Driving Signals to the ESB**

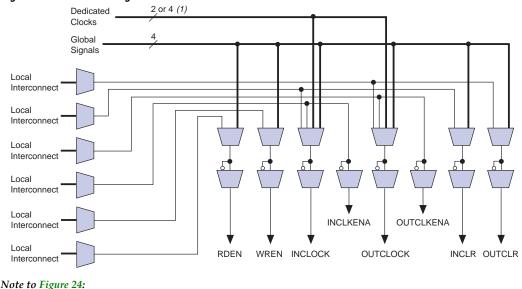

ESBs provide flexible options for driving control signals. Different clocks can be used for the ESB inputs and outputs. Registers can be inserted independently on the data input, data output, read address, write address, WE, and RE signals. The global signals and the local interconnect can drive the WE and RE signals. The global signals, dedicated clock pins, and local interconnect can drive the ESB clock signals. Because the LEs drive the local interconnect, the LEs can control the WE and RE signals and the ESB clock, clock enable, and asynchronous clear signals. Figure 24 shows the ESB control signal generation logic.

(1) APEX 20KE devices have four dedicated clocks.

An ESB is fed by the local interconnect, which is driven by adjacent LEs (for high-speed connection to the ESB) or the MegaLAB interconnect. The ESB can drive the local, MegaLAB, or FastTrack Interconnect routing structure to drive LEs and IOEs in the same MegaLAB structure or anywhere in the device.

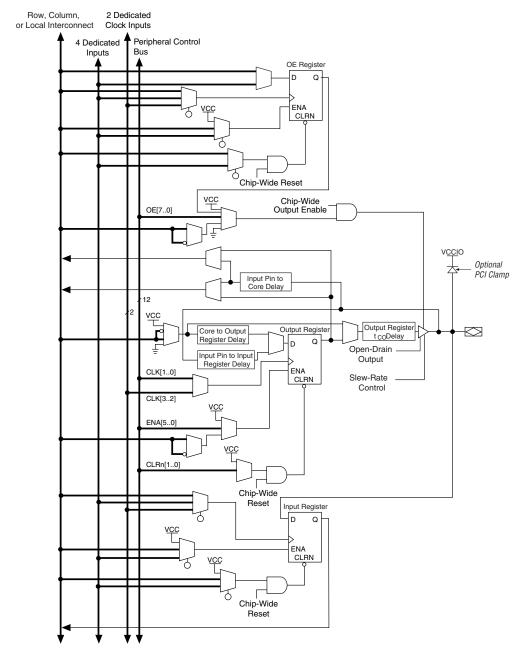

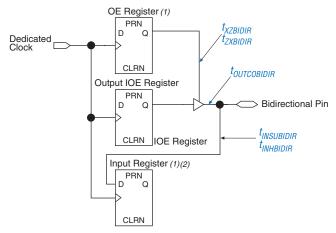

#### Figure 25. APEX 20K Bidirectional I/O Registers Note (1)

#### **Altera Corporation**

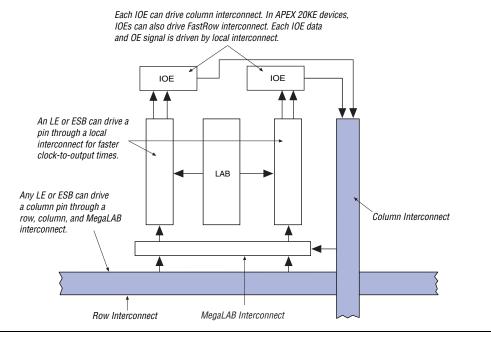

Figure 28 shows how a column IOE connects to the interconnect.

#### Figure 28. Column IOE Connection to the Interconnect

## **Dedicated Fast I/O Pins**

APEX 20KE devices incorporate an enhancement to support bidirectional pins with high internal fanout such as PCI control signals. These pins are called Dedicated Fast I/O pins (FAST1, FAST2, FAST3, and FAST4) and replace dedicated inputs. These pins can be used for fast clock, clear, or high fanout logic signal distribution. They also can drive out. The Dedicated Fast I/O pin data output and tri-state control are driven by local interconnect from the adjacent MegaLAB for high speed. APEX 20KE devices also support the MultiVolt I/O interface feature. The APEX 20KE VCCINT pins must always be connected to a 1.8-V power supply. With a 1.8-V V<sub>CCINT</sub> level, input pins are 1.8-V, 2.5-V, and 3.3-V tolerant. The VCCIO pins can be connected to either a 1.8-V, 2.5-V, or 3.3-V power supply, depending on the I/O standard requirements. When the VCCIO pins are connected to a 1.8-V power supply, the output levels are compatible with 1.8-V systems. When VCCIO pins are connected to a 2.5-V power supply, the output levels are compatible with 2.5-V systems. When VCCIO pins are connected to a 3.3-V power supply, the output levels are sometime with 2.5-V systems. When VCCIO pins are connected to a 3.3-V power supply, the output high is 3.3 V and compatible with 3.3-V or 5.0-V systems. An APEX 20KE device is 5.0-V tolerant with the addition of a resistor.

#### Table 13 summarizes APEX 20KE MultiVolt I/O support.

| Table 13. /           | APEX 20KE I  | MultiVolt I/O | Support /    | Vote (1)       |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |     |

|-----------------------|--------------|---------------|--------------|----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----|

| V <sub>CCIO</sub> (V) |              | Input Siç     | Output S     | ut Signals (V) |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |     |

|                       | 1.8          | 2.5           | 3.3          | 5.0            | 1.8          | 2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.3          | 5.0 |

| 1.8                   | <b>&gt;</b>  | $\checkmark$  | <b>&gt;</b>  |                | $\checkmark$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |     |

| 2.5                   | $\checkmark$ | $\checkmark$  | $\checkmark$ |                |              | <ul> <li>Image: A start of the start of</li></ul> |              |     |

| 3.3                   | ~            | $\checkmark$  | >            | (2)            |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>√</b> (3) |     |

#### Notes to Table 13:

The PCI clamping diode must be disabled to drive an input with voltages higher than V<sub>CCIO</sub>, except for the 5.0-V input case.

(2) An APEX 20KE device can be made 5.0-V tolerant with the addition of an external resistor. You also need a PCI clamp and series resistor.

(3) When V<sub>CCIO</sub> = 3.3 V, an APEX 20KE device can drive a 2.5-V device with 3.3-V tolerant inputs.

# ClockLock & ClockBoost Features

APEX 20K devices support the ClockLock and ClockBoost clock management features, which are implemented with PLLs. The ClockLock circuitry uses a synchronizing PLL that reduces the clock delay and skew within a device. This reduction minimizes clock-to-output and setup times while maintaining zero hold times. The ClockBoost circuitry, which provides a clock multiplier, allows the designer to enhance device area efficiency by sharing resources within the device. The ClockBoost circuitry allows the designer to distribute a low-speed clock and multiply that clock on-device. APEX 20K devices include a high-speed clock tree; unlike ASICs, the user does not have to design and optimize the clock tree. The ClockLock and ClockBoost features work in conjunction with the APEX 20K device's high-speed clock to provide significant improvements in system performance and band-width. Devices with an X-suffix on the ordering code include the ClockLock circuit.

The ClockLock and ClockBoost features in APEX 20K devices are enabled through the Quartus II software. External devices are not required to use these features.

#### Clock Phase & Delay Adjustment

The APEX 20KE ClockShift feature allows the clock phase and delay to be adjusted. The clock phase can be adjusted by 90° steps. The clock delay can be adjusted to increase or decrease the clock delay by an arbitrary amount, up to one clock period.

#### LVDS Support

Two PLLs are designed to support the LVDS interface. When using LVDS, the I/O clock runs at a slower rate than the data transfer rate. Thus, PLLs are used to multiply the I/O clock internally to capture the LVDS data. For example, an I/O clock may run at 105 MHz to support 840 megabits per second (Mbps) LVDS data transfer. In this example, the PLL multiplies the incoming clock by eight to support the high-speed data transfer. You can use PLLs in EP20K400E and larger devices for high-speed LVDS interfacing.

#### Lock Signals

The APEX 20KE ClockLock circuitry supports individual LOCK signals. The LOCK signal drives high when the ClockLock circuit has locked onto the input clock. The LOCK signals are optional for each ClockLock circuit; when not used, they are I/O pins.

## ClockLock & ClockBoost Timing Parameters

For the ClockLock and ClockBoost circuitry to function properly, the incoming clock must meet certain requirements. If these specifications are not met, the circuitry may not lock onto the incoming clock, which generates an erroneous clock within the device. The clock generated by the ClockLock and ClockBoost circuitry must also meet certain specifications. If the incoming clock meets these requirements during configuration, the APEX 20K ClockLock and ClockBoost circuitry will lock onto the clock during configuration. The circuit will be ready for use immediately after configuration. In APEX 20KE devices, the clock input standard is programmable, so the PLL cannot respond to the clock until the device is configured. The PLL locks onto the input clock as soon as configuration is complete. Figure 30 shows the incoming and generated clock specifications.

For more information on ClockLock and ClockBoost circuitry, see Application Note 115: Using the ClockLock and ClockBoost PLL Features in APEX Devices.

| Table 18. I     | Table 18. APEX 20KE Clock Input & Output Parameters       (Part 2 of 2)       Note (1) |                    |         |          |                 |     |       |  |

|-----------------|----------------------------------------------------------------------------------------|--------------------|---------|----------|-----------------|-----|-------|--|

| Symbol          | Parameter                                                                              | I/O Standard       | -1X Spe | ed Grade | -2X Speed Grade |     | Units |  |

|                 |                                                                                        |                    | Min     | Max      | Min             | Max |       |  |

| f <sub>IN</sub> | Input clock frequency                                                                  | 3.3-V LVTTL        | 1.5     | 290      | 1.5             | 257 | MHz   |  |

|                 |                                                                                        | 2.5-V LVTTL        | 1.5     | 281      | 1.5             | 250 | MHz   |  |

|                 |                                                                                        | 1.8-V LVTTL        | 1.5     | 272      | 1.5             | 243 | MHz   |  |

|                 |                                                                                        | GTL+               | 1.5     | 303      | 1.5             | 261 | MHz   |  |

|                 |                                                                                        | SSTL-2 Class<br>I  | 1.5     | 291      | 1.5             | 253 | MHz   |  |

|                 |                                                                                        | SSTL-2 Class<br>II | 1.5     | 291      | 1.5             | 253 | MHz   |  |

|                 |                                                                                        | SSTL-3 Class<br>I  | 1.5     | 300      | 1.5             | 260 | MHz   |  |

|                 |                                                                                        | SSTL-3 Class<br>II | 1.5     | 300      | 1.5             | 260 | MHz   |  |

|                 |                                                                                        | LVDS               | 1.5     | 420      | 1.5             | 350 | MHz   |  |

#### Notes to Tables 17 and 18:

All input clock specifications must be met. The PLL may not lock onto an incoming clock if the clock specifications are not met, creating an erroneous clock within the device.

- (2) The maximum lock time is 40 µs or 2000 input clock cycles, whichever occurs first.

- (3) Before configuration, the PLL circuits are disable and powered down. During configuration, the PLLs are still disabled. The PLLs begin to lock once the device is in the user mode. If the clock enable feature is used, lock begins once the CLKLK\_ENA pin goes high in user mode.

- (4) The PLL VCO operating range is 200 MHz ð f<sub>VCO</sub> ð 840 MHz for LVDS mode.

# SignalTap Embedded Logic Analyzer

APEX 20K devices include device enhancements to support the SignalTap embedded logic analyzer. By including this circuitry, the APEX 20K device provides the ability to monitor design operation over a period of time through the IEEE Std. 1149.1 (JTAG) circuitry; a designer can analyze internal logic at speed without bringing internal signals to the I/O pins. This feature is particularly important for advanced packages such as FineLine BGA packages because adding a connection to a pin during the debugging process can be difficult after a board is designed and manufactured.

| Table 2            | 8. APEX 20KE Device Recommende                      | ed Operating Conditions |                  |                   |      |

|--------------------|-----------------------------------------------------|-------------------------|------------------|-------------------|------|

| Symbol             | Parameter                                           | Conditions              | Min              | Max               | Unit |

| V <sub>CCINT</sub> | Supply voltage for internal logic and input buffers | (3), (4)                | 1.71 (1.71)      | 1.89 (1.89)       | V    |

| V <sub>CCIO</sub>  | Supply voltage for output buffers, 3.3-V operation  | (3), (4)                | 3.00 (3.00)      | 3.60 (3.60)       | V    |

|                    | Supply voltage for output buffers, 2.5-V operation  | (3), (4)                | 2.375<br>(2.375) | 2.625<br>(2.625)  | V    |

|                    | Supply voltage for output buffers, 1.8-V operation  | (3), (4)                | 1.71 (1.71)      | 1.89 (1.89)       | V    |

| VI                 | Input voltage                                       | (5), (6)                | -0.5             | 4.0               | V    |

| Vo                 | Output voltage                                      |                         | 0                | V <sub>CCIO</sub> | V    |

| ТJ                 | Junction temperature                                | For commercial use      | 0                | 85                | °C   |

|                    |                                                     | For industrial use      | -40              | 100               | °C   |

| t <sub>R</sub>     | Input rise time                                     |                         |                  | 40                | ns   |

| t <sub>F</sub>     | Input fall time                                     |                         |                  | 40                | ns   |

#### Figure 40. Synchronous Bidirectional Pin External Timing

#### Notes to Figure 40:

- (1) The output enable and input registers are LE registers in the LAB adjacent to a bidirectional row pin. The output enable register is set with "Output Enable Routing= Signal-Pin" option in the Quartus II software.

- (2) The LAB adjacent input register is set with "Decrease Input Delay to Internal Cells= Off". This maintains a zero hold time for lab adjacent registers while giving a fast, position independent setup time. A faster setup time with zero hold time is possible by setting "Decrease Input Delay to Internal Cells= ON" and moving the input register farther away from the bidirectional pin. The exact position where zero hold occurs with the minimum setup time, varies with device density and speed grade.

Table 31 describes the  $f_{MAX}$  timing parameters shown in Figure 36 on page 68.

| Table 31. APEX 2        | OK f <sub>MAX</sub> Timing Parameters (Part 1 of 2)            |  |  |  |  |  |  |

|-------------------------|----------------------------------------------------------------|--|--|--|--|--|--|

| Symbol                  | Parameter                                                      |  |  |  |  |  |  |

| t <sub>SU</sub>         | LE register setup time before clock                            |  |  |  |  |  |  |

| t <sub>H</sub>          | LE register hold time after clock                              |  |  |  |  |  |  |

| t <sub>CO</sub>         | LE register clock-to-output delay                              |  |  |  |  |  |  |

| t <sub>LUT</sub>        | LUT delay for data-in                                          |  |  |  |  |  |  |

| t <sub>ESBRC</sub>      | ESB Asynchronous read cycle time                               |  |  |  |  |  |  |

| t <sub>ESBWC</sub>      | ESB Asynchronous write cycle time                              |  |  |  |  |  |  |

| t <sub>ESBWESU</sub>    | ESB WE setup time before clock when using input register       |  |  |  |  |  |  |

| t <sub>ESBDATASU</sub>  | ESB data setup time before clock when using input register     |  |  |  |  |  |  |

| t <sub>ESBDATAH</sub>   | ESB data hold time after clock when using input register       |  |  |  |  |  |  |

| t <sub>ESBADDRSU</sub>  | ESB address setup time before clock when using input registers |  |  |  |  |  |  |

| t <sub>ESBDATACO1</sub> | ESB clock-to-output delay when using output registers          |  |  |  |  |  |  |

| Symbol                  | -1 Spee | d Grade | -2 Spee | d Grade | -3 Spee | Units |    |

|-------------------------|---------|---------|---------|---------|---------|-------|----|

|                         | Min     | Мах     | Min     | Max     | Min     | Max   |    |

| t <sub>SU</sub>         | 0.5     |         | 0.6     |         | 0.8     |       | ns |

| t <sub>H</sub>          | 0.7     |         | 0.8     |         | 1.0     |       | ns |

| t <sub>co</sub>         |         | 0.3     |         | 0.4     |         | 0.5   | ns |

| t <sub>lut</sub>        |         | 0.8     |         | 1.0     |         | 1.3   | ns |

| t <sub>ESBRC</sub>      |         | 1.7     |         | 2.1     |         | 2.4   | ns |

| t <sub>ESBWC</sub>      |         | 5.7     |         | 6.9     |         | 8.1   | ns |

| t <sub>ESBWESU</sub>    | 3.3     |         | 3.9     |         | 4.6     |       | ns |

| t <sub>ESBDATASU</sub>  | 2.2     |         | 2.7     |         | 3.1     |       | ns |

| t <sub>ESBDATAH</sub>   | 0.6     |         | 0.8     |         | 0.9     |       | ns |

| t <sub>ESBADDRSU</sub>  | 2.4     |         | 2.9     |         | 3.3     |       | ns |

| t <sub>ESBDATACO1</sub> |         | 1.3     |         | 1.6     |         | 1.8   | ns |

| t <sub>ESBDATACO2</sub> |         | 2.6     |         | 3.1     |         | 3.6   | ns |

| t <sub>ESBDD</sub>      |         | 2.5     |         | 3.3     |         | 3.6   | ns |

| t <sub>PD</sub>         |         | 2.5     |         | 3.0     |         | 3.6   | ns |

| t <sub>PTERMSU</sub>    | 2.3     |         | 2.7     |         | 3.2     |       | ns |

| t <sub>PTERMCO</sub>    |         | 1.5     |         | 1.8     |         | 2.1   | ns |

| t <sub>F1-4</sub>       |         | 0.5     |         | 0.6     |         | 0.7   | ns |

| t <sub>F5-20</sub>      |         | 1.6     |         | 1.7     |         | 1.8   | ns |

| t <sub>F20+</sub>       |         | 2.2     |         | 2.2     |         | 2.3   | ns |

| t <sub>CH</sub>         | 2.0     |         | 2.5     |         | 3.0     |       | ns |

| t <sub>CL</sub>         | 2.0     |         | 2.5     |         | 3.0     |       | ns |

| t <sub>CLRP</sub>       | 0.3     |         | 0.4     |         | 0.4     |       | ns |

| t <sub>PREP</sub>       | 0.4     |         | 0.5     |         | 0.5     |       | ns |

| t <sub>ESBCH</sub>      | 2.0     |         | 2.5     |         | 3.0     |       | ns |

| t <sub>ESBCL</sub>      | 2.0     |         | 2.5     |         | 3.0     |       | ns |

| t <sub>ESBWP</sub>      | 1.6     |         | 1.9     |         | 2.2     |       | ns |

| t <sub>ESBRP</sub>      | 1.0     |         | 1.3     |         | 1.4     |       | ns |

| Symbol                    | -1   |      | -    | 2    | -    | 3    | Unit |  |  |

|---------------------------|------|------|------|------|------|------|------|--|--|

| -                         | Min  | Max  | Min  | Max  | Min  | Max  |      |  |  |

| t <sub>insubidir</sub>    | 2.77 |      | 2.91 |      | 3.11 |      | ns   |  |  |

| t <sub>inhbidir</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |  |  |

| toutcobidir               | 2.00 | 4.84 | 2.00 | 5.31 | 2.00 | 5.81 | ns   |  |  |

| t <sub>XZBIDIR</sub>      |      | 6.47 |      | 7.44 |      | 8.65 | ns   |  |  |

| t <sub>ZXBIDIR</sub>      |      | 6.47 |      | 7.44 |      | 8.65 | ns   |  |  |

| t <sub>insubidirpll</sub> | 3.44 |      | 3.24 |      | -    |      | ns   |  |  |

| t <sub>inhbidirpll</sub>  | 0.00 |      | 0.00 |      | -    |      | ns   |  |  |

| toutcobidirpll            | 0.50 | 3.37 | 0.50 | 3.69 | -    | -    | ns   |  |  |

| t <sub>xzbidirpll</sub>   |      | 5.00 |      | 5.82 |      | -    | ns   |  |  |

| t <sub>zxbidirpll</sub>   |      | 5.00 |      | 5.82 |      | -    | ns   |  |  |

Tables 61 through 66 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K100E APEX 20KE devices.

| Table 61. EP20K100E f <sub>MAX</sub> LE Timing Microparameters |      |      |      |      |      |      |    |  |  |  |

|----------------------------------------------------------------|------|------|------|------|------|------|----|--|--|--|

| Symbol                                                         | -    | 1    | -    | 2    | -;   | Unit |    |  |  |  |

|                                                                | Min  | Max  | Min  | Max  | Min  | Max  | 1  |  |  |  |

| t <sub>SU</sub>                                                | 0.25 |      | 0.25 |      | 0.25 |      | ns |  |  |  |

| t <sub>H</sub>                                                 | 0.25 |      | 0.25 |      | 0.25 |      | ns |  |  |  |

| t <sub>CO</sub>                                                |      | 0.28 |      | 0.28 |      | 0.34 | ns |  |  |  |

| t <sub>LUT</sub>                                               |      | 0.80 |      | 0.95 |      | 1.13 | ns |  |  |  |

| Symbol             | -'   | 1   | -    | -2  |      | -3  |    |

|--------------------|------|-----|------|-----|------|-----|----|

|                    | Min  | Max | Min  | Max | Min  | Max |    |

| t <sub>CH</sub>    | 2.00 |     | 2.00 |     | 2.00 |     | ns |

| t <sub>CL</sub>    | 2.00 |     | 2.00 |     | 2.00 |     | ns |

| t <sub>CLRP</sub>  | 0.20 |     | 0.20 |     | 0.20 |     | ns |

| t <sub>PREP</sub>  | 0.20 |     | 0.20 |     | 0.20 |     | ns |

| t <sub>ESBCH</sub> | 2.00 |     | 2.00 |     | 2.00 |     | ns |

| t <sub>ESBCL</sub> | 2.00 |     | 2.00 |     | 2.00 |     | ns |

| t <sub>ESBWP</sub> | 1.29 |     | 1.53 |     | 1.66 |     | ns |

| t <sub>ESBRP</sub> | 1.11 |     | 1.29 |     | 1.41 |     | ns |

| Table 65. EP20K100E External Timing Parameters |      |      |      |      |      |      |      |  |  |  |

|------------------------------------------------|------|------|------|------|------|------|------|--|--|--|

| Symbol                                         | -1   |      |      | -2   | -3   |      | Unit |  |  |  |

|                                                | Min  | Max  | Min  | Max  | Min  | Max  |      |  |  |  |

| t <sub>INSU</sub>                              | 2.23 |      | 2.32 |      | 2.43 |      | ns   |  |  |  |

| t <sub>INH</sub>                               | 0.00 |      | 0.00 |      | 0.00 |      | ns   |  |  |  |

| t <sub>outco</sub>                             | 2.00 | 4.86 | 2.00 | 5.35 | 2.00 | 5.84 | ns   |  |  |  |

| t <sub>INSUPLL</sub>                           | 1.58 |      | 1.66 |      | -    |      | ns   |  |  |  |

| t <sub>INHPLL</sub>                            | 0.00 |      | 0.00 |      | -    |      | ns   |  |  |  |

| t <sub>outcopll</sub>                          | 0.50 | 2.96 | 0.50 | 3.29 | -    | -    | ns   |  |  |  |

| Symbol                     | -1   |      | -    | 2    | -    | 3    | Unit |  |  |

|----------------------------|------|------|------|------|------|------|------|--|--|

|                            | Min  | Max  | Min  | Max  | Min  | Max  |      |  |  |

| t <sub>insubidir</sub>     | 2.74 |      | 2.96 |      | 3.19 |      | ns   |  |  |

| t <sub>inhbidir</sub>      | 0.00 |      | 0.00 |      | 0.00 |      | ns   |  |  |

| t <sub>оитсовідія</sub>    | 2.00 | 4.86 | 2.00 | 5.35 | 2.00 | 5.84 | ns   |  |  |

| t <sub>xzbidir</sub>       |      | 5.00 |      | 5.48 |      | 5.89 | ns   |  |  |

| t <sub>zxbidir</sub>       |      | 5.00 |      | 5.48 |      | 5.89 | ns   |  |  |

| t <sub>insubidirpll</sub>  | 4.64 |      | 5.03 |      | -    |      | ns   |  |  |

| t <sub>inhbidirpll</sub>   | 0.00 |      | 0.00 |      | -    |      | ns   |  |  |

| t <sub>outcobidirpll</sub> | 0.50 | 2.96 | 0.50 | 3.29 | -    | -    | ns   |  |  |

| t <sub>xzbidirpll</sub>    |      | 3.10 |      | 3.42 |      | -    | ns   |  |  |

| t <sub>ZXBIDIRPLL</sub>    |      | 3.10 |      | 3.42 |      | -    | ns   |  |  |

| Symbol                  | -1 Spee | d Grade | -2 Spee | ed Grade | -3 Spee | d Grade | Unit |

|-------------------------|---------|---------|---------|----------|---------|---------|------|

|                         | Min     | Max     | Min     | Max      | Min     | Max     | 1    |

| t <sub>ESBARC</sub>     |         | 1.67    |         | 1.91     |         | 1.99    | ns   |

| t <sub>ESBSRC</sub>     |         | 2.30    |         | 2.66     |         | 2.93    | ns   |

| t <sub>ESBAWC</sub>     |         | 3.09    |         | 3.58     |         | 3.99    | ns   |

| t <sub>ESBSWC</sub>     |         | 3.01    |         | 3.65     |         | 4.05    | ns   |

| t <sub>ESBWASU</sub>    | 0.54    |         | 0.63    |          | 0.65    |         | ns   |

| t <sub>ESBWAH</sub>     | 0.36    |         | 0.43    |          | 0.42    |         | ns   |

| t <sub>ESBWDSU</sub>    | 0.69    |         | 0.77    |          | 0.84    |         | ns   |

| t <sub>ESBWDH</sub>     | 0.36    |         | 0.43    |          | 0.42    |         | ns   |

| t <sub>ESBRASU</sub>    | 1.61    |         | 1.77    |          | 1.86    |         | ns   |

| t <sub>ESBRAH</sub>     | 0.00    |         | 0.00    |          | 0.01    |         | ns   |

| t <sub>ESBWESU</sub>    | 1.35    |         | 1.47    |          | 1.61    |         | ns   |

| t <sub>ESBWEH</sub>     | 0.00    |         | 0.00    |          | 0.00    |         | ns   |

| t <sub>ESBDATASU</sub>  | -0.18   |         | -0.30   |          | -0.27   |         | ns   |

| t <sub>ESBDATAH</sub>   | 0.13    |         | 0.13    |          | 0.13    |         | ns   |

| t <sub>ESBWADDRSU</sub> | -0.02   |         | -0.11   |          | -0.03   |         | ns   |

| t <sub>ESBRADDRSU</sub> | 0.06    |         | -0.01   |          | -0.05   |         | ns   |

| t <sub>ESBDATACO1</sub> |         | 1.16    |         | 1.40     |         | 1.54    | ns   |

| t <sub>ESBDATACO2</sub> |         | 2.18    |         | 2.55     |         | 2.85    | ns   |

| t <sub>ESBDD</sub>      |         | 2.73    |         | 3.17     |         | 3.58    | ns   |

| t <sub>PD</sub>         |         | 1.57    |         | 1.83     |         | 2.07    | ns   |

| t <sub>PTERMSU</sub>    | 0.92    |         | 0.99    |          | 1.18    |         | ns   |

| t <sub>PTERMCO</sub>    |         | 1.18    |         | 1.43     |         | 1.17    | ns   |

#### APEX 20K Programmable Logic Device Family Data Sheet

| Table 87. EP20K400E f <sub>MAX</sub> Routing Delays |         |         |        |          |         |      |    |  |  |  |

|-----------------------------------------------------|---------|---------|--------|----------|---------|------|----|--|--|--|

| Symbol                                              | -1 Spee | d Grade | -2 Spe | ed Grade | -3 Spee | Unit |    |  |  |  |

|                                                     | Min     | Max     | Min    | Max      | Min     | Мах  |    |  |  |  |

| t <sub>F1-4</sub>                                   |         | 0.25    |        | 0.25     |         | 0.26 | ns |  |  |  |

| t <sub>F5-20</sub>                                  |         | 1.01    |        | 1.12     |         | 1.25 | ns |  |  |  |

| t <sub>F20+</sub>                                   |         | 3.71    |        | 3.92     |         | 4.17 | ns |  |  |  |

| Symbol             | -1 Spee | d Grade | -2 Spee | d Grade | -3 Spee | Unit |    |

|--------------------|---------|---------|---------|---------|---------|------|----|

|                    | Min     | Max     | Min     | Max     | Min     | Max  |    |

| t <sub>CH</sub>    | 1.36    |         | 2.22    |         | 2.35    |      | ns |

| t <sub>CL</sub>    | 1.36    |         | 2.26    |         | 2.35    |      | ns |

| t <sub>CLRP</sub>  | 0.18    |         | 0.18    |         | 0.19    |      | ns |

| t <sub>PREP</sub>  | 0.18    |         | 0.18    |         | 0.19    |      | ns |

| t <sub>ESBCH</sub> | 1.36    |         | 2.26    |         | 2.35    |      | ns |

| t <sub>ESBCL</sub> | 1.36    |         | 2.26    |         | 2.35    |      | ns |

| t <sub>ESBWP</sub> | 1.17    |         | 1.38    |         | 1.56    |      | ns |

| t <sub>ESBRP</sub> | 0.94    |         | 1.09    |         | 1.25    |      | ns |

| Table 89. EP20K400E External Timing Parameters |                |      |         |          |          |         |      |  |  |

|------------------------------------------------|----------------|------|---------|----------|----------|---------|------|--|--|

| Symbol                                         | -1 Speed Grade |      | -2 Spec | ed Grade | -3 Speed | l Grade | Unit |  |  |

|                                                | Min            | Max  | Min     | Max      | Min      | Max     |      |  |  |

| t <sub>INSU</sub>                              | 2.51           |      | 2.64    |          | 2.77     |         | ns   |  |  |

| t <sub>INH</sub>                               | 0.00           |      | 0.00    |          | 0.00     |         | ns   |  |  |

| t <sub>outco</sub>                             | 2.00           | 5.25 | 2.00    | 5.79     | 2.00     | 6.32    | ns   |  |  |

| tINSUPLL                                       | 3.221          |      | 3.38    |          | -        |         | ns   |  |  |

| t <sub>INHPLL</sub>                            | 0.00           |      | 0.00    |          | -        |         | ns   |  |  |

| t <sub>outcopll</sub>                          | 0.50           | 2.25 | 0.50    | 2.45     | -        | -       | ns   |  |  |

Г

| Symbol             | -1 Speed Grade |     | -2 Spee | d Grade | -3 Spee | d Grade | Unit |  |

|--------------------|----------------|-----|---------|---------|---------|---------|------|--|

|                    | Min            | Max | Min     | Max     | Min     | Max     |      |  |

| t <sub>CH</sub>    | 2.00           |     | 2.50    |         | 2.75    |         | ns   |  |

| t <sub>CL</sub>    | 2.00           |     | 2.50    |         | 2.75    |         | ns   |  |

| t <sub>CLRP</sub>  | 0.18           |     | 0.26    |         | 0.34    |         | ns   |  |

| t <sub>PREP</sub>  | 0.18           |     | 0.26    |         | 0.34    |         | ns   |  |

| t <sub>ESBCH</sub> | 2.00           |     | 2.50    |         | 2.75    |         | ns   |  |

| t <sub>ESBCL</sub> | 2.00           |     | 2.50    |         | 2.75    |         | ns   |  |

| t <sub>ESBWP</sub> | 1.17           |     | 1.68    |         | 2.18    |         | ns   |  |

| t <sub>ESBRP</sub> | 0.95           |     | 1.35    |         | 1.76    |         | ns   |  |

| Symbol              | -1 Spee | d Grade | -2 Spee | d Grade | -3 Speed Grade |      | Unit |

|---------------------|---------|---------|---------|---------|----------------|------|------|

|                     | Min     | Max     | Min     | Max     | Min            | Max  |      |

| t <sub>INSU</sub>   | 2.74    |         | 2.74    |         | 2.87           |      | ns   |

| t <sub>INH</sub>    | 0.00    |         | 0.00    |         | 0.00           |      | ns   |

| toutco              | 2.00    | 5.51    | 2.00    | 6.06    | 2.00           | 6.61 | ns   |

| tINSUPLL            | 1.86    |         | 1.96    |         | -              |      | ns   |

| t <sub>INHPLL</sub> | 0.00    |         | 0.00    |         | -              |      | ns   |

| toutcopll           | 0.50    | 2.62    | 0.50    | 2.91    | -              | -    | ns   |

| Symbol                    | -1 Speed Grade |      | -2 Spee | d Grade | -3 Spee | d Grade | Unit |

|---------------------------|----------------|------|---------|---------|---------|---------|------|

|                           | Min            | Max  | Min     | Max     | Min     | Max     |      |

| t <sub>insubidir</sub>    | 0.64           |      | 0.98    |         | 1.08    |         | ns   |

| t <sub>inhbidir</sub>     | 0.00           |      | 0.00    |         | 0.00    |         | ns   |

| t <sub>outcobidir</sub>   | 2.00           | 5.51 | 2.00    | 6.06    | 2.00    | 6.61    | ns   |

| t <sub>xzbidir</sub>      |                | 6.10 |         | 6.74    |         | 7.10    | ns   |

| t <sub>zxbidir</sub>      |                | 6.10 |         | 6.74    |         | 7.10    | ns   |

| t <sub>insubidirpll</sub> | 2.26           |      | 2.68    |         | -       |         | ns   |

| t <sub>inhbidirpll</sub>  | 0.00           |      | 0.00    |         | -       |         | ns   |

| toutcobidirpll            | 0.50           | 2.62 | 0.50    | 2.91    | -       | -       | ns   |

| t <sub>xzbidirpll</sub>   |                | 3.21 |         | 3.59    |         | -       | ns   |

| t <sub>ZXBIDIRPLL</sub>   |                | 3.21 |         | 3.59    |         | -       | ns   |

#### APEX 20K Programmable Logic Device Family Data Sheet

| Table 99. EP2      | Table 99. EP20K1000E f <sub>MAX</sub> Routing Delays |         |        |          |                |      |      |  |  |  |  |

|--------------------|------------------------------------------------------|---------|--------|----------|----------------|------|------|--|--|--|--|

| Symbol             | -1 Spee                                              | d Grade | -2 Spe | ed Grade | -3 Speed Grade |      | Unit |  |  |  |  |

|                    | Min                                                  | Max     | Min    | Max      | Min            | Max  |      |  |  |  |  |

| t <sub>F1-4</sub>  |                                                      | 0.27    |        | 0.27     |                | 0.27 | ns   |  |  |  |  |

| t <sub>F5-20</sub> |                                                      | 1.45    |        | 1.63     |                | 1.75 | ns   |  |  |  |  |

| t <sub>F20+</sub>  |                                                      | 4.15    |        | 4.33     |                | 4.97 | ns   |  |  |  |  |

| Symbol             | -1 Spee | d Grade | -2 Spee | d Grade | -3 Speed Grade |     | Unit |

|--------------------|---------|---------|---------|---------|----------------|-----|------|

|                    | Min     | Max     | Min     | Max     | Min            | Max |      |

| t <sub>CH</sub>    | 1.25    |         | 1.43    |         | 1.67           |     | ns   |

| t <sub>CL</sub>    | 1.25    |         | 1.43    |         | 1.67           |     | ns   |

| t <sub>CLRP</sub>  | 0.20    |         | 0.20    |         | 0.20           |     | ns   |

| t <sub>PREP</sub>  | 0.20    |         | 0.20    |         | 0.20           |     | ns   |

| t <sub>ESBCH</sub> | 1.25    |         | 1.43    |         | 1.67           |     | ns   |

| t <sub>ESBCL</sub> | 1.25    |         | 1.43    |         | 1.67           |     | ns   |

| t <sub>ESBWP</sub> | 1.28    |         | 1.51    |         | 1.65           |     | ns   |

| t <sub>ESBRP</sub> | 1.11    |         | 1.29    |         | 1.41           |     | ns   |

| Table 101. EP20K1000E External Timing Parameters |                |      |         |          |          |                  |    |  |  |

|--------------------------------------------------|----------------|------|---------|----------|----------|------------------|----|--|--|

| Symbol                                           | -1 Speed Grade |      | -2 Spee | ed Grade | -3 Speed | -3 Speed Grade L |    |  |  |

|                                                  | Min            | Max  | Min     | Max      | Min      | Max              |    |  |  |

| t <sub>INSU</sub>                                | 2.70           |      | 2.84    |          | 2.97     |                  | ns |  |  |

| t <sub>INH</sub>                                 | 0.00           |      | 0.00    |          | 0.00     |                  | ns |  |  |

| t <sub>outco</sub>                               | 2.00           | 5.75 | 2.00    | 6.33     | 2.00     | 6.90             | ns |  |  |

| t <sub>INSUPLL</sub>                             | 1.64           |      | 2.09    |          | -        |                  | ns |  |  |

| t <sub>INHPLL</sub>                              | 0.00           |      | 0.00    |          | -        |                  | ns |  |  |

| t <sub>outcopll</sub>                            | 0.50           | 2.25 | 0.50    | 2.99     | -        | -                | ns |  |  |