# E·XFL

## Intel - EP20K30ETC144-2X Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

## Details

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 120                                                         |

| Number of Logic Elements/Cells | 1200                                                        |

| Total RAM Bits                 | 24576                                                       |

| Number of I/O                  | 92                                                          |

| Number of Gates                | 113000                                                      |

| Voltage - Supply               | 1.71V ~ 1.89V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 144-LQFP                                                    |

| Supplier Device Package        | 144-TQFP (20x20)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep20k30etc144-2x |

|                                |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

All APEX 20K devices are reconfigurable and are 100% tested prior to shipment. As a result, test vectors do not have to be generated for fault coverage purposes. Instead, the designer can focus on simulation and design verification. In addition, the designer does not need to manage inventories of different application-specific integrated circuit (ASIC) designs; APEX 20K devices can be configured on the board for the specific functionality required.

APEX 20K devices are configured at system power-up with data stored in an Altera serial configuration device or provided by a system controller. Altera offers in-system programmability (ISP)-capable EPC1, EPC2, and EPC16 configuration devices, which configure APEX 20K devices via a serial data stream. Moreover, APEX 20K devices contain an optimized interface that permits microprocessors to configure APEX 20K devices serially or in parallel, and synchronously or asynchronously. The interface also enables microprocessors to treat APEX 20K devices as memory and configure the device by writing to a virtual memory location, making reconfiguration easy.

After an APEX 20K device has been configured, it can be reconfigured in-circuit by resetting the device and loading new data. Real-time changes can be made during system operation, enabling innovative reconfigurable computing applications.

APEX 20K devices are supported by the Altera Quartus II development system, a single, integrated package that offers HDL and schematic design entry, compilation and logic synthesis, full simulation and worst-case timing analysis, SignalTap logic analysis, and device configuration. The Quartus II software runs on Windows-based PCs, Sun SPARCstations, and HP 9000 Series 700/800 workstations.

The Quartus II software provides NativeLink interfaces to other industrystandard PC- and UNIX workstation-based EDA tools. For example, designers can invoke the Quartus II software from within third-party design tools. Further, the Quartus II software contains built-in optimized synthesis libraries; synthesis tools can use these libraries to optimize designs for APEX 20K devices. For example, the Synopsys Design Compiler library, supplied with the Quartus II development system, includes DesignWare functions optimized for the APEX 20K architecture. Each LE has two outputs that drive the local, MegaLAB, or FastTrack Interconnect routing structure. Each output can be driven independently by the LUT's or register's output. For example, the LUT can drive one output while the register drives the other output. This feature, called register packing, improves device utilization because the register and the LUT can be used for unrelated functions. The LE can also drive out registered and unregistered versions of the LUT output.

The APEX 20K architecture provides two types of dedicated high-speed data paths that connect adjacent LEs without using local interconnect paths: carry chains and cascade chains. A carry chain supports high-speed arithmetic functions such as counters and adders, while a cascade chain implements wide-input functions such as equality comparators with minimum delay. Carry and cascade chains connect LEs 1 through 10 in an LAB and all LABs in the same MegaLAB structure.

## Carry Chain

The carry chain provides a very fast carry-forward function between LEs. The carry-in signal from a lower-order bit drives forward into the higherorder bit via the carry chain, and feeds into both the LUT and the next portion of the carry chain. This feature allows the APEX 20K architecture to implement high-speed counters, adders, and comparators of arbitrary width. Carry chain logic can be created automatically by the Quartus II software Compiler during design processing, or manually by the designer during design entry. Parameterized functions such as library of parameterized modules (LPM) and DesignWare functions automatically take advantage of carry chains for the appropriate functions.

The Quartus II software Compiler creates carry chains longer than ten LEs by linking LABs together automatically. For enhanced fitting, a long carry chain skips alternate LABs in a MegaLAB<sup>™</sup> structure. A carry chain longer than one LAB skips either from an even-numbered LAB to the next even-numbered LAB, or from an odd-numbered LAB to the next odd-numbered LAB. For example, the last LE of the first LAB in the upper-left MegaLAB structure carries to the first LE of the third LAB in the MegaLAB structure.

Figure 6 shows how an *n*-bit full adder can be implemented in n + 1 LEs with the carry chain. One portion of the LUT generates the sum of two bits using the input signals and the carry-in signal; the sum is routed to the output of the LE. The register can be bypassed for simple adders or used for accumulator functions. Another portion of the LUT and the carry chain logic generates the carry-out signal, which is routed directly to the carry-in signal of the next-higher-order bit. The final carry-out signal is routed to an LE, where it is driven onto the local, MegaLAB, or FastTrack Interconnect routing structures.

The counter mode uses two three-input LUTs: one generates the counter data, and the other generates the fast carry bit. A 2-to-1 multiplexer provides synchronous loading, and another AND gate provides synchronous clearing. If the cascade function is used by an LE in counter mode, the synchronous clear or load overrides any signal carried on the cascade chain. The synchronous clear overrides the synchronous load. LEs in arithmetic mode can drive out registered and unregistered versions of the LUT output.

## Clear & Preset Logic Control

Logic for the register's clear and preset signals is controlled by LAB-wide signals. The LE directly supports an asynchronous clear function. The Quartus II software Compiler can use a NOT-gate push-back technique to emulate an asynchronous preset. Moreover, the Quartus II software Compiler can use a programmable NOT-gate push-back technique to emulate simultaneous preset and clear or asynchronous load. However, this technique uses three additional LEs per register. All emulation is performed automatically when the design is compiled. Registers that emulate simultaneous preset and load will enter an unknown state upon power-up or when the chip-wide reset is asserted.

In addition to the two clear and preset modes, APEX 20K devices provide a chip-wide reset pin (DEV\_CLRn) that resets all registers in the device. Use of this pin is controlled through an option in the Quartus II software that is set before compilation. The chip-wide reset overrides all other control signals. Registers using an asynchronous preset are preset when the chip-wide reset is asserted; this effect results from the inversion technique used to implement the asynchronous preset.

## FastTrack Interconnect

In the APEX 20K architecture, connections between LEs, ESBs, and I/O pins are provided by the FastTrack Interconnect. The FastTrack Interconnect is a series of continuous horizontal and vertical routing channels that traverse the device. This global routing structure provides predictable performance, even in complex designs. In contrast, the segmented routing in FPGAs requires switch matrices to connect a variable number of routing paths, increasing the delays between logic resources and reducing performance.

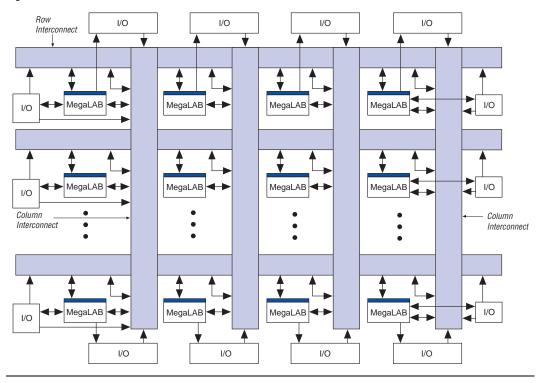

The FastTrack Interconnect consists of row and column interconnect channels that span the entire device. The row interconnect routes signals throughout a row of MegaLAB structures; the column interconnect routes signals throughout a column of MegaLAB structures. When using the row and column interconnect, an LE, IOE, or ESB can drive any other LE, IOE, or ESB in a device. See Figure 9.

A row line can be driven directly by LEs, IOEs, or ESBs in that row. Further, a column line can drive a row line, allowing an LE, IOE, or ESB to drive elements in a different row via the column and row interconnect. The row interconnect drives the MegaLAB interconnect to drive LEs, IOEs, or ESBs in a particular MegaLAB structure.

A column line can be directly driven by LEs, IOEs, or ESBs in that column. A column line on a device's left or right edge can also be driven by row IOEs. The column line is used to route signals from one row to another. A column line can drive a row line; it can also drive the MegaLAB interconnect directly, allowing faster connections between rows.

Figure 10 shows how the FastTrack Interconnect uses the local interconnect to drive LEs within MegaLAB structures.

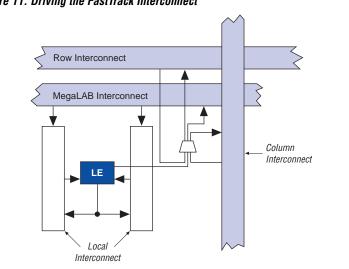

Figure 11 shows the intersection of a row and column interconnect, and how these forms of interconnects and LEs drive each other.

Figure 11. Driving the FastTrack Interconnect

APEX 20KE devices include an enhanced interconnect structure for faster routing of input signals with high fan-out. Column I/O pins can drive the FastRow<sup>™</sup> interconnect, which routes signals directly into the local interconnect without having to drive through the MegaLAB interconnect. FastRow lines traverse two MegaLAB structures. Also, these pins can drive the local interconnect directly for fast setup times. On EP20K300E and larger devices, the FastRow interconnect drives the two MegaLABs in the top left corner, the two MegaLABs in the top right corner, the two MegaLABS in the bottom left corner, and the two MegaLABs in the bottom right corner. On EP20K200E and smaller devices, FastRow interconnect drives the two MegaLABs on the top and the two MegaLABs on the bottom of the device. On all devices, the FastRow interconnect drives all local interconnect in the appropriate MegaLABs except the local interconnect on the side of the MegaLAB opposite the ESB. Pins using the FastRow interconnect achieve a faster set-up time, as the signal does not need to use a MegaLAB interconnect line to reach the destination LE. Figure 12 shows the FastRow interconnect.

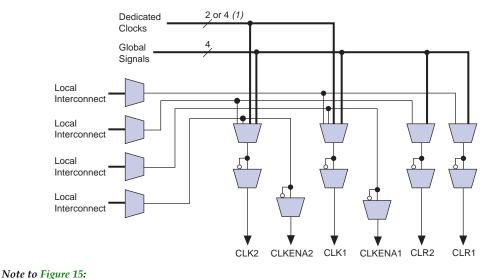

The programmable register also supports an asynchronous clear function. Within the ESB, two asynchronous clears are generated from global signals and the local interconnect. Each macrocell can either choose between the two asynchronous clear signals or choose to not be cleared. Either of the two clear signals can be inverted within the ESB. Figure 15 shows the ESB control logic when implementing product-terms.

Figure 15. ESB Product-Term Mode Control Logic

(1) APEX 20KE devices have four dedicated clocks.

## Parallel Expanders

Parallel expanders are unused product terms that can be allocated to a neighboring macrocell to implement fast, complex logic functions. Parallel expanders allow up to 32 product terms to feed the macrocell OR logic directly, with two product terms provided by the macrocell and 30 parallel expanders provided by the neighboring macrocells in the ESB.

The Quartus II software Compiler can allocate up to 15 sets of up to two parallel expanders per set to the macrocells automatically. Each set of two parallel expanders incurs a small, incremental timing delay. Figure 16 shows the APEX 20K parallel expanders.

For more information on APEX 20KE devices and CAM, see *Application* Note 119 (Implementing High-Speed Search Applications with APEX CAM).

## **Driving Signals to the ESB**

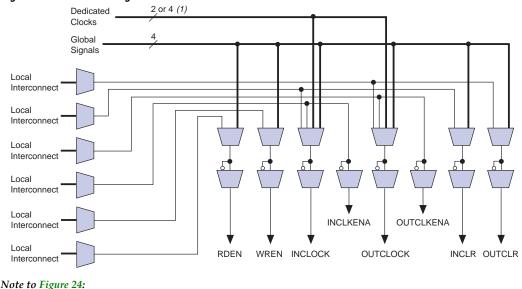

ESBs provide flexible options for driving control signals. Different clocks can be used for the ESB inputs and outputs. Registers can be inserted independently on the data input, data output, read address, write address, WE, and RE signals. The global signals and the local interconnect can drive the WE and RE signals. The global signals, dedicated clock pins, and local interconnect can drive the ESB clock signals. Because the LEs drive the local interconnect, the LEs can control the WE and RE signals and the ESB clock, clock enable, and asynchronous clear signals. Figure 24 shows the ESB control signal generation logic.

(1) APEX 20KE devices have four dedicated clocks.

An ESB is fed by the local interconnect, which is driven by adjacent LEs (for high-speed connection to the ESB) or the MegaLAB interconnect. The ESB can drive the local, MegaLAB, or FastTrack Interconnect routing structure to drive LEs and IOEs in the same MegaLAB structure or anywhere in the device.

Table 10 describes the APEX 20K programmable delays and their logic options in the Quartus II software.

| Table 10. APEX 20K Programmable Delay Chains |                                         |  |  |  |  |  |  |

|----------------------------------------------|-----------------------------------------|--|--|--|--|--|--|

| Programmable Delays Quartus II Logic Option  |                                         |  |  |  |  |  |  |

| Input pin to core delay                      | Decrease input delay to internal cells  |  |  |  |  |  |  |

| Input pin to input register delay            | Decrease input delay to input register  |  |  |  |  |  |  |

| Core to output register delay                | Decrease input delay to output register |  |  |  |  |  |  |

| Output register $t_{CO}$ delay               | Increase delay to output pin            |  |  |  |  |  |  |

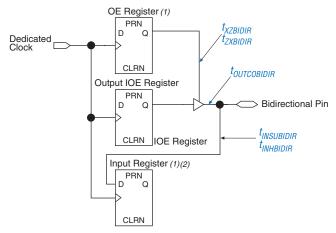

#### The Quartus II software compiler can program these delays automatically to minimize setup time while providing a zero hold time. Figure 25 shows how fast bidirectional I/Os are implemented in APEX 20K devices.

The register in the APEX 20K IOE can be programmed to power-up high or low after configuration is complete. If it is programmed to power-up low, an asynchronous clear can control the register. If it is programmed to power-up high, the register cannot be asynchronously cleared or preset. This feature is useful for cases where the APEX 20K device controls an active-low input or another device; it prevents inadvertent activation of the input upon power-up.

## IEEE Std. 1149.1 (JTAG) Boundary-Scan Support

All APEX 20K devices provide JTAG BST circuitry that complies with the IEEE Std. 1149.1-1990 specification. JTAG boundary-scan testing can be performed before or after configuration, but not during configuration. APEX 20K devices can also use the JTAG port for configuration with the Quartus II software or with hardware using either Jam Files (.jam) or Jam Byte-Code Files (.jbc). Finally, APEX 20K devices use the JTAG port to monitor the logic operation of the device with the SignalTap embedded logic analyzer. APEX 20K devices support the JTAG instructions shown in Table 19. Although EP20K1500E devices support the JTAG BYPASS and SignalTap instructions, they do not support boundary-scan testing or the use of the JTAG port for configuration.

| Table 19. APEX 20K J       | FAG Instructions                                                                                                                                                                                                                     |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTAG Instruction           | Description                                                                                                                                                                                                                          |

| SAMPLE/PRELOAD             | Allows a snapshot of signals at the device pins to be captured and examined during normal device operation, and permits an initial data pattern to be output at the device pins. Also used by the SignalTap embedded logic analyzer. |

| EXTEST                     | Allows the external circuitry and board-level interconnections to be tested by forcing a test pattern at the output pins and capturing test results at the input pins.                                                               |

| BYPASS (1)                 | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation.                                          |

| USERCODE                   | Selects the 32-bit USERCODE register and places it between the TDI and TDO pins, allowing the USERCODE to be serially shifted out of TDO.                                                                                            |

| IDCODE                     | Selects the IDCODE register and places it between TDI and TDO, allowing the IDCODE to be serially shifted out of TDO.                                                                                                                |

| ICR Instructions           | Used when configuring an APEX 20K device via the JTAG port with a MasterBlaster <sup>™</sup> or ByteBlasterMV <sup>™</sup> download cable, or when using a Jam File or Jam Byte-Code File via an embedded processor.                 |

| SignalTap Instructions (1) | Monitors internal device operation with the SignalTap embedded logic analyzer.                                                                                                                                                       |

## able 19 APFX 20K .ITAG Instruction

#### Note to Table 19:

(1) The EP20K1500E device supports the JTAG BYPASS instruction and the SignalTap instructions.

| Symbol            | Parameter                                                                 | Conditions                                                                            | Min | Тур | Мах                  | Unit |

|-------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----|-----|----------------------|------|

| V <sub>OL</sub>   | 3.3-V low-level TTL output voltage                                        | I <sub>OL</sub> = 12 mA DC,<br>V <sub>CCIO</sub> = 3.00 V (11)                        |     |     | 0.45                 | V    |

|                   | 3.3-V low-level CMOS output voltage                                       | I <sub>OL</sub> = 0.1 mA DC,<br>V <sub>CCIO</sub> = 3.00 V (11)                       |     |     | 0.2                  | V    |

|                   | 3.3-V low-level PCI output voltage                                        | $I_{OL} = 1.5 \text{ mA DC},$<br>$V_{CCIO} = 3.00 \text{ to } 3.60 \text{ V}$<br>(11) |     |     | $0.1 	imes V_{CCIO}$ | V    |

|                   | 2.5-V low-level output voltage                                            | I <sub>OL</sub> = 0.1 mA DC,<br>V <sub>CCIO</sub> = 2.30 V (11)                       |     |     | 0.2                  | V    |

|                   | I <sub>OL</sub> = 1 mA DC,<br>V <sub>CCIO</sub> = 2.30 V (11)             |                                                                                       |     | 0.4 | V                    |      |

|                   |                                                                           | I <sub>OL</sub> = 2 mA DC,<br>V <sub>CCIO</sub> = 2.30 V (11)                         |     |     | 0.7                  | V    |

| I <sub>I</sub>    | Input pin leakage current                                                 | $V_1 = 5.75$ to $-0.5$ V                                                              | -10 |     | 10                   | μA   |

| I <sub>OZ</sub>   | Tri-stated I/O pin leakage current                                        | V <sub>O</sub> = 5.75 to -0.5 V                                                       | -10 |     | 10                   | μΑ   |

| I <sub>CC0</sub>  | V <sub>CC</sub> supply current (standby)<br>(All ESBs in power-down mode) | $V_1$ = ground, no load, no<br>toggling inputs, -1 speed<br>grade (12)                |     | 10  |                      | mA   |

|                   |                                                                           | V <sub>I</sub> = ground, no load, no<br>toggling inputs,<br>-2, -3 speed grades (12)  |     | 5   |                      | mA   |

| R <sub>CONF</sub> | Value of I/O pin pull-up resistor                                         | V <sub>CCIO</sub> = 3.0 V (13)                                                        | 20  |     | 50                   | W    |

|                   | before and during configuration                                           | V <sub>CCIO</sub> = 2.375 V (13)                                                      | 30  |     | 80                   | W    |

| Symbol            | Parameter                                                                 | Conditions                                                                           | Min                                  | Тур | Max                                  | Unit |

|-------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------|-----|--------------------------------------|------|

| V <sub>IH</sub>   | High-level LVTTL, CMOS, or 3.3-V<br>PCI input voltage                     |                                                                                      | 1.7, 0.5 × V <sub>CCIO</sub><br>(10) |     | 4.1                                  | V    |

| V <sub>IL</sub>   | Low-level LVTTL, CMOS, or 3.3-V<br>PCI input voltage                      |                                                                                      | -0.5                                 |     | 0.8, 0.3 × V <sub>CCIO</sub><br>(10) | V    |

| V <sub>OH</sub>   | 3.3-V high-level LVTTL output voltage                                     | I <sub>OH</sub> = -12 mA DC,<br>V <sub>CCIO</sub> = 3.00 V <i>(11)</i>               | 2.4                                  |     |                                      | ۷    |

|                   | 3.3-V high-level LVCMOS output voltage                                    | I <sub>OH</sub> = -0.1 mA DC,<br>V <sub>CCIO</sub> = 3.00 V <i>(11)</i>              | V <sub>CCIO</sub> – 0.2              |     |                                      | V    |

|                   | 3.3-V high-level PCI output voltage                                       | I <sub>OH</sub> = -0.5 mA DC,<br>V <sub>CCIO</sub> = 3.00 to 3.60 V<br>( <i>11</i> ) | $0.9 	imes V_{CCIO}$                 |     |                                      | V    |

|                   | 2.5-V high-level output voltage                                           | I <sub>OH</sub> = -0.1 mA DC,<br>V <sub>CCIO</sub> = 2.30 V (11)                     | 2.1                                  |     |                                      | V    |

|                   |                                                                           | I <sub>OH</sub> = -1 mA DC,<br>V <sub>CCIO</sub> = 2.30 V <i>(11)</i>                | 2.0                                  |     |                                      | ۷    |

|                   |                                                                           | I <sub>OH</sub> = -2 mA DC,<br>V <sub>CCIO</sub> = 2.30 V <i>(11)</i>                | 1.7                                  |     |                                      | v    |

| V <sub>OL</sub>   | 3.3-V low-level LVTTL output<br>voltage                                   | I <sub>OL</sub> = 12 mA DC,<br>V <sub>CCIO</sub> = 3.00 V <i>(12)</i>                |                                      |     | 0.4                                  | V    |

|                   | 3.3-V low-level LVCMOS output voltage                                     | I <sub>OL</sub> = 0.1 mA DC,<br>V <sub>CCIO</sub> = 3.00 V ( <i>12</i> )             |                                      |     | 0.2                                  | V    |

|                   | 3.3-V low-level PCI output voltage                                        | I <sub>OL</sub> = 1.5 mA DC,<br>V <sub>CCIO</sub> = 3.00 to 3.60 V<br>( <i>12</i> )  |                                      |     | $0.1 \times V_{CCIO}$                | V    |

|                   | 2.5-V low-level output voltage                                            | I <sub>OL</sub> = 0.1 mA DC,<br>V <sub>CCIO</sub> = 2.30 V <i>(12)</i>               |                                      |     | 0.2                                  | V    |

|                   |                                                                           | I <sub>OL</sub> = 1 mA DC,<br>V <sub>CCIO</sub> = 2.30 V <i>(12)</i>                 |                                      |     | 0.4                                  | V    |

|                   |                                                                           | I <sub>OL</sub> = 2 mA DC,<br>V <sub>CCIO</sub> = 2.30 V <i>(12)</i>                 |                                      |     | 0.7                                  | V    |

| l <sub>l</sub>    | Input pin leakage current                                                 | V <sub>I</sub> = 4.1 to -0.5 V (13)                                                  | -10                                  |     | 10                                   | μA   |

| I <sub>OZ</sub>   | Tri-stated I/O pin leakage current                                        | V <sub>O</sub> = 4.1 to -0.5 V (13)                                                  | -10                                  |     | 10                                   | μΑ   |

| I <sub>CC0</sub>  | V <sub>CC</sub> supply current (standby)<br>(All ESBs in power-down mode) | V <sub>I</sub> = ground, no load, no<br>toggling inputs, -1 speed<br>grade           |                                      | 10  |                                      | mA   |

|                   |                                                                           | V <sub>1</sub> = ground, no load, no<br>toggling inputs,<br>-2, -3 speed grades      |                                      | 5   |                                      | mA   |

| R <sub>CONF</sub> | Value of I/O pin pull-up resistor                                         | V <sub>CCIO</sub> = 3.0 V (14)                                                       | 20                                   |     | 50                                   | kΩ   |

|                   | before and during configuration                                           | V <sub>CCIO</sub> = 2.375 V (14)                                                     | 30                                   |     | 80                                   | kΩ   |

|                   |                                                                           | V <sub>CCIO</sub> = 1.71 V (14)                                                      | 60                                   |     | 150                                  | kΩ   |

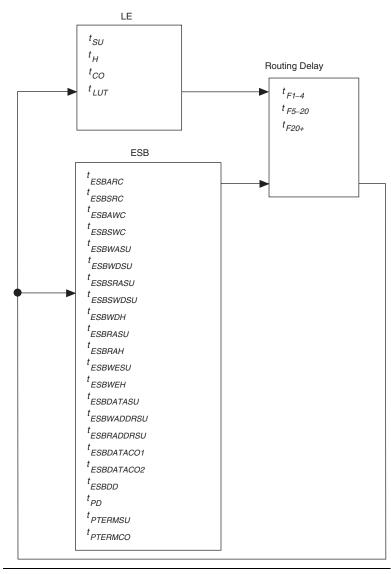

Figure 37. APEX 20KE f<sub>MAX</sub> Timing Model

#### Figure 40. Synchronous Bidirectional Pin External Timing

#### Notes to Figure 40:

- (1) The output enable and input registers are LE registers in the LAB adjacent to a bidirectional row pin. The output enable register is set with "Output Enable Routing= Signal-Pin" option in the Quartus II software.

- (2) The LAB adjacent input register is set with "Decrease Input Delay to Internal Cells= Off". This maintains a zero hold time for lab adjacent registers while giving a fast, position independent setup time. A faster setup time with zero hold time is possible by setting "Decrease Input Delay to Internal Cells= ON" and moving the input register farther away from the bidirectional pin. The exact position where zero hold occurs with the minimum setup time, varies with device density and speed grade.

Table 31 describes the  $f_{MAX}$  timing parameters shown in Figure 36 on page 68.

| Table 31. APEX 20K f <sub>MAX</sub> Timing Parameters       (Part 1 of 2) |                                                                |  |  |  |  |  |  |

|---------------------------------------------------------------------------|----------------------------------------------------------------|--|--|--|--|--|--|

| Symbol                                                                    | Parameter                                                      |  |  |  |  |  |  |

| t <sub>SU</sub>                                                           | LE register setup time before clock                            |  |  |  |  |  |  |

| t <sub>H</sub>                                                            | LE register hold time after clock                              |  |  |  |  |  |  |

| t <sub>CO</sub>                                                           | LE register clock-to-output delay                              |  |  |  |  |  |  |

| t <sub>LUT</sub>                                                          | LUT delay for data-in                                          |  |  |  |  |  |  |

| t <sub>ESBRC</sub>                                                        | ESB Asynchronous read cycle time                               |  |  |  |  |  |  |

| t <sub>ESBWC</sub>                                                        | ESB Asynchronous write cycle time                              |  |  |  |  |  |  |

| t <sub>ESBWESU</sub>                                                      | ESB WE setup time before clock when using input register       |  |  |  |  |  |  |

| t <sub>ESBDATASU</sub>                                                    | ESB data setup time before clock when using input register     |  |  |  |  |  |  |

| t <sub>ESBDATAH</sub>                                                     | ESB data hold time after clock when using input register       |  |  |  |  |  |  |

| t <sub>ESBADDRSU</sub>                                                    | ESB address setup time before clock when using input registers |  |  |  |  |  |  |

| t <sub>ESBDATACO1</sub>                                                   | ESB clock-to-output delay when using output registers          |  |  |  |  |  |  |

| Symbol                        | -1 Spee | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |    |

|-------------------------------|---------|----------------|-----|----------------|-----|----------------|----|

|                               | Min     | Max            | Min | Мах            | Min | Мах            | 1  |

| t <sub>INSU</sub> (1)         | 2.3     |                | 2.8 |                | 3.2 |                | ns |

| t <sub>INH</sub> (1)          | 0.0     |                | 0.0 |                | 0.0 |                | ns |

| t <sub>OUTCO</sub> (1)        | 2.0     | 4.5            | 2.0 | 4.9            | 2.0 | 6.6            | ns |

| t <sub>INSU</sub> (2)         | 1.1     |                | 1.2 |                | -   |                | ns |

| t <sub>INH</sub> (2)          | 0.0     |                | 0.0 |                | -   |                | ns |

| t <sub>оитсо</sub> <i>(2)</i> | 0.5     | 2.7            | 0.5 | 3.1            | _   | 4.8            | ns |

| Table 44. EP20K100 External Bidirectional Timing Parameters |                |     |                |     |                |     |      |  |

|-------------------------------------------------------------|----------------|-----|----------------|-----|----------------|-----|------|--|

| Symbol                                                      | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |  |

|                                                             | Min            | Max | Min            | Max | Min            | Max | 1    |  |

| t <sub>INSUBIDIR</sub> (1)                                  | 2.3            |     | 2.8            |     | 3.2            |     | ns   |  |

| t <sub>INHBIDIR</sub> (1)                                   | 0.0            |     | 0.0            |     | 0.0            |     | ns   |  |

| toutcobidir<br>(1)                                          | 2.0            | 4.5 | 2.0            | 4.9 | 2.0            | 6.6 | ns   |  |

| t <sub>XZBIDIR</sub> (1)                                    |                | 5.0 |                | 5.9 |                | 6.9 | ns   |  |

| t <sub>ZXBIDIR</sub> (1)                                    |                | 5.0 |                | 5.9 |                | 6.9 | ns   |  |

| t <sub>insubidir</sub> (2)                                  | 1.0            |     | 1.2            |     | -              |     | ns   |  |

| t <sub>INHBIDIR</sub> (2)                                   | 0.0            |     | 0.0            |     | -              |     | ns   |  |

| toutcobidir<br>(2)                                          | 0.5            | 2.7 | 0.5            | 3.1 | -              | -   | ns   |  |

| t <sub>XZBIDIR</sub> (2)                                    |                | 4.3 |                | 5.0 |                | -   | ns   |  |

| t <sub>ZXBIDIR</sub> (2)                                    |                | 4.3 |                | 5.0 |                | -   | ns   |  |

| Table 45. EP20K200 External Timing Parameters |                |     |        |                |     |                |    |  |  |

|-----------------------------------------------|----------------|-----|--------|----------------|-----|----------------|----|--|--|

| Symbol                                        | -1 Speed Grade |     | -2 Spe | -2 Speed Grade |     | -3 Speed Grade |    |  |  |

|                                               | Min            | Max | Min    | Мах            | Min | Max            |    |  |  |

| t <sub>INSU</sub> (1)                         | 1.9            |     | 2.3    |                | 2.6 |                | ns |  |  |

| t <sub>INH</sub> (1)                          | 0.0            |     | 0.0    |                | 0.0 |                | ns |  |  |

| t <sub>OUTCO</sub> (1)                        | 2.0            | 4.6 | 2.0    | 5.6            | 2.0 | 6.8            | ns |  |  |

| t <sub>INSU</sub> (2)                         | 1.1            |     | 1.2    |                | -   |                | ns |  |  |

| t <sub>INH</sub> (2)                          | 0.0            |     | 0.0    |                | -   |                | ns |  |  |

| t <sub>оитсо</sub> <i>(2)</i>                 | 0.5            | 2.7 | 0.5    | 3.1            | -   | -              | ns |  |  |

Tables 67 through 72 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K160E APEX 20KE devices.

| Table 67. EP20K160E f <sub>MAX</sub> LE Timing Microparameters |      |      |      |      |      |      |    |  |  |

|----------------------------------------------------------------|------|------|------|------|------|------|----|--|--|

| Symbol                                                         | -    | -1   |      | -2   |      | -3   |    |  |  |

|                                                                | Min  | Max  | Min  | Max  | Min  | Max  |    |  |  |

| t <sub>SU</sub>                                                | 0.22 |      | 0.24 |      | 0.26 |      | ns |  |  |

| t <sub>H</sub>                                                 | 0.22 |      | 0.24 |      | 0.26 |      | ns |  |  |

| t <sub>CO</sub>                                                |      | 0.25 |      | 0.31 |      | 0.35 | ns |  |  |

| t <sub>LUT</sub>                                               |      | 0.69 |      | 0.88 |      | 1.12 | ns |  |  |

| Symbol                  | -     | 1    | -     | -2   |      | -3   |    |

|-------------------------|-------|------|-------|------|------|------|----|

|                         | Min   | Max  | Min   | Max  | Min  | Max  |    |

| t <sub>ESBARC</sub>     |       | 1.65 |       | 2.02 |      | 2.11 | ns |

| t <sub>ESBSRC</sub>     |       | 2.21 |       | 2.70 |      | 3.11 | ns |

| t <sub>ESBAWC</sub>     |       | 3.04 |       | 3.79 |      | 4.42 | ns |

| t <sub>ESBSWC</sub>     |       | 2.81 |       | 3.56 |      | 4.10 | ns |

| t <sub>ESBWASU</sub>    | 0.54  |      | 0.66  |      | 0.73 |      | ns |

| t <sub>ESBWAH</sub>     | 0.36  |      | 0.45  |      | 0.47 |      | ns |

| t <sub>ESBWDSU</sub>    | 0.68  |      | 0.81  |      | 0.94 |      | ns |

| t <sub>ESBWDH</sub>     | 0.36  |      | 0.45  |      | 0.47 |      | ns |

| t <sub>ESBRASU</sub>    | 1.58  |      | 1.87  |      | 2.06 |      | ns |

| t <sub>ESBRAH</sub>     | 0.00  |      | 0.00  |      | 0.01 |      | ns |

| t <sub>ESBWESU</sub>    | 1.41  |      | 1.71  |      | 2.00 |      | ns |

| t <sub>ESBWEH</sub>     | 0.00  |      | 0.00  |      | 0.00 |      | ns |

| t <sub>ESBDATASU</sub>  | -0.02 |      | -0.03 |      | 0.09 |      | ns |

| t <sub>ESBDATAH</sub>   | 0.13  |      | 0.13  |      | 0.13 |      | ns |

| t <sub>ESBWADDRSU</sub> | 0.14  |      | 0.17  |      | 0.35 |      | ns |

| t <sub>ESBRADDRSU</sub> | 0.21  |      | 0.27  |      | 0.43 |      | ns |

| t <sub>ESBDATACO1</sub> |       | 1.04 |       | 1.30 |      | 1.46 | ns |

| t <sub>ESBDATACO2</sub> |       | 2.15 |       | 2.70 |      | 3.16 | ns |

| t <sub>ESBDD</sub>      |       | 2.69 |       | 3.35 |      | 3.97 | ns |

| t <sub>PD</sub>         |       | 1.55 |       | 1.93 |      | 2.29 | ns |

| t <sub>PTERMSU</sub>    | 1.01  |      | 1.23  |      | 1.52 |      | ns |

| t <sub>PTERMCO</sub>    |       | 1.06 |       | 1.32 |      | 1.04 | ns |

| Symbol             | -1   |     | -    | -2  |      | -3  |    |

|--------------------|------|-----|------|-----|------|-----|----|

|                    | Min  | Max | Min  | Max | Min  | Max |    |

| t <sub>CH</sub>    | 1.25 |     | 1.43 |     | 1.67 |     | ns |

| t <sub>CL</sub>    | 1.25 |     | 1.43 |     | 1.67 |     | ns |

| t <sub>CLRP</sub>  | 0.19 |     | 0.26 |     | 0.35 |     | ns |

| t <sub>PREP</sub>  | 0.19 |     | 0.26 |     | 0.35 |     | ns |

| t <sub>ESBCH</sub> | 1.25 |     | 1.43 |     | 1.67 |     | ns |

| t <sub>ESBCL</sub> | 1.25 |     | 1.43 |     | 1.67 |     | ns |

| t <sub>ESBWP</sub> | 1.25 |     | 1.71 |     | 2.28 |     | ns |

| t <sub>ESBRP</sub> | 1.01 |     | 1.38 |     | 1.84 |     | ns |

| Symbol               |      | -1   |      | 2    | -3   |      | Unit |

|----------------------|------|------|------|------|------|------|------|

|                      | Min  | Max  | Min  | Max  | Min  | Max  |      |

| t <sub>INSU</sub>    | 2.31 |      | 2.44 |      | 2.57 |      | ns   |

| t <sub>INH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| tоитсо               | 2.00 | 5.29 | 2.00 | 5.82 | 2.00 | 6.24 | ns   |

| t <sub>insupll</sub> | 1.76 |      | 1.85 |      | -    |      | ns   |

| t <sub>INHPLL</sub>  | 0.00 |      | 0.00 |      | -    |      | ns   |

| toutcopll            | 0.50 | 2.65 | 0.50 | 2.95 | -    | -    | ns   |

| Symbol                    | -1   |      | -:   | 2    | -    | Unit |    |

|---------------------------|------|------|------|------|------|------|----|

|                           | Min  | Max  | Min  | Max  | Min  | Max  | 1  |

| t <sub>insubidir</sub>    | 2.77 |      | 2.85 |      | 3.11 |      | ns |

| t <sub>inhbidir</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns |

| toutcobidir               | 2.00 | 5.29 | 2.00 | 5.82 | 2.00 | 6.24 | ns |

| t <sub>XZBIDIR</sub>      |      | 7.59 |      | 8.30 |      | 9.09 | ns |

| t <sub>zxbidir</sub>      |      | 7.59 |      | 8.30 |      | 9.09 | ns |

| t <sub>insubidirpll</sub> | 2.50 |      | 2.76 |      | -    |      | ns |

| t <sub>inhbidirpll</sub>  | 0.00 |      | 0.00 |      | -    |      | ns |

| toutcobidirpll            | 0.50 | 2.65 | 0.50 | 2.95 | -    | -    | ns |

| t <sub>XZBIDIRPLL</sub>   |      | 5.00 |      | 5.43 |      | -    | ns |

| t <sub>ZXBIDIRPLL</sub>   |      | 5.00 |      | 5.43 |      | -    | ns |

| Symbol             | -1 Speed Grade |     | -2 Spee | d Grade | -3 Speed Grade |     | Unit |

|--------------------|----------------|-----|---------|---------|----------------|-----|------|

|                    | Min            | Max | Min     | Max     | Min            | Max |      |

| t <sub>CH</sub>    | 2.00           |     | 2.50    |         | 2.75           |     | ns   |

| t <sub>CL</sub>    | 2.00           |     | 2.50    |         | 2.75           |     | ns   |

| t <sub>CLRP</sub>  | 0.18           |     | 0.26    |         | 0.34           |     | ns   |

| t <sub>PREP</sub>  | 0.18           |     | 0.26    |         | 0.34           |     | ns   |

| t <sub>ESBCH</sub> | 2.00           |     | 2.50    |         | 2.75           |     | ns   |

| t <sub>ESBCL</sub> | 2.00           |     | 2.50    |         | 2.75           |     | ns   |

| t <sub>ESBWP</sub> | 1.17           |     | 1.68    |         | 2.18           |     | ns   |

| t <sub>ESBRP</sub> | 0.95           |     | 1.35    |         | 1.76           |     | ns   |

| Symbol              | -1 Speed Grade |      | -2 Spee | d Grade | -3 Speed Grade |      | Unit |

|---------------------|----------------|------|---------|---------|----------------|------|------|

|                     | Min            | Max  | Min     | Max     | Min            | Max  |      |

| t <sub>INSU</sub>   | 2.74           |      | 2.74    |         | 2.87           |      | ns   |

| t <sub>INH</sub>    | 0.00           |      | 0.00    |         | 0.00           |      | ns   |

| toutco              | 2.00           | 5.51 | 2.00    | 6.06    | 2.00           | 6.61 | ns   |

| tINSUPLL            | 1.86           |      | 1.96    |         | -              |      | ns   |

| t <sub>INHPLL</sub> | 0.00           |      | 0.00    |         | -              |      | ns   |

| toutcopll           | 0.50           | 2.62 | 0.50    | 2.91    | -              | -    | ns   |

| Symbol                    | -1 Speed Grade |      | -2 Spee | d Grade | -3 Spee | Unit |    |

|---------------------------|----------------|------|---------|---------|---------|------|----|

|                           | Min            | Max  | Min     | Max     | Min     | Max  | 1  |

| t <sub>insubidir</sub>    | 0.64           |      | 0.98    |         | 1.08    |      | ns |

| t <sub>inhbidir</sub>     | 0.00           |      | 0.00    |         | 0.00    |      | ns |

| t <sub>outcobidir</sub>   | 2.00           | 5.51 | 2.00    | 6.06    | 2.00    | 6.61 | ns |

| t <sub>xzbidir</sub>      |                | 6.10 |         | 6.74    |         | 7.10 | ns |

| t <sub>zxbidir</sub>      |                | 6.10 |         | 6.74    |         | 7.10 | ns |

| t <sub>insubidirpll</sub> | 2.26           |      | 2.68    |         | -       |      | ns |

| t <sub>inhbidirpll</sub>  | 0.00           |      | 0.00    |         | -       |      | ns |

| toutcobidirpll            | 0.50           | 2.62 | 0.50    | 2.91    | -       | -    | ns |

| t <sub>xzbidirpll</sub>   |                | 3.21 |         | 3.59    |         | -    | ns |

| t <sub>ZXBIDIRPLL</sub>   |                | 3.21 |         | 3.59    |         | -    | ns |

## APEX 20K Programmable Logic Device Family Data Sheet

| Table 99. EP20K1000E f <sub>MAX</sub> Routing Delays |         |         |                   |      |         |         |      |  |  |  |

|------------------------------------------------------|---------|---------|-------------------|------|---------|---------|------|--|--|--|

| Symbol                                               | -1 Spee | d Grade | le -2 Speed Grade |      | -3 Spee | d Grade | Unit |  |  |  |

|                                                      | Min     | Max     | Min               | Max  | Min     | Max     |      |  |  |  |

| t <sub>F1-4</sub>                                    |         | 0.27    |                   | 0.27 |         | 0.27    | ns   |  |  |  |

| t <sub>F5-20</sub>                                   |         | 1.45    |                   | 1.63 |         | 1.75    | ns   |  |  |  |

| t <sub>F20+</sub>                                    |         | 4.15    |                   | 4.33 |         | 4.97    | ns   |  |  |  |

| Symbol             | -1 Speed Grade |     | -2 Spee | d Grade | -3 Spee | Unit |    |

|--------------------|----------------|-----|---------|---------|---------|------|----|

|                    | Min            | Max | Min     | Max     | Min     | Max  | 7  |

| t <sub>CH</sub>    | 1.25           |     | 1.43    |         | 1.67    |      | ns |

| t <sub>CL</sub>    | 1.25           |     | 1.43    |         | 1.67    |      | ns |

| t <sub>CLRP</sub>  | 0.20           |     | 0.20    |         | 0.20    |      | ns |

| t <sub>PREP</sub>  | 0.20           |     | 0.20    |         | 0.20    |      | ns |

| t <sub>ESBCH</sub> | 1.25           |     | 1.43    |         | 1.67    |      | ns |

| t <sub>ESBCL</sub> | 1.25           |     | 1.43    |         | 1.67    |      | ns |

| t <sub>ESBWP</sub> | 1.28           |     | 1.51    |         | 1.65    |      | ns |

| t <sub>ESBRP</sub> | 1.11           |     | 1.29    |         | 1.41    |      | ns |

| Table 101. EP20K1000E External Timing Parameters |                |      |         |          |                |      |      |  |  |

|--------------------------------------------------|----------------|------|---------|----------|----------------|------|------|--|--|

| Symbol                                           | -1 Speed Grade |      | -2 Spee | ed Grade | -3 Speed Grade |      | Unit |  |  |

|                                                  | Min            | Max  | Min     | Max      | Min            | Max  |      |  |  |

| t <sub>INSU</sub>                                | 2.70           |      | 2.84    |          | 2.97           |      | ns   |  |  |

| t <sub>INH</sub>                                 | 0.00           |      | 0.00    |          | 0.00           |      | ns   |  |  |

| t <sub>outco</sub>                               | 2.00           | 5.75 | 2.00    | 6.33     | 2.00           | 6.90 | ns   |  |  |

| t <sub>INSUPLL</sub>                             | 1.64           |      | 2.09    |          | -              |      | ns   |  |  |

| t <sub>INHPLL</sub>                              | 0.00           |      | 0.00    |          | -              |      | ns   |  |  |

| t <sub>outcopll</sub>                            | 0.50           | 2.25 | 0.50    | 2.99     | -              | -    | ns   |  |  |

| Symbol             | -1 Speed Grade |     | -2 Spee | d Grade | -3 Speed Grade |     | Unit |

|--------------------|----------------|-----|---------|---------|----------------|-----|------|

|                    | Min            | Max | Min     | Max     | Min            | Мах |      |

| t <sub>CH</sub>    | 1.25           |     | 1.43    |         | 1.67           |     | ns   |

| t <sub>CL</sub>    | 1.25           |     | 1.43    |         | 1.67           |     | ns   |

| t <sub>CLRP</sub>  | 0.20           |     | 0.20    |         | 0.20           |     | ns   |

| t <sub>PREP</sub>  | 0.20           |     | 0.20    |         | 0.20           |     | ns   |

| t <sub>ESBCH</sub> | 1.25           |     | 1.43    |         | 1.67           |     | ns   |

| t <sub>ESBCL</sub> | 1.25           |     | 1.43    |         | 1.67           |     | ns   |

| t <sub>ESBWP</sub> | 1.28           |     | 1.51    |         | 1.65           |     | ns   |

| t <sub>ESBRP</sub> | 1.11           |     | 1.29    |         | 1.41           |     | ns   |

| Table 107. EP20K1500E External Timing Parameters |         |                |      |                |      |         |      |  |  |

|--------------------------------------------------|---------|----------------|------|----------------|------|---------|------|--|--|

| Symbol                                           | -1 Spee | -1 Speed Grade |      | -2 Speed Grade |      | l Grade | Unit |  |  |

|                                                  | Min     | Max            | Min  | Max            | Min  | Max     |      |  |  |

| tINSU                                            | 3.09    |                | 3.30 |                | 3.58 |         | ns   |  |  |

| t <sub>INH</sub>                                 | 0.00    |                | 0.00 |                | 0.00 |         | ns   |  |  |

| t <sub>outco</sub>                               | 2.00    | 6.18           | 2.00 | 6.81           | 2.00 | 7.36    | ns   |  |  |

| tINSUPLL                                         | 1.94    |                | 2.08 |                | -    |         | ns   |  |  |

| t <sub>INHPLL</sub>                              | 0.00    |                | 0.00 |                | -    |         | ns   |  |  |

| toutcopll                                        | 0.50    | 2.67           | 0.50 | 2.99           | -    | -       | ns   |  |  |