Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 1664                                                        |

| Number of Logic Elements/Cells | 16640                                                       |

| Total RAM Bits                 | 212992                                                      |

| Number of I/O                  | -                                                           |

| Number of Gates                | 1052000                                                     |

| Voltage - Supply               | 1.71V ~ 1.89V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 240-BFQFP Exposed Pad                                       |

| Supplier Device Package        | 240-RQFP (32x32)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep20k400erc240-2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

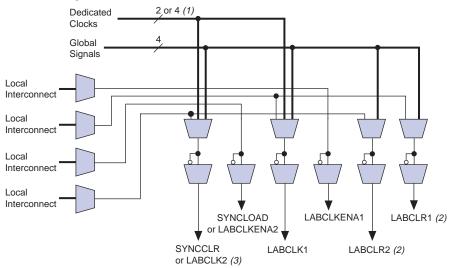

Each LAB contains dedicated logic for driving control signals to its LEs and ESBs. The control signals include clock, clock enable, asynchronous clear, asynchronous preset, asynchronous load, synchronous clear, and synchronous load signals. A maximum of six control signals can be used at a time. Although synchronous load and clear signals are generally used when implementing counters, they can also be used with other functions.

Each LAB can use two clocks and two clock enable signals. Each LAB's clock and clock enable signals are linked (e.g., any LE in a particular LAB using CLK1 will also use CLKENA1). LEs with the same clock but different clock enable signals either use both clock signals in one LAB or are placed into separate LABs.

If both the rising and falling edges of a clock are used in a LAB, both LAB-wide clock signals are used.

The LAB-wide control signals can be generated from the LAB local interconnect, global signals, and dedicated clock pins. The inherent low skew of the FastTrack Interconnect enables it to be used for clock distribution. Figure 4 shows the LAB control signal generation circuit.

Figure 4. LAB Control Signal Generation

#### Notes to Figure 4:

- (1) APEX 20KE devices have four dedicated clocks.

- (2) The LABCLR1 and LABCLR2 signals also control asynchronous load and asynchronous preset for LEs within the LAB.

- (3) The SYNCCLR signal can be generated by the local interconnect or global signals.

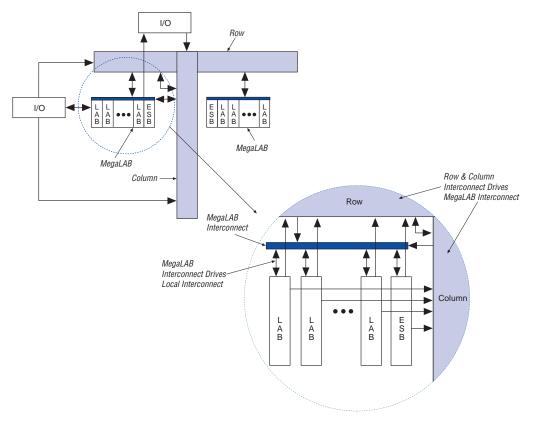

Figure 10. FastTrack Connection to Local Interconnect

Figure 11 shows the intersection of a row and column interconnect, and how these forms of interconnects and LEs drive each other.

Row Interconnect

MegaLAB Interconnect

Column Interconnect

Interconnect

Figure 11. Driving the FastTrack Interconnect

APEX 20KE devices include an enhanced interconnect structure for faster routing of input signals with high fan-out. Column I/O pins can drive the FastRow interconnect, which routes signals directly into the local interconnect without having to drive through the MegaLAB interconnect. FastRow lines traverse two MegaLAB structures. Also, these pins can drive the local interconnect directly for fast setup times. On EP20K300E and larger devices, the FastRow interconnect drives the two MegaLABs in the top left corner, the two MegaLABs in the top right corner, the two MegaLABS in the bottom left corner, and the two MegaLABs in the bottom right corner. On EP20K200E and smaller devices, FastRow interconnect drives the two MegaLABs on the top and the two MegaLABs on the bottom of the device. On all devices, the FastRow interconnect drives all local interconnect in the appropriate MegaLABs except the local interconnect on the side of the MegaLAB opposite the ESB. Pins using the FastRow interconnect achieve a faster set-up time, as the signal does not need to use a MegaLAB interconnect line to reach the destination LE. Figure 12 shows the FastRow interconnect.

Figure 14. APEX 20K Macrocell

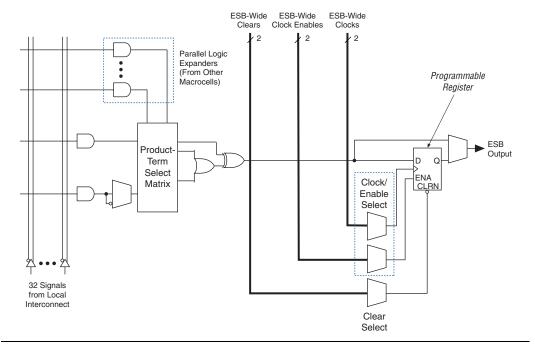

For registered functions, each macrocell register can be programmed individually to implement D, T, JK, or SR operation with programmable clock control. The register can be bypassed for combinatorial operation. During design entry, the designer specifies the desired register type; the Quartus II software then selects the most efficient register operation for each registered function to optimize resource utilization. The Quartus II software or other synthesis tools can also select the most efficient register operation automatically when synthesizing HDL designs.

Each programmable register can be clocked by one of two ESB-wide clocks. The ESB-wide clocks can be generated from device dedicated clock pins, global signals, or local interconnect. Each clock also has an associated clock enable, generated from the local interconnect. The clock and clock enable signals are related for a particular ESB; any macrocell using a clock also uses the associated clock enable.

If both the rising and falling edges of a clock are used in an ESB, both ESB-wide clock signals are used.

From Previous Macrocell Product-Macrocell Term Product-Select Term Logic Matrix Parallel Expander Switch Product-Macrocell Term Product-Select Term Logic Matrix Parallel Expander Switch 32 Signals from To Next

Figure 16. APEX 20K Parallel Expanders

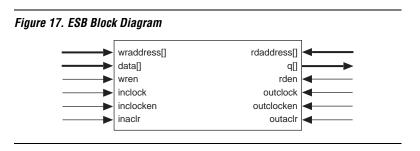

## Embedded System Block

Local Interconnect

The ESB can implement various types of memory blocks, including dual-port RAM, ROM, FIFO, and CAM blocks. The ESB includes input and output registers; the input registers synchronize writes, and the output registers can pipeline designs to improve system performance. The ESB offers a dual-port mode, which supports simultaneous reads and writes at two different clock frequencies. Figure 17 shows the ESB block diagram.

Macrocell

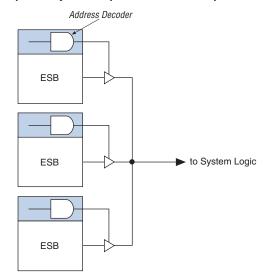

Figure 18. Deep Memory Block Implemented with Multiple ESBs

The ESB implements two forms of dual-port memory: read/write clock mode and input/output clock mode. The ESB can also be used for bidirectional, dual-port memory applications in which two ports read or write simultaneously. To implement this type of dual-port memory, two or four ESBs are used to support two simultaneous reads or writes. This functionality is shown in Figure 19.

Figure 19. APEX 20K ESB Implementing Dual-Port RAM

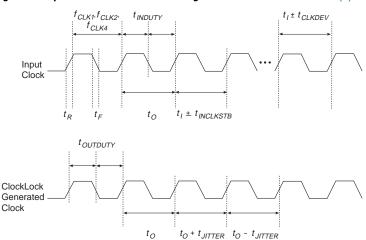

Figure 30. Specifications for the Incoming & Generated Clocks Note (1)

*Note to Figure 30:*

(1) The tl parameter refers to the nominal input clock period; the tO parameter refers to the nominal output clock period.

Table 15 summarizes the APEX 20K ClockLock and ClockBoost parameters for -1 speed-grade devices.

| Symbol                | Parameter                                                                                                                | Min | Max        | Unit |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------|-----|------------|------|

| f <sub>OUT</sub>      | Output frequency                                                                                                         | 25  | 180        | MHz  |

| f <sub>CLK1</sub> (1) | Input clock frequency (ClockBoost clock multiplication factor equals 1)                                                  | 25  | 180 (1)    | MHz  |

| f <sub>CLK2</sub>     | Input clock frequency (ClockBoost clock multiplication factor equals 2)                                                  | 16  | 90         | MHz  |

| f <sub>CLK4</sub>     | Input clock frequency (ClockBoost clock multiplication factor equals 4)                                                  | 10  | 48         | MHz  |

| <sup>t</sup> OUTDUTY  | Duty cycle for ClockLock/ClockBoost-generated clock                                                                      | 40  | 60         | %    |

| f <sub>CLKDEV</sub>   | Input deviation from user specification in the Quartus II software (ClockBoost clock multiplication factor equals 1) (2) |     | 25,000 (3) | PPM  |

| t <sub>R</sub>        | Input rise time                                                                                                          |     | 5          | ns   |

| t <sub>F</sub>        | Input fall time                                                                                                          |     | 5          | ns   |

| t <sub>LOCK</sub>     | Time required for ClockLock/ClockBoost to acquire lock (4)                                                               |     | 10         | μs   |

#### Notes to Table 16:

- (1) To implement the ClockLock and ClockBoost circuitry with the Quartus II software, designers must specify the input frequency. The Quartus II software tunes the PLL in the ClockLock and ClockBoost circuitry to this frequency. The f<sub>CLKDEV</sub> parameter specifies how much the incoming clock can differ from the specified frequency during device operation. Simulation does not reflect this parameter.

- (2) Twenty-five thousand parts per million (PPM) equates to 2.5% of input clock period.

- (3) During device configuration, the ClockLock and ClockBoost circuitry is configured before the rest of the device. If the incoming clock is supplied during configuration, the ClockLock and ClockBoost circuitry locks during configuration because the  $t_{LOCK}$  value is less than the time required for configuration.

- (4) The  $t_{IITTER}$  specification is measured under long-term observation.

Tables 17 and 18 summarize the ClockLock and ClockBoost parameters for APEX 20KE devices.

| Table 17. APEX 20KE ClockLock & ClockBoost Parameters   Note (1) |                                                           |            |     |     |                        |                  |  |  |  |

|------------------------------------------------------------------|-----------------------------------------------------------|------------|-----|-----|------------------------|------------------|--|--|--|

| Symbol                                                           | Parameter                                                 | Conditions | Min | Тур | Max                    | Unit             |  |  |  |

| t <sub>R</sub>                                                   | Input rise time                                           |            |     |     | 5                      | ns               |  |  |  |

| t <sub>F</sub>                                                   | Input fall time                                           |            |     |     | 5                      | ns               |  |  |  |

| t <sub>INDUTY</sub>                                              | Input duty cycle                                          |            | 40  |     | 60                     | %                |  |  |  |

| t <sub>INJITTER</sub>                                            | Input jitter peak-to-peak                                 |            |     |     | 2% of input period     | peak-to-<br>peak |  |  |  |

| t <sub>OUTJITTER</sub>                                           | Jitter on ClockLock or ClockBoost-<br>generated clock     |            |     |     | 0.35% of output period | RMS              |  |  |  |

| t <sub>OUTDUTY</sub>                                             | Duty cycle for ClockLock or ClockBoost-generated clock    |            | 45  |     | 55                     | %                |  |  |  |

| t <sub>LOCK</sub> (2), (3)                                       | Time required for ClockLock or ClockBoost to acquire lock |            |     |     | 40                     | μs               |  |  |  |

| Symbol                  | Parameter                                     | I/O Standard      | -1X Spe | ed Grade | -2X Spee | d Grade | Units |

|-------------------------|-----------------------------------------------|-------------------|---------|----------|----------|---------|-------|

|                         |                                               |                   | Min     | Max      | Min      | Max     |       |

| f <sub>VCO</sub> (4)    | Voltage controlled oscillator operating range |                   | 200     | 500      | 200      | 500     | MHz   |

| f <sub>CLOCK0</sub>     | Clock0 PLL output frequency for internal use  |                   | 1.5     | 335      | 1.5      | 200     | MHz   |

| f <sub>CLOCK1</sub>     | Clock1 PLL output frequency for internal use  |                   | 20      | 335      | 20       | 200     | MHz   |

| CLOCKO LATE :           | Output clock frequency for                    | 3.3-V LVTTL       | 1.5     | 245      | 1.5      | 226     | MHz   |

|                         | external clock0 output                        | 2.5-V LVTTL       | 1.5     | 234      | 1.5      | 221     | MHz   |

|                         |                                               | 1.8-V LVTTL       | 1.5     | 223      | 1.5      | 216     | MHz   |

|                         |                                               | GTL+              | 1.5     | 205      | 1.5      | 193     | MHz   |

|                         |                                               | SSTL-2 Class      | 1.5     | 158      | 1.5      | 157     | MHz   |

|                         |                                               | SSTL-2 Class      | 1.5     | 142      | 1.5      | 142     | MHz   |

|                         |                                               | SSTL-3 Class      | 1.5     | 166      | 1.5      | 162     | MHz   |

|                         |                                               | SSTL-3 Class      | 1.5     | 149      | 1.5      | 146     | MHz   |

|                         |                                               | LVDS              | 1.5     | 420      | 1.5      | 350     | MHz   |

| f <sub>CLOCK1_EXT</sub> | Output clock frequency for                    | 3.3-V LVTTL       | 20      | 245      | 20       | 226     | MHz   |

|                         | external clock1 output                        | 2.5-V LVTTL       | 20      | 234      | 20       | 221     | MHz   |

|                         |                                               | 1.8-V LVTTL       | 20      | 223      | 20       | 216     | MHz   |

|                         |                                               | GTL+              | 20      | 205      | 20       | 193     | MHz   |

|                         |                                               | SSTL-2 Class<br>I | 20      | 158      | 20       | 157     | MHz   |

|                         |                                               | SSTL-2 Class      | 20      | 142      | 20       | 142     | MHz   |

|                         |                                               | SSTL-3 Class      | 20      | 166      | 20       | 162     | MHz   |

|                         |                                               | SSTL-3 Class      | 20      | 149      | 20       | 146     | MHz   |

|                         |                                               | LVDS              | 20      | 420      | 20       | 350     | MHz   |

All specifications are always representative of worst-case supply voltage and junction temperature conditions. All output-pin-timing specifications are reported for maximum driver strength.

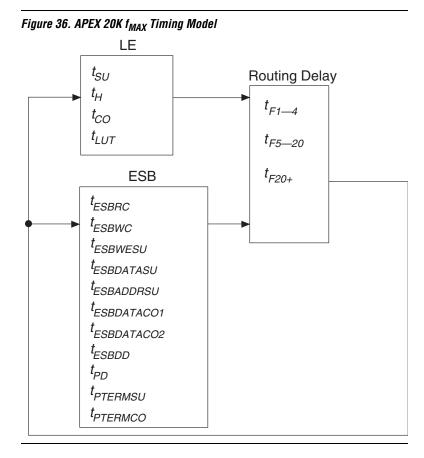

Figure 36 shows the  $f_{MAX}$  timing model for APEX 20K devices.

Figure 37 shows the  $f_{MAX}$  timing model for APEX 20KE devices. These parameters can be used to estimate  $f_{MAX}$  for multiple levels of logic. Quartus II software timing analysis should be used for more accurate timing information.

| Symbol                  | -1 Spee | d Grade | -2 Spee | d Grade | -3 Spee | d Grade | Units |

|-------------------------|---------|---------|---------|---------|---------|---------|-------|

|                         | Min     | Max     | Min     | Max     | Min     | Max     |       |

| t <sub>SU</sub>         | 0.1     |         | 0.3     |         | 0.6     |         | ns    |

| t <sub>H</sub>          | 0.5     |         | 0.8     |         | 0.9     |         | ns    |

| t <sub>CO</sub>         |         | 0.1     |         | 0.4     |         | 0.6     | ns    |

| t <sub>LUT</sub>        |         | 1.0     |         | 1.2     |         | 1.4     | ns    |

| t <sub>ESBRC</sub>      |         | 1.7     |         | 2.1     |         | 2.4     | ns    |

| t <sub>ESBWC</sub>      |         | 5.7     |         | 6.9     |         | 8.1     | ns    |

| t <sub>ESBWESU</sub>    | 3.3     |         | 3.9     |         | 4.6     |         | ns    |

| t <sub>ESBDATASU</sub>  | 2.2     |         | 2.7     |         | 3.1     |         | ns    |

| t <sub>ESBDATAH</sub>   | 0.6     |         | 0.8     |         | 0.9     |         | ns    |

| t <sub>ESBADDRSU</sub>  | 2.4     |         | 2.9     |         | 3.3     |         | ns    |

| t <sub>ESBDATACO1</sub> |         | 1.3     |         | 1.6     |         | 1.8     | ns    |

| t <sub>ESBDATACO2</sub> |         | 2.5     |         | 3.1     |         | 3.6     | ns    |

| t <sub>ESBDD</sub>      |         | 2.5     |         | 3.3     |         | 3.6     | ns    |

| t <sub>PD</sub>         |         | 2.5     |         | 3.1     |         | 3.6     | ns    |

| t <sub>PTERMSU</sub>    | 1.7     |         | 2.1     |         | 2.4     |         | ns    |

| t <sub>PTERMCO</sub>    |         | 1.0     |         | 1.2     |         | 1.4     | ns    |

| t <sub>F1-4</sub>       |         | 0.4     |         | 0.5     |         | 0.6     | ns    |

| t <sub>F5-20</sub>      |         | 2.6     |         | 2.8     |         | 2.9     | ns    |

| t <sub>F20+</sub>       |         | 3.7     |         | 3.8     |         | 3.9     | ns    |

| t <sub>CH</sub>         | 2.0     |         | 2.5     |         | 3.0     |         | ns    |

| t <sub>CL</sub>         | 2.0     |         | 2.5     |         | 3.0     |         | ns    |

| t <sub>CLRP</sub>       | 0.5     |         | 0.6     |         | 0.8     |         | ns    |

| t <sub>PREP</sub>       | 0.5     |         | 0.5     |         | 0.5     |         | ns    |

| t <sub>ESBCH</sub>      | 2.0     |         | 2.5     |         | 3.0     |         | ns    |

| t <sub>ESBCL</sub>      | 2.0     |         | 2.5     |         | 3.0     |         | ns    |

| t <sub>ESBWP</sub>      | 1.5     |         | 1.9     |         | 2.2     |         | ns    |

| t <sub>ESBRP</sub>      | 1.0     |         | 1.2     |         | 1.4     |         | ns    |

Tables 43 through 48 show the I/O external and external bidirectional timing parameter values for EP20K100, EP20K200, and EP20K400 APEX 20K devices.

| Symbol                      | -1 Speed Grade |     | -2 Spee | -2 Speed Grade |     | d Grade | Unit |

|-----------------------------|----------------|-----|---------|----------------|-----|---------|------|

|                             | Min            | Max | Min     | Max            | Min | Max     |      |

| t <sub>INSUBIDIR</sub> (1)  | 1.9            |     | 2.3     |                | 2.6 |         | ns   |

| t <sub>INHBIDIR</sub> (1)   | 0.0            |     | 0.0     |                | 0.0 |         | ns   |

| t <sub>OUTCOBIDIR</sub> (1) | 2.0            | 4.6 | 2.0     | 5.6            | 2.0 | 6.8     | ns   |

| t <sub>XZBIDIR</sub> (1)    |                | 5.0 |         | 5.9            |     | 6.9     | ns   |

| t <sub>ZXBIDIR</sub> (1)    |                | 5.0 |         | 5.9            |     | 6.9     | ns   |

| t <sub>INSUBIDIR</sub> (2)  | 1.1            |     | 1.2     |                | -   |         | ns   |

| t <sub>INHBIDIR</sub> (2)   | 0.0            |     | 0.0     |                | -   |         | ns   |

| t <sub>OUTCOBIDIR</sub> (2) | 0.5            | 2.7 | 0.5     | 3.1            | -   | _       | ns   |

| t <sub>XZBIDIR</sub> (2)    |                | 4.3 |         | 5.0            |     | _       | ns   |

| t <sub>ZXBIDIR</sub> (2)    |                | 4.3 |         | 5.0            |     | _       | ns   |

| Table 47. EP20K400 External Timing Parameters |         |         |         |          |                |     |      |  |  |  |

|-----------------------------------------------|---------|---------|---------|----------|----------------|-----|------|--|--|--|

| Symbol                                        | -1 Spee | d Grade | -2 Spec | ed Grade | -3 Speed Grade |     | Unit |  |  |  |

|                                               | Min     | Max     | Min     | Max      | Min            | Max | 1    |  |  |  |

| t <sub>INSU</sub> (1)                         | 1.4     |         | 1.8     |          | 2.0            |     | ns   |  |  |  |

| t <sub>INH</sub> (1)                          | 0.0     |         | 0.0     |          | 0.0            |     | ns   |  |  |  |

| t <sub>OUTCO</sub> (1)                        | 2.0     | 4.9     | 2.0     | 6.1      | 2.0            | 7.0 | ns   |  |  |  |

| t <sub>INSU</sub> (2)                         | 0.4     |         | 1.0     |          | -              |     | ns   |  |  |  |

| t <sub>INH</sub> (2)                          | 0.0     |         | 0.0     |          | _              |     | ns   |  |  |  |

| t <sub>OUTCO</sub> (2)                        | 0.5     | 3.1     | 0.5     | 4.1      | _              | _   | ns   |  |  |  |

| Table 48. EP20K400 External Bidirections | I Timina | Parameters 1 4 1 |

|------------------------------------------|----------|------------------|

|------------------------------------------|----------|------------------|

| Symbol                      | -1 Spee | d Grade | -2 Spee | ed Grade | -3 Spe | ed Grade | Unit |

|-----------------------------|---------|---------|---------|----------|--------|----------|------|

|                             | Min     | Max     | Min     | Max      | Min    | Max      |      |

| t <sub>INSUBIDIR</sub> (1)  | 1.4     |         | 1.8     |          | 2.0    |          | ns   |

| t <sub>INHBIDIR</sub> (1)   | 0.0     |         | 0.0     |          | 0.0    |          | ns   |

| t <sub>OUTCOBIDIR</sub> (1) | 2.0     | 4.9     | 2.0     | 6.1      | 2.0    | 7.0      | ns   |

| t <sub>XZBIDIR</sub> (1)    |         | 7.3     |         | 8.9      |        | 10.3     | ns   |

| t <sub>ZXBIDIR</sub> (1)    |         | 7.3     |         | 8.9      |        | 10.3     | ns   |

| t <sub>INSUBIDIR</sub> (2)  | 0.5     |         | 1.0     |          | -      |          | ns   |

| t <sub>INHBIDIR</sub> (2)   | 0.0     |         | 0.0     |          | -      |          | ns   |

| toutcobidir (2)             | 0.5     | 3.1     | 0.5     | 4.1      | -      | -        | ns   |

| t <sub>XZBIDIR</sub> (2)    |         | 6.2     |         | 7.6      |        | -        | ns   |

| t <sub>ZXBIDIR</sub> (2)    |         | 6.2     |         | 7.6      |        | _        | ns   |

| Symbol                  | -    | 1    |      | -2   | -3   |      | Unit |

|-------------------------|------|------|------|------|------|------|------|

|                         | Min  | Max  | Min  | Max  | Min  | Max  |      |

| t <sub>ESBARC</sub>     |      | 2.03 |      | 2.86 |      | 4.24 | ns   |

| t <sub>ESBSRC</sub>     |      | 2.58 |      | 3.49 |      | 5.02 | ns   |

| t <sub>ESBAWC</sub>     |      | 3.88 |      | 5.45 |      | 8.08 | ns   |

| t <sub>ESBSWC</sub>     |      | 4.08 |      | 5.35 |      | 7.48 | ns   |

| t <sub>ESBWASU</sub>    | 1.77 |      | 2.49 |      | 3.68 |      | ns   |

| t <sub>ESBWAH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>ESBWDSU</sub>    | 1.95 |      | 2.74 |      | 4.05 |      | ns   |

| t <sub>ESBWDH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>ESBRASU</sub>    | 1.96 |      | 2.75 |      | 4.07 |      | ns   |

| t <sub>ESBRAH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>ESBWESU</sub>    | 1.80 |      | 2.73 |      | 4.28 |      | ns   |

| t <sub>ESBWEH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>ESBDATASU</sub>  | 0.07 |      | 0.48 |      | 1.17 |      | ns   |

| t <sub>ESBDATAH</sub>   | 0.13 |      | 0.13 |      | 0.13 |      | ns   |

| t <sub>ESBWADDRSU</sub> | 0.30 |      | 0.80 |      | 1.64 |      | ns   |

| t <sub>ESBRADDRSU</sub> | 0.37 |      | 0.90 |      | 1.78 |      | ns   |

| t <sub>ESBDATACO1</sub> |      | 1.11 |      | 1.32 |      | 1.67 | ns   |

| t <sub>ESBDATACO2</sub> |      | 2.65 |      | 3.73 |      | 5.53 | ns   |

| t <sub>ESBDD</sub>      |      | 3.88 |      | 5.45 |      | 8.08 | ns   |

| t <sub>PD</sub>         |      | 1.91 | _    | 2.69 |      | 3.98 | ns   |

| t <sub>PTERMSU</sub>    | 1.04 |      | 1.71 |      | 2.82 |      | ns   |

| t <sub>PTERMCO</sub>    |      | 1.13 |      | 1.34 |      | 1.69 | ns   |

| Table 51. EP20K30E f <sub>MAX</sub> Routing Delays |     |      |     |      |     |        |    |  |  |  |

|----------------------------------------------------|-----|------|-----|------|-----|--------|----|--|--|--|

| Symbol                                             | -   | 1    | ,   | -2   | -;  | 3 Unit |    |  |  |  |

|                                                    | Min | Max  | Min | Max  | Min | Max    |    |  |  |  |

| t <sub>F1-4</sub>                                  |     | 0.24 |     | 0.27 |     | 0.31   | ns |  |  |  |

| t <sub>F5-20</sub>                                 |     | 1.03 |     | 1.14 |     | 1.30   | ns |  |  |  |

| t <sub>F20+</sub>                                  |     | 1.42 |     | 1.54 |     | 1.77   | ns |  |  |  |

| Table 76. EP20K200E Minimum Pulse Width Timing Parameters |      |     |      |     |      |     |      |  |  |

|-----------------------------------------------------------|------|-----|------|-----|------|-----|------|--|--|

| Symbol                                                    |      | 1   | -    | 2   | -:   | 3   | Unit |  |  |

|                                                           | Min  | Max | Min  | Max | Min  | Max |      |  |  |

| t <sub>CH</sub>                                           | 1.36 |     | 2.44 |     | 2.65 |     | ns   |  |  |

| t <sub>CL</sub>                                           | 1.36 |     | 2.44 |     | 2.65 |     | ns   |  |  |

| t <sub>CLRP</sub>                                         | 0.18 |     | 0.19 |     | 0.21 |     | ns   |  |  |

| t <sub>PREP</sub>                                         | 0.18 |     | 0.19 |     | 0.21 |     | ns   |  |  |

| t <sub>ESBCH</sub>                                        | 1.36 |     | 2.44 |     | 2.65 |     | ns   |  |  |

| t <sub>ESBCL</sub>                                        | 1.36 |     | 2.44 |     | 2.65 |     | ns   |  |  |

| t <sub>ESBWP</sub>                                        | 1.18 |     | 1.48 |     | 1.76 |     | ns   |  |  |

| t <sub>ESBRP</sub>                                        | 0.95 |     | 1.17 |     | 1.41 |     | ns   |  |  |

| Symbol                | -    | 1    | -    | 2    | -3   | 3    | Unit |

|-----------------------|------|------|------|------|------|------|------|

|                       | Min  | Max  | Min  | Max  | Min  | Max  |      |

| t <sub>INSU</sub>     | 2.24 |      | 2.35 |      | 2.47 |      | ns   |

| t <sub>INH</sub>      | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>outco</sub>    | 2.00 | 5.12 | 2.00 | 5.62 | 2.00 | 6.11 | ns   |

| t <sub>INSUPLL</sub>  | 2.13 |      | 2.07 |      | -    |      | ns   |

| t <sub>INHPLL</sub>   | 0.00 |      | 0.00 |      | -    |      | ns   |

| t <sub>OUTCOPLL</sub> | 0.50 | 3.01 | 0.50 | 3.36 | -    | -    | ns   |

| Symbol                  | -1 Speed Grade |      | -2 Speed Grade |      | -3 Spee | Unit |    |

|-------------------------|----------------|------|----------------|------|---------|------|----|

|                         | Min            | Max  | Min            | Max  | Min     | Max  |    |

| t <sub>ESBARC</sub>     |                | 1.67 |                | 1.91 |         | 1.99 | ns |

| t <sub>ESBSRC</sub>     |                | 2.30 |                | 2.66 |         | 2.93 | ns |

| t <sub>ESBAWC</sub>     |                | 3.09 |                | 3.58 |         | 3.99 | ns |

| t <sub>ESBSWC</sub>     |                | 3.01 |                | 3.65 |         | 4.05 | ns |

| t <sub>ESBWASU</sub>    | 0.54           |      | 0.63           |      | 0.65    |      | ns |

| t <sub>ESBWAH</sub>     | 0.36           |      | 0.43           |      | 0.42    |      | ns |

| t <sub>ESBWDSU</sub>    | 0.69           |      | 0.77           |      | 0.84    |      | ns |

| t <sub>ESBWDH</sub>     | 0.36           |      | 0.43           |      | 0.42    |      | ns |

| t <sub>ESBRASU</sub>    | 1.61           |      | 1.77           |      | 1.86    |      | ns |

| t <sub>ESBRAH</sub>     | 0.00           |      | 0.00           |      | 0.01    |      | ns |

| t <sub>ESBWESU</sub>    | 1.35           |      | 1.47           |      | 1.61    |      | ns |

| t <sub>ESBWEH</sub>     | 0.00           |      | 0.00           |      | 0.00    |      | ns |

| t <sub>ESBDATASU</sub>  | -0.18          |      | -0.30          |      | -0.27   |      | ns |

| t <sub>ESBDATAH</sub>   | 0.13           |      | 0.13           |      | 0.13    |      | ns |

| t <sub>ESBWADDRSU</sub> | -0.02          |      | -0.11          |      | -0.03   |      | ns |

| t <sub>ESBRADDRSU</sub> | 0.06           |      | -0.01          |      | -0.05   |      | ns |

| t <sub>ESBDATACO1</sub> |                | 1.16 |                | 1.40 |         | 1.54 | ns |

| t <sub>ESBDATACO2</sub> |                | 2.18 |                | 2.55 |         | 2.85 | ns |

| t <sub>ESBDD</sub>      |                | 2.73 |                | 3.17 |         | 3.58 | ns |

| t <sub>PD</sub>         |                | 1.57 |                | 1.83 |         | 2.07 | ns |

| t <sub>PTERMSU</sub>    | 0.92           |      | 0.99           |      | 1.18    |      | ns |

| t <sub>PTERMCO</sub>    |                | 1.18 |                | 1.43 |         | 1.17 | ns |

| Table 92. EP20K         | 600E f <sub>MAX</sub> ESE | 3 Timing Micr | oparameters |                |      |                |    |

|-------------------------|---------------------------|---------------|-------------|----------------|------|----------------|----|

| Symbol                  | -1 Speed Grade            |               | -2 Spee     | -2 Speed Grade |      | -3 Speed Grade |    |

|                         | Min                       | Max           | Min         | Max            | Min  | Max            |    |

| t <sub>ESBARC</sub>     |                           | 1.67          |             | 2.39           |      | 3.11           | ns |

| t <sub>ESBSRC</sub>     |                           | 2.27          |             | 3.07           |      | 3.86           | ns |

| t <sub>ESBAWC</sub>     |                           | 3.19          |             | 4.56           |      | 5.93           | ns |

| t <sub>ESBSWC</sub>     |                           | 3.51          |             | 4.62           |      | 5.72           | ns |

| t <sub>ESBWASU</sub>    | 1.46                      |               | 2.08        |                | 2.70 |                | ns |

| t <sub>ESBWAH</sub>     | 0.00                      |               | 0.00        |                | 0.00 |                | ns |

| t <sub>ESBWDSU</sub>    | 1.60                      |               | 2.29        |                | 2.97 |                | ns |

| t <sub>ESBWDH</sub>     | 0.00                      |               | 0.00        |                | 0.00 |                | ns |

| t <sub>ESBRASU</sub>    | 1.61                      |               | 2.30        |                | 2.99 |                | ns |

| t <sub>ESBRAH</sub>     | 0.00                      |               | 0.00        |                | 0.00 |                | ns |

| t <sub>ESBWESU</sub>    | 1.49                      |               | 2.30        |                | 3.11 |                | ns |

| t <sub>ESBWEH</sub>     | 0.00                      |               | 0.00        |                | 0.00 |                | ns |

| t <sub>ESBDATASU</sub>  | -0.01                     |               | 0.35        |                | 0.71 |                | ns |

| t <sub>ESBDATAH</sub>   | 0.13                      |               | 0.13        |                | 0.13 |                | ns |

| t <sub>ESBWADDRSU</sub> | 0.19                      |               | 0.62        |                | 1.06 |                | ns |

| t <sub>ESBRADDRSU</sub> | 0.25                      |               | 0.71        |                | 1.17 |                | ns |

| t <sub>ESBDATACO1</sub> |                           | 1.01          |             | 1.19           |      | 1.37           | ns |

| t <sub>ESBDATACO2</sub> |                           | 2.18          |             | 3.12           |      | 4.05           | ns |

| t <sub>ESBDD</sub>      |                           | 3.19          |             | 4.56           |      | 5.93           | ns |

| t <sub>PD</sub>         |                           | 1.57          |             | 2.25           |      | 2.92           | ns |

| t <sub>PTERMSU</sub>    | 0.85                      |               | 1.43        |                | 2.01 |                | ns |

| t <sub>PTERMCO</sub>    |                           | 1.03          |             | 1.21           |      | 1.39           | ns |

| Table 93. EP20K600E f <sub>MAX</sub> Routing Delays |         |         |        |          |         |         |      |  |  |  |

|-----------------------------------------------------|---------|---------|--------|----------|---------|---------|------|--|--|--|

| Symbol                                              | -1 Spee | d Grade | -2 Spe | ed Grade | -3 Spee | d Grade | Unit |  |  |  |

|                                                     | Min     | Max     | Min    | Max      | Min     | Max     |      |  |  |  |

| t <sub>F1-4</sub>                                   |         | 0.22    |        | 0.25     |         | 0.26    | ns   |  |  |  |

| t <sub>F5-20</sub>                                  |         | 1.26    |        | 1.39     |         | 1.52    | ns   |  |  |  |

| t <sub>F20+</sub>                                   |         | 3.51    |        | 3.88     |         | 4.26    | ns   |  |  |  |

| Symbol                     | -1 Speed Grade |      | -2 Spee | d Grade | -3 Spee | Unit |    |

|----------------------------|----------------|------|---------|---------|---------|------|----|

|                            | Min            | Max  | Min     | Max     | Min     | Max  | 1  |

| t <sub>INSUBIDIR</sub>     | 3.22           |      | 3.33    |         | 3.51    |      | ns |

| t <sub>INHBIDIR</sub>      | 0.00           |      | 0.00    |         | 0.00    |      | ns |

| t <sub>OUTCOBIDIR</sub>    | 2.00           | 5.75 | 2.00    | 6.33    | 2.00    | 6.90 | ns |

| t <sub>XZBIDIR</sub>       |                | 6.31 |         | 7.09    |         | 7.76 | ns |

| tzxbidir                   |                | 6.31 |         | 7.09    |         | 7.76 | ns |

| t <sub>INSUBIDIRPL</sub> L | 3.25           |      | 3.26    |         |         |      | ns |

| t <sub>INHBIDIRPLL</sub>   | 0.00           |      | 0.00    |         |         |      | ns |

| t <sub>OUTCOBIDIRPLL</sub> | 0.50           | 2.25 | 0.50    | 2.99    |         |      | ns |

| txzbidirpll                |                | 2.81 |         | 3.80    |         |      | ns |

| tzxbidirpll                |                | 2.81 |         | 3.80    |         |      | ns |

Tables 103 through 108 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K1500E APEX 20KE devices.

| Table 103. EP20K1500E f <sub>MAX</sub> LE Timing Microparameters |         |         |         |         |         |      |    |  |  |

|------------------------------------------------------------------|---------|---------|---------|---------|---------|------|----|--|--|

| Symbol                                                           | -1 Spee | d Grade | -2 Spee | d Grade | -3 Spee | Unit |    |  |  |

|                                                                  | Min     | Max     | Min     | Max     | Min     | Max  |    |  |  |

| t <sub>SU</sub>                                                  | 0.25    |         | 0.25    |         | 0.25    |      | ns |  |  |

| t <sub>H</sub>                                                   | 0.25    |         | 0.25    |         | 0.25    |      | ns |  |  |

| t <sub>CO</sub>                                                  |         | 0.28    |         | 0.32    |         | 0.33 | ns |  |  |

| t <sub>LUT</sub>                                                 |         | 0.80    |         | 0.95    |         | 1.13 | ns |  |  |

| Table 110. Selectable I/O Standard Output Delays |         |          |         |                               |     |         |      |  |  |

|--------------------------------------------------|---------|----------|---------|-------------------------------|-----|---------|------|--|--|

| Symbol                                           | -1 Spec | ed Grade | -2 Spec | -2 Speed Grade -3 Speed Grade |     | d Grade | Unit |  |  |

|                                                  | Min     | Max      | Min     | Max                           | Min | Max     | Min  |  |  |

| LVCMOS                                           |         | 0.00     |         | 0.00                          |     | 0.00    | ns   |  |  |

| LVTTL                                            |         | 0.00     |         | 0.00                          |     | 0.00    | ns   |  |  |

| 2.5 V                                            |         | 0.00     |         | 0.09                          |     | 0.10    | ns   |  |  |

| 1.8 V                                            |         | 2.49     |         | 2.98                          |     | 3.03    | ns   |  |  |

| PCI                                              |         | -0.03    |         | 0.17                          |     | 0.16    | ns   |  |  |

| GTL+                                             |         | 0.75     |         | 0.75                          |     | 0.76    | ns   |  |  |

| SSTL-3 Class I                                   |         | 1.39     |         | 1.51                          |     | 1.50    | ns   |  |  |

| SSTL-3 Class II                                  |         | 1.11     |         | 1.23                          |     | 1.23    | ns   |  |  |

| SSTL-2 Class I                                   |         | 1.35     |         | 1.48                          |     | 1.47    | ns   |  |  |

| SSTL-2 Class II                                  |         | 1.00     |         | 1.12                          |     | 1.12    | ns   |  |  |

| LVDS                                             |         | -0.48    |         | -0.48                         |     | -0.48   | ns   |  |  |

| CTT                                              |         | 0.00     |         | 0.00                          |     | 0.00    | ns   |  |  |

| AGP                                              |         | 0.00     |         | 0.00                          |     | 0.00    | ns   |  |  |

# Power Consumption

To estimate device power consumption, use the interactive power calculator on the Altera web site at http://www.altera.com.

# Configuration & Operation

The APEX 20K architecture supports several configuration schemes. This section summarizes the device operating modes and available device configuration schemes.

## **Operating Modes**

The APEX architecture uses SRAM configuration elements that require configuration data to be loaded each time the circuit powers up. The process of physically loading the SRAM data into the device is called configuration. During initialization, which occurs immediately after configuration, the device resets registers, enables I/O pins, and begins to operate as a logic device. The I/O pins are tri-stated during power-up, and before and during configuration. Together, the configuration and initialization processes are called *command mode*; normal device operation is called *user mode*.

Before and during device configuration, all I/O pins are pulled to  $V_{\mbox{\scriptsize CCIO}}$  by a built-in weak pull-up resistor.

### Version 4.1

APEX 20K Programmable Logic Device Family Data Sheet version 4.1 contains the following changes:

- t<sub>ESBWEH</sub> added to Figure 37 and Tables 35, 50, 56, 62, 68, 74, 86, 92, 97, and 104.

- Updated EP20K300E device internal and external timing numbers in Tables 79 through 84.

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 http://www.altera.com Applications Hotline: (800) 800-EPLD Customer Marketing: (408) 544-7104 Literature Services: lit\_req@altera.com Copyright © 2004 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, mask work rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes

to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.