# E·XFL

### Intel - EP20K600EBC652-2 Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 2432                                                        |

| Number of Logic Elements/Cells | 24320                                                       |

| Total RAM Bits                 | 311296                                                      |

| Number of I/O                  | 488                                                         |

| Number of Gates                | 1537000                                                     |

| Voltage - Supply               | $1.71V \sim 1.89V$                                          |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 652-BGA                                                     |

| Supplier Device Package        | 652-BGA (45x45)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep20k600ebc652-2 |

|                                |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Feature                        | APEX 20K Devices                                                                                                                                                    | APEX 20KE Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MultiCore system integration   | Full support                                                                                                                                                        | Full support                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SignalTap logic analysis       | Full support                                                                                                                                                        | Full support                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 32/64-Bit, 33-MHz PCI          | Full compliance in -1, -2 speed grades                                                                                                                              | Full compliance in -1, -2 speed grades                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 32/64-Bit, 66-MHz PCI          | -                                                                                                                                                                   | Full compliance in -1 speed grade                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MultiVolt I/O                  | 2.5-V or 3.3-V $V_{CCIO}$<br>V <sub>CCIO</sub> selected for device<br>Certain devices are 5.0-V tolerant                                                            | 1.8-V, 2.5-V, or 3.3-V V <sub>CCIO</sub><br>V <sub>CCIO</sub> selected block-by-block<br>5.0-V tolerant with use of external resistor                                                                                                                                                                                                                                                                                                                                 |

| ClockLock support              | Clock delay reduction<br>2× and 4× clock multiplication                                                                                                             | Clock delay reduction<br>$m/(n \times v)$ or $m/(n \times k)$ clock multiplication<br>Drive ClockLock output off-chip<br>External clock feedback<br>ClockShift<br>LVDS support<br>Up to four PLLs<br>ClockShift, clock phase adjustment                                                                                                                                                                                                                               |

| Dedicated clock and input pins | Six                                                                                                                                                                 | Eight                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| I/O standard support           | 2.5-V, 3.3-V, 5.0-V I/O<br>3.3-V PCI<br>Low-voltage complementary<br>metal-oxide semiconductor<br>(LVCMOS)<br>Low-voltage transistor-to-transistor<br>logic (LVTTL) | 1.8-V, 2.5-V, 3.3-V, 5.0-V I/O<br>2.5-V I/O<br>3.3-V PCI and PCI-X<br>3.3-V Advanced Graphics Port (AGP)<br>Center tap terminated (CTT)<br>GTL+<br>LVCMOS<br>LVTTL<br>True-LVDS and LVPECL data pins<br>(in EP20K300E and larger devices)<br>LVDS and LVPECL signaling (in all BGA<br>and FineLine BGA devices)<br>LVDS and LVPECL data pins up to<br>156 Mbps (in -1 speed grade devices)<br>HSTL Class I<br>PCI-X<br>SSTL-2 Class I and II<br>SSTL-3 Class I and II |

| Memory support                 | Dual-port RAM<br>FIFO<br>RAM<br>ROM                                                                                                                                 | CAM<br>Dual-port RAM<br>FIFO<br>RAM<br>ROM                                                                                                                                                                                                                                                                                                                                                                                                                            |

#### Logic Element

The LE, the smallest unit of logic in the APEX 20K architecture, is compact and provides efficient logic usage. Each LE contains a four-input LUT, which is a function generator that can quickly implement any function of four variables. In addition, each LE contains a programmable register and carry and cascade chains. Each LE drives the local interconnect, MegaLAB interconnect, and FastTrack Interconnect routing structures. See Figure 5.

Each LE's programmable register can be configured for D, T, JK, or SR operation. The register's clock and clear control signals can be driven by global signals, general-purpose I/O pins, or any internal logic. For combinatorial functions, the register is bypassed and the output of the LUT drives the outputs of the LE.

The counter mode uses two three-input LUTs: one generates the counter data, and the other generates the fast carry bit. A 2-to-1 multiplexer provides synchronous loading, and another AND gate provides synchronous clearing. If the cascade function is used by an LE in counter mode, the synchronous clear or load overrides any signal carried on the cascade chain. The synchronous clear overrides the synchronous load. LEs in arithmetic mode can drive out registered and unregistered versions of the LUT output.

#### Clear & Preset Logic Control

Logic for the register's clear and preset signals is controlled by LAB-wide signals. The LE directly supports an asynchronous clear function. The Quartus II software Compiler can use a NOT-gate push-back technique to emulate an asynchronous preset. Moreover, the Quartus II software Compiler can use a programmable NOT-gate push-back technique to emulate simultaneous preset and clear or asynchronous load. However, this technique uses three additional LEs per register. All emulation is performed automatically when the design is compiled. Registers that emulate simultaneous preset and load will enter an unknown state upon power-up or when the chip-wide reset is asserted.

In addition to the two clear and preset modes, APEX 20K devices provide a chip-wide reset pin (DEV\_CLRn) that resets all registers in the device. Use of this pin is controlled through an option in the Quartus II software that is set before compilation. The chip-wide reset overrides all other control signals. Registers using an asynchronous preset are preset when the chip-wide reset is asserted; this effect results from the inversion technique used to implement the asynchronous preset.

#### FastTrack Interconnect

In the APEX 20K architecture, connections between LEs, ESBs, and I/O pins are provided by the FastTrack Interconnect. The FastTrack Interconnect is a series of continuous horizontal and vertical routing channels that traverse the device. This global routing structure provides predictable performance, even in complex designs. In contrast, the segmented routing in FPGAs requires switch matrices to connect a variable number of routing paths, increasing the delays between logic resources and reducing performance.

The FastTrack Interconnect consists of row and column interconnect channels that span the entire device. The row interconnect routes signals throughout a row of MegaLAB structures; the column interconnect routes signals throughout a column of MegaLAB structures. When using the row and column interconnect, an LE, IOE, or ESB can drive any other LE, IOE, or ESB in a device. See Figure 9.

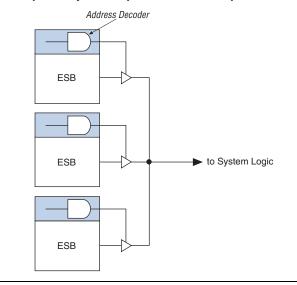

Figure 18. Deep Memory Block Implemented with Multiple ESBs

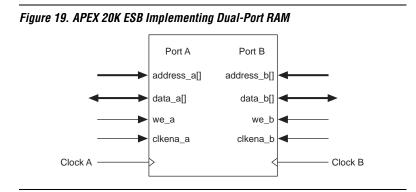

The ESB implements two forms of dual-port memory: read/write clock mode and input/output clock mode. The ESB can also be used for bidirectional, dual-port memory applications in which two ports read or write simultaneously. To implement this type of dual-port memory, two or four ESBs are used to support two simultaneous reads or writes. This functionality is shown in Figure 19.

APEX 20KE devices include an enhanced IOE, which drives the FastRow interconnect. The FastRow interconnect connects a column I/O pin directly to the LAB local interconnect within two MegaLAB structures. This feature provides fast setup times for pins that drive high fan-outs with complex logic, such as PCI designs. For fast bidirectional I/O timing, LE registers using local routing can improve setup times and OE timing. The APEX 20KE IOE also includes direct support for open-drain operation, giving faster clock-to-output for open-drain signals. Some programmable delays in the APEX 20KE IOE offer multiple levels of delay to fine-tune setup and hold time requirements. The Quartus II software compiler can set these delays automatically to minimize setup time while providing a zero hold time.

Table 11 describes the APEX 20KE programmable delays and their logic options in the Quartus II software.

| Table 11. APEX 20KE Programmable Delay Chains |                                         |  |  |  |  |  |

|-----------------------------------------------|-----------------------------------------|--|--|--|--|--|

| Programmable Delays                           | Quartus II Logic Option                 |  |  |  |  |  |

| Input Pin to Core Delay                       | Decrease input delay to internal cells  |  |  |  |  |  |

| Input Pin to Input Register Delay             | Decrease input delay to input registers |  |  |  |  |  |

| Core to Output Register Delay                 | Decrease input delay to output register |  |  |  |  |  |

| Output Register t <sub>CO</sub> Delay         | Increase delay to output pin            |  |  |  |  |  |

| Clock Enable Delay                            | Increase clock enable delay             |  |  |  |  |  |

The register in the APEX 20KE IOE can be programmed to power-up high or low after configuration is complete. If it is programmed to power-up low, an asynchronous clear can control the register. If it is programmed to power-up high, an asynchronous preset can control the register. Figure 26 shows how fast bidirectional I/O pins are implemented in APEX 20KE devices. This feature is useful for cases where the APEX 20KE device controls an active-low input or another device; it prevents inadvertent activation of the input upon power-up.

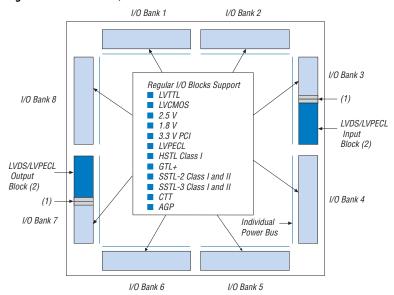

#### Figure 29. APEX 20KE I/O Banks

#### Notes to Figure 29:

- For more information on placing I/O pins in LVDS blocks, refer to the Guidelines for Using LVDS Blocks section in Application Note 120 (Using LVDS in APEX 20KE Devices).

- (2) If the LVDS input and output blocks are not used for LVDS, they can support all of the I/O standards and can be used as input, output, or bidirectional pins with V<sub>CCIO</sub> set to 3.3 V, 2.5 V, or 1.8 V.

#### Power Sequencing & Hot Socketing

Because APEX 20K and APEX 20KE devices can be used in a mixedvoltage environment, they have been designed specifically to tolerate any possible power-up sequence. Therefore, the  $V_{CCIO}$  and  $V_{CCINT}$  power supplies may be powered in any order.

For more information, please refer to the "Power Sequencing Considerations" section in the *Configuring APEX 20KE & APEX 20KC Devices* chapter of the *Configuration Devices Handbook*.

Signals can be driven into APEX 20K devices before and during power-up without damaging the device. In addition, APEX 20K devices do not drive out during power-up. Once operating conditions are reached and the device is configured, APEX 20K and APEX 20KE devices operate as specified by the user.

APEX 20KE devices also support the MultiVolt I/O interface feature. The APEX 20KE VCCINT pins must always be connected to a 1.8-V power supply. With a 1.8-V V<sub>CCINT</sub> level, input pins are 1.8-V, 2.5-V, and 3.3-V tolerant. The VCCIO pins can be connected to either a 1.8-V, 2.5-V, or 3.3-V power supply, depending on the I/O standard requirements. When the VCCIO pins are connected to a 1.8-V power supply, the output levels are compatible with 1.8-V systems. When VCCIO pins are connected to a 2.5-V power supply, the output levels are compatible with 2.5-V systems. When VCCIO pins are connected to a 3.3-V power supply, the output levels are sometime with 2.5-V systems. When VCCIO pins are connected to a 3.3-V power supply, the output high is 3.3 V and compatible with 3.3-V or 5.0-V systems. An APEX 20KE device is 5.0-V tolerant with the addition of a resistor.

#### Table 13 summarizes APEX 20KE MultiVolt I/O support.

| Table 13. APEX 20KE MultiVolt I/O Support     Note (1) |              |              |              |     |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |     |  |  |

|--------------------------------------------------------|--------------|--------------|--------------|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----|--|--|

| V <sub>CCIO</sub> (V)                                  |              | Input Siç    | jnals (V)    |     |              | Output S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ignals (V)   |     |  |  |

|                                                        | 1.8          | 2.5          | 3.3          | 5.0 | 1.8          | 2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.3          | 5.0 |  |  |

| 1.8                                                    | ~            | $\checkmark$ | <b>&gt;</b>  |     | $\checkmark$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |     |  |  |

| 2.5                                                    | $\checkmark$ | $\checkmark$ | $\checkmark$ |     |              | <ul> <li>Image: A start of the start of</li></ul> |              |     |  |  |

| 3.3                                                    | ~            | $\checkmark$ | >            | (2) |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>√</b> (3) |     |  |  |

#### Notes to Table 13:

The PCI clamping diode must be disabled to drive an input with voltages higher than V<sub>CCIO</sub>, except for the 5.0-V input case.

(2) An APEX 20KE device can be made 5.0-V tolerant with the addition of an external resistor. You also need a PCI clamp and series resistor.

(3) When V<sub>CCIO</sub> = 3.3 V, an APEX 20KE device can drive a 2.5-V device with 3.3-V tolerant inputs.

# ClockLock & ClockBoost Features

APEX 20K devices support the ClockLock and ClockBoost clock management features, which are implemented with PLLs. The ClockLock circuitry uses a synchronizing PLL that reduces the clock delay and skew within a device. This reduction minimizes clock-to-output and setup times while maintaining zero hold times. The ClockBoost circuitry, which provides a clock multiplier, allows the designer to enhance device area efficiency by sharing resources within the device. The ClockBoost circuitry allows the designer to distribute a low-speed clock and multiply that clock on-device. APEX 20K devices include a high-speed clock tree; unlike ASICs, the user does not have to design and optimize the clock tree. The ClockLock and ClockBoost features work in conjunction with the APEX 20K device's high-speed clock to provide significant improvements in system performance and band-width. Devices with an X-suffix on the ordering code include the ClockLock circuit.

The ClockLock and ClockBoost features in APEX 20K devices are enabled through the Quartus II software. External devices are not required to use these features.

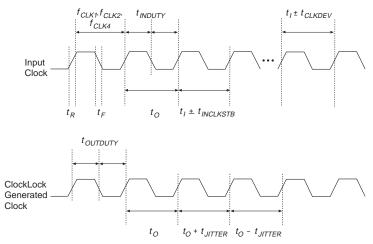

Figure 30. Specifications for the Incoming & Generated Clocks Note (1)

#### Note to Figure 30:

(1) The tI parameter refers to the nominal input clock period; the tO parameter refers to the nominal output clock period.

Table 15 summarizes the APEX 20K ClockLock and ClockBoost parameters for -1 speed-grade devices.

| Symbol                | Parameter                                                                                                                      | Min | Мах        | Unit |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------|-----|------------|------|

| f <sub>OUT</sub>      | Output frequency                                                                                                               | 25  | 180        | MHz  |

| f <sub>CLK1</sub> (1) | Input clock frequency (ClockBoost clock multiplication factor equals 1)                                                        | 25  | 180 (1)    | MHz  |

| f <sub>CLK2</sub>     | Input clock frequency (ClockBoost clock multiplication factor equals 2)                                                        | 16  | 90         | MHz  |

| f <sub>CLK4</sub>     | Input clock frequency (ClockBoost clock multiplication factor equals 4)                                                        | 10  | 48         | MHz  |

| toutduty              | Duty cycle for ClockLock/ClockBoost-generated<br>clock                                                                         | 40  | 60         | %    |

| f <sub>CLKDEV</sub>   | Input deviation from user specification in the<br>Quartus II software (ClockBoost clock<br>multiplication factor equals 1) (2) |     | 25,000 (3) | PPM  |

| t <sub>R</sub>        | Input rise time                                                                                                                |     | 5          | ns   |

| t <sub>F</sub>        | Input fall time                                                                                                                |     | 5          | ns   |

| t <sub>LOCK</sub>     | Time required for ClockLock/ClockBoost to acquire lock (4)                                                                     |     | 10         | μs   |

٦

All specifications are always representative of worst-case supply voltage and junction temperature conditions. All output-pin-timing specifications are reported for maximum driver strength.

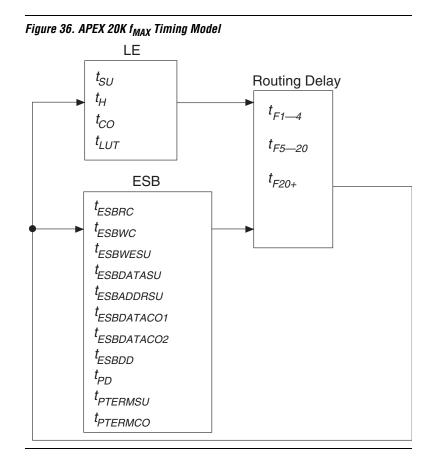

Figure 36 shows the  $f_{MAX}$  timing model for APEX 20K devices.

Figure 37 shows the  $f_{MAX}$  timing model for APEX 20KE devices. These parameters can be used to estimate  $f_{MAX}$  for multiple levels of logic. Quartus II software timing analysis should be used for more accurate timing information.

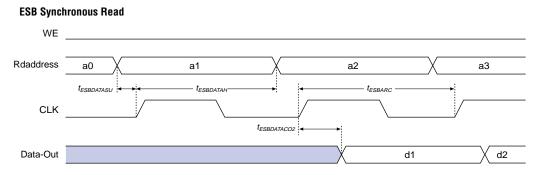

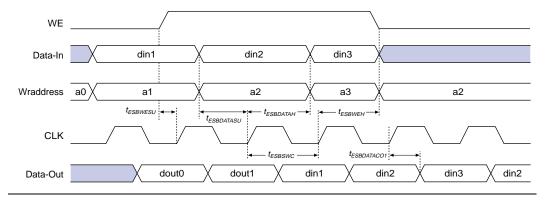

Figure 39. ESB Synchronous Timing Waveforms

#### ESB Synchronous Write (ESB Output Registers Used)

Figure 40 shows the timing model for bidirectional I/O pin timing.

| Table 31. APEX 20K f <sub>MAX</sub> Timing Parameters       (Part 2 of 2) |                                                    |  |  |  |  |  |

|---------------------------------------------------------------------------|----------------------------------------------------|--|--|--|--|--|

| Symbol                                                                    | Parameter                                          |  |  |  |  |  |

| t <sub>ESBDATACO2</sub>                                                   | ESB clock-to-output delay without output registers |  |  |  |  |  |

| t <sub>ESBDD</sub>                                                        | ESB data-in to data-out delay for RAM mode         |  |  |  |  |  |

| t <sub>PD</sub>                                                           | ESB macrocell input to non-registered output       |  |  |  |  |  |

| t <sub>PTERMSU</sub>                                                      | ESB macrocell register setup time before clock     |  |  |  |  |  |

| t <sub>PTERMCO</sub>                                                      | ESB macrocell register clock-to-output delay       |  |  |  |  |  |

| t <sub>F1-4</sub>                                                         | Fanout delay using local interconnect              |  |  |  |  |  |

| t <sub>F5-20</sub>                                                        | Fanout delay using MegaLab Interconnect            |  |  |  |  |  |

| t <sub>F20+</sub>                                                         | Fanout delay using FastTrack Interconnect          |  |  |  |  |  |

| t <sub>CH</sub>                                                           | Minimum clock high time from clock pin             |  |  |  |  |  |

| t <sub>CL</sub>                                                           | Minimum clock low time from clock pin              |  |  |  |  |  |

| t <sub>CLRP</sub>                                                         | LE clear pulse width                               |  |  |  |  |  |

| t <sub>PREP</sub>                                                         | LE preset pulse width                              |  |  |  |  |  |

| t <sub>ESBCH</sub>                                                        | Clock high time                                    |  |  |  |  |  |

| t <sub>ESBCL</sub>                                                        | Clock low time                                     |  |  |  |  |  |

| t <sub>ESBWP</sub>                                                        | Write pulse width                                  |  |  |  |  |  |

| t <sub>ESBRP</sub>                                                        | Read pulse width                                   |  |  |  |  |  |

#### Tables 32 and 33 describe APEX 20K external timing parameters.

| Table 32. APEX 20K External Timing Parameters       Note (1) |                                                         |  |  |  |  |  |

|--------------------------------------------------------------|---------------------------------------------------------|--|--|--|--|--|

| Symbol                                                       | Clock Parameter                                         |  |  |  |  |  |

| t <sub>INSU</sub>                                            | Setup time with global clock at IOE register            |  |  |  |  |  |

| t <sub>INH</sub>                                             | Hold time with global clock at IOE register             |  |  |  |  |  |

| t <sub>оитсо</sub>                                           | Clock-to-output delay with global clock at IOE register |  |  |  |  |  |

| Table 33. APEX 20K External Bidirectional Timing Parameters         Note (1) |                                                                                            |            |  |  |  |  |  |  |

|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------|--|--|--|--|--|--|

| Symbol                                                                       | Parameter                                                                                  | Conditions |  |  |  |  |  |  |

| t <sub>INSUBIDIR</sub>                                                       | Setup time for bidirectional pins with global clock at same-row or same-column LE register |            |  |  |  |  |  |  |

| t <sub>INHBIDIR</sub>                                                        | Hold time for bidirectional pins with global clock at same-row or same-column LE register  |            |  |  |  |  |  |  |

| <sup>t</sup> OUTCOBIDIR                                                      | Clock-to-output delay for bidirectional pins with global clock at IOE register             | C1 = 10 pF |  |  |  |  |  |  |

| t <sub>XZBIDIR</sub>                                                         | Synchronous IOE output buffer disable delay                                                | C1 = 10 pF |  |  |  |  |  |  |

| t <sub>ZXBIDIR</sub>                                                         | Synchronous IOE output buffer enable delay, slow slew rate = off                           | C1 = 10 pF |  |  |  |  |  |  |

Tables 40 through 42 show the  $f_{MAX}$  timing parameters for EP20K100, EP20K200, and EP20K400 APEX 20K devices.

| Symbol                  | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Units |

|-------------------------|----------------|-----|----------------|-----|----------------|-----|-------|

|                         | Min            | Max | Min            | Max | Min            | Max |       |

| t <sub>SU</sub>         | 0.5            |     | 0.6            |     | 0.8            |     | ns    |

| t <sub>H</sub>          | 0.7            |     | 0.8            |     | 1.0            |     | ns    |

| t <sub>CO</sub>         |                | 0.3 |                | 0.4 |                | 0.5 | ns    |

| t <sub>lut</sub>        |                | 0.8 |                | 1.0 |                | 1.3 | ns    |

| t <sub>ESBRC</sub>      |                | 1.7 |                | 2.1 |                | 2.4 | ns    |

| t <sub>ESBWC</sub>      |                | 5.7 |                | 6.9 |                | 8.1 | ns    |

| t <sub>ESBWESU</sub>    | 3.3            |     | 3.9            |     | 4.6            |     | ns    |

| t <sub>ESBDATASU</sub>  | 2.2            |     | 2.7            |     | 3.1            |     | ns    |

| t <sub>ESBDATAH</sub>   | 0.6            |     | 0.8            |     | 0.9            |     | ns    |

| t <sub>ESBADDRSU</sub>  | 2.4            |     | 2.9            |     | 3.3            |     | ns    |

| t <sub>ESBDATACO1</sub> |                | 1.3 |                | 1.6 |                | 1.8 | ns    |

| t <sub>ESBDATACO2</sub> |                | 2.6 |                | 3.1 |                | 3.6 | ns    |

| t <sub>ESBDD</sub>      |                | 2.5 |                | 3.3 |                | 3.6 | ns    |

| t <sub>PD</sub>         |                | 2.5 |                | 3.0 |                | 3.6 | ns    |

| <b>TERMSU</b>           | 2.3            |     | 2.6            |     | 3.2            |     | ns    |

| t <sub>PTERMCO</sub>    |                | 1.5 |                | 1.8 |                | 2.1 | ns    |

| t <sub>F1-4</sub>       |                | 0.5 |                | 0.6 |                | 0.7 | ns    |

| t <sub>F5-20</sub>      |                | 1.6 |                | 1.7 |                | 1.8 | ns    |

| t <sub>F20+</sub>       |                | 2.2 |                | 2.2 |                | 2.3 | ns    |

| t <sub>CH</sub>         | 2.0            |     | 2.5            |     | 3.0            |     | ns    |

| t <sub>CL</sub>         | 2.0            |     | 2.5            |     | 3.0            |     | ns    |

| t <sub>CLRP</sub>       | 0.3            |     | 0.4            |     | 0.4            |     | ns    |

| t <sub>PREP</sub>       | 0.5            |     | 0.5            |     | 0.5            |     | ns    |

| t <sub>ESBCH</sub>      | 2.0            |     | 2.5            |     | 3.0            |     | ns    |

| t <sub>ESBCL</sub>      | 2.0            |     | 2.5            |     | 3.0            |     | ns    |

| t <sub>ESBWP</sub>      | 1.6            |     | 1.9            |     | 2.2            |     | ns    |

| t <sub>ESBRP</sub>      | 1.0            |     | 1.3            |     | 1.4            |     | ns    |

Tables 67 through 72 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K160E APEX 20KE devices.

| Table 67. EP20K160E f <sub>MAX</sub> LE Timing Microparameters |      |      |      |      |      |      |    |  |  |

|----------------------------------------------------------------|------|------|------|------|------|------|----|--|--|

| Symbol                                                         | -    | 1    | -2   |      | -    | Unit |    |  |  |

|                                                                | Min  | Max  | Min  | Max  | Min  | Max  |    |  |  |

| t <sub>SU</sub>                                                | 0.22 |      | 0.24 |      | 0.26 |      | ns |  |  |

| t <sub>H</sub>                                                 | 0.22 |      | 0.24 |      | 0.26 |      | ns |  |  |

| t <sub>CO</sub>                                                |      | 0.25 |      | 0.31 |      | 0.35 | ns |  |  |

| t <sub>LUT</sub>                                               |      | 0.69 |      | 0.88 |      | 1.12 | ns |  |  |

| Symbol                  | -1    |      | -     | 2    | -3   |      | Unit |

|-------------------------|-------|------|-------|------|------|------|------|

|                         | Min   | Max  | Min   | Max  | Min  | Max  |      |

| t <sub>ESBARC</sub>     |       | 1.68 |       | 2.06 |      | 2.24 | ns   |

| t <sub>ESBSRC</sub>     |       | 2.27 |       | 2.77 |      | 3.18 | ns   |

| t <sub>ESBAWC</sub>     |       | 3.10 |       | 3.86 |      | 4.50 | ns   |

| t <sub>ESBSWC</sub>     |       | 2.90 |       | 3.67 |      | 4.21 | ns   |

| t <sub>ESBWASU</sub>    | 0.55  |      | 0.67  |      | 0.74 |      | ns   |

| t <sub>ESBWAH</sub>     | 0.36  |      | 0.46  |      | 0.48 |      | ns   |

| t <sub>ESBWDSU</sub>    | 0.69  |      | 0.83  |      | 0.95 |      | ns   |

| t <sub>ESBWDH</sub>     | 0.36  |      | 0.46  |      | 0.48 |      | ns   |

| t <sub>ESBRASU</sub>    | 1.61  |      | 1.90  |      | 2.09 |      | ns   |

| t <sub>ESBRAH</sub>     | 0.00  |      | 0.00  |      | 0.01 |      | ns   |

| t <sub>ESBWESU</sub>    | 1.42  |      | 1.71  |      | 2.01 |      | ns   |

| t <sub>ESBWEH</sub>     | 0.00  |      | 0.00  |      | 0.00 |      | ns   |

| t <sub>ESBDATASU</sub>  | -0.06 |      | -0.07 |      | 0.05 |      | ns   |

| t <sub>ESBDATAH</sub>   | 0.13  |      | 0.13  |      | 0.13 |      | ns   |

| t <sub>ESBWADDRSU</sub> | 0.11  |      | 0.13  |      | 0.31 |      | ns   |

| t <sub>ESBRADDRSU</sub> | 0.18  |      | 0.23  |      | 0.39 |      | ns   |

| t <sub>ESBDATACO1</sub> |       | 1.09 |       | 1.35 |      | 1.51 | ns   |

| t <sub>ESBDATACO2</sub> |       | 2.19 |       | 2.75 |      | 3.22 | ns   |

| t <sub>ESBDD</sub>      |       | 2.75 |       | 3.41 |      | 4.03 | ns   |

| t <sub>PD</sub>         |       | 1.58 |       | 1.97 |      | 2.33 | ns   |

| t <sub>PTERMSU</sub>    | 1.00  |      | 1.22  |      | 1.51 |      | ns   |

| t <sub>PTERMCO</sub>    |       | 1.10 |       | 1.37 |      | 1.09 | ns   |

| Table 75. EP20K200E f <sub>MAX</sub> Routing Delays |     |          |     |      |     |      |    |  |  |  |

|-----------------------------------------------------|-----|----------|-----|------|-----|------|----|--|--|--|

| Symbol                                              | -   | -1 -2 -3 |     |      |     |      |    |  |  |  |

|                                                     | Min | Max      | Min | Max  | Min | Max  |    |  |  |  |

| t <sub>F1-4</sub>                                   |     | 0.25     |     | 0.27 |     | 0.29 | ns |  |  |  |

| t <sub>F5-20</sub>                                  |     | 1.02     |     | 1.20 |     | 1.41 | ns |  |  |  |

| t <sub>F20+</sub>                                   |     | 1.99     |     | 2.23 |     | 2.53 | ns |  |  |  |

| Symbol                  | -1   |      | -2   |      | -3   |      | Unit |

|-------------------------|------|------|------|------|------|------|------|

|                         | Min  | Max  | Min  | Max  | Min  | Max  |      |

| t <sub>ESBARC</sub>     |      | 1.79 |      | 2.44 |      | 3.25 | ns   |

| t <sub>ESBSRC</sub>     |      | 2.40 |      | 3.12 |      | 4.01 | ns   |

| t <sub>ESBAWC</sub>     |      | 3.41 |      | 4.65 |      | 6.20 | ns   |

| t <sub>ESBSWC</sub>     |      | 3.68 |      | 4.68 |      | 5.93 | ns   |

| t <sub>ESBWASU</sub>    | 1.55 |      | 2.12 |      | 2.83 |      | ns   |

| t <sub>ESBWAH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>ESBWDSU</sub>    | 1.71 |      | 2.33 |      | 3.11 |      | ns   |

| t <sub>ESBWDH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>ESBRASU</sub>    | 1.72 |      | 2.34 |      | 3.13 |      | ns   |

| t <sub>ESBRAH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>ESBWESU</sub>    | 1.63 |      | 2.36 |      | 3.28 |      | ns   |

| t <sub>ESBWEH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns   |

| t <sub>ESBDATASU</sub>  | 0.07 |      | 0.39 |      | 0.80 |      | ns   |

| t <sub>ESBDATAH</sub>   | 0.13 |      | 0.13 |      | 0.13 |      | ns   |

| t <sub>ESBWADDRSU</sub> | 0.27 |      | 0.67 |      | 1.17 |      | ns   |

| t <sub>ESBRADDRSU</sub> | 0.34 |      | 0.75 |      | 1.28 |      | ns   |

| t <sub>ESBDATACO1</sub> |      | 1.03 |      | 1.20 |      | 1.40 | ns   |

| t <sub>ESBDATACO2</sub> |      | 2.33 |      | 3.18 |      | 4.24 | ns   |

| t <sub>ESBDD</sub>      |      | 3.41 |      | 4.65 |      | 6.20 | ns   |

| t <sub>PD</sub>         |      | 1.68 |      | 2.29 |      | 3.06 | ns   |

| t <sub>PTERMSU</sub>    | 0.96 |      | 1.48 |      | 2.14 |      | ns   |

| t <sub>PTERMCO</sub>    |      | 1.05 |      | 1.22 |      | 1.42 | ns   |

| Table 81. EP20K300E f <sub>MAX</sub> Routing Delays |     |      |     |      |     |      |      |  |

|-----------------------------------------------------|-----|------|-----|------|-----|------|------|--|

| Symbol                                              | -1  |      | -2  |      | -;  | 3    | Unit |  |

|                                                     | Min | Max  | Min | Max  | Min | Мах  |      |  |

| t <sub>F1-4</sub>                                   |     | 0.22 |     | 0.24 |     | 0.26 | ns   |  |

| t <sub>F5-20</sub>                                  |     | 1.33 |     | 1.43 |     | 1.58 | ns   |  |

| t <sub>F20+</sub>                                   |     | 3.63 |     | 3.93 |     | 4.35 | ns   |  |

#### **Altera Corporation**

Tables 85 through 90 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K400E APEX 20KE devices.

| Table 85. EP20K400E f <sub>MAX</sub> LE Timing Microparameters |         |          |        |          |         |      |    |  |

|----------------------------------------------------------------|---------|----------|--------|----------|---------|------|----|--|

| Symbol                                                         | -1 Spee | ed Grade | -2 Spe | ed Grade | -3 Spee | Unit |    |  |

|                                                                | Min     | Max      | Min    | Max      | Min     | Max  |    |  |

| t <sub>SU</sub>                                                | 0.23    |          | 0.23   |          | 0.23    |      | ns |  |

| t <sub>H</sub>                                                 | 0.23    |          | 0.23   |          | 0.23    |      | ns |  |

| t <sub>CO</sub>                                                |         | 0.25     |        | 0.29     |         | 0.32 | ns |  |

| t <sub>LUT</sub>                                               |         | 0.70     |        | 0.83     |         | 1.01 | ns |  |

| Symbol                  | -1 Speed Grade |      | -2 Speed Grade |      | -3 Spee | d Grade | Unit |

|-------------------------|----------------|------|----------------|------|---------|---------|------|

|                         | Min            | Max  | Min            | Max  | Min     | Max     |      |

| t <sub>ESBARC</sub>     |                | 1.67 |                | 1.91 |         | 1.99    | ns   |

| t <sub>ESBSRC</sub>     |                | 2.30 |                | 2.66 |         | 2.93    | ns   |

| t <sub>ESBAWC</sub>     |                | 3.09 |                | 3.58 |         | 3.99    | ns   |

| t <sub>ESBSWC</sub>     |                | 3.01 |                | 3.65 |         | 4.05    | ns   |

| t <sub>ESBWASU</sub>    | 0.54           |      | 0.63           |      | 0.65    |         | ns   |

| t <sub>ESBWAH</sub>     | 0.36           |      | 0.43           |      | 0.42    |         | ns   |

| t <sub>ESBWDSU</sub>    | 0.69           |      | 0.77           |      | 0.84    |         | ns   |

| t <sub>ESBWDH</sub>     | 0.36           |      | 0.43           |      | 0.42    |         | ns   |

| t <sub>ESBRASU</sub>    | 1.61           |      | 1.77           |      | 1.86    |         | ns   |

| t <sub>ESBRAH</sub>     | 0.00           |      | 0.00           |      | 0.01    |         | ns   |

| t <sub>ESBWESU</sub>    | 1.35           |      | 1.47           |      | 1.61    |         | ns   |

| t <sub>ESBWEH</sub>     | 0.00           |      | 0.00           |      | 0.00    |         | ns   |

| t <sub>ESBDATASU</sub>  | -0.18          |      | -0.30          |      | -0.27   |         | ns   |

| t <sub>ESBDATAH</sub>   | 0.13           |      | 0.13           |      | 0.13    |         | ns   |

| t <sub>ESBWADDRSU</sub> | -0.02          |      | -0.11          |      | -0.03   |         | ns   |

| t <sub>ESBRADDRSU</sub> | 0.06           |      | -0.01          |      | -0.05   |         | ns   |

| t <sub>ESBDATACO1</sub> |                | 1.16 |                | 1.40 |         | 1.54    | ns   |

| t <sub>ESBDATACO2</sub> |                | 2.18 |                | 2.55 |         | 2.85    | ns   |

| t <sub>ESBDD</sub>      |                | 2.73 |                | 3.17 |         | 3.58    | ns   |

| t <sub>PD</sub>         |                | 1.57 |                | 1.83 |         | 2.07    | ns   |

| t <sub>PTERMSU</sub>    | 0.92           |      | 0.99           |      | 1.18    |         | ns   |

| t <sub>PTERMCO</sub>    |                | 1.18 |                | 1.43 |         | 1.17    | ns   |

| Symbol                  | -1 Speed Grade |      | -2 Speed Grade |      | -3 Speed Grade |      | Unit |

|-------------------------|----------------|------|----------------|------|----------------|------|------|

|                         | Min            | Max  | Min            | Max  | Min            | Max  |      |

| t <sub>ESBARC</sub>     |                | 1.78 |                | 2.02 |                | 1.95 | ns   |

| t <sub>ESBSRC</sub>     |                | 2.52 |                | 2.91 |                | 3.14 | ns   |

| t <sub>ESBAWC</sub>     |                | 3.52 |                | 4.11 |                | 4.40 | ns   |

| t <sub>ESBSWC</sub>     |                | 3.23 |                | 3.84 |                | 4.16 | ns   |

| t <sub>ESBWASU</sub>    | 0.62           |      | 0.67           |      | 0.61           |      | ns   |

| t <sub>ESBWAH</sub>     | 0.41           |      | 0.55           |      | 0.55           |      | ns   |

| t <sub>ESBWDSU</sub>    | 0.77           |      | 0.79           |      | 0.81           |      | ns   |

| t <sub>ESBWDH</sub>     | 0.41           |      | 0.55           |      | 0.55           |      | ns   |

| t <sub>ESBRASU</sub>    | 1.74           |      | 1.92           |      | 1.85           |      | ns   |

| t <sub>ESBRAH</sub>     | 0.00           |      | 0.01           |      | 0.23           |      | ns   |

| t <sub>ESBWESU</sub>    | 2.07           |      | 2.28           |      | 2.41           |      | ns   |

| t <sub>ESBWEH</sub>     | 0.00           |      | 0.00           |      | 0.00           |      | ns   |

| t <sub>ESBDATASU</sub>  | 0.25           |      | 0.27           |      | 0.29           |      | ns   |

| t <sub>ESBDATAH</sub>   | 0.13           |      | 0.13           |      | 0.13           |      | ns   |

| t <sub>ESBWADDRSU</sub> | 0.11           |      | 0.04           |      | 0.11           |      | ns   |

| t <sub>ESBRADDRSU</sub> | 0.14           |      | 0.11           |      | 0.16           |      | ns   |

| t <sub>ESBDATACO1</sub> |                | 1.29 |                | 1.50 |                | 1.63 | ns   |

| t <sub>ESBDATACO2</sub> |                | 2.55 |                | 2.99 |                | 3.22 | ns   |

| t <sub>ESBDD</sub>      |                | 3.12 |                | 3.57 |                | 3.85 | ns   |

| t <sub>PD</sub>         |                | 1.84 |                | 2.13 |                | 2.32 | ns   |

| t <sub>PTERMSU</sub>    | 1.08           |      | 1.19           |      | 1.32           |      | ns   |

| t <sub>PTERMCO</sub>    |                | 1.31 |                | 1.53 |                | 1.66 | ns   |

Г

٦

| Table 108. EP20K1500E External Bidirectional Timing Parameters |                |      |         |         |         |      |    |

|----------------------------------------------------------------|----------------|------|---------|---------|---------|------|----|

| Symbol                                                         | -1 Speed Grade |      | -2 Spee | d Grade | -3 Spee | Unit |    |

|                                                                | Min            | Мах  | Min     | Max     | Min     | Max  |    |

| t <sub>insubidir</sub>                                         | 3.47           |      | 3.68    |         | 3.99    |      | ns |

| t <sub>inhbidir</sub>                                          | 0.00           |      | 0.00    |         | 0.00    |      | ns |

| t <sub>outcobidir</sub>                                        | 2.00           | 6.18 | 2.00    | 6.81    | 2.00    | 7.36 | ns |

| t <sub>XZBIDIR</sub>                                           |                | 6.91 |         | 7.62    |         | 8.38 | ns |

| t <sub>zxbidir</sub>                                           |                | 6.91 |         | 7.62    |         | 8.38 | ns |

| t <sub>insubidirpll</sub>                                      | 3.05           |      | 3.26    |         |         |      | ns |

| t <sub>inhbidirpll</sub>                                       | 0.00           |      | 0.00    |         |         |      | ns |

| t <sub>outcobidirpll</sub>                                     | 0.50           | 2.67 | 0.50    | 2.99    |         |      | ns |

| t <sub>xzbidirpll</sub>                                        |                | 3.41 |         | 3.80    |         |      | ns |

| t <sub>ZXBIDIRPLL</sub>                                        |                | 3.41 |         | 3.80    |         |      | ns |

Tables 109 and 110 show selectable I/O standard input and output delays for APEX 20KE devices. If you select an I/O standard input or output delay other than LVCMOS, add or subtract the selected speed grade to or from the LVCMOS value.

| Table 109. Selectable I/O Standard Input Delays |         |                |     |                |     |         |      |

|-------------------------------------------------|---------|----------------|-----|----------------|-----|---------|------|

| Symbol                                          | -1 Spee | -1 Speed Grade |     | -2 Speed Grade |     | d Grade | Unit |

|                                                 | Min     | Max            | Min | Max            | Min | Max     | Min  |

| LVCMOS                                          |         | 0.00           |     | 0.00           |     | 0.00    | ns   |

| LVTTL                                           |         | 0.00           |     | 0.00           |     | 0.00    | ns   |

| 2.5 V                                           |         | 0.00           |     | 0.04           |     | 0.05    | ns   |

| 1.8 V                                           |         | -0.11          |     | 0.03           |     | 0.04    | ns   |

| PCI                                             |         | 0.01           |     | 0.09           |     | 0.10    | ns   |

| GTL+                                            |         | -0.24          |     | -0.23          |     | -0.19   | ns   |

| SSTL-3 Class I                                  |         | -0.32          |     | -0.21          |     | -0.47   | ns   |

| SSTL-3 Class II                                 |         | -0.08          |     | 0.03           |     | -0.23   | ns   |

| SSTL-2 Class I                                  |         | -0.17          |     | -0.06          |     | -0.32   | ns   |

| SSTL-2 Class II                                 |         | -0.16          |     | -0.05          |     | -0.31   | ns   |

| LVDS                                            |         | -0.12          |     | -0.12          |     | -0.12   | ns   |

| CTT                                             |         | 0.00           |     | 0.00           |     | 0.00    | ns   |

| AGP                                             |         | 0.00           |     | 0.00           |     | 0.00    | ns   |

Г

SRAM configuration elements allow APEX 20K devices to be reconfigured in-circuit by loading new configuration data into the device. Real-time reconfiguration is performed by forcing the device into command mode with a device pin, loading different configuration data, reinitializing the device, and resuming usermode operation. In-field upgrades can be performed by distributing new configuration files.

### **Configuration Schemes**

The configuration data for an APEX 20K device can be loaded with one of five configuration schemes (see Table 111), chosen on the basis of the target application. An EPC2 or EPC16 configuration device, intelligent controller, or the JTAG port can be used to control the configuration of an APEX 20K device. When a configuration device is used, the system can configure automatically at system power-up.

Multiple APEX 20K devices can be configured in any of five configuration schemes by connecting the configuration enable (nCE) and configuration enable output (nCEO) pins on each device.

| Table 111. Data Sources for Configuration |                                                                     |  |  |  |  |

|-------------------------------------------|---------------------------------------------------------------------|--|--|--|--|

| Configuration Scheme                      | Data Source                                                         |  |  |  |  |

| Configuration device                      | EPC1, EPC2, EPC16 configuration devices                             |  |  |  |  |

| Passive serial (PS)                       | MasterBlaster or ByteBlasterMV download cable or serial data source |  |  |  |  |

| Passive parallel asynchronous (PPA)       | Parallel data source                                                |  |  |  |  |

| Passive parallel synchronous (PPS)        | Parallel data source                                                |  |  |  |  |

| JTAG                                      | MasterBlaster or ByteBlasterMV download cable or a microprocessor   |  |  |  |  |

|                                           | with a Jam or JBC File                                              |  |  |  |  |

For more information on configuration, see *Application Note* 116 (*Configuring APEX 20K, FLEX 10K, & FLEX 6000 Devices.*)

## **Device Pin-Outs**

See the Altera web site (http://www.altera.com) or the *Altera Digital Library* for pin-out information