# E·XFL

### Intel - EP20K60EFC144-1X Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 2560                                                        |

| Number of Logic Elements/Cells | 2560                                                        |

| Total RAM Bits                 | 32768                                                       |

| Number of I/O                  | 93                                                          |

| Number of Gates                | 162000                                                      |

| Voltage - Supply               | 1.71V ~ 1.89V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 144-BGA                                                     |

| Supplier Device Package        | 144-FBGA (13x13)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep20k60efc144-1x |

|                                |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

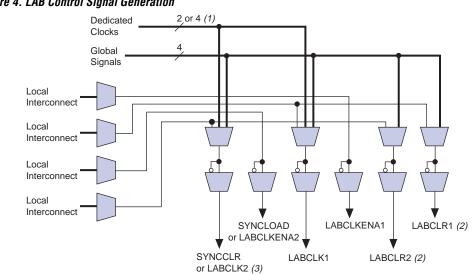

Each LAB contains dedicated logic for driving control signals to its LEs and ESBs. The control signals include clock, clock enable, asynchronous clear, asynchronous preset, asynchronous load, synchronous clear, and synchronous load signals. A maximum of six control signals can be used at a time. Although synchronous load and clear signals are generally used when implementing counters, they can also be used with other functions.

Each LAB can use two clocks and two clock enable signals. Each LAB's clock and clock enable signals are linked (e.g., any LE in a particular LAB using CLK1 will also use CLKENA1). LEs with the same clock but different clock enable signals either use both clock signals in one LAB or are placed into separate LABs.

If both the rising and falling edges of a clock are used in a LAB, both LABwide clock signals are used.

The LAB-wide control signals can be generated from the LAB local interconnect, global signals, and dedicated clock pins. The inherent low skew of the FastTrack Interconnect enables it to be used for clock distribution. Figure 4 shows the LAB control signal generation circuit.

#### Figure 4. LAB Control Signal Generation

#### Notes to Figure 4:

- APEX 20KE devices have four dedicated clocks. (1)

- The LABCLR1 and LABCLR2 signals also control asynchronous load and asynchronous preset for LEs within the (2) LAB.

- (3)The SYNCCLR signal can be generated by the local interconnect or global signals.

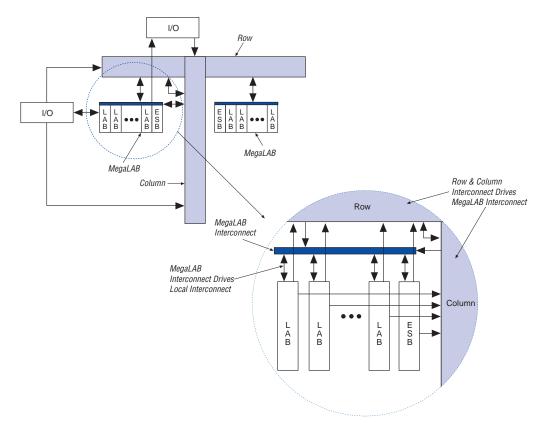

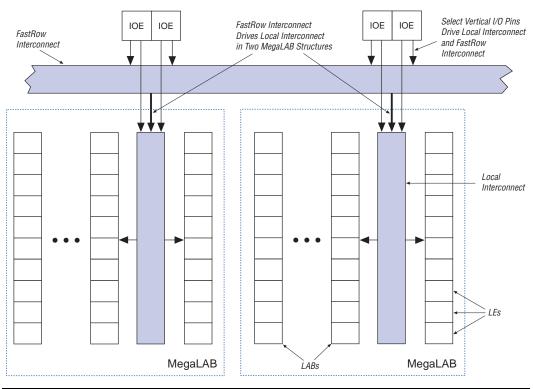

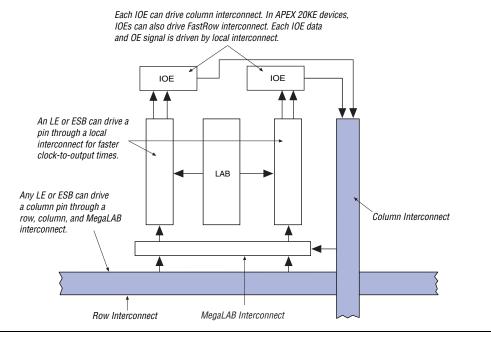

Figure 10. FastTrack Connection to Local Interconnect

Figure 12. APEX 20KE FastRow Interconnect

Table 9 summarizes how various elements of the APEX 20K architecture drive each other.

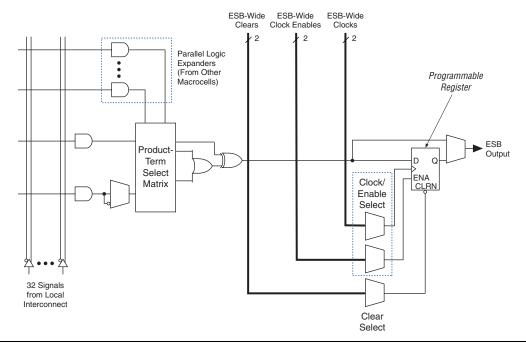

#### Figure 14. APEX 20K Macrocell

For registered functions, each macrocell register can be programmed individually to implement D, T, JK, or SR operation with programmable clock control. The register can be bypassed for combinatorial operation. During design entry, the designer specifies the desired register type; the Quartus II software then selects the most efficient register operation for each registered function to optimize resource utilization. The Quartus II software or other synthesis tools can also select the most efficient register operation automatically when synthesizing HDL designs.

Each programmable register can be clocked by one of two ESB-wide clocks. The ESB-wide clocks can be generated from device dedicated clock pins, global signals, or local interconnect. Each clock also has an associated clock enable, generated from the local interconnect. The clock and clock enable signals are related for a particular ESB; any macrocell using a clock also uses the associated clock enable.

If both the rising and falling edges of a clock are used in an ESB, both ESB-wide clock signals are used.

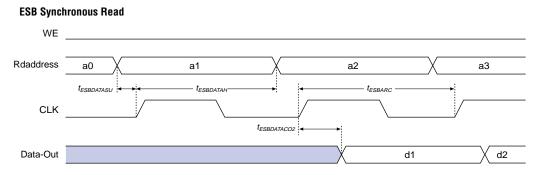

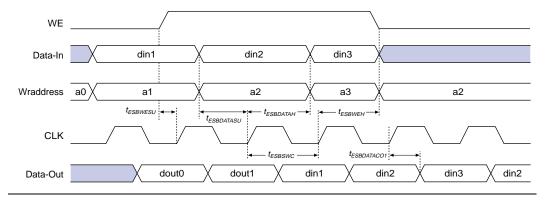

ESBs can implement synchronous RAM, which is easier to use than asynchronous RAM. A circuit using asynchronous RAM must generate the RAM write enable (WE) signal, while ensuring that its data and address signals meet setup and hold time specifications relative to the WE signal. In contrast, the ESB's synchronous RAM generates its own WE signal and is self-timed with respect to the global clock. Circuits using the ESB's selftimed RAM must only meet the setup and hold time specifications of the global clock.

ESB inputs are driven by the adjacent local interconnect, which in turn can be driven by the MegaLAB or FastTrack Interconnect. Because the ESB can be driven by the local interconnect, an adjacent LE can drive it directly for fast memory access. ESB outputs drive the MegaLAB and FastTrack Interconnect. In addition, ten ESB outputs, nine of which are unique output lines, drive the local interconnect for fast connection to adjacent LEs or for fast feedback product-term logic.

When implementing memory, each ESB can be configured in any of the following sizes:  $128 \times 16$ ,  $256 \times 8$ ,  $512 \times 4$ ,  $1,024 \times 2$ , or  $2,048 \times 1$ . By combining multiple ESBs, the Quartus II software implements larger memory blocks automatically. For example, two  $128 \times 16$  RAM blocks can be combined to form a  $128 \times 32$  RAM block, and two  $512 \times 4$  RAM blocks can be combined to form a  $512 \times 8$  RAM block. Memory performance does not degrade for memory blocks up to 2,048 words deep. Each ESB can implement a 2,048-word-deep memory; the ESBs are used in parallel, eliminating the need for any external control logic and its associated delays.

To create a high-speed memory block that is more than 2,048 words deep, ESBs drive tri-state lines. Each tri-state line connects all ESBs in a column of MegaLAB structures, and drives the MegaLAB interconnect and row and column FastTrack Interconnect throughout the column. Each ESB incorporates a programmable decoder to activate the tri-state driver appropriately. For instance, to implement 8,192-word-deep memory, four ESBs are used. Eleven address lines drive the ESB memory, and two more drive the tri-state decoder. Depending on which 2,048-word memory page is selected, the appropriate ESB driver is turned on, driving the output to the tri-state line. The Quartus II software automatically combines ESBs with tri-state lines to form deeper memory blocks. The internal tri-state control logic is designed to avoid internal contention and floating lines. See Figure 18.

Figure 28 shows how a column IOE connects to the interconnect.

#### Figure 28. Column IOE Connection to the Interconnect

#### **Dedicated Fast I/O Pins**

APEX 20KE devices incorporate an enhancement to support bidirectional pins with high internal fanout such as PCI control signals. These pins are called Dedicated Fast I/O pins (FAST1, FAST2, FAST3, and FAST4) and replace dedicated inputs. These pins can be used for fast clock, clear, or high fanout logic signal distribution. They also can drive out. The Dedicated Fast I/O pin data output and tri-state control are driven by local interconnect from the adjacent MegaLAB for high speed.

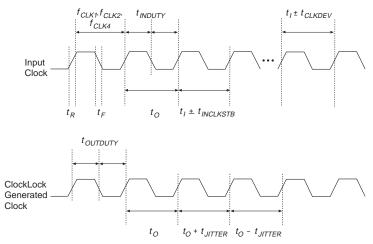

Figure 30. Specifications for the Incoming & Generated Clocks Note (1)

#### Note to Figure 30:

(1) The tI parameter refers to the nominal input clock period; the tO parameter refers to the nominal output clock period.

Table 15 summarizes the APEX 20K ClockLock and ClockBoost parameters for -1 speed-grade devices.

| Symbol                | Parameter                                                                                                                      | Min | Мах        | Unit |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------|-----|------------|------|

| f <sub>OUT</sub>      | Output frequency                                                                                                               | 25  | 180        | MHz  |

| f <sub>CLK1</sub> (1) | Input clock frequency (ClockBoost clock multiplication factor equals 1)                                                        | 25  | 180 (1)    | MHz  |

| f <sub>CLK2</sub>     | Input clock frequency (ClockBoost clock multiplication factor equals 2)                                                        | 16  | 90         | MHz  |

| f <sub>CLK4</sub>     | Input clock frequency (ClockBoost clock multiplication factor equals 4)                                                        | 10  | 48         | MHz  |

| toutduty              | Duty cycle for ClockLock/ClockBoost-generated<br>clock                                                                         | 40  | 60         | %    |

| f <sub>CLKDEV</sub>   | Input deviation from user specification in the<br>Quartus II software (ClockBoost clock<br>multiplication factor equals 1) (2) |     | 25,000 (3) | PPM  |

| t <sub>R</sub>        | Input rise time                                                                                                                |     | 5          | ns   |

| t <sub>F</sub>        | Input fall time                                                                                                                |     | 5          | ns   |

| t <sub>LOCK</sub>     | Time required for ClockLock/ClockBoost to acquire lock (4)                                                                     |     | 10         | μs   |

٦

#### Notes to Table 16:

- (1) To implement the ClockLock and ClockBoost circuitry with the Quartus II software, designers must specify the input frequency. The Quartus II software tunes the PLL in the ClockLock and ClockBoost circuitry to this frequency. The *f<sub>CLKDEV</sub>* parameter specifies how much the incoming clock can differ from the specified frequency during device operation. Simulation does not reflect this parameter.

- (2) Twenty-five thousand parts per million (PPM) equates to 2.5% of input clock period.

- (3) During device configuration, the ClockLock and ClockBoost circuitry is configured before the rest of the device. If the incoming clock is supplied during configuration, the ClockLock and ClockBoost circuitry locks during configuration because the t<sub>LOCK</sub> value is less than the time required for configuration.

- (4) The  $t_{IITTER}$  specification is measured under long-term observation.

Tables 17 and 18 summarize the ClockLock and ClockBoost parameters for APEX 20KE devices.

| Table 17. APEX 20KE ClockLock & ClockBoost Parameters Note (1) |                                                              |            |     |     |                        |                  |  |  |  |  |

|----------------------------------------------------------------|--------------------------------------------------------------|------------|-----|-----|------------------------|------------------|--|--|--|--|

| Symbol                                                         | Parameter                                                    | Conditions | Min | Тур | Мах                    | Unit             |  |  |  |  |

| t <sub>R</sub>                                                 | Input rise time                                              |            |     |     | 5                      | ns               |  |  |  |  |

| t <sub>F</sub>                                                 | Input fall time                                              |            |     |     | 5                      | ns               |  |  |  |  |

| t <sub>INDUTY</sub>                                            | Input duty cycle                                             |            | 40  |     | 60                     | %                |  |  |  |  |

| t <sub>INJITTER</sub>                                          | Input jitter peak-to-peak                                    |            |     |     | 2% of input<br>period  | peak-to-<br>peak |  |  |  |  |

| t <sub>OUTJITTER</sub>                                         | Jitter on ClockLock or ClockBoost-<br>generated clock        |            |     |     | 0.35% of output period | RMS              |  |  |  |  |

| t <sub>OUTDUTY</sub>                                           | Duty cycle for ClockLock or<br>ClockBoost-generated clock    |            | 45  |     | 55                     | %                |  |  |  |  |

| t <sub>LOCK</sub> (2) <sub>,</sub> (3)                         | Time required for ClockLock or<br>ClockBoost to acquire lock |            |     |     | 40                     | μs               |  |  |  |  |

| Device     | IDCODE (32 Bits) (1) |                       |                                    |                      |  |  |  |  |  |  |

|------------|----------------------|-----------------------|------------------------------------|----------------------|--|--|--|--|--|--|

|            | Version<br>(4 Bits)  | Part Number (16 Bits) | Manufacturer<br>Identity (11 Bits) | <b>1 (1 Bit)</b> (2) |  |  |  |  |  |  |

| EP20K30E   | 0000                 | 1000 0000 0011 0000   | 000 0110 1110                      | 1                    |  |  |  |  |  |  |

| EP20K60E   | 0000                 | 1000 0000 0110 0000   | 000 0110 1110                      | 1                    |  |  |  |  |  |  |

| EP20K100   | 0000                 | 0000 0100 0001 0110   | 000 0110 1110                      | 1                    |  |  |  |  |  |  |

| EP20K100E  | 0000                 | 1000 0001 0000 0000   | 000 0110 1110                      | 1                    |  |  |  |  |  |  |

| EP20K160E  | 0000                 | 1000 0001 0110 0000   | 000 0110 1110                      | 1                    |  |  |  |  |  |  |

| EP20K200   | 0000                 | 0000 1000 0011 0010   | 000 0110 1110                      | 1                    |  |  |  |  |  |  |

| EP20K200E  | 0000                 | 1000 0010 0000 0000   | 000 0110 1110                      | 1                    |  |  |  |  |  |  |

| EP20K300E  | 0000                 | 1000 0011 0000 0000   | 000 0110 1110                      | 1                    |  |  |  |  |  |  |

| EP20K400   | 0000                 | 0001 0110 0110 0100   | 000 0110 1110                      | 1                    |  |  |  |  |  |  |

| EP20K400E  | 0000                 | 1000 0100 0000 0000   | 000 0110 1110                      | 1                    |  |  |  |  |  |  |

| EP20K600E  | 0000                 | 1000 0110 0000 0000   | 000 0110 1110                      | 1                    |  |  |  |  |  |  |

| EP20K1000E | 0000                 | 1001 0000 0000 0000   | 000 0110 1110                      | 1                    |  |  |  |  |  |  |

#### 11- 04 00 04 4 ~

Notes to Table 21:

The most significant bit (MSB) is on the left. (1)

(2) The IDCODE's least significant bit (LSB) is always 1.

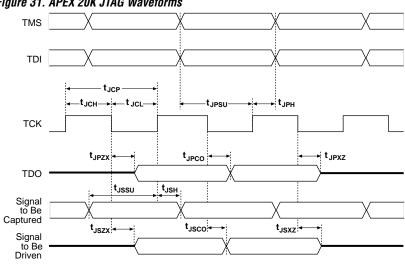

#### Figure 31 shows the timing requirements for the JTAG signals.

**Altera Corporation**

Table 22 shows the JTAG timing parameters and values for APEX 20K devices.

| Table 22. AFEX 20K JIAG Tilling Falameters & Values |                                                |     |     |      |  |  |  |

|-----------------------------------------------------|------------------------------------------------|-----|-----|------|--|--|--|

| Symbol                                              | Parameter                                      | Min | Max | Unit |  |  |  |

| t <sub>JCP</sub>                                    | TCK clock period                               | 100 |     | ns   |  |  |  |

| t <sub>JCH</sub>                                    | TCK clock high time                            | 50  |     | ns   |  |  |  |

| t <sub>JCL</sub>                                    | TCK clock low time                             | 50  |     | ns   |  |  |  |

| t <sub>JPSU</sub>                                   | JTAG port setup time                           | 20  |     | ns   |  |  |  |

| t <sub>JPH</sub>                                    | JTAG port hold time                            | 45  |     | ns   |  |  |  |

| t <sub>JPCO</sub>                                   | JTAG port clock to output                      |     | 25  | ns   |  |  |  |

| t <sub>JPZX</sub>                                   | JTAG port high impedance to valid output       |     | 25  | ns   |  |  |  |

| t <sub>JPXZ</sub>                                   | JTAG port valid output to high impedance       |     | 25  | ns   |  |  |  |

| t <sub>JSSU</sub>                                   | Capture register setup time                    | 20  |     | ns   |  |  |  |

| t <sub>JSH</sub>                                    | Capture register hold time                     | 45  |     | ns   |  |  |  |

| t <sub>JSCO</sub>                                   | Update register clock to output                |     | 35  | ns   |  |  |  |

| t <sub>JSZX</sub>                                   | Update register high impedance to valid output |     | 35  | ns   |  |  |  |

| t <sub>JSXZ</sub>                                   | Update register valid output to high impedance |     | 35  | ns   |  |  |  |

Table 22. APEX 20K JTAG Timing Parameters & Values

For more information, see the following documents:

- Application Note 39 (IEEE Std. 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices)

- Jam Programming & Test Language Specification

## **Generic Testing**

Each APEX 20K device is functionally tested. Complete testing of each configurable static random access memory (SRAM) bit and all logic functionality ensures 100% yield. AC test measurements for APEX 20K devices are made under conditions equivalent to those shown in Figure 32. Multiple test patterns can be used to configure devices during all stages of the production flow.

| Table 2            | 8. APEX 20KE Device Recommende                      | ed Operating Conditions |                  |                   |      |

|--------------------|-----------------------------------------------------|-------------------------|------------------|-------------------|------|

| Symbol             | Parameter                                           | Conditions              | Min              | Max               | Unit |

| V <sub>CCINT</sub> | Supply voltage for internal logic and input buffers | (3), (4)                | 1.71 (1.71)      | 1.89 (1.89)       | V    |

| V <sub>CCIO</sub>  | Supply voltage for output buffers, 3.3-V operation  | (3), (4)                | 3.00 (3.00)      | 3.60 (3.60)       | V    |

|                    | Supply voltage for output buffers, 2.5-V operation  | (3), (4)                | 2.375<br>(2.375) | 2.625<br>(2.625)  | V    |

|                    | Supply voltage for output buffers, 1.8-V operation  | (3), (4)                | 1.71 (1.71)      | 1.89 (1.89)       | V    |

| VI                 | Input voltage                                       | (5), (6)                | -0.5             | 4.0               | V    |

| Vo                 | Output voltage                                      |                         | 0                | V <sub>CCIO</sub> | V    |

| ТJ                 | Junction temperature                                | For commercial use      | 0                | 85                | °C   |

|                    |                                                     | For industrial use      | -40              | 100               | °C   |

| t <sub>R</sub>     | Input rise time                                     |                         |                  | 40                | ns   |

| t <sub>F</sub>     | Input fall time                                     |                         |                  | 40                | ns   |

Figure 39. ESB Synchronous Timing Waveforms

#### ESB Synchronous Write (ESB Output Registers Used)

Figure 40 shows the timing model for bidirectional I/O pin timing.

| Symbol                     | Parameter                                                                             | Conditions |

|----------------------------|---------------------------------------------------------------------------------------|------------|

| t <sub>INSUBIDIR</sub>     | Setup time for bidirectional pins with global clock at LAB adjacent Input Register    |            |

| t <sub>INHBIDIR</sub>      | Hold time for bidirectional pins with global clock at LAB adjacent Input Register     |            |

| <sup>t</sup> OUTCOBIDIR    | Clock-to-output delay for bidirectional pins with global clock at IOE output register | C1 = 10 pF |

| t <sub>XZBIDIR</sub>       | Synchronous Output Enable Register to output buffer disable delay                     | C1 = 10 pF |

| t <sub>ZXBIDIR</sub>       | Synchronous Output Enable Register output buffer enable delay                         | C1 = 10 pF |

| <sup>t</sup> INSUBIDIRPLL  | Setup time for bidirectional pins with PLL clock at LAB adjacent Input Register       |            |

| t <sub>INHBIDIRPLL</sub>   | Hold time for bidirectional pins with PLL clock at LAB adjacent Input Register        |            |

| <sup>t</sup> OUTCOBIDIRPLL | Clock-to-output delay for bidirectional pins with PLL clock at IOE output register    | C1 = 10 pF |

| t <sub>XZBIDIRPLL</sub>    | Synchronous Output Enable Register to output buffer disable delay with PLL            | C1 = 10 pF |

| t <sub>ZXBIDIRPLL</sub>    | Synchronous Output Enable Register output buffer enable delay with PLL                | C1 = 10 pF |

#### Note to Tables 38 and 39:

Г

(1) These timing parameters are sample-tested only.

| Symbol             | -    | -1  |      | -2  |      | -3  |    |  |

|--------------------|------|-----|------|-----|------|-----|----|--|

|                    | Min  | Max | Min  | Max | Min  | Мах |    |  |

| t <sub>CH</sub>    | 0.55 |     | 0.78 |     | 1.15 |     | ns |  |

| t <sub>CL</sub>    | 0.55 |     | 0.78 |     | 1.15 |     | ns |  |

| t <sub>CLRP</sub>  | 0.22 |     | 0.31 |     | 0.46 |     | ns |  |

| t <sub>PREP</sub>  | 0.22 |     | 0.31 |     | 0.46 |     | ns |  |

| t <sub>ESBCH</sub> | 0.55 |     | 0.78 |     | 1.15 |     | ns |  |

| t <sub>ESBCL</sub> | 0.55 |     | 0.78 |     | 1.15 |     | ns |  |

| t <sub>ESBWP</sub> | 1.43 |     | 2.01 |     | 2.97 |     | ns |  |

| t <sub>ESBRP</sub> | 1.15 |     | 1.62 |     | 2.39 |     | ns |  |

| Symbol               | -    | 1    | -2   |      | -3   | Unit |    |

|----------------------|------|------|------|------|------|------|----|

|                      | Min  | Мах  | Min  | Max  | Min  | Max  |    |

| t <sub>INSU</sub>    | 2.02 |      | 2.13 |      | 2.24 |      | ns |

| t <sub>INH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns |

| t <sub>outco</sub>   | 2.00 | 4.88 | 2.00 | 5.36 | 2.00 | 5.88 | ns |

| t <sub>INSUPLL</sub> | 2.11 |      | 2.23 |      | -    |      | ns |

| t <sub>INHPLL</sub>  | 0.00 |      | 0.00 |      | -    |      | ns |

| toutcopll            | 0.50 | 2.60 | 0.50 | 2.88 | -    | -    | ns |

| Symbol                    | -    | 1    | -    | 2    | -    | Unit |    |

|---------------------------|------|------|------|------|------|------|----|

|                           | Min  | Max  | Min  | Max  | Min  | Max  |    |

| t <sub>insubidir</sub>    | 1.85 |      | 1.77 |      | 1.54 |      | ns |

| t <sub>inhbidir</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns |

| t <sub>outcobidir</sub>   | 2.00 | 4.88 | 2.00 | 5.36 | 2.00 | 5.88 | ns |

| t <sub>XZBIDIR</sub>      |      | 7.48 |      | 8.46 |      | 9.83 | ns |

| t <sub>ZXBIDIR</sub>      |      | 7.48 |      | 8.46 |      | 9.83 | ns |

| t <sub>insubidirpll</sub> | 4.12 |      | 4.24 |      | -    |      | ns |

| t <sub>inhbidirpll</sub>  | 0.00 |      | 0.00 |      | -    |      | ns |

| toutcobidirpll            | 0.50 | 2.60 | 0.50 | 2.88 | -    | -    | ns |

| t <sub>XZBIDIRPLL</sub>   |      | 5.21 |      | 5.99 |      | -    | ns |

| t <sub>ZXBIDIRPLL</sub>   |      | 5.21 |      | 5.99 |      | -    | ns |

Tables 55 through 60 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K60E APEX 20KE devices.

| Table 55. EP2    | OK60E f <sub>max</sub> L | E Timing Micr | oparameters |      |      |      |    |      |

|------------------|--------------------------|---------------|-------------|------|------|------|----|------|

| Symbol           | Symbol -                 |               | -1 -2       |      | -2   | -    | 3  | Unit |

|                  | Min                      | Max           | Min         | Max  | Min  | Max  |    |      |

| t <sub>SU</sub>  | 0.17                     |               | 0.15        |      | 0.16 |      | ns |      |

| t <sub>H</sub>   | 0.32                     |               | 0.33        |      | 0.39 |      | ns |      |

| t <sub>CO</sub>  |                          | 0.29          |             | 0.40 |      | 0.60 | ns |      |

| t <sub>LUT</sub> |                          | 0.77          |             | 1.07 |      | 1.59 | ns |      |

| Table 78. EP20K200E External Bidirectional Timing Parameters |      |      |      |      |      |      |    |  |  |  |

|--------------------------------------------------------------|------|------|------|------|------|------|----|--|--|--|

| Symbol                                                       | -1   |      | -2   |      | -    | Unit |    |  |  |  |

|                                                              | Min  | Мах  | Min  | Max  | Min  | Max  |    |  |  |  |

| t <sub>insubidir</sub>                                       | 2.81 |      | 3.19 |      | 3.54 |      | ns |  |  |  |

| t <sub>INHBIDIR</sub>                                        | 0.00 |      | 0.00 |      | 0.00 |      | ns |  |  |  |

| t <sub>outcobidir</sub>                                      | 2.00 | 5.12 | 2.00 | 5.62 | 2.00 | 6.11 | ns |  |  |  |

| t <sub>XZBIDIR</sub>                                         |      | 7.51 |      | 8.32 |      | 8.67 | ns |  |  |  |

| t <sub>ZXBIDIR</sub>                                         |      | 7.51 |      | 8.32 |      | 8.67 | ns |  |  |  |

| t <sub>insubidirpll</sub>                                    | 3.30 |      | 3.64 |      | -    |      | ns |  |  |  |

| t <sub>inhbidirpll</sub>                                     | 0.00 |      | 0.00 |      | -    |      | ns |  |  |  |

| t <sub>outcobidirpll</sub>                                   | 0.50 | 3.01 | 0.50 | 3.36 | -    | -    | ns |  |  |  |

| t <sub>XZBIDIRPLL</sub>                                      |      | 5.40 |      | 6.05 |      | -    | ns |  |  |  |

| t <sub>ZXBIDIRPLL</sub>                                      |      | 5.40 |      | 6.05 |      | -    | ns |  |  |  |

Tables 79 through 84 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K300E APEX 20KE devices.

| Table 79. EP20K300E f <sub>MAX</sub> LE Timing Microparameters |      |      |      |      |      |      |      |

|----------------------------------------------------------------|------|------|------|------|------|------|------|

| Symbol                                                         | -1   |      | -2   |      | -3   |      | Unit |

|                                                                | Min  | Max  | Min  | Max  | Min  | Max  |      |

| t <sub>SU</sub>                                                | 0.16 |      | 0.17 |      | 0.18 |      | ns   |

| t <sub>H</sub>                                                 | 0.31 |      | 0.33 |      | 0.38 |      | ns   |

| t <sub>CO</sub>                                                |      | 0.28 |      | 0.38 |      | 0.51 | ns   |

| t <sub>LUT</sub>                                               |      | 0.79 |      | 1.07 |      | 1.43 | ns   |

Tables 85 through 90 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K400E APEX 20KE devices.

| Table 85. EP20K400E f <sub>MAX</sub> LE Timing Microparameters |                |      |                |      |                |      |      |

|----------------------------------------------------------------|----------------|------|----------------|------|----------------|------|------|

| Symbol                                                         | -1 Speed Grade |      | -2 Speed Grade |      | -3 Speed Grade |      | Unit |

|                                                                | Min            | Max  | Min            | Max  | Min            | Max  |      |

| t <sub>SU</sub>                                                | 0.23           |      | 0.23           |      | 0.23           |      | ns   |

| t <sub>H</sub>                                                 | 0.23           |      | 0.23           |      | 0.23           |      | ns   |

| t <sub>CO</sub>                                                |                | 0.25 |                | 0.29 |                | 0.32 | ns   |

| t <sub>LUT</sub>                                               |                | 0.70 |                | 0.83 |                | 1.01 | ns   |

| Symbol                     | -1 Speed Grade |      | -2 Speed Grade |      | -3 Speed Grade |      | Unit |

|----------------------------|----------------|------|----------------|------|----------------|------|------|

|                            | Min            | Max  | Min            | Max  | Min            | Max  |      |

| t <sub>insubidir</sub>     | 3.22           |      | 3.33           |      | 3.51           |      | ns   |

| t <sub>inhbidir</sub>      | 0.00           |      | 0.00           |      | 0.00           |      | ns   |

| toutcobidir                | 2.00           | 5.75 | 2.00           | 6.33 | 2.00           | 6.90 | ns   |

| t <sub>xzbidir</sub>       |                | 6.31 |                | 7.09 |                | 7.76 | ns   |

| t <sub>ZXBIDIR</sub>       |                | 6.31 |                | 7.09 |                | 7.76 | ns   |

| t <sub>insubidirpl</sub> L | 3.25           |      | 3.26           |      |                |      | ns   |

| t <sub>inhbidirpll</sub>   | 0.00           |      | 0.00           |      |                |      | ns   |

| toutcobidirpll             | 0.50           | 2.25 | 0.50           | 2.99 |                |      | ns   |

| t <sub>xzbidirpll</sub>    |                | 2.81 |                | 3.80 |                |      | ns   |

| t <sub>zxbidirpll</sub>    |                | 2.81 |                | 3.80 |                |      | ns   |

Tables 103 through 108 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K1500E APEX 20KE devices.

| Table 103. EP20K1500E f <sub>MAX</sub> LE Timing Microparameters |                |      |                |      |                |      |      |

|------------------------------------------------------------------|----------------|------|----------------|------|----------------|------|------|

| Symbol                                                           | -1 Speed Grade |      | -2 Speed Grade |      | -3 Speed Grade |      | Unit |

|                                                                  | Min            | Max  | Min            | Max  | Min            | Max  |      |

| t <sub>SU</sub>                                                  | 0.25           |      | 0.25           |      | 0.25           |      | ns   |

| t <sub>H</sub>                                                   | 0.25           |      | 0.25           |      | 0.25           |      | ns   |

| t <sub>CO</sub>                                                  |                | 0.28 |                | 0.32 |                | 0.33 | ns   |

| t <sub>LUT</sub>                                                 |                | 0.80 |                | 0.95 |                | 1.13 | ns   |

Т

SRAM configuration elements allow APEX 20K devices to be reconfigured in-circuit by loading new configuration data into the device. Real-time reconfiguration is performed by forcing the device into command mode with a device pin, loading different configuration data, reinitializing the device, and resuming usermode operation. In-field upgrades can be performed by distributing new configuration files.

#### **Configuration Schemes**

The configuration data for an APEX 20K device can be loaded with one of five configuration schemes (see Table 111), chosen on the basis of the target application. An EPC2 or EPC16 configuration device, intelligent controller, or the JTAG port can be used to control the configuration of an APEX 20K device. When a configuration device is used, the system can configure automatically at system power-up.

Multiple APEX 20K devices can be configured in any of five configuration schemes by connecting the configuration enable (nCE) and configuration enable output (nCEO) pins on each device.

| Table 111. Data Sources for Configuration |                                                                     |  |  |  |

|-------------------------------------------|---------------------------------------------------------------------|--|--|--|

| Configuration Scheme                      | Data Source                                                         |  |  |  |

| Configuration device                      | EPC1, EPC2, EPC16 configuration devices                             |  |  |  |

| Passive serial (PS)                       | MasterBlaster or ByteBlasterMV download cable or serial data source |  |  |  |

| Passive parallel asynchronous (PPA)       | Parallel data source                                                |  |  |  |

| Passive parallel synchronous (PPS)        | Parallel data source                                                |  |  |  |

| JTAG                                      | MasterBlaster or ByteBlasterMV download cable or a microprocessor   |  |  |  |

|                                           | with a Jam or JBC File                                              |  |  |  |

For more information on configuration, see *Application Note* 116 (*Configuring APEX 20K, FLEX 10K, & FLEX 6000 Devices.*)

# **Device Pin-Outs**

See the Altera web site (http://www.altera.com) or the *Altera Digital Library* for pin-out information

# Revision History

The information contained in the *APEX 20K Programmable Logic Device Family Data Sheet* version 5.1 supersedes information published in previous versions.

#### Version 5.1

*APEX 20K Programmable Logic Device Family Data Sheet* version 5.1 contains the following changes:

- In version 5.0, the VI input voltage spec was updated in Table 28 on page 63.

- In version 5.0, *Note* (5) to Tables 27 through 30 was revised.

- Added *Note* (2) to Figure 21 on page 33.

#### Version 5.0

*APEX 20K Programmable Logic Device Family Data Sheet* version 5.0 contains the following changes:

- Updated Tables 23 through 26. Removed 2.5-V operating condition tables because all APEX 20K devices are now 5.0-V tolerant.

- Updated conditions in Tables 33, 38 and 39.

- Updated data for t<sub>ESBDATAH</sub> parameter.

#### Version 4.3

*APEX 20K Programmable Logic Device Family Data Sheet* version 4.3 contains the following changes:

- Updated Figure 20.

- Updated *Note* (2) to Table 13.

- Updated notes to Tables 27 through 30.

#### Version 4.2

*APEX 20K Programmable Logic Device Family Data Sheet* version 4.2 contains the following changes:

- Updated Figure 29.

- Updated *Note* (1) to Figure 29.