# E·XFL

## Altera - EP20K60EFC324-2N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Product Status                 | Active                                                        |

|--------------------------------|---------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                             |

| Number of Logic Elements/Cells | -                                                             |

| Total RAM Bits                 | -                                                             |

| Number of I/O                  | 196                                                           |

| Number of Gates                | -                                                             |

| Voltage - Supply               | 1.71V ~ 1.89V                                                 |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                               |

| Package / Case                 | 324-BGA                                                       |

| Supplier Device Package        | 324-FBGA (19x19)                                              |

| Purchase URL                   | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=ep20k60efc324-2n |

|                                |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Flexible clock management circuitry with up to four phase-locked loops (PLLs)

- Built-in low-skew clock tree

- Up to eight global clock signals

- ClockLock<sup>®</sup> feature reducing clock delay and skew

- ClockBoost<sup>®</sup> feature providing clock multiplication and division

- ClockShift<sup>TM</sup> programmable clock phase and delay shifting

- Powerful I/O features

- Compliant with peripheral component interconnect Special Interest Group (PCI SIG) *PCI Local Bus Specification, Revision 2.2* for 3.3-V operation at 33 or 66 MHz and 32 or 64 bits

- Support for high-speed external memories, including DDR SDRAM and ZBT SRAM (ZBT is a trademark of Integrated Device Technology, Inc.)

- Bidirectional I/O performance  $(t_{CO} + t_{SU})$  up to 250 MHz

- LVDS performance up to 840 Mbits per channel

- Direct connection from I/O pins to local interconnect providing fast t<sub>CO</sub> and t<sub>SU</sub> times for complex logic

- MultiVolt I/O interface support to interface with 1.8-V, 2.5-V, 3.3-V, and 5.0-V devices (see Table 3)

- Programmable clamp to V<sub>CCIO</sub>

- Individual tri-state output enable control for each pin

- Programmable output slew-rate control to reduce switching noise

- Support for advanced I/O standards, including low-voltage differential signaling (LVDS), LVPECL, PCI-X, AGP, CTT, stubseries terminated logic (SSTL-3 and SSTL-2), Gunning transceiver logic plus (GTL+), and high-speed terminated logic (HSTL Class I)

- Pull-up on I/O pins before and during configuration

- Advanced interconnect structure

- Four-level hierarchical FastTrack<sup>®</sup> Interconnect structure providing fast, predictable interconnect delays

- Dedicated carry chain that implements arithmetic functions such as fast adders, counters, and comparators (automatically used by software tools and megafunctions)

- Dedicated cascade chain that implements high-speed, high-fan-in logic functions (automatically used by software tools and megafunctions)

- Interleaved local interconnect allows one LE to drive 29 other LEs through the fast local interconnect

- Advanced packaging options

- Available in a variety of packages with 144 to 1,020 pins (see Tables 4 through 7)

- FineLine BGA<sup>®</sup> packages maximize board space efficiency

- Advanced software support

- Software design support and automatic place-and-route provided by the Altera<sup>®</sup> Quartus<sup>®</sup> II development system for

Windows-based PCs, Sun SPARCstations, and HP 9000 Series 700/800 workstations

- Altera MegaCore<sup>®</sup> functions and Altera Megafunction Partners Program (AMPP<sup>SM</sup>) megafunctions

- NativeLink<sup>™</sup> integration with popular synthesis, simulation, and timing analysis tools

- Quartus II SignalTap<sup>®</sup> embedded logic analyzer simplifies in-system design evaluation by giving access to internal nodes during device operation

- Supports popular revision-control software packages including PVCS, Revision Control System (RCS), and Source Code Control System (SCCS)

Table 4. APEX 20K QFP, BGA & PGA Package Options & I/O Count

Notes (1), (2)

| Device     | 144-Pin<br>TQFP | 208-Pin<br>PQFP<br>RQFP | 240-Pin<br>PQFP<br>RQFP | 356-Pin BGA | 652-Pin BGA | 655-Pin PGA |

|------------|-----------------|-------------------------|-------------------------|-------------|-------------|-------------|

| EP20K30E   | 92              | 125                     |                         |             |             |             |

| EP20K60E   | 92              | 148                     | 151                     | 196         |             |             |

| EP20K100   | 101             | 159                     | 189                     | 252         |             |             |

| EP20K100E  | 92              | 151                     | 183                     | 246         |             |             |

| EP20K160E  | 88              | 143                     | 175                     | 271         |             |             |

| EP20K200   |                 | 144                     | 174                     | 277         |             |             |

| EP20K200E  |                 | 136                     | 168                     | 271         | 376         |             |

| EP20K300E  |                 |                         | 152                     |             | 408         |             |

| EP20K400   |                 |                         |                         |             | 502         | 502         |

| EP20K400E  |                 |                         |                         |             | 488         |             |

| EP20K600E  |                 |                         |                         |             | 488         |             |

| EP20K1000E |                 |                         |                         |             | 488         |             |

| EP20K1500E |                 |                         |                         |             | 488         |             |

APEX 20K devices provide two dedicated clock pins and four dedicated input pins that drive register control inputs. These signals ensure efficient distribution of high-speed, low-skew control signals. These signals use dedicated routing channels to provide short delays and low skews. Four of the dedicated inputs drive four global signals. These four global signals can also be driven by internal logic, providing an ideal solution for a clock divider or internally generated asynchronous clear signals with high fan-out. The dedicated clock pins featured on the APEX 20K devices can also feed logic. The devices also feature ClockLock and ClockBoost clock management circuitry. APEX 20KE devices provide two additional dedicated clock pins, for a total of four dedicated clock pins.

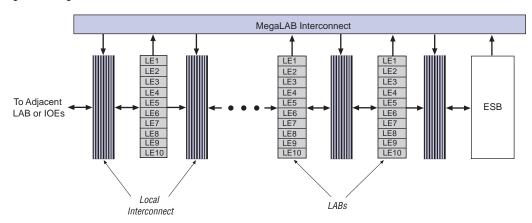

#### **MegaLAB Structure**

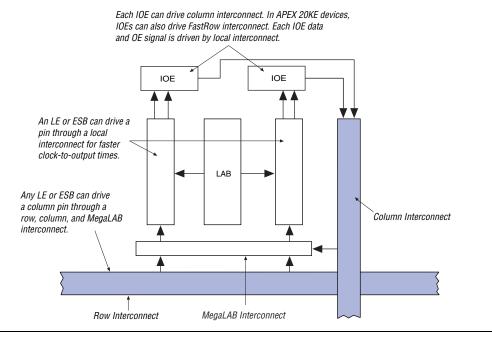

APEX 20K devices are constructed from a series of MegaLAB<sup>TM</sup> structures. Each MegaLAB structure contains a group of logic array blocks (LABs), one ESB, and a MegaLAB interconnect, which routes signals within the MegaLAB structure. The EP20K30E device has 10 LABs, EP20K60E through EP20K600E devices have 16 LABs, and the EP20K1000E and EP20K1500E devices have 24 LABs. Signals are routed between MegaLAB structures and I/O pins via the FastTrack Interconnect. In addition, edge LABs can be driven by I/O pins through the local interconnect. Figure 2 shows the MegaLAB structure.

#### Logic Element

The LE, the smallest unit of logic in the APEX 20K architecture, is compact and provides efficient logic usage. Each LE contains a four-input LUT, which is a function generator that can quickly implement any function of four variables. In addition, each LE contains a programmable register and carry and cascade chains. Each LE drives the local interconnect, MegaLAB interconnect, and FastTrack Interconnect routing structures. See Figure 5.

Each LE's programmable register can be configured for D, T, JK, or SR operation. The register's clock and clear control signals can be driven by global signals, general-purpose I/O pins, or any internal logic. For combinatorial functions, the register is bypassed and the output of the LUT drives the outputs of the LE.

Each LE has two outputs that drive the local, MegaLAB, or FastTrack Interconnect routing structure. Each output can be driven independently by the LUT's or register's output. For example, the LUT can drive one output while the register drives the other output. This feature, called register packing, improves device utilization because the register and the LUT can be used for unrelated functions. The LE can also drive out registered and unregistered versions of the LUT output.

The APEX 20K architecture provides two types of dedicated high-speed data paths that connect adjacent LEs without using local interconnect paths: carry chains and cascade chains. A carry chain supports high-speed arithmetic functions such as counters and adders, while a cascade chain implements wide-input functions such as equality comparators with minimum delay. Carry and cascade chains connect LEs 1 through 10 in an LAB and all LABs in the same MegaLAB structure.

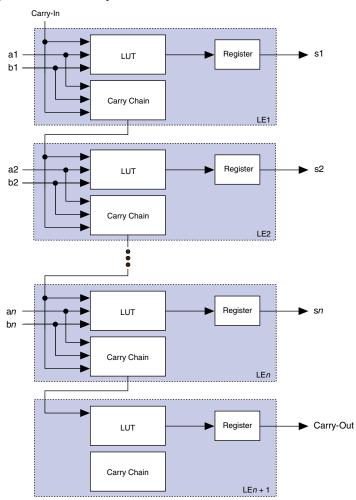

#### Carry Chain

The carry chain provides a very fast carry-forward function between LEs. The carry-in signal from a lower-order bit drives forward into the higherorder bit via the carry chain, and feeds into both the LUT and the next portion of the carry chain. This feature allows the APEX 20K architecture to implement high-speed counters, adders, and comparators of arbitrary width. Carry chain logic can be created automatically by the Quartus II software Compiler during design processing, or manually by the designer during design entry. Parameterized functions such as library of parameterized modules (LPM) and DesignWare functions automatically take advantage of carry chains for the appropriate functions.

The Quartus II software Compiler creates carry chains longer than ten LEs by linking LABs together automatically. For enhanced fitting, a long carry chain skips alternate LABs in a MegaLAB<sup>™</sup> structure. A carry chain longer than one LAB skips either from an even-numbered LAB to the next even-numbered LAB, or from an odd-numbered LAB to the next odd-numbered LAB. For example, the last LE of the first LAB in the upper-left MegaLAB structure carries to the first LE of the third LAB in the MegaLAB structure.

Figure 6 shows how an *n*-bit full adder can be implemented in n + 1 LEs with the carry chain. One portion of the LUT generates the sum of two bits using the input signals and the carry-in signal; the sum is routed to the output of the LE. The register can be bypassed for simple adders or used for accumulator functions. Another portion of the LUT and the carry chain logic generates the carry-out signal, which is routed directly to the carry-in signal of the next-higher-order bit. The final carry-out signal is routed to an LE, where it is driven onto the local, MegaLAB, or FastTrack Interconnect routing structures.

Figure 6. APEX 20K Carry Chain

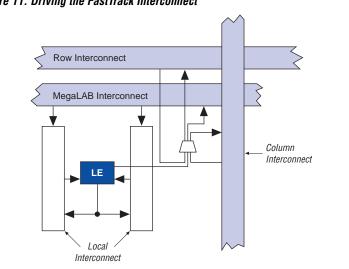

Figure 11 shows the intersection of a row and column interconnect, and how these forms of interconnects and LEs drive each other.

Figure 11. Driving the FastTrack Interconnect

APEX 20KE devices include an enhanced interconnect structure for faster routing of input signals with high fan-out. Column I/O pins can drive the FastRow<sup>™</sup> interconnect, which routes signals directly into the local interconnect without having to drive through the MegaLAB interconnect. FastRow lines traverse two MegaLAB structures. Also, these pins can drive the local interconnect directly for fast setup times. On EP20K300E and larger devices, the FastRow interconnect drives the two MegaLABs in the top left corner, the two MegaLABs in the top right corner, the two MegaLABS in the bottom left corner, and the two MegaLABs in the bottom right corner. On EP20K200E and smaller devices, FastRow interconnect drives the two MegaLABs on the top and the two MegaLABs on the bottom of the device. On all devices, the FastRow interconnect drives all local interconnect in the appropriate MegaLABs except the local interconnect on the side of the MegaLAB opposite the ESB. Pins using the FastRow interconnect achieve a faster set-up time, as the signal does not need to use a MegaLAB interconnect line to reach the destination LE. Figure 12 shows the FastRow interconnect.

| Table 9. APEX 20K Routing Scheme    |                |                   |    |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                         |                                  |                                     |                         |  |  |

|-------------------------------------|----------------|-------------------|----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------------------|-------------------------------------|-------------------------|--|--|

| Source                              | Destination    |                   |    |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                         |                                  |                                     |                         |  |  |

|                                     | Row<br>I/O Pin | Column<br>I/O Pin | LE | ESB | Local<br>Interconnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MegaLAB<br>Interconnect | Row<br>FastTrack<br>Interconnect | Column<br>FastTrack<br>Interconnect | FastRow<br>Interconnect |  |  |

| Row I/O Pin                         |                |                   |    |     | ✓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $\checkmark$            | $\checkmark$                     | <ul> <li></li> </ul>                |                         |  |  |

| Column I/O<br>Pin                   |                |                   |    |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                         |                                  | ~                                   | ✓<br>(1)                |  |  |

| LE                                  |                |                   |    |     | $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $\checkmark$            | $\checkmark$                     | $\checkmark$                        |                         |  |  |

| ESB                                 |                |                   |    |     | <ul> <li>Image: A set of the set of the</li></ul> | $\checkmark$            | ~                                | ~                                   |                         |  |  |

| Local<br>Interconnect               | ~              | ~                 | ~  | ~   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                         |                                  |                                     |                         |  |  |

| MegaLAB<br>Interconnect             |                |                   |    |     | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |                                  |                                     |                         |  |  |

| Row<br>FastTrack<br>Interconnect    |                |                   |    |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ~                       |                                  | ~                                   |                         |  |  |

| Column<br>FastTrack<br>Interconnect |                |                   |    |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ~                       | ~                                |                                     |                         |  |  |

| FastRow<br>Interconnect             |                |                   |    |     | ✓<br>(1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                         |                                  |                                     |                         |  |  |

#### Note to Table 9:

(1) This connection is supported in APEX 20KE devices only.

#### Product-Term Logic

The product-term portion of the MultiCore architecture is implemented with the ESB. The ESB can be configured to act as a block of macrocells on an ESB-by-ESB basis. Each ESB is fed by 32 inputs from the adjacent local interconnect; therefore, it can be driven by the MegaLAB interconnect or the adjacent LAB. Also, nine ESB macrocells feed back into the ESB through the local interconnect for higher performance. Dedicated clock pins, global signals, and additional inputs from the local interconnect drive the ESB control signals.

In product-term mode, each ESB contains 16 macrocells. Each macrocell consists of two product terms and a programmable register. Figure 13 shows the ESB in product-term mode.

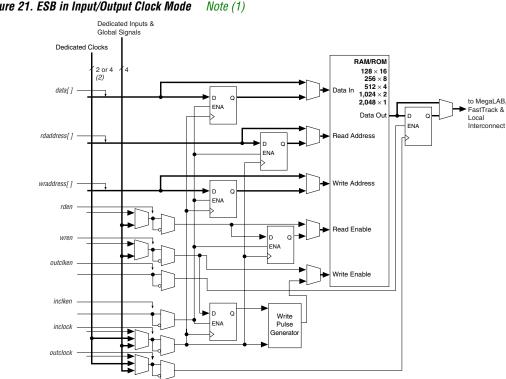

#### Input/Output Clock Mode

The input/output clock mode contains two clocks. One clock controls all registers for inputs into the ESB: data input, WE, RE, read address, and write address. The other clock controls the ESB data output registers. The ESB also supports clock enable and asynchronous clear signals; these signals also control the reading and writing of registers independently. Input/output clock mode is commonly used for applications where the reads and writes occur at the same system frequency, but require different clock enable signals for the input and output registers. Figure 21 shows the ESB in input/output clock mode.

#### Figure 21. ESB in Input/Output Clock Mode

#### Notes to Figure 21:

All registers can be cleared asynchronously by ESB local interconnect signals, global signals, or the chip-wide reset. (1)APEX 20KE devices have four dedicated clocks. (2)

#### Single-Port Mode

The APEX 20K ESB also supports a single-port mode, which is used when simultaneous reads and writes are not required. See Figure 22.

#### Altera Corporation

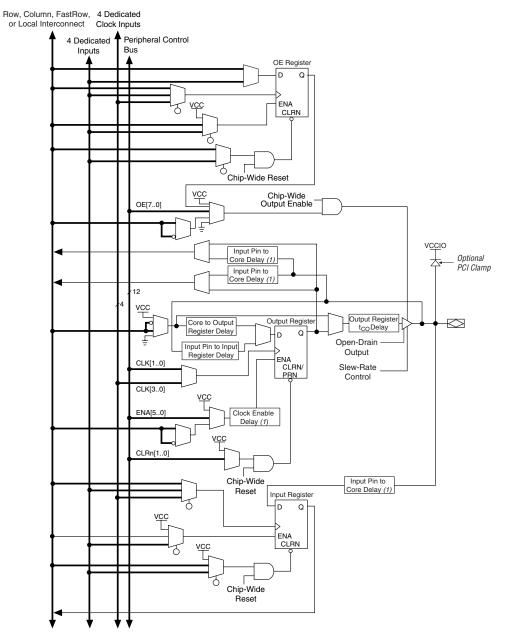

APEX 20KE devices include an enhanced IOE, which drives the FastRow interconnect. The FastRow interconnect connects a column I/O pin directly to the LAB local interconnect within two MegaLAB structures. This feature provides fast setup times for pins that drive high fan-outs with complex logic, such as PCI designs. For fast bidirectional I/O timing, LE registers using local routing can improve setup times and OE timing. The APEX 20KE IOE also includes direct support for open-drain operation, giving faster clock-to-output for open-drain signals. Some programmable delays in the APEX 20KE IOE offer multiple levels of delay to fine-tune setup and hold time requirements. The Quartus II software compiler can set these delays automatically to minimize setup time while providing a zero hold time.

Table 11 describes the APEX 20KE programmable delays and their logic options in the Quartus II software.

| Table 11. APEX 20KE Programmable Delay Chains |                                         |  |  |  |  |  |

|-----------------------------------------------|-----------------------------------------|--|--|--|--|--|

| Programmable Delays                           | Quartus II Logic Option                 |  |  |  |  |  |

| Input Pin to Core Delay                       | Decrease input delay to internal cells  |  |  |  |  |  |

| Input Pin to Input Register Delay             | Decrease input delay to input registers |  |  |  |  |  |

| Core to Output Register Delay                 | Decrease input delay to output register |  |  |  |  |  |

| Output Register t <sub>CO</sub> Delay         | Increase delay to output pin            |  |  |  |  |  |

| Clock Enable Delay                            | Increase clock enable delay             |  |  |  |  |  |

The register in the APEX 20KE IOE can be programmed to power-up high or low after configuration is complete. If it is programmed to power-up low, an asynchronous clear can control the register. If it is programmed to power-up high, an asynchronous preset can control the register. Figure 26 shows how fast bidirectional I/O pins are implemented in APEX 20KE devices. This feature is useful for cases where the APEX 20KE device controls an active-low input or another device; it prevents inadvertent activation of the input upon power-up.

#### Figure 26. APEX 20KE Bidirectional I/O Registers N

#### Notes to Figure 26:

- (1) This programmable delay has four settings: off and three levels of delay.

- (2) The output enable and input registers are LE registers in the LAB adjacent to the bidirectional pin.

Figure 28 shows how a column IOE connects to the interconnect.

#### Figure 28. Column IOE Connection to the Interconnect

## **Dedicated Fast I/O Pins**

APEX 20KE devices incorporate an enhancement to support bidirectional pins with high internal fanout such as PCI control signals. These pins are called Dedicated Fast I/O pins (FAST1, FAST2, FAST3, and FAST4) and replace dedicated inputs. These pins can be used for fast clock, clear, or high fanout logic signal distribution. They also can drive out. The Dedicated Fast I/O pin data output and tri-state control are driven by local interconnect from the adjacent MegaLAB for high speed.

#### Advanced I/O Standard Support

APEX 20KE IOEs support the following I/O standards: LVTTL, LVCMOS, 1.8-V I/O, 2.5-V I/O, 3.3-V PCI, PCI-X, 3.3-V AGP, LVDS, LVPECL, GTL+, CTT, HSTL Class I, SSTL-3 Class I and II, and SSTL-2 Class I and II.

For more information on I/O standards supported by APEX 20KE devices, see *Application Note* 117 (*Using Selectable I/O Standards in Altera Devices*).

The APEX 20KE device contains eight I/O banks. In QFP packages, the banks are linked to form four I/O banks. The I/O banks directly support all standards except LVDS and LVPECL. All I/O banks can support LVDS and LVPECL with the addition of external resistors. In addition, one block within a bank contains circuitry to support high-speed True-LVDS and LVPECL inputs, and another block within a particular bank supports high-speed True-LVDS and LVPECL outputs. The LVDS blocks support all of the I/O standards. Each I/O bank has its own VCCIO pins. A single device can support 1.8-V, 2.5-V, and 3.3-V interfaces; each bank can support a different standard independently. Each bank can also use a separate V<sub>REF</sub> level so that each bank can support any of the terminated standards (such as SSTL-3) independently. Within a bank, any one of the terminated standards can be supported. EP20K300E and larger APEX 20KE devices support the LVDS interface for data pins (smaller devices support LVDS clock pins, but not data pins). All EP20K300E and larger devices support the LVDS interface for data pins up to 155 Mbit per channel; EP20K400E devices and larger with an X-suffix on the ordering code add a serializer/deserializer circuit and PLL for higher-speed support.

Each bank can support multiple standards with the same VCCIO for output pins. Each bank can support one voltage-referenced I/O standard, but it can support multiple I/O standards with the same VCCIO voltage level. For example, when VCCIO is 3.3 V, a bank can support LVTTL, LVCMOS, 3.3-V PCI, and SSTL-3 for inputs and outputs.

When the LVDS banks are not used as LVDS I/O banks, they support all of the other I/O standards. Figure 29 shows the arrangement of the APEX 20KE I/O banks.

| Table 18. APEX 20KE Clock Input & Output Parameters       (Part 2 of 2)       Note (1) |                       |                    |                 |     |           |       |       |  |  |

|----------------------------------------------------------------------------------------|-----------------------|--------------------|-----------------|-----|-----------|-------|-------|--|--|

| Symbol                                                                                 | Parameter             | I/O Standard       | -1X Speed Grade |     | -2X Speed | Grade | Units |  |  |

|                                                                                        |                       |                    | Min             | Max | Min       | Max   |       |  |  |

| f <sub>IN</sub>                                                                        | Input clock frequency | 3.3-V LVTTL        | 1.5             | 290 | 1.5       | 257   | MHz   |  |  |

|                                                                                        |                       | 2.5-V LVTTL        | 1.5             | 281 | 1.5       | 250   | MHz   |  |  |

|                                                                                        |                       | 1.8-V LVTTL        | 1.5             | 272 | 1.5       | 243   | MHz   |  |  |

|                                                                                        |                       | GTL+               | 1.5             | 303 | 1.5       | 261   | MHz   |  |  |

|                                                                                        |                       | SSTL-2 Class<br>I  | 1.5             | 291 | 1.5       | 253   | MHz   |  |  |

|                                                                                        |                       | SSTL-2 Class<br>II | 1.5             | 291 | 1.5       | 253   | MHz   |  |  |

|                                                                                        |                       | SSTL-3 Class<br>I  | 1.5             | 300 | 1.5       | 260   | MHz   |  |  |

|                                                                                        |                       | SSTL-3 Class<br>II | 1.5             | 300 | 1.5       | 260   | MHz   |  |  |

|                                                                                        |                       | LVDS               | 1.5             | 420 | 1.5       | 350   | MHz   |  |  |

#### Notes to Tables 17 and 18:

All input clock specifications must be met. The PLL may not lock onto an incoming clock if the clock specifications are not met, creating an erroneous clock within the device.

- (2) The maximum lock time is 40 µs or 2000 input clock cycles, whichever occurs first.

- (3) Before configuration, the PLL circuits are disable and powered down. During configuration, the PLLs are still disabled. The PLLs begin to lock once the device is in the user mode. If the clock enable feature is used, lock begins once the CLKLK\_ENA pin goes high in user mode.

- (4) The PLL VCO operating range is 200 MHz ð f<sub>VCO</sub> ð 840 MHz for LVDS mode.

# SignalTap Embedded Logic Analyzer

APEX 20K devices include device enhancements to support the SignalTap embedded logic analyzer. By including this circuitry, the APEX 20K device provides the ability to monitor design operation over a period of time through the IEEE Std. 1149.1 (JTAG) circuitry; a designer can analyze internal logic at speed without bringing internal signals to the I/O pins. This feature is particularly important for advanced packages such as FineLine BGA packages because adding a connection to a pin during the debugging process can be difficult after a board is designed and manufactured.

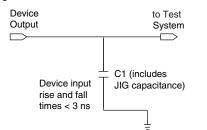

#### Figure 32. APEX 20K AC Test Conditions Note (1)

#### Note to Figure 32:

Power supply transients can affect AC measurements. Simultaneous transitions of (1) multiple outputs should be avoided for accurate measurement. Threshold tests must not be performed under AC conditions. Large-amplitude, fast-groundcurrent transients normally occur as the device outputs discharge the load capacitances. When these transients flow through the parasitic inductance between the device ground pin and the test system ground, significant reductions in observable noise immunity can result.

## Operating **Conditions**

Tables 23 through 26 provide information on absolute maximum ratings, recommended operating conditions, DC operating conditions, and capacitance for 2.5-V APEX 20K devices.

| Table 2            | Table 23. APEX 20K 5.0-V Tolerant Device Absolute Maximum Ratings       Notes (1), (2) |                                                |      |      |      |  |  |  |  |

|--------------------|----------------------------------------------------------------------------------------|------------------------------------------------|------|------|------|--|--|--|--|

| Symbol             | Parameter                                                                              | Conditions                                     | Min  | Max  | Unit |  |  |  |  |

| V <sub>CCINT</sub> | Supply voltage                                                                         | With respect to ground (3)                     | -0.5 | 3.6  | V    |  |  |  |  |

| V <sub>CCIO</sub>  |                                                                                        |                                                | -0.5 | 4.6  | V    |  |  |  |  |

| VI                 | DC input voltage                                                                       |                                                | -2.0 | 5.75 | V    |  |  |  |  |

| I <sub>OUT</sub>   | DC output current, per pin                                                             |                                                | -25  | 25   | mA   |  |  |  |  |

| T <sub>STG</sub>   | Storage temperature                                                                    | No bias                                        | -65  | 150  | °C   |  |  |  |  |

| T <sub>AMB</sub>   | Ambient temperature                                                                    | Under bias                                     | -65  | 135  | °C   |  |  |  |  |

| TJ                 | Junction temperature                                                                   | PQFP, RQFP, TQFP, and BGA packages, under bias |      | 135  | °C   |  |  |  |  |

|                    |                                                                                        | Ceramic PGA packages, under bias               |      | 150  | °C   |  |  |  |  |

| Table 23. APEX 20K 5.0-V Tolerant Device Absolute Maximum Ratings | Notes (1), (2) |

|-------------------------------------------------------------------|----------------|

|-------------------------------------------------------------------|----------------|

| Table 26. APEX 20K 5.0-V Tolerant Device Capacitance       Notes (2), (14) |                                          |                                     |     |     |      |  |  |  |

|----------------------------------------------------------------------------|------------------------------------------|-------------------------------------|-----|-----|------|--|--|--|

| Symbol                                                                     | Parameter                                | Conditions                          | Min | Мах | Unit |  |  |  |

| C <sub>IN</sub>                                                            | Input capacitance                        | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 8   | pF   |  |  |  |

| C <sub>INCLK</sub>                                                         | Input capacitance on dedicated clock pin | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 12  | pF   |  |  |  |

| C <sub>OUT</sub>                                                           | Output capacitance                       | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 8   | pF   |  |  |  |

#### Notes to Tables 23 through 26:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- All APEX 20K devices are 5.0-V tolerant. (2)

- (3) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to 5.75 V for input currents less than 100 mA and periods shorter than 20 ns.

- Numbers in parentheses are for industrial-temperature-range devices. (4)

- Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically. (5)

- All pins, including dedicated inputs, clock I/O, and JTAG pins, may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are (6) powered.

- (7)Typical values are for  $T_A = 25^{\circ}$  C,  $V_{CCINT} = 2.5$  V, and  $V_{CCIO} = 2.5$  or 3.3 V.

- These values are specified in the APEX 20K device recommended operating conditions, shown in Table 26 on (8)page 62.

- (9) The APEX 20K input buffers are compatible with 2.5-V and 3.3-V (LVTTL and LVCMOS) signals. Additionally, the input buffers are 3.3-V PCI compliant when V<sub>CCIO</sub> and V<sub>CCINT</sub> meet the relationship shown in Figure 33 on page 68.

- (10) The I<sub>OH</sub> parameter refers to high-level TTL, PCI or CMOS output current.

- (11) The I<sub>OL</sub> parameter refers to low-level TTL, PCI, or CMOS output current. This parameter applies to open-drain pins as well as output pins.

- (12) This value is specified for normal device operation. The value may vary during power-up.

- (13) Pin pull-up resistance values will be lower if an external source drives the pin higher than  $V_{CCIO}$ .

- (14) Capacitance is sample-tested only.

Tables 27 through 30 provide information on absolute maximum ratings, recommended operating conditions, DC operating conditions, and capacitance for 1.8-V APEX 20KE devices.

| Symbol             | Parameter                  | Conditions                                        | Min  | Max | Unit |

|--------------------|----------------------------|---------------------------------------------------|------|-----|------|

| V <sub>CCINT</sub> | Supply voltage             | With respect to ground (2)                        | -0.5 | 2.5 | V    |

| V <sub>CCIO</sub>  |                            |                                                   | -0.5 | 4.6 | V    |

| VI                 | DC input voltage           |                                                   | -0.5 | 4.6 | V    |

| I <sub>OUT</sub>   | DC output current, per pin |                                                   | -25  | 25  | mA   |

| T <sub>STG</sub>   | Storage temperature        | No bias                                           | -65  | 150 | °C   |

| T <sub>AMB</sub>   | Ambient temperature        | Under bias                                        | -65  | 135 | °C   |

| ΤJ                 | Junction temperature       | PQFP, RQFP, TQFP, and BGA packages,<br>under bias |      | 135 | °C   |

|                    |                            | Ceramic PGA packages, under bias                  |      | 150 | °C   |

| Symbol                  | -1 Spee | d Grade | -2 Spee | d Grade | -3 Speed Grade |     | Units |

|-------------------------|---------|---------|---------|---------|----------------|-----|-------|

|                         |         |         |         |         | _              |     | -     |

|                         | Min     | Max     | Min     | Max     | Min            | Max |       |

| t <sub>SU</sub>         | 0.1     |         | 0.3     |         | 0.6            |     | ns    |

| t <sub>H</sub>          | 0.5     |         | 0.8     |         | 0.9            |     | ns    |

| t <sub>CO</sub>         |         | 0.1     |         | 0.4     |                | 0.6 | ns    |

| t <sub>LUT</sub>        |         | 1.0     |         | 1.2     |                | 1.4 | ns    |

| t <sub>ESBRC</sub>      |         | 1.7     |         | 2.1     |                | 2.4 | ns    |

| t <sub>ESBWC</sub>      |         | 5.7     |         | 6.9     |                | 8.1 | ns    |

| t <sub>ESBWESU</sub>    | 3.3     |         | 3.9     |         | 4.6            |     | ns    |

| t <sub>ESBDATASU</sub>  | 2.2     |         | 2.7     |         | 3.1            |     | ns    |

| t <sub>ESBDATAH</sub>   | 0.6     |         | 0.8     |         | 0.9            |     | ns    |

| t <sub>ESBADDRSU</sub>  | 2.4     |         | 2.9     |         | 3.3            |     | ns    |

| t <sub>ESBDATACO1</sub> |         | 1.3     |         | 1.6     |                | 1.8 | ns    |

| t <sub>ESBDATACO2</sub> |         | 2.5     |         | 3.1     |                | 3.6 | ns    |

| t <sub>ESBDD</sub>      |         | 2.5     |         | 3.3     |                | 3.6 | ns    |

| t <sub>PD</sub>         |         | 2.5     |         | 3.1     |                | 3.6 | ns    |

| t <sub>PTERMSU</sub>    | 1.7     |         | 2.1     |         | 2.4            |     | ns    |

| t <sub>PTERMCO</sub>    |         | 1.0     |         | 1.2     |                | 1.4 | ns    |

| t <sub>F1-4</sub>       |         | 0.4     |         | 0.5     |                | 0.6 | ns    |

| t <sub>F5-20</sub>      |         | 2.6     |         | 2.8     |                | 2.9 | ns    |

| t <sub>F20+</sub>       |         | 3.7     |         | 3.8     |                | 3.9 | ns    |

| t <sub>CH</sub>         | 2.0     |         | 2.5     |         | 3.0            |     | ns    |

| t <sub>CL</sub>         | 2.0     |         | 2.5     |         | 3.0            |     | ns    |

| t <sub>CLRP</sub>       | 0.5     |         | 0.6     |         | 0.8            |     | ns    |

| t <sub>PREP</sub>       | 0.5     |         | 0.5     |         | 0.5            |     | ns    |

| t <sub>ESBCH</sub>      | 2.0     |         | 2.5     |         | 3.0            |     | ns    |

| t <sub>ESBCL</sub>      | 2.0     |         | 2.5     |         | 3.0            |     | ns    |

| t <sub>ESBWP</sub>      | 1.5     |         | 1.9     |         | 2.2            |     | ns    |

| t <sub>ESBRP</sub>      | 1.0     |         | 1.2     |         | 1.4            |     | ns    |

Tables 43 through 48 show the I/O external and external bidirectional timing parameter values for EP20K100, EP20K200, and EP20K400 APEX 20K devices.

| Table 57. EP20K60E f <sub>MAX</sub> Routing Delays |       |      |     |      |     |      |    |  |  |

|----------------------------------------------------|-------|------|-----|------|-----|------|----|--|--|

| Symbol                                             | -1 -2 |      | -:  | Unit |     |      |    |  |  |

|                                                    | Min   | Max  | Min | Max  | Min | Max  |    |  |  |

| t <sub>F1-4</sub>                                  |       | 0.24 |     | 0.26 |     | 0.30 | ns |  |  |

| t <sub>F5-20</sub>                                 |       | 1.45 |     | 1.58 |     | 1.79 | ns |  |  |

| t <sub>F20+</sub>                                  |       | 1.96 |     | 2.14 |     | 2.45 | ns |  |  |

| Table 58. EP20K60E Minimum Pulse Width Timing Parameters |      |     |      |     |      |     |      |  |  |

|----------------------------------------------------------|------|-----|------|-----|------|-----|------|--|--|

| Symbol                                                   | -    | 1   | -    | 2   | -3   |     | Unit |  |  |

|                                                          | Min  | Max | Min  | Max | Min  | Max | 1    |  |  |

| t <sub>CH</sub>                                          | 2.00 |     | 2.50 |     | 2.75 |     | ns   |  |  |

| t <sub>CL</sub>                                          | 2.00 |     | 2.50 |     | 2.75 |     | ns   |  |  |

| t <sub>CLRP</sub>                                        | 0.20 |     | 0.28 |     | 0.41 |     | ns   |  |  |

| t <sub>PREP</sub>                                        | 0.20 |     | 0.28 |     | 0.41 |     | ns   |  |  |

| t <sub>ESBCH</sub>                                       | 2.00 |     | 2.50 |     | 2.75 |     | ns   |  |  |

| t <sub>ESBCL</sub>                                       | 2.00 |     | 2.50 |     | 2.75 |     | ns   |  |  |

| t <sub>ESBWP</sub>                                       | 1.29 |     | 1.80 |     | 2.66 |     | ns   |  |  |

| t <sub>ESBRP</sub>                                       | 1.04 |     | 1.45 |     | 2.14 |     | ns   |  |  |

| Table 59. EP20K60E External Timing Parameters |      |      |      |      |      |      |      |  |  |

|-----------------------------------------------|------|------|------|------|------|------|------|--|--|

| Symbol                                        | -    | 1    | -    | -2   | -3   |      | Unit |  |  |

|                                               | Min  | Max  | Min  | Max  | Min  | Max  |      |  |  |

| t <sub>INSU</sub>                             | 2.03 |      | 2.12 |      | 2.23 |      | ns   |  |  |

| t <sub>INH</sub>                              | 0.00 |      | 0.00 |      | 0.00 |      | ns   |  |  |

| t <sub>outco</sub>                            | 2.00 | 4.84 | 2.00 | 5.31 | 2.00 | 5.81 | ns   |  |  |

| t <sub>INSUPLL</sub>                          | 1.12 |      | 1.15 |      | -    |      | ns   |  |  |

| t <sub>INHPLL</sub>                           | 0.00 |      | 0.00 |      | -    |      | ns   |  |  |

| toutcopll                                     | 0.50 | 3.37 | 0.50 | 3.69 | -    | -    | ns   |  |  |

| Symbol                  | -1    |      | -2    |      | -3   |      | Unit |

|-------------------------|-------|------|-------|------|------|------|------|

|                         | Min   | Max  | Min   | Max  | Min  | Max  | 1    |

| t <sub>ESBARC</sub>     |       | 1.68 |       | 2.06 |      | 2.24 | ns   |

| t <sub>ESBSRC</sub>     |       | 2.27 |       | 2.77 |      | 3.18 | ns   |

| t <sub>ESBAWC</sub>     |       | 3.10 |       | 3.86 |      | 4.50 | ns   |

| t <sub>ESBSWC</sub>     |       | 2.90 |       | 3.67 |      | 4.21 | ns   |

| t <sub>ESBWASU</sub>    | 0.55  |      | 0.67  |      | 0.74 |      | ns   |

| t <sub>ESBWAH</sub>     | 0.36  |      | 0.46  |      | 0.48 |      | ns   |

| t <sub>ESBWDSU</sub>    | 0.69  |      | 0.83  |      | 0.95 |      | ns   |

| t <sub>ESBWDH</sub>     | 0.36  |      | 0.46  |      | 0.48 |      | ns   |

| t <sub>ESBRASU</sub>    | 1.61  |      | 1.90  |      | 2.09 |      | ns   |

| t <sub>ESBRAH</sub>     | 0.00  |      | 0.00  |      | 0.01 |      | ns   |

| t <sub>ESBWESU</sub>    | 1.42  |      | 1.71  |      | 2.01 |      | ns   |

| t <sub>ESBWEH</sub>     | 0.00  |      | 0.00  |      | 0.00 |      | ns   |

| t <sub>ESBDATASU</sub>  | -0.06 |      | -0.07 |      | 0.05 |      | ns   |

| t <sub>ESBDATAH</sub>   | 0.13  |      | 0.13  |      | 0.13 |      | ns   |

| t <sub>ESBWADDRSU</sub> | 0.11  |      | 0.13  |      | 0.31 |      | ns   |

| t <sub>ESBRADDRSU</sub> | 0.18  |      | 0.23  |      | 0.39 |      | ns   |

| t <sub>ESBDATACO1</sub> |       | 1.09 |       | 1.35 |      | 1.51 | ns   |

| t <sub>ESBDATACO2</sub> |       | 2.19 |       | 2.75 |      | 3.22 | ns   |

| t <sub>ESBDD</sub>      |       | 2.75 |       | 3.41 |      | 4.03 | ns   |

| t <sub>PD</sub>         |       | 1.58 |       | 1.97 |      | 2.33 | ns   |

| t <sub>PTERMSU</sub>    | 1.00  |      | 1.22  |      | 1.51 |      | ns   |

| t <sub>PTERMCO</sub>    |       | 1.10 |       | 1.37 |      | 1.09 | ns   |

| Table 75. EP20K200E f <sub>MAX</sub> Routing Delays |     |      |     |      |     |      |      |  |  |  |

|-----------------------------------------------------|-----|------|-----|------|-----|------|------|--|--|--|

| Symbol                                              | -   | ·1   | -2  |      | -3  |      | Unit |  |  |  |

|                                                     | Min | Max  | Min | Max  | Min | Max  |      |  |  |  |

| t <sub>F1-4</sub>                                   |     | 0.25 |     | 0.27 |     | 0.29 | ns   |  |  |  |

| t <sub>F5-20</sub>                                  |     | 1.02 |     | 1.20 |     | 1.41 | ns   |  |  |  |

| t <sub>F20+</sub>                                   |     | 1.99 |     | 2.23 |     | 2.53 | ns   |  |  |  |

| Table 78. EP20K200E External Bidirectional Timing Parameters |      |      |      |      |      |      |      |  |  |

|--------------------------------------------------------------|------|------|------|------|------|------|------|--|--|

| Symbol                                                       | -1   |      | -2   |      | -3   |      | Unit |  |  |

|                                                              | Min  | Мах  | Min  | Max  | Min  | Max  | 1    |  |  |

| t <sub>insubidir</sub>                                       | 2.81 |      | 3.19 |      | 3.54 |      | ns   |  |  |

| t <sub>INHBIDIR</sub>                                        | 0.00 |      | 0.00 |      | 0.00 |      | ns   |  |  |

| t <sub>outcobidir</sub>                                      | 2.00 | 5.12 | 2.00 | 5.62 | 2.00 | 6.11 | ns   |  |  |

| t <sub>XZBIDIR</sub>                                         |      | 7.51 |      | 8.32 |      | 8.67 | ns   |  |  |

| t <sub>ZXBIDIR</sub>                                         |      | 7.51 |      | 8.32 |      | 8.67 | ns   |  |  |

| t <sub>insubidirpll</sub>                                    | 3.30 |      | 3.64 |      | -    |      | ns   |  |  |

| t <sub>inhbidirpll</sub>                                     | 0.00 |      | 0.00 |      | -    |      | ns   |  |  |

| t <sub>outcobidirpll</sub>                                   | 0.50 | 3.01 | 0.50 | 3.36 | -    | -    | ns   |  |  |

| t <sub>XZBIDIRPLL</sub>                                      |      | 5.40 |      | 6.05 |      | -    | ns   |  |  |

| tZXBIDIRPLL                                                  |      | 5.40 |      | 6.05 |      | -    | ns   |  |  |

Tables 79 through 84 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K300E APEX 20KE devices.

| Table 79. EP20K300E f <sub>MAX</sub> LE Timing Microparameters |      |      |      |      |      |      |    |  |  |

|----------------------------------------------------------------|------|------|------|------|------|------|----|--|--|

| Symbol                                                         | -    | 1    | -    | 2    | -;   | Unit |    |  |  |

|                                                                | Min  | Max  | Min  | Max  | Min  | Max  | 1  |  |  |

| t <sub>SU</sub>                                                | 0.16 |      | 0.17 |      | 0.18 |      | ns |  |  |

| t <sub>H</sub>                                                 | 0.31 |      | 0.33 |      | 0.38 |      | ns |  |  |

| t <sub>CO</sub>                                                |      | 0.28 |      | 0.38 |      | 0.51 | ns |  |  |

| t <sub>LUT</sub>                                               |      | 0.79 |      | 1.07 |      | 1.43 | ns |  |  |