### Intel - EP20K60EFC324-3 Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 2560                                                       |

| Number of Logic Elements/Cells | 2560                                                       |

| Total RAM Bits                 | 32768                                                      |

| Number of I/O                  | 196                                                        |

| Number of Gates                | 162000                                                     |

| Voltage - Supply               | 1.71V ~ 1.89V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 324-BGA                                                    |

| Supplier Device Package        | 324-FBGA (19x19)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep20k60efc324-3 |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 2. Additiona       | vice Features | Note (1)  |           |           |            |            |

|--------------------------|---------------|-----------|-----------|-----------|------------|------------|

| Feature                  | EP20K300E     | EP20K400  | EP20K400E | EP20K600E | EP20K1000E | EP20K1500E |

| Maximum system gates     | 728,000       | 1,052,000 | 1,052,000 | 1,537,000 | 1,772,000  | 2,392,000  |

| Typical gates            | 300,000       | 400,000   | 400,000   | 600,000   | 1,000,000  | 1,500,000  |

| LEs                      | 11,520        | 16,640    | 16,640    | 24,320    | 38,400     | 51,840     |

| ESBs                     | 72            | 104       | 104       | 152       | 160        | 216        |

| Maximum<br>RAM bits      | 147,456       | 212,992   | 212,992   | 311,296   | 327,680    | 442,368    |

| Maximum<br>macrocells    | 1,152         | 1,664     | 1,664     | 2,432     | 2,560      | 3,456      |

| Maximum user I/O<br>pins | 408           | 502       | 488       | 588       | 708        | 808        |

#### Note to Tables 1 and 2:

The embedded IEEE Std. 1149.1 Joint Test Action Group (JTAG) boundary-scan circuitry contributes up to 57,000 additional gates.

Additional Features

- Designed for low-power operation

- 1.8-V and 2.5-V supply voltage (see Table 3)

- MultiVolt<sup>™</sup> I/O interface support to interface with 1.8-V, 2.5-V, 3.3-V, and 5.0-V devices (see Table 3)

- ESB offering programmable power-saving mode

| Feature                                                     | Device                           |                                                                                                                                |  |  |

|-------------------------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                             | EP20K100<br>EP20K200<br>EP20K400 | EP20K30E<br>EP20K60E<br>EP20K100E<br>EP20K160E<br>EP20K200E<br>EP20K300E<br>EP20K400E<br>EP20K600E<br>EP20K1000E<br>EP20K1500E |  |  |

| Internal supply voltage (V <sub>CCINT</sub> )               | 2.5 V                            | 1.8 V                                                                                                                          |  |  |

| MultiVolt I/O interface voltage levels (V <sub>CCIO</sub> ) | 2.5 V, 3.3 V, 5.0 V              | 1.8 V, 2.5 V, 3.3 V, 5.0 V (1)                                                                                                 |  |  |

#### Note to Table 3:

(1) APEX 20KE devices can be 5.0-V tolerant by using an external resistor.

# General Description

APEX<sup>™</sup> 20K devices are the first PLDs designed with the MultiCore architecture, which combines the strengths of LUT-based and productterm-based devices with an enhanced memory structure. LUT-based logic provides optimized performance and efficiency for data-path, registerintensive, mathematical, or digital signal processing (DSP) designs. Product-term-based logic is optimized for complex combinatorial paths, such as complex state machines. LUT- and product-term-based logic combined with memory functions and a wide variety of MegaCore and AMPP functions make the APEX 20K device architecture uniquely suited for system-on-a-programmable-chip designs. Applications historically requiring a combination of LUT-, product-term-, and memory-based devices can now be integrated into one APEX 20K device.

APEX 20KE devices are a superset of APEX 20K devices and include additional features such as advanced I/O standard support, CAM, additional global clocks, and enhanced ClockLock clock circuitry. In addition, APEX 20KE devices extend the APEX 20K family to 1.5 million gates. APEX 20KE devices are denoted with an "E" suffix in the device name (e.g., the EP20K1000E device is an APEX 20KE device). Table 8 compares the features included in APEX 20K and APEX 20KE devices.

### **Logic Array Block**

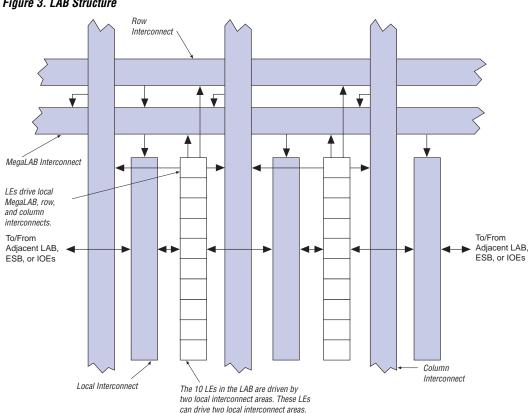

Each LAB consists of 10 LEs, the LEs' associated carry and cascade chains, LAB control signals, and the local interconnect. The local interconnect transfers signals between LEs in the same or adjacent LABs, IOEs, or ESBs. The Quartus II Compiler places associated logic within an LAB or adjacent LABs, allowing the use of a fast local interconnect for high performance. Figure 3 shows the APEX 20K LAB.

APEX 20K devices use an interleaved LAB structure. This structure allows each LE to drive two local interconnect areas. This feature minimizes use of the MegaLAB and FastTrack interconnect, providing higher performance and flexibility. Each LE can drive 29 other LEs through the fast local interconnect.

#### Figure 13. Product-Term Logic in ESB

### Note to Figure 13:

(1) APEX 20KE devices have four dedicated clocks.

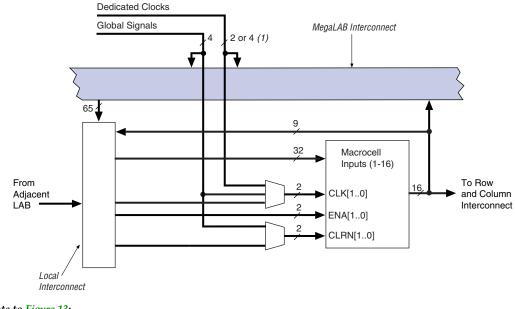

#### Macrocells

APEX 20K macrocells can be configured individually for either sequential or combinatorial logic operation. The macrocell consists of three functional blocks: the logic array, the product-term select matrix, and the programmable register.

Combinatorial logic is implemented in the product terms. The productterm select matrix allocates these product terms for use as either primary logic inputs (to the OR and XOR gates) to implement combinatorial functions, or as parallel expanders to be used to increase the logic available to another macrocell. One product term can be inverted; the Quartus II software uses this feature to perform DeMorgan's inversion for more efficient implementation of wide OR functions. The Quartus II software Compiler can use a NOT-gate push-back technique to emulate an asynchronous preset. Figure 14 shows the APEX 20K macrocell.

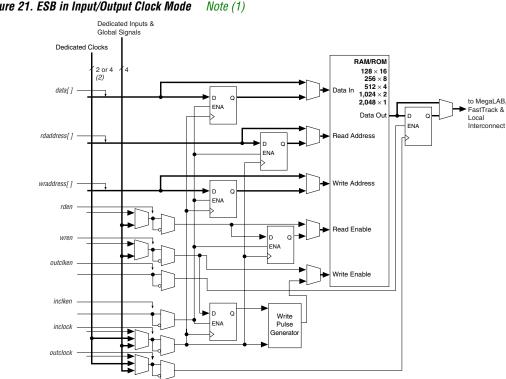

### Input/Output Clock Mode

The input/output clock mode contains two clocks. One clock controls all registers for inputs into the ESB: data input, WE, RE, read address, and write address. The other clock controls the ESB data output registers. The ESB also supports clock enable and asynchronous clear signals; these signals also control the reading and writing of registers independently. Input/output clock mode is commonly used for applications where the reads and writes occur at the same system frequency, but require different clock enable signals for the input and output registers. Figure 21 shows the ESB in input/output clock mode.

#### Figure 21. ESB in Input/Output Clock Mode

#### Notes to Figure 21:

All registers can be cleared asynchronously by ESB local interconnect signals, global signals, or the chip-wide reset. (1)APEX 20KE devices have four dedicated clocks. (2)

### Single-Port Mode

The APEX 20K ESB also supports a single-port mode, which is used when simultaneous reads and writes are not required. See Figure 22.

#### Altera Corporation

### Implementing Logic in ROM

In addition to implementing logic with product terms, the ESB can implement logic functions when it is programmed with a read-only pattern during configuration, creating a large LUT. With LUTs, combinatorial functions are implemented by looking up the results, rather than by computing them. This implementation of combinatorial functions can be faster than using algorithms implemented in general logic, a performance advantage that is further enhanced by the fast access times of ESBs. The large capacity of ESBs enables designers to implement complex functions in one logic level without the routing delays associated with linked LEs or distributed RAM blocks. Parameterized functions such as LPM functions can take advantage of the ESB automatically. Further, the Quartus II software can implement portions of a design with ESBs where appropriate.

## **Programmable Speed/Power Control**

APEX 20K ESBs offer a high-speed mode that supports very fast operation on an ESB-by-ESB basis. When high speed is not required, this feature can be turned off to reduce the ESB's power dissipation by up to 50%. ESBs that run at low power incur a nominal timing delay adder. This Turbo Bit<sup>™</sup> option is available for ESBs that implement product-term logic or memory functions. An ESB that is not used will be powered down so that it does not consume DC current.

Designers can program each ESB in the APEX 20K device for either high-speed or low-power operation. As a result, speed-critical paths in the design can run at high speed, while the remaining paths operate at reduced power.

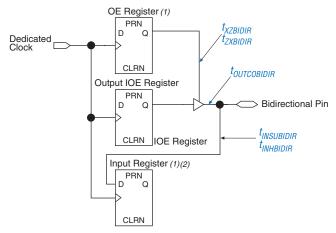

# I/O Structure

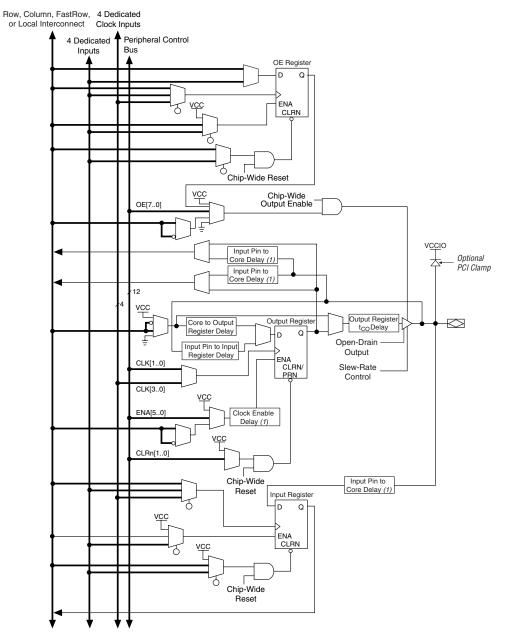

The APEX 20K IOE contains a bidirectional I/O buffer and a register that can be used either as an input register for external data requiring fast setup times, or as an output register for data requiring fast clock-to-output performance. IOEs can be used as input, output, or bidirectional pins. For fast bidirectional I/O timing, LE registers using local routing can improve setup times and OE timing. The Quartus II software Compiler uses the programmable inversion option to invert signals from the row and column interconnect automatically where appropriate. Because the APEX 20K IOE offers one output enable per pin, the Quartus II software Compiler can emulate open-drain operation efficiently.

The APEX 20K IOE includes programmable delays that can be activated to ensure zero hold times, minimum clock-to-output times, input IOE register-to-core register transfers, or core-to-output IOE register transfers. A path in which a pin directly drives a register may require the delay to ensure zero hold time, whereas a path in which a pin drives a register through combinatorial logic may not require the delay.

### Figure 26. APEX 20KE Bidirectional I/O Registers N

#### Notes to Figure 26:

- (1) This programmable delay has four settings: off and three levels of delay.

- (2) The output enable and input registers are LE registers in the LAB adjacent to the bidirectional pin.

Table 22 shows the JTAG timing parameters and values for APEX 20K devices.

| Table 22. AFEA 20K JTAG TIIIIIIY Farameters & Values |                                                |     |     |      |  |  |

|------------------------------------------------------|------------------------------------------------|-----|-----|------|--|--|

| Symbol                                               | Parameter                                      | Min | Max | Unit |  |  |

| t <sub>JCP</sub>                                     | TCK clock period                               | 100 |     | ns   |  |  |

| t <sub>JCH</sub>                                     | TCK clock high time                            | 50  |     | ns   |  |  |

| t <sub>JCL</sub>                                     | TCK clock low time                             | 50  |     | ns   |  |  |

| t <sub>JPSU</sub>                                    | JTAG port setup time                           | 20  |     | ns   |  |  |

| t <sub>JPH</sub>                                     | JTAG port hold time                            | 45  |     | ns   |  |  |

| t <sub>JPCO</sub>                                    | JTAG port clock to output                      |     | 25  | ns   |  |  |

| t <sub>JPZX</sub>                                    | JTAG port high impedance to valid output       |     | 25  | ns   |  |  |

| t <sub>JPXZ</sub>                                    | JTAG port valid output to high impedance       |     | 25  | ns   |  |  |

| t <sub>JSSU</sub>                                    | Capture register setup time                    | 20  |     | ns   |  |  |

| t <sub>JSH</sub>                                     | Capture register hold time                     | 45  |     | ns   |  |  |

| t <sub>JSCO</sub>                                    | Update register clock to output                |     | 35  | ns   |  |  |

| t <sub>JSZX</sub>                                    | Update register high impedance to valid output |     | 35  | ns   |  |  |

| t <sub>JSXZ</sub>                                    | Update register valid output to high impedance |     | 35  | ns   |  |  |

Table 22. APEX 20K JTAG Timing Parameters & Values

For more information, see the following documents:

- Application Note 39 (IEEE Std. 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices)

- Jam Programming & Test Language Specification

# **Generic Testing**

Each APEX 20K device is functionally tested. Complete testing of each configurable static random access memory (SRAM) bit and all logic functionality ensures 100% yield. AC test measurements for APEX 20K devices are made under conditions equivalent to those shown in Figure 32. Multiple test patterns can be used to configure devices during all stages of the production flow.

| Symbol             | Parameter                                              | Conditions         | Min              | Max               | Unit |

|--------------------|--------------------------------------------------------|--------------------|------------------|-------------------|------|

| V <sub>CCINT</sub> | Supply voltage for internal logic<br>and input buffers | (4), (5)           | 2.375<br>(2.375) | 2.625<br>(2.625)  | V    |

| V <sub>CCIO</sub>  | Supply voltage for output buffers, 3.3-V operation     | (4), (5)           | 3.00 (3.00)      | 3.60 (3.60)       | V    |

|                    | Supply voltage for output buffers, 2.5-V operation     | (4), (5)           | 2.375<br>(2.375) | 2.625<br>(2.625)  | V    |

| VI                 | Input voltage                                          | (3), (6)           | -0.5             | 5.75              | V    |

| Vo                 | Output voltage                                         |                    | 0                | V <sub>CCIO</sub> | V    |

| TJ                 | Junction temperature                                   | For commercial use | 0                | 85                | °C   |

|                    |                                                        | For industrial use | -40              | 100               | °C   |

| t <sub>R</sub>     | Input rise time                                        |                    |                  | 40                | ns   |

| t <sub>F</sub>     | Input fall time                                        |                    |                  | 40                | ns   |

| Symbol          | Parameter                            | Conditions                                                                             | Min                                 | Тур | Max                        | Unit |

|-----------------|--------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------|-----|----------------------------|------|

| V <sub>IH</sub> | High-level input voltage             |                                                                                        | 1.7, 0.5 × V <sub>CCIO</sub><br>(9) |     | 5.75                       | V    |

| V <sub>IL</sub> | Low-level input voltage              |                                                                                        | -0.5                                |     | $0.8, 0.3 \times V_{CCIO}$ | V    |

| V <sub>OH</sub> | 3.3-V high-level TTL output voltage  | I <sub>OH</sub> = -8 mA DC,<br>V <sub>CCIO</sub> = 3.00 V <i>(10)</i>                  | 2.4                                 |     |                            | V    |

|                 | 3.3-V high-level CMOS output voltage | I <sub>OH</sub> = -0.1 mA DC,<br>V <sub>CCIO</sub> = 3.00 V <i>(10)</i>                | V <sub>CCIO</sub> - 0.2             |     |                            | V    |

|                 | 3.3-V high-level PCI output voltage  | $I_{OH} = -0.5 \text{ mA DC},$<br>$V_{CCIO} = 3.00 \text{ to } 3.60 \text{ V}$<br>(10) | $0.9 \times V_{CCIO}$               |     |                            | V    |

|                 | 2.5-V high-level output voltage      | I <sub>OH</sub> = -0.1 mA DC,<br>V <sub>CCIO</sub> = 2.30 V <i>(10)</i>                | 2.1                                 |     |                            | V    |

|                 |                                      | I <sub>OH</sub> = -1 mA DC,<br>V <sub>CCIO</sub> = 2.30 V <i>(10)</i>                  | 2.0                                 |     |                            | V    |

|                 |                                      | I <sub>OH</sub> = –2 mA DC,<br>V <sub>CCIO</sub> = 2.30 V <i>(10)</i>                  | 1.7                                 |     |                            | V    |

| Table 26. APEX 20K 5.0-V Tolerant Device Capacitance Notes (2), (14) |                                          |                                     |     |     |      |  |  |

|----------------------------------------------------------------------|------------------------------------------|-------------------------------------|-----|-----|------|--|--|

| Symbol                                                               | Parameter                                | Conditions                          | Min | Мах | Unit |  |  |

| C <sub>IN</sub>                                                      | Input capacitance                        | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 8   | pF   |  |  |

| C <sub>INCLK</sub>                                                   | Input capacitance on dedicated clock pin | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 12  | pF   |  |  |

| C <sub>OUT</sub>                                                     | Output capacitance                       | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 8   | pF   |  |  |

#### Notes to Tables 23 through 26:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- All APEX 20K devices are 5.0-V tolerant. (2)

- (3) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to 5.75 V for input currents less than 100 mA and periods shorter than 20 ns.

- Numbers in parentheses are for industrial-temperature-range devices. (4)

- Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically. (5)

- All pins, including dedicated inputs, clock I/O, and JTAG pins, may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are (6) powered.

- (7)Typical values are for  $T_A = 25^{\circ}$  C,  $V_{CCINT} = 2.5$  V, and  $V_{CCIO} = 2.5$  or 3.3 V.

- These values are specified in the APEX 20K device recommended operating conditions, shown in Table 26 on (8)page 62.

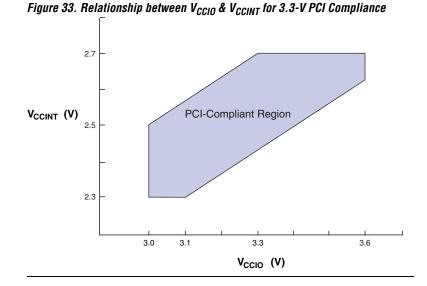

- (9) The APEX 20K input buffers are compatible with 2.5-V and 3.3-V (LVTTL and LVCMOS) signals. Additionally, the input buffers are 3.3-V PCI compliant when V<sub>CCIO</sub> and V<sub>CCINT</sub> meet the relationship shown in Figure 33 on page 68.

- (10) The I<sub>OH</sub> parameter refers to high-level TTL, PCI or CMOS output current.

- (11) The I<sub>OL</sub> parameter refers to low-level TTL, PCI, or CMOS output current. This parameter applies to open-drain pins as well as output pins.

- (12) This value is specified for normal device operation. The value may vary during power-up.

- (13) Pin pull-up resistance values will be lower if an external source drives the pin higher than  $V_{CCIO}$ .

- (14) Capacitance is sample-tested only.

Tables 27 through 30 provide information on absolute maximum ratings, recommended operating conditions, DC operating conditions, and capacitance for 1.8-V APEX 20KE devices.

| Symbol             | Parameter                  | Conditions                                        | Min  | Max | Unit |

|--------------------|----------------------------|---------------------------------------------------|------|-----|------|

| V <sub>CCINT</sub> | Supply voltage             | With respect to ground (2)                        | -0.5 | 2.5 | V    |

| V <sub>CCIO</sub>  |                            |                                                   | -0.5 | 4.6 | V    |

| VI                 | DC input voltage           |                                                   | -0.5 | 4.6 | V    |

| I <sub>OUT</sub>   | DC output current, per pin |                                                   | -25  | 25  | mA   |

| T <sub>STG</sub>   | Storage temperature        | No bias                                           | -65  | 150 | °C   |

| T <sub>AMB</sub>   | Ambient temperature        | Under bias                                        | -65  | 135 | °C   |

| ΤJ                 | Junction temperature       | PQFP, RQFP, TQFP, and BGA packages,<br>under bias |      | 135 | °C   |

|                    |                            | Ceramic PGA packages, under bias                  |      | 150 | °C   |

| Symbol            | Parameter                                                                 | Conditions                                                                           | Min                                  | Тур | Max                                  | Unit |

|-------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------|-----|--------------------------------------|------|

| V <sub>IH</sub>   | High-level LVTTL, CMOS, or 3.3-V<br>PCI input voltage                     |                                                                                      | 1.7, 0.5 × V <sub>CCIO</sub><br>(10) |     | 4.1                                  | V    |

| V <sub>IL</sub>   | Low-level LVTTL, CMOS, or 3.3-V<br>PCI input voltage                      |                                                                                      | -0.5                                 |     | 0.8, 0.3 × V <sub>CCIO</sub><br>(10) | V    |

| V <sub>OH</sub>   | 3.3-V high-level LVTTL output voltage                                     | I <sub>OH</sub> = -12 mA DC,<br>V <sub>CCIO</sub> = 3.00 V <i>(11)</i>               | 2.4                                  |     |                                      | ۷    |

|                   | 3.3-V high-level LVCMOS output voltage                                    | I <sub>OH</sub> = -0.1 mA DC,<br>V <sub>CCIO</sub> = 3.00 V <i>(11)</i>              | V <sub>CCIO</sub> – 0.2              |     |                                      | V    |

|                   | 3.3-V high-level PCI output voltage                                       | I <sub>OH</sub> = -0.5 mA DC,<br>V <sub>CCIO</sub> = 3.00 to 3.60 V<br>( <i>11</i> ) | $0.9 	imes V_{CCIO}$                 |     |                                      | V    |

|                   | 2.5-V high-level output voltage                                           | I <sub>OH</sub> = -0.1 mA DC,<br>V <sub>CCIO</sub> = 2.30 V (11)                     | 2.1                                  |     |                                      | V    |

|                   |                                                                           | I <sub>OH</sub> = -1 mA DC,<br>V <sub>CCIO</sub> = 2.30 V <i>(11)</i>                | 2.0                                  |     |                                      | ۷    |

|                   |                                                                           | I <sub>OH</sub> = -2 mA DC,<br>V <sub>CCIO</sub> = 2.30 V <i>(11)</i>                | 1.7                                  |     |                                      | v    |

| V <sub>OL</sub>   | 3.3-V low-level LVTTL output<br>voltage                                   | I <sub>OL</sub> = 12 mA DC,<br>V <sub>CCIO</sub> = 3.00 V <i>(12)</i>                |                                      |     | 0.4                                  | V    |

|                   | 3.3-V low-level LVCMOS output voltage                                     | I <sub>OL</sub> = 0.1 mA DC,<br>V <sub>CCIO</sub> = 3.00 V ( <i>12</i> )             |                                      |     | 0.2                                  | V    |

|                   | 3.3-V low-level PCI output voltage                                        | I <sub>OL</sub> = 1.5 mA DC,<br>V <sub>CCIO</sub> = 3.00 to 3.60 V<br>( <i>12</i> )  |                                      |     | $0.1 \times V_{CCIO}$                | V    |

|                   | 2.5-V low-level output voltage                                            | I <sub>OL</sub> = 0.1 mA DC,<br>V <sub>CCIO</sub> = 2.30 V <i>(12)</i>               |                                      |     | 0.2                                  | V    |

|                   |                                                                           | I <sub>OL</sub> = 1 mA DC,<br>V <sub>CCIO</sub> = 2.30 V <i>(12)</i>                 |                                      |     | 0.4                                  | V    |

|                   |                                                                           | I <sub>OL</sub> = 2 mA DC,<br>V <sub>CCIO</sub> = 2.30 V <i>(12)</i>                 |                                      |     | 0.7                                  | V    |

| l <sub>l</sub>    | Input pin leakage current                                                 | V <sub>I</sub> = 4.1 to -0.5 V (13)                                                  | -10                                  |     | 10                                   | μA   |

| I <sub>OZ</sub>   | Tri-stated I/O pin leakage current                                        | V <sub>O</sub> = 4.1 to -0.5 V (13)                                                  | -10                                  |     | 10                                   | μΑ   |

| I <sub>CC0</sub>  | V <sub>CC</sub> supply current (standby)<br>(All ESBs in power-down mode) | V <sub>I</sub> = ground, no load, no<br>toggling inputs, -1 speed<br>grade           |                                      | 10  |                                      | mA   |

|                   |                                                                           | V <sub>1</sub> = ground, no load, no<br>toggling inputs,<br>-2, -3 speed grades      |                                      | 5   |                                      | mA   |

| R <sub>CONF</sub> | Value of I/O pin pull-up resistor                                         | V <sub>CCIO</sub> = 3.0 V (14)                                                       | 20                                   |     | 50                                   | kΩ   |

|                   | before and during configuration                                           | V <sub>CCIO</sub> = 2.375 V (14)                                                     | 30                                   |     | 80                                   | kΩ   |

|                   |                                                                           | V <sub>CCIO</sub> = 1.71 V (14)                                                      | 60                                   |     | 150                                  | kΩ   |

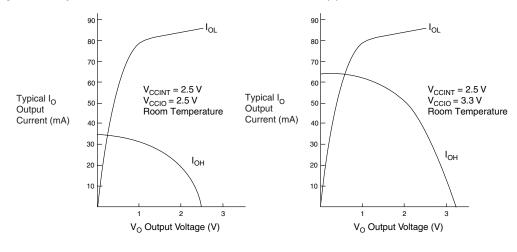

Figure 34 shows the typical output drive characteristics of APEX 20K devices with 3.3-V and 2.5-V V<sub>CCIO</sub>. The output driver is compatible with the 3.3-V *PCI Local Bus Specification, Revision 2.2* (when VCCIO pins are connected to 3.3 V). 5-V tolerant APEX 20K devices in the -1 speed grade are 5-V PCI compliant over all operating conditions.

**Altera Corporation**

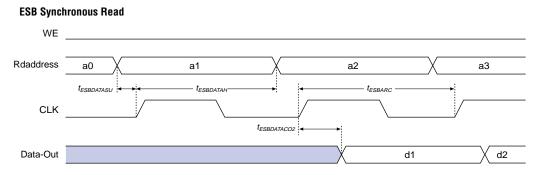

Figure 39. ESB Synchronous Timing Waveforms

#### ESB Synchronous Write (ESB Output Registers Used)

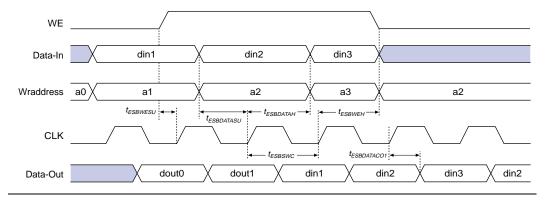

Figure 40 shows the timing model for bidirectional I/O pin timing.

### Figure 40. Synchronous Bidirectional Pin External Timing

#### Notes to Figure 40:

- (1) The output enable and input registers are LE registers in the LAB adjacent to a bidirectional row pin. The output enable register is set with "Output Enable Routing= Signal-Pin" option in the Quartus II software.

- (2) The LAB adjacent input register is set with "Decrease Input Delay to Internal Cells= Off". This maintains a zero hold time for lab adjacent registers while giving a fast, position independent setup time. A faster setup time with zero hold time is possible by setting "Decrease Input Delay to Internal Cells= ON" and moving the input register farther away from the bidirectional pin. The exact position where zero hold occurs with the minimum setup time, varies with device density and speed grade.

Table 31 describes the  $f_{MAX}$  timing parameters shown in Figure 36 on page 68.

| Table 31. APEX 20K f <sub>MAX</sub> Timing Parameters (Part 1 of 2) |                                                                |  |  |  |  |  |

|---------------------------------------------------------------------|----------------------------------------------------------------|--|--|--|--|--|

| Symbol                                                              | Parameter                                                      |  |  |  |  |  |

| t <sub>SU</sub>                                                     | LE register setup time before clock                            |  |  |  |  |  |

| t <sub>H</sub>                                                      | LE register hold time after clock                              |  |  |  |  |  |

| t <sub>CO</sub>                                                     | LE register clock-to-output delay                              |  |  |  |  |  |

| t <sub>LUT</sub>                                                    | LUT delay for data-in                                          |  |  |  |  |  |

| t <sub>ESBRC</sub>                                                  | ESB Asynchronous read cycle time                               |  |  |  |  |  |

| t <sub>ESBWC</sub>                                                  | ESB Asynchronous write cycle time                              |  |  |  |  |  |

| t <sub>ESBWESU</sub>                                                | ESB WE setup time before clock when using input register       |  |  |  |  |  |

| t <sub>ESBDATASU</sub>                                              | ESB data setup time before clock when using input register     |  |  |  |  |  |

| t <sub>ESBDATAH</sub>                                               | ESB data hold time after clock when using input register       |  |  |  |  |  |

| t <sub>ESBADDRSU</sub>                                              | ESB address setup time before clock when using input registers |  |  |  |  |  |

| t <sub>ESBDATACO1</sub>                                             | ESB clock-to-output delay when using output registers          |  |  |  |  |  |

| Symbol                      | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|-----------------------------|----------------|-----|----------------|-----|----------------|-----|------|

|                             | Min            | Max | Min            | Max | Min            | Max |      |

| t <sub>INSUBIDIR</sub> (1)  | 1.9            |     | 2.3            |     | 2.6            |     | ns   |

| t <sub>INHBIDIR</sub> (1)   | 0.0            |     | 0.0            |     | 0.0            |     | ns   |

| t <sub>OUTCOBIDIR</sub> (1) | 2.0            | 4.6 | 2.0            | 5.6 | 2.0            | 6.8 | ns   |

| t <sub>XZBIDIR</sub> (1)    |                | 5.0 |                | 5.9 |                | 6.9 | ns   |

| t <sub>ZXBIDIR</sub> (1)    |                | 5.0 |                | 5.9 |                | 6.9 | ns   |

| t <sub>INSUBIDIR</sub> (2)  | 1.1            |     | 1.2            |     | -              |     | ns   |

| t <sub>INHBIDIR</sub> (2)   | 0.0            |     | 0.0            |     | -              |     | ns   |

| t <sub>OUTCOBIDIR</sub> (2) | 0.5            | 2.7 | 0.5            | 3.1 | -              | -   | ns   |

| t <sub>XZBIDIR</sub> (2)    |                | 4.3 |                | 5.0 |                | -   | ns   |

| t <sub>ZXBIDIR</sub> (2)    |                | 4.3 |                | 5.0 |                | -   | ns   |

### Table 47. EP20K400 External Timing Parameters

| Symbol                 | -1 Speed Grade |     | -2 Spee | -2 Speed Grade |     | -3 Speed Grade |    |  |  |

|------------------------|----------------|-----|---------|----------------|-----|----------------|----|--|--|

|                        | Min            | Max | Min     | Max            | Min | Max            |    |  |  |

| t <sub>INSU</sub> (1)  | 1.4            |     | 1.8     |                | 2.0 |                | ns |  |  |

| t <sub>INH</sub> (1)   | 0.0            |     | 0.0     |                | 0.0 |                | ns |  |  |

| t <sub>OUTCO</sub> (1) | 2.0            | 4.9 | 2.0     | 6.1            | 2.0 | 7.0            | ns |  |  |

| t <sub>INSU</sub> (2)  | 0.4            |     | 1.0     |                | -   |                | ns |  |  |

| t <sub>INH</sub> (2)   | 0.0            |     | 0.0     |                | -   |                | ns |  |  |

| t <sub>оитсо</sub> (2) | 0.5            | 3.1 | 0.5     | 4.1            | -   | -              | ns |  |  |

Table 48. EP20K400 External Bidirectional Timing Parameters

| Symbol                      | -1 Spee | d Grade | -2 Spe | ed Grade | -3 Spe | ed Grade | Unit |

|-----------------------------|---------|---------|--------|----------|--------|----------|------|

|                             | Min     | Max     | Min    | Max      | Min    | Max      |      |

| t <sub>INSUBIDIR</sub> (1)  | 1.4     |         | 1.8    |          | 2.0    |          | ns   |

| t <sub>INHBIDIR</sub> (1)   | 0.0     |         | 0.0    |          | 0.0    |          | ns   |

| t <sub>OUTCOBIDIR</sub> (1) | 2.0     | 4.9     | 2.0    | 6.1      | 2.0    | 7.0      | ns   |

| t <sub>XZBIDIR</sub> (1)    |         | 7.3     |        | 8.9      |        | 10.3     | ns   |

| t <sub>ZXBIDIR</sub> (1)    |         | 7.3     |        | 8.9      |        | 10.3     | ns   |

| t <sub>INSUBIDIR</sub> (2)  | 0.5     |         | 1.0    |          | -      |          | ns   |

| t <sub>INHBIDIR</sub> (2)   | 0.0     |         | 0.0    |          | -      |          | ns   |

| t <sub>OUTCOBIDIR</sub> (2) | 0.5     | 3.1     | 0.5    | 4.1      | -      | -        | ns   |

| t <sub>XZBIDIR</sub> (2)    |         | 6.2     |        | 7.6      |        | -        | ns   |

| t <sub>ZXBIDIR</sub> (2)    |         | 6.2     |        | 7.6      |        | -        | ns   |

#### **Altera Corporation**

| Symbol             | -1   |     | -    | -2  |      | -3  |    |

|--------------------|------|-----|------|-----|------|-----|----|

|                    | Min  | Max | Min  | Max | Min  | Max |    |

| t <sub>CH</sub>    | 2.00 |     | 2.00 |     | 2.00 |     | ns |

| t <sub>CL</sub>    | 2.00 |     | 2.00 |     | 2.00 |     | ns |

| t <sub>CLRP</sub>  | 0.20 |     | 0.20 |     | 0.20 |     | ns |

| t <sub>PREP</sub>  | 0.20 |     | 0.20 |     | 0.20 |     | ns |

| t <sub>ESBCH</sub> | 2.00 |     | 2.00 |     | 2.00 |     | ns |

| t <sub>ESBCL</sub> | 2.00 |     | 2.00 |     | 2.00 |     | ns |

| t <sub>ESBWP</sub> | 1.29 |     | 1.53 |     | 1.66 |     | ns |

| t <sub>ESBRP</sub> | 1.11 |     | 1.29 |     | 1.41 |     | ns |

| Table 65. EP2         | 20K100E Extern | nal Timing Pa | rameters |      |      |      |      |

|-----------------------|----------------|---------------|----------|------|------|------|------|

| Symbol                | ol -1          | 1             |          | -2   | -3   |      | Unit |

|                       | Min            | Max           | Min      | Max  | Min  | Max  |      |

| t <sub>INSU</sub>     | 2.23           |               | 2.32     |      | 2.43 |      | ns   |

| t <sub>INH</sub>      | 0.00           |               | 0.00     |      | 0.00 |      | ns   |

| t <sub>outco</sub>    | 2.00           | 4.86          | 2.00     | 5.35 | 2.00 | 5.84 | ns   |

| t <sub>INSUPLL</sub>  | 1.58           |               | 1.66     |      | -    |      | ns   |

| t <sub>INHPLL</sub>   | 0.00           |               | 0.00     |      | -    |      | ns   |

| t <sub>outcopll</sub> | 0.50           | 2.96          | 0.50     | 3.29 | -    | -    | ns   |

| Symbol                     | -1   |      | -2   |      | -    | Unit |    |

|----------------------------|------|------|------|------|------|------|----|

| Γ                          | Min  | Max  | Min  | Max  | Min  | Max  |    |

| t <sub>insubidir</sub>     | 2.74 |      | 2.96 |      | 3.19 |      | ns |

| t <sub>inhbidir</sub>      | 0.00 |      | 0.00 |      | 0.00 |      | ns |

| t <sub>оитсовідія</sub>    | 2.00 | 4.86 | 2.00 | 5.35 | 2.00 | 5.84 | ns |

| t <sub>xzbidir</sub>       |      | 5.00 |      | 5.48 |      | 5.89 | ns |

| t <sub>zxbidir</sub>       |      | 5.00 |      | 5.48 |      | 5.89 | ns |

| t <sub>insubidirpll</sub>  | 4.64 |      | 5.03 |      | -    |      | ns |

| t <sub>inhbidirpll</sub>   | 0.00 |      | 0.00 |      | -    |      | ns |

| t <sub>outcobidirpll</sub> | 0.50 | 2.96 | 0.50 | 3.29 | -    | -    | ns |

| t <sub>xzbidirpll</sub>    |      | 3.10 |      | 3.42 |      | -    | ns |

| t <sub>ZXBIDIRPLL</sub>    |      | 3.10 |      | 3.42 |      | -    | ns |

| Symbol             | -1   |     | -    | -2  |      | -3  |    |

|--------------------|------|-----|------|-----|------|-----|----|

|                    | Min  | Max | Min  | Max | Min  | Max |    |

| t <sub>CH</sub>    | 1.36 |     | 2.44 |     | 2.65 |     | ns |

| t <sub>CL</sub>    | 1.36 |     | 2.44 |     | 2.65 |     | ns |

| t <sub>CLRP</sub>  | 0.18 |     | 0.19 |     | 0.21 |     | ns |

| t <sub>PREP</sub>  | 0.18 |     | 0.19 |     | 0.21 |     | ns |

| t <sub>ESBCH</sub> | 1.36 |     | 2.44 |     | 2.65 |     | ns |

| t <sub>ESBCL</sub> | 1.36 |     | 2.44 |     | 2.65 |     | ns |

| t <sub>ESBWP</sub> | 1.18 |     | 1.48 |     | 1.76 |     | ns |

| t <sub>ESBRP</sub> | 0.95 |     | 1.17 |     | 1.41 |     | ns |

| Table 77. EP2         | 20K200E Extern | nal Timing Pa | rameters |      |      |      |      |

|-----------------------|----------------|---------------|----------|------|------|------|------|

| Symbol                | -              | 1             | ,        | -2   | -3   | 3    | Unit |

|                       | Min            | Max           | Min      | Max  | Min  | Max  |      |

| t <sub>INSU</sub>     | 2.24           |               | 2.35     |      | 2.47 |      | ns   |

| t <sub>INH</sub>      | 0.00           |               | 0.00     |      | 0.00 |      | ns   |

| t <sub>outco</sub>    | 2.00           | 5.12          | 2.00     | 5.62 | 2.00 | 6.11 | ns   |

| t <sub>INSUPLL</sub>  | 2.13           |               | 2.07     |      | -    |      | ns   |

| t <sub>INHPLL</sub>   | 0.00           |               | 0.00     |      | -    |      | ns   |

| t <sub>outcopll</sub> | 0.50           | 3.01          | 0.50     | 3.36 | -    | -    | ns   |

| Symbol                     | -1 Speed Grade |      | -2 Spee | d Grade | -3 Spee | Unit |    |

|----------------------------|----------------|------|---------|---------|---------|------|----|

| -                          | Min            | Max  | Min     | Max     | Min     | Max  |    |

| t <sub>insubidir</sub>     | 2.93           |      | 3.23    |         | 3.44    |      | ns |

| t <sub>inhbidir</sub>      | 0.00           |      | 0.00    |         | 0.00    |      | ns |

| toutcobidir                | 2.00           | 5.25 | 2.00    | 5.79    | 2.00    | 6.32 | ns |

| t <sub>XZBIDIR</sub>       |                | 5.95 |         | 6.77    |         | 7.12 | ns |

| t <sub>zxbidir</sub>       |                | 5.95 |         | 6.77    |         | 7.12 | ns |

| t <sub>insubidirpll</sub>  | 4.31           |      | 4.76    |         | -       |      | ns |

| t <sub>inhbidirpll</sub>   | 0.00           |      | 0.00    |         | -       |      | ns |

| t <sub>outcobidirpll</sub> | 0.50           | 2.25 | 0.50    | 2.45    | -       | -    | ns |

| t <sub>xzbidirpll</sub>    |                | 2.94 |         | 3.43    |         | -    | ns |

| t <sub>zxbidirpll</sub>    |                | 2.94 |         | 3.43    |         | -    | ns |

Tables 91 through 96 describe  $f_{MAX}$  LE Timing Microparameters,  $f_{MAX}$  ESB Timing Microparameters,  $f_{MAX}$  Routing Delays, Minimum Pulse Width Timing Parameters, External Timing Parameters, and External Bidirectional Timing Parameters for EP20K600E APEX 20KE devices.

| Table 91. EP2    | OK600E f <sub>MAX</sub> I | LE Timing Mid | roparameters | 5        |         |         |      |

|------------------|---------------------------|---------------|--------------|----------|---------|---------|------|

| Symbol           | -1 Spee                   | d Grade       | -2 Spee      | ed Grade | -3 Spee | d Grade | Unit |

|                  | Min                       | Max           | Min          | Max      | Min     | Max     |      |

| t <sub>SU</sub>  | 0.16                      |               | 0.16         |          | 0.17    |         | ns   |

| t <sub>H</sub>   | 0.29                      |               | 0.33         |          | 0.37    |         | ns   |

| t <sub>CO</sub>  |                           | 0.65          |              | 0.38     |         | 0.49    | ns   |

| t <sub>LUT</sub> |                           | 0.70          |              | 1.00     |         | 1.30    | ns   |

Т

| Symbol             | -1 Speed Grade |     | -2 Spee | -2 Speed Grade |      | -3 Speed Grade |    |  |

|--------------------|----------------|-----|---------|----------------|------|----------------|----|--|

|                    | Min            | Max | Min     | Max            | Min  | Max            |    |  |

| t <sub>CH</sub>    | 2.00           |     | 2.50    |                | 2.75 |                | ns |  |

| t <sub>CL</sub>    | 2.00           |     | 2.50    |                | 2.75 |                | ns |  |

| t <sub>CLRP</sub>  | 0.18           |     | 0.26    |                | 0.34 |                | ns |  |

| t <sub>PREP</sub>  | 0.18           |     | 0.26    |                | 0.34 |                | ns |  |

| t <sub>ESBCH</sub> | 2.00           |     | 2.50    |                | 2.75 |                | ns |  |

| t <sub>ESBCL</sub> | 2.00           |     | 2.50    |                | 2.75 |                | ns |  |

| t <sub>ESBWP</sub> | 1.17           |     | 1.68    |                | 2.18 |                | ns |  |

| t <sub>ESBRP</sub> | 0.95           |     | 1.35    |                | 1.76 |                | ns |  |

| Symbol              | -1 Spee | d Grade | -2 Spee | d Grade | -3 Speed Grade |      | Unit |  |

|---------------------|---------|---------|---------|---------|----------------|------|------|--|

|                     | Min     | Max     | Min     | Max     | Min            | Max  |      |  |

| t <sub>INSU</sub>   | 2.74    |         | 2.74    |         | 2.87           |      | ns   |  |

| t <sub>INH</sub>    | 0.00    |         | 0.00    |         | 0.00           |      | ns   |  |

| toutco              | 2.00    | 5.51    | 2.00    | 6.06    | 2.00           | 6.61 | ns   |  |

| tINSUPLL            | 1.86    |         | 1.96    |         | -              |      | ns   |  |

| t <sub>INHPLL</sub> | 0.00    |         | 0.00    |         | -              |      | ns   |  |

| toutcopll           | 0.50    | 2.62    | 0.50    | 2.91    | -              | -    | ns   |  |

| Symbol                    | -1 Speed Grade |      | -2 Speed Grade |      | -3 Spee | Unit |    |

|---------------------------|----------------|------|----------------|------|---------|------|----|

|                           | Min            | Max  | Min            | Max  | Min     | Max  |    |

| t <sub>insubidir</sub>    | 0.64           |      | 0.98           |      | 1.08    |      | ns |

| t <sub>inhbidir</sub>     | 0.00           |      | 0.00           |      | 0.00    |      | ns |

| toutcobidir               | 2.00           | 5.51 | 2.00           | 6.06 | 2.00    | 6.61 | ns |

| t <sub>xzbidir</sub>      |                | 6.10 |                | 6.74 |         | 7.10 | ns |

| t <sub>zxbidir</sub>      |                | 6.10 |                | 6.74 |         | 7.10 | ns |

| t <sub>insubidirpll</sub> | 2.26           |      | 2.68           |      | -       |      | ns |

| t <sub>inhbidirpll</sub>  | 0.00           |      | 0.00           |      | -       |      | ns |

| toutcobidirpll            | 0.50           | 2.62 | 0.50           | 2.91 | -       | -    | ns |

| t <sub>xzbidirpll</sub>   |                | 3.21 |                | 3.59 |         | -    | ns |

| t <sub>ZXBIDIRPLL</sub>   |                | 3.21 |                | 3.59 |         | -    | ns |

| Table 108. EP20K15         | 00E External | Bidirectional | Timing Para | meters  |         |          |      |

|----------------------------|--------------|---------------|-------------|---------|---------|----------|------|

| Symbol                     | -1 Spee      | d Grade       | -2 Spee     | d Grade | -3 Spee | ed Grade | Unit |

|                            | Min          | Мах           | Min         | Max     | Min     | Max      |      |

| t <sub>insubidir</sub>     | 3.47         |               | 3.68        |         | 3.99    |          | ns   |

| t <sub>inhbidir</sub>      | 0.00         |               | 0.00        |         | 0.00    |          | ns   |

| t <sub>outcobidir</sub>    | 2.00         | 6.18          | 2.00        | 6.81    | 2.00    | 7.36     | ns   |

| t <sub>XZBIDIR</sub>       |              | 6.91          |             | 7.62    |         | 8.38     | ns   |

| t <sub>ZXBIDIR</sub>       |              | 6.91          |             | 7.62    |         | 8.38     | ns   |

| t <sub>insubidirpll</sub>  | 3.05         |               | 3.26        |         |         |          | ns   |

| t <sub>inhbidirpll</sub>   | 0.00         |               | 0.00        |         |         |          | ns   |

| t <sub>outcobidirpll</sub> | 0.50         | 2.67          | 0.50        | 2.99    |         |          | ns   |

| t <sub>xzbidirpll</sub>    |              | 3.41          |             | 3.80    |         |          | ns   |

| t <sub>ZXBIDIRPLL</sub>    |              | 3.41          |             | 3.80    |         |          | ns   |

Tables 109 and 110 show selectable I/O standard input and output delays for APEX 20KE devices. If you select an I/O standard input or output delay other than LVCMOS, add or subtract the selected speed grade to or from the LVCMOS value.

| Table 109. Selectable I/O Standard Input Delays |                |       |                |       |                |       |      |

|-------------------------------------------------|----------------|-------|----------------|-------|----------------|-------|------|

| Symbol                                          | -1 Speed Grade |       | -2 Speed Grade |       | -3 Speed Grade |       | Unit |

|                                                 | Min            | Max   | Min            | Max   | Min            | Max   | Min  |

| LVCMOS                                          |                | 0.00  |                | 0.00  |                | 0.00  | ns   |

| LVTTL                                           |                | 0.00  |                | 0.00  |                | 0.00  | ns   |

| 2.5 V                                           |                | 0.00  |                | 0.04  |                | 0.05  | ns   |

| 1.8 V                                           |                | -0.11 |                | 0.03  |                | 0.04  | ns   |

| PCI                                             |                | 0.01  |                | 0.09  |                | 0.10  | ns   |

| GTL+                                            |                | -0.24 |                | -0.23 |                | -0.19 | ns   |

| SSTL-3 Class I                                  |                | -0.32 |                | -0.21 |                | -0.47 | ns   |

| SSTL-3 Class II                                 |                | -0.08 |                | 0.03  |                | -0.23 | ns   |

| SSTL-2 Class I                                  |                | -0.17 |                | -0.06 |                | -0.32 | ns   |

| SSTL-2 Class II                                 |                | -0.16 |                | -0.05 |                | -0.31 | ns   |

| LVDS                                            |                | -0.12 |                | -0.12 |                | -0.12 | ns   |

| CTT                                             |                | 0.00  |                | 0.00  |                | 0.00  | ns   |

| AGP                                             |                | 0.00  |                | 0.00  |                | 0.00  | ns   |

Г