# E·XFL

# Intel - EP20K60EQC208-3N Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 2560                                                        |

| Number of Logic Elements/Cells | 2560                                                        |

| Total RAM Bits                 | 32768                                                       |

| Number of I/O                  | 148                                                         |

| Number of Gates                | 162000                                                      |

| Voltage - Supply               | 1.71V ~ 1.89V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 208-BFQFP                                                   |

| Supplier Device Package        | 208-PQFP (28x28)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep20k60eqc208-3n |

|                                |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Logic Element

The LE, the smallest unit of logic in the APEX 20K architecture, is compact and provides efficient logic usage. Each LE contains a four-input LUT, which is a function generator that can quickly implement any function of four variables. In addition, each LE contains a programmable register and carry and cascade chains. Each LE drives the local interconnect, MegaLAB interconnect, and FastTrack Interconnect routing structures. See Figure 5.

Each LE's programmable register can be configured for D, T, JK, or SR operation. The register's clock and clear control signals can be driven by global signals, general-purpose I/O pins, or any internal logic. For combinatorial functions, the register is bypassed and the output of the LUT drives the outputs of the LE.

Each LE has two outputs that drive the local, MegaLAB, or FastTrack Interconnect routing structure. Each output can be driven independently by the LUT's or register's output. For example, the LUT can drive one output while the register drives the other output. This feature, called register packing, improves device utilization because the register and the LUT can be used for unrelated functions. The LE can also drive out registered and unregistered versions of the LUT output.

The APEX 20K architecture provides two types of dedicated high-speed data paths that connect adjacent LEs without using local interconnect paths: carry chains and cascade chains. A carry chain supports high-speed arithmetic functions such as counters and adders, while a cascade chain implements wide-input functions such as equality comparators with minimum delay. Carry and cascade chains connect LEs 1 through 10 in an LAB and all LABs in the same MegaLAB structure.

### Carry Chain

The carry chain provides a very fast carry-forward function between LEs. The carry-in signal from a lower-order bit drives forward into the higherorder bit via the carry chain, and feeds into both the LUT and the next portion of the carry chain. This feature allows the APEX 20K architecture to implement high-speed counters, adders, and comparators of arbitrary width. Carry chain logic can be created automatically by the Quartus II software Compiler during design processing, or manually by the designer during design entry. Parameterized functions such as library of parameterized modules (LPM) and DesignWare functions automatically take advantage of carry chains for the appropriate functions.

The Quartus II software Compiler creates carry chains longer than ten LEs by linking LABs together automatically. For enhanced fitting, a long carry chain skips alternate LABs in a MegaLAB<sup>™</sup> structure. A carry chain longer than one LAB skips either from an even-numbered LAB to the next even-numbered LAB, or from an odd-numbered LAB to the next odd-numbered LAB. For example, the last LE of the first LAB in the upper-left MegaLAB structure carries to the first LE of the third LAB in the MegaLAB structure.

Figure 6 shows how an *n*-bit full adder can be implemented in n + 1 LEs with the carry chain. One portion of the LUT generates the sum of two bits using the input signals and the carry-in signal; the sum is routed to the output of the LE. The register can be bypassed for simple adders or used for accumulator functions. Another portion of the LUT and the carry chain logic generates the carry-out signal, which is routed directly to the carry-in signal of the next-higher-order bit. The final carry-out signal is routed to an LE, where it is driven onto the local, MegaLAB, or FastTrack Interconnect routing structures.

#### Cascade Chain

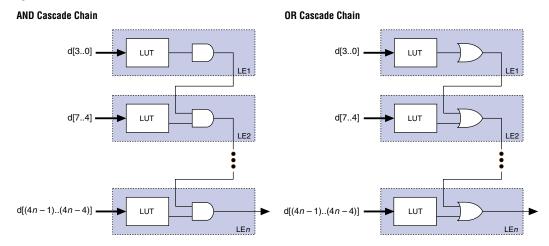

With the cascade chain, the APEX 20K architecture can implement functions with a very wide fan-in. Adjacent LUTs can compute portions of a function in parallel; the cascade chain serially connects the intermediate values. The cascade chain can use a logical AND or logical OR (via De Morgan's inversion) to connect the outputs of adjacent LEs. Each additional LE provides four more inputs to the effective width of a function, with a short cascade delay. Cascade chain logic can be created automatically by the Quartus II software Compiler during design processing, or manually by the designer during design entry.

Cascade chains longer than ten LEs are implemented automatically by linking LABs together. For enhanced fitting, a long cascade chain skips alternate LABs in a MegaLAB structure. A cascade chain longer than one LAB skips either from an even-numbered LAB to the next even-numbered LAB, or from an odd-numbered LAB to the next odd-numbered LAB. For example, the last LE of the first LAB in the upper-left MegaLAB structure carries to the first LE of the third LAB in the MegaLAB structure. Figure 7 shows how the cascade function can connect adjacent LEs to form functions with a wide fan-in.

Figure 7. APEX 20K Cascade Chain

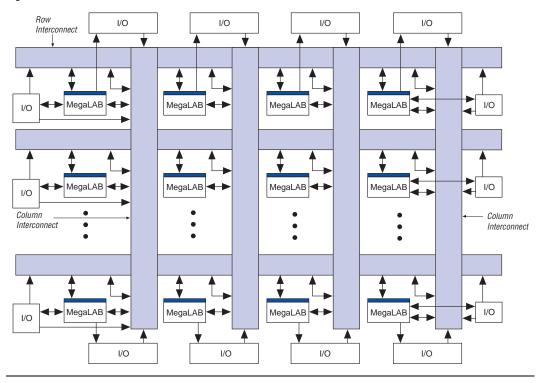

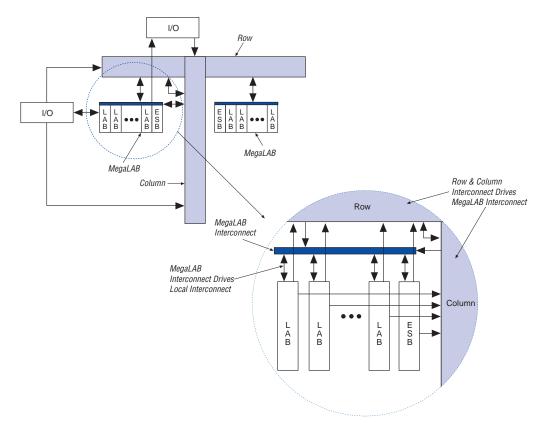

A row line can be driven directly by LEs, IOEs, or ESBs in that row. Further, a column line can drive a row line, allowing an LE, IOE, or ESB to drive elements in a different row via the column and row interconnect. The row interconnect drives the MegaLAB interconnect to drive LEs, IOEs, or ESBs in a particular MegaLAB structure.

A column line can be directly driven by LEs, IOEs, or ESBs in that column. A column line on a device's left or right edge can also be driven by row IOEs. The column line is used to route signals from one row to another. A column line can drive a row line; it can also drive the MegaLAB interconnect directly, allowing faster connections between rows.

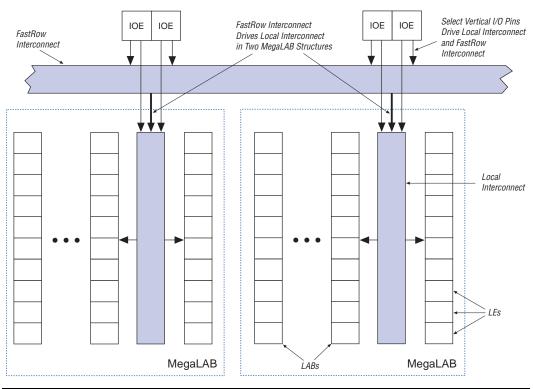

Figure 10 shows how the FastTrack Interconnect uses the local interconnect to drive LEs within MegaLAB structures.

Figure 10. FastTrack Connection to Local Interconnect

Figure 12. APEX 20KE FastRow Interconnect

Table 9 summarizes how various elements of the APEX 20K architecture drive each other.

| Table 9. AP                         | EX 20K         | Routing S         | cheme |     |                       |                         |                                  |                                     |                         |  |  |  |

|-------------------------------------|----------------|-------------------|-------|-----|-----------------------|-------------------------|----------------------------------|-------------------------------------|-------------------------|--|--|--|

| Source                              | Destination    |                   |       |     |                       |                         |                                  |                                     |                         |  |  |  |

|                                     | Row<br>I/O Pin | Column<br>I/O Pin | LE    | ESB | Local<br>Interconnect | MegaLAB<br>Interconnect | Row<br>FastTrack<br>Interconnect | Column<br>FastTrack<br>Interconnect | FastRow<br>Interconnect |  |  |  |

| Row I/O Pin                         |                |                   |       |     | ~                     | $\checkmark$            | ✓                                | ~                                   |                         |  |  |  |

| Column I/O<br>Pin                   |                |                   |       |     |                       |                         |                                  | ~                                   | ✓<br>(1)                |  |  |  |

| LE                                  |                |                   |       |     | $\checkmark$          | $\checkmark$            | $\checkmark$                     | $\checkmark$                        |                         |  |  |  |

| ESB                                 |                |                   |       |     | <ul> <li></li> </ul>  | ~                       | ~                                | ~                                   |                         |  |  |  |

| Local<br>Interconnect               | ~              | ~                 | ~     | ~   |                       |                         |                                  |                                     |                         |  |  |  |

| MegaLAB<br>Interconnect             |                |                   |       |     | ~                     |                         |                                  |                                     |                         |  |  |  |

| Row<br>FastTrack<br>Interconnect    |                |                   |       |     |                       | ~                       |                                  | ~                                   |                         |  |  |  |

| Column<br>FastTrack<br>Interconnect |                |                   |       |     |                       | ~                       | ~                                |                                     |                         |  |  |  |

| FastRow<br>Interconnect             |                |                   |       |     | ✓<br>(1)              |                         |                                  |                                     |                         |  |  |  |

#### Note to Table 9:

(1) This connection is supported in APEX 20KE devices only.

## Product-Term Logic

The product-term portion of the MultiCore architecture is implemented with the ESB. The ESB can be configured to act as a block of macrocells on an ESB-by-ESB basis. Each ESB is fed by 32 inputs from the adjacent local interconnect; therefore, it can be driven by the MegaLAB interconnect or the adjacent LAB. Also, nine ESB macrocells feed back into the ESB through the local interconnect for higher performance. Dedicated clock pins, global signals, and additional inputs from the local interconnect drive the ESB control signals.

In product-term mode, each ESB contains 16 macrocells. Each macrocell consists of two product terms and a programmable register. Figure 13 shows the ESB in product-term mode.

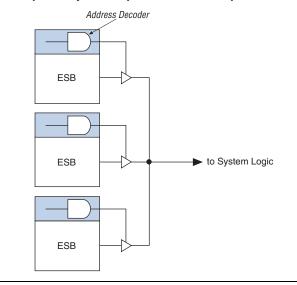

Figure 18. Deep Memory Block Implemented with Multiple ESBs

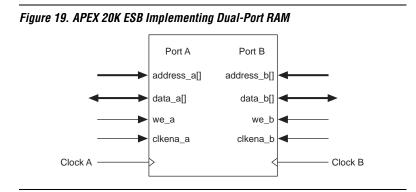

The ESB implements two forms of dual-port memory: read/write clock mode and input/output clock mode. The ESB can also be used for bidirectional, dual-port memory applications in which two ports read or write simultaneously. To implement this type of dual-port memory, two or four ESBs are used to support two simultaneous reads or writes. This functionality is shown in Figure 19.

For more information on APEX 20KE devices and CAM, see *Application* Note 119 (Implementing High-Speed Search Applications with APEX CAM).

# **Driving Signals to the ESB**

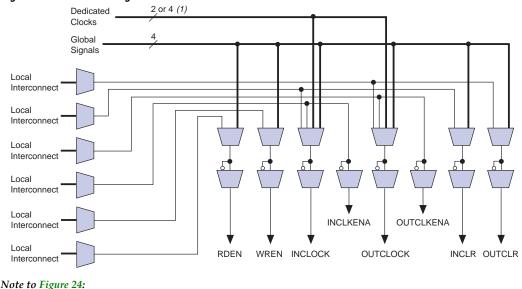

ESBs provide flexible options for driving control signals. Different clocks can be used for the ESB inputs and outputs. Registers can be inserted independently on the data input, data output, read address, write address, WE, and RE signals. The global signals and the local interconnect can drive the WE and RE signals. The global signals, dedicated clock pins, and local interconnect can drive the ESB clock signals. Because the LEs drive the local interconnect, the LEs can control the WE and RE signals and the ESB clock, clock enable, and asynchronous clear signals. Figure 24 shows the ESB control signal generation logic.

(1) APEX 20KE devices have four dedicated clocks.

An ESB is fed by the local interconnect, which is driven by adjacent LEs (for high-speed connection to the ESB) or the MegaLAB interconnect. The ESB can drive the local, MegaLAB, or FastTrack Interconnect routing structure to drive LEs and IOEs in the same MegaLAB structure or anywhere in the device.

# Implementing Logic in ROM

In addition to implementing logic with product terms, the ESB can implement logic functions when it is programmed with a read-only pattern during configuration, creating a large LUT. With LUTs, combinatorial functions are implemented by looking up the results, rather than by computing them. This implementation of combinatorial functions can be faster than using algorithms implemented in general logic, a performance advantage that is further enhanced by the fast access times of ESBs. The large capacity of ESBs enables designers to implement complex functions in one logic level without the routing delays associated with linked LEs or distributed RAM blocks. Parameterized functions such as LPM functions can take advantage of the ESB automatically. Further, the Quartus II software can implement portions of a design with ESBs where appropriate.

# **Programmable Speed/Power Control**

APEX 20K ESBs offer a high-speed mode that supports very fast operation on an ESB-by-ESB basis. When high speed is not required, this feature can be turned off to reduce the ESB's power dissipation by up to 50%. ESBs that run at low power incur a nominal timing delay adder. This Turbo Bit<sup>™</sup> option is available for ESBs that implement product-term logic or memory functions. An ESB that is not used will be powered down so that it does not consume DC current.

Designers can program each ESB in the APEX 20K device for either high-speed or low-power operation. As a result, speed-critical paths in the design can run at high speed, while the remaining paths operate at reduced power.

# I/O Structure

The APEX 20K IOE contains a bidirectional I/O buffer and a register that can be used either as an input register for external data requiring fast setup times, or as an output register for data requiring fast clock-to-output performance. IOEs can be used as input, output, or bidirectional pins. For fast bidirectional I/O timing, LE registers using local routing can improve setup times and OE timing. The Quartus II software Compiler uses the programmable inversion option to invert signals from the row and column interconnect automatically where appropriate. Because the APEX 20K IOE offers one output enable per pin, the Quartus II software Compiler can emulate open-drain operation efficiently.

The APEX 20K IOE includes programmable delays that can be activated to ensure zero hold times, minimum clock-to-output times, input IOE register-to-core register transfers, or core-to-output IOE register transfers. A path in which a pin directly drives a register may require the delay to ensure zero hold time, whereas a path in which a pin drives a register through combinatorial logic may not require the delay.

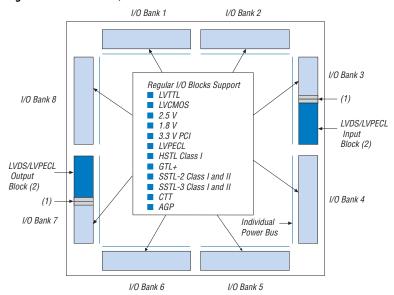

#### Figure 29. APEX 20KE I/O Banks

#### Notes to Figure 29:

- For more information on placing I/O pins in LVDS blocks, refer to the Guidelines for Using LVDS Blocks section in Application Note 120 (Using LVDS in APEX 20KE Devices).

- (2) If the LVDS input and output blocks are not used for LVDS, they can support all of the I/O standards and can be used as input, output, or bidirectional pins with V<sub>CCIO</sub> set to 3.3 V, 2.5 V, or 1.8 V.

## Power Sequencing & Hot Socketing

Because APEX 20K and APEX 20KE devices can be used in a mixedvoltage environment, they have been designed specifically to tolerate any possible power-up sequence. Therefore, the  $V_{CCIO}$  and  $V_{CCINT}$  power supplies may be powered in any order.

For more information, please refer to the "Power Sequencing Considerations" section in the *Configuring APEX 20KE & APEX 20KC Devices* chapter of the *Configuration Devices Handbook*.

Signals can be driven into APEX 20K devices before and during power-up without damaging the device. In addition, APEX 20K devices do not drive out during power-up. Once operating conditions are reached and the device is configured, APEX 20K and APEX 20KE devices operate as specified by the user.

APEX 20KE devices also support the MultiVolt I/O interface feature. The APEX 20KE VCCINT pins must always be connected to a 1.8-V power supply. With a 1.8-V V<sub>CCINT</sub> level, input pins are 1.8-V, 2.5-V, and 3.3-V tolerant. The VCCIO pins can be connected to either a 1.8-V, 2.5-V, or 3.3-V power supply, depending on the I/O standard requirements. When the VCCIO pins are connected to a 1.8-V power supply, the output levels are compatible with 1.8-V systems. When VCCIO pins are connected to a 2.5-V power supply, the output levels are compatible with 2.5-V systems. When VCCIO pins are connected to a 3.3-V power supply, the output levels are sometime with 2.5-V systems. When VCCIO pins are connected to a 3.3-V power supply, the output high is 3.3 V and compatible with 3.3-V or 5.0-V systems. An APEX 20KE device is 5.0-V tolerant with the addition of a resistor.

### Table 13 summarizes APEX 20KE MultiVolt I/O support.

| Table 13. A           | APEX 20KE I  | MultiVolt I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Support /    | Vote (1) |              |              |              |     |

|-----------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------|--------------|--------------|--------------|-----|

| V <sub>CCIO</sub> (V) |              | Input Sig                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | gnals (V)    |          |              | Output S     | ignals (V)   |     |

|                       | 1.8          | 2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.3          | 5.0      | 1.8          | 2.5          | 3.3          | 5.0 |

| 1.8                   | $\checkmark$ | <ul> <li>Image: A start of the start of</li></ul> | $\checkmark$ |          | $\checkmark$ |              |              |     |

| 2.5                   | $\checkmark$ | $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $\checkmark$ |          |              | $\checkmark$ |              |     |

| 3.3                   | $\checkmark$ | $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $\checkmark$ | (2)      |              |              | <b>√</b> (3) |     |

#### Notes to Table 13:

The PCI clamping diode must be disabled to drive an input with voltages higher than V<sub>CCIO</sub>, except for the 5.0-V input case.

(2) An APEX 20KE device can be made 5.0-V tolerant with the addition of an external resistor. You also need a PCI clamp and series resistor.

(3) When V<sub>CCIO</sub> = 3.3 V, an APEX 20KE device can drive a 2.5-V device with 3.3-V tolerant inputs.

# ClockLock & ClockBoost Features

APEX 20K devices support the ClockLock and ClockBoost clock management features, which are implemented with PLLs. The ClockLock circuitry uses a synchronizing PLL that reduces the clock delay and skew within a device. This reduction minimizes clock-to-output and setup times while maintaining zero hold times. The ClockBoost circuitry, which provides a clock multiplier, allows the designer to enhance device area efficiency by sharing resources within the device. The ClockBoost circuitry allows the designer to distribute a low-speed clock and multiply that clock on-device. APEX 20K devices include a high-speed clock tree; unlike ASICs, the user does not have to design and optimize the clock tree. The ClockLock and ClockBoost features work in conjunction with the APEX 20K device's high-speed clock to provide significant improvements in system performance and band-width. Devices with an X-suffix on the ordering code include the ClockLock circuit.

The ClockLock and ClockBoost features in APEX 20K devices are enabled through the Quartus II software. External devices are not required to use these features.

| Symbol               | Parameter                                        | I/O Standard       | -1X Spe | ed Grade | -2X Spee | d Grade | Units |

|----------------------|--------------------------------------------------|--------------------|---------|----------|----------|---------|-------|

|                      |                                                  | -                  | Min     | Мах      | Min      | Max     |       |

| f <sub>VCO</sub> (4) | Voltage controlled oscillator<br>operating range |                    | 200     | 500      | 200      | 500     | MHz   |

| f <sub>CLOCK0</sub>  | Clock0 PLL output frequency for internal use     |                    | 1.5     | 335      | 1.5      | 200     | MHz   |

| f <sub>CLOCK1</sub>  | Clock1 PLL output frequency for internal use     |                    | 20      | 335      | 20       | 200     | MHz   |

| fCLOCK0_EXT          | Output clock frequency for                       | 3.3-V LVTTL        | 1.5     | 245      | 1.5      | 226     | MHz   |

|                      | external clock0 output                           | 2.5-V LVTTL        | 1.5     | 234      | 1.5      | 221     | MHz   |

|                      |                                                  | 1.8-V LVTTL        | 1.5     | 223      | 1.5      | 216     | MHz   |

|                      |                                                  | GTL+               | 1.5     | 205      | 1.5      | 193     | MHz   |

|                      |                                                  | SSTL-2 Class<br>I  | 1.5     | 158      | 1.5      | 157     | MHz   |

|                      |                                                  | SSTL-2 Class<br>II | 1.5     | 142      | 1.5      | 142     | MHz   |

|                      |                                                  | SSTL-3 Class<br>I  | 1.5     | 166      | 1.5      | 162     | MHz   |

|                      |                                                  | SSTL-3 Class<br>II | 1.5     | 149      | 1.5      | 146     | MHz   |

|                      |                                                  | LVDS               | 1.5     | 420      | 1.5      | 350     | MHz   |

| fCLOCK1_EXT          | Output clock frequency for                       | 3.3-V LVTTL        | 20      | 245      | 20       | 226     | MHz   |

|                      | external clock1 output                           | 2.5-V LVTTL        | 20      | 234      | 20       | 221     | MHz   |

|                      |                                                  | 1.8-V LVTTL        | 20      | 223      | 20       | 216     | MHz   |

|                      |                                                  | GTL+               | 20      | 205      | 20       | 193     | MHz   |

|                      |                                                  | SSTL-2 Class<br>I  | 20      | 158      | 20       | 157     | MHz   |

|                      |                                                  | SSTL-2 Class<br>II | 20      | 142      | 20       | 142     | MHz   |

|                      |                                                  | SSTL-3 Class<br>I  | 20      | 166      | 20       | 162     | MHz   |

|                      |                                                  | SSTL-3 Class<br>II | 20      | 149      | 20       | 146     | MHz   |

|                      |                                                  | LVDS               | 20      | 420      | 20       | 350     | MHz   |

| Device     |                     | IDCODE (32 Bits) (1)  |                                    |                      |  |  |  |  |  |  |  |  |

|------------|---------------------|-----------------------|------------------------------------|----------------------|--|--|--|--|--|--|--|--|

|            | Version<br>(4 Bits) | Part Number (16 Bits) | Manufacturer<br>Identity (11 Bits) | <b>1 (1 Bit)</b> (2) |  |  |  |  |  |  |  |  |

| EP20K30E   | 0000                | 1000 0000 0011 0000   | 000 0110 1110                      | 1                    |  |  |  |  |  |  |  |  |

| EP20K60E   | 0000                | 1000 0000 0110 0000   | 000 0110 1110                      | 1                    |  |  |  |  |  |  |  |  |

| EP20K100   | 0000                | 0000 0100 0001 0110   | 000 0110 1110                      | 1                    |  |  |  |  |  |  |  |  |

| EP20K100E  | 0000                | 1000 0001 0000 0000   | 000 0110 1110                      | 1                    |  |  |  |  |  |  |  |  |

| EP20K160E  | 0000                | 1000 0001 0110 0000   | 000 0110 1110                      | 1                    |  |  |  |  |  |  |  |  |

| EP20K200   | 0000                | 0000 1000 0011 0010   | 000 0110 1110                      | 1                    |  |  |  |  |  |  |  |  |

| EP20K200E  | 0000                | 1000 0010 0000 0000   | 000 0110 1110                      | 1                    |  |  |  |  |  |  |  |  |

| EP20K300E  | 0000                | 1000 0011 0000 0000   | 000 0110 1110                      | 1                    |  |  |  |  |  |  |  |  |

| EP20K400   | 0000                | 0001 0110 0110 0100   | 000 0110 1110                      | 1                    |  |  |  |  |  |  |  |  |

| EP20K400E  | 0000                | 1000 0100 0000 0000   | 000 0110 1110                      | 1                    |  |  |  |  |  |  |  |  |

| EP20K600E  | 0000                | 1000 0110 0000 0000   | 000 0110 1110                      | 1                    |  |  |  |  |  |  |  |  |

| EP20K1000E | 0000                | 1001 0000 0000 0000   | 000 0110 1110                      | 1                    |  |  |  |  |  |  |  |  |

#### - -- -\_ \_ .

Notes to Table 21:

The most significant bit (MSB) is on the left. (1)

(2) The IDCODE's least significant bit (LSB) is always 1.

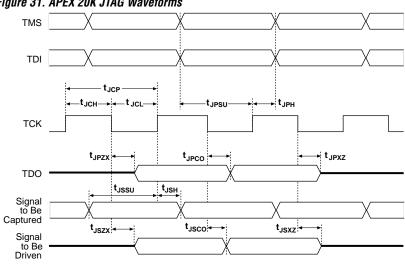

# Figure 31 shows the timing requirements for the JTAG signals.

**Altera Corporation**

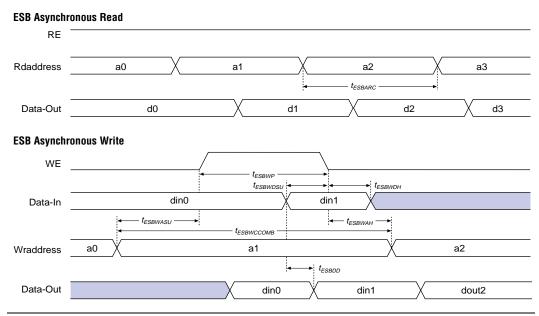

Figures 38 and 39 show the asynchronous and synchronous timing waveforms, respectively, for the ESB macroparameters in Table 31.

Figure 38. ESB Asynchronous Timing Waveforms

Tables 40 through 42 show the  $f_{MAX}$  timing parameters for EP20K100, EP20K200, and EP20K400 APEX 20K devices.

| Symbol                  | -1 Speed Grade |     | -2 Spee | d Grade | -3 Spee | Units |    |

|-------------------------|----------------|-----|---------|---------|---------|-------|----|

|                         | Min            | Max | Min     | Max     | Min     | Max   |    |

| t <sub>SU</sub>         | 0.5            |     | 0.6     |         | 0.8     |       | ns |

| t <sub>H</sub>          | 0.7            |     | 0.8     |         | 1.0     |       | ns |

| t <sub>CO</sub>         |                | 0.3 |         | 0.4     |         | 0.5   | ns |

| t <sub>lut</sub>        |                | 0.8 |         | 1.0     |         | 1.3   | ns |

| t <sub>ESBRC</sub>      |                | 1.7 |         | 2.1     |         | 2.4   | ns |

| t <sub>ESBWC</sub>      |                | 5.7 |         | 6.9     |         | 8.1   | ns |

| t <sub>ESBWESU</sub>    | 3.3            |     | 3.9     |         | 4.6     |       | ns |

| t <sub>ESBDATASU</sub>  | 2.2            |     | 2.7     |         | 3.1     |       | ns |

| t <sub>ESBDATAH</sub>   | 0.6            |     | 0.8     |         | 0.9     |       | ns |

| t <sub>ESBADDRSU</sub>  | 2.4            |     | 2.9     |         | 3.3     |       | ns |

| t <sub>ESBDATACO1</sub> |                | 1.3 |         | 1.6     |         | 1.8   | ns |

| t <sub>ESBDATACO2</sub> |                | 2.6 |         | 3.1     |         | 3.6   | ns |

| t <sub>ESBDD</sub>      |                | 2.5 |         | 3.3     |         | 3.6   | ns |

| t <sub>PD</sub>         |                | 2.5 |         | 3.0     |         | 3.6   | ns |

| <b>TERMSU</b>           | 2.3            |     | 2.6     |         | 3.2     |       | ns |

| t <sub>PTERMCO</sub>    |                | 1.5 |         | 1.8     |         | 2.1   | ns |

| t <sub>F1-4</sub>       |                | 0.5 |         | 0.6     |         | 0.7   | ns |

| t <sub>F5-20</sub>      |                | 1.6 |         | 1.7     |         | 1.8   | ns |

| t <sub>F20+</sub>       |                | 2.2 |         | 2.2     |         | 2.3   | ns |

| t <sub>CH</sub>         | 2.0            |     | 2.5     |         | 3.0     |       | ns |

| t <sub>CL</sub>         | 2.0            |     | 2.5     |         | 3.0     |       | ns |

| t <sub>CLRP</sub>       | 0.3            |     | 0.4     |         | 0.4     |       | ns |

| t <sub>PREP</sub>       | 0.5            |     | 0.5     |         | 0.5     |       | ns |

| t <sub>ESBCH</sub>      | 2.0            |     | 2.5     |         | 3.0     |       | ns |

| t <sub>ESBCL</sub>      | 2.0            |     | 2.5     |         | 3.0     |       | ns |

| t <sub>ESBWP</sub>      | 1.6            |     | 1.9     |         | 2.2     |       | ns |

| t <sub>ESBRP</sub>      | 1.0            |     | 1.3     |         | 1.4     |       | ns |

| Symbol                  | -1 Speed Grade |     | -2 Speed Grade |     | -3 Spee | Units |    |

|-------------------------|----------------|-----|----------------|-----|---------|-------|----|

|                         | Min            | Мах | Min            | Max | Min     | Max   |    |

| t <sub>SU</sub>         | 0.5            |     | 0.6            |     | 0.8     |       | ns |

| t <sub>H</sub>          | 0.7            |     | 0.8            |     | 1.0     |       | ns |

| t <sub>co</sub>         |                | 0.3 |                | 0.4 |         | 0.5   | ns |

| t <sub>lut</sub>        |                | 0.8 |                | 1.0 |         | 1.3   | ns |

| t <sub>ESBRC</sub>      |                | 1.7 |                | 2.1 |         | 2.4   | ns |

| t <sub>ESBWC</sub>      |                | 5.7 |                | 6.9 |         | 8.1   | ns |

| t <sub>ESBWESU</sub>    | 3.3            |     | 3.9            |     | 4.6     |       | ns |

| t <sub>ESBDATASU</sub>  | 2.2            |     | 2.7            |     | 3.1     |       | ns |

| t <sub>ESBDATAH</sub>   | 0.6            |     | 0.8            |     | 0.9     |       | ns |

| t <sub>ESBADDRSU</sub>  | 2.4            |     | 2.9            |     | 3.3     |       | ns |

| t <sub>ESBDATACO1</sub> |                | 1.3 |                | 1.6 |         | 1.8   | ns |

| t <sub>ESBDATACO2</sub> |                | 2.6 |                | 3.1 |         | 3.6   | ns |

| t <sub>ESBDD</sub>      |                | 2.5 |                | 3.3 |         | 3.6   | ns |

| t <sub>PD</sub>         |                | 2.5 |                | 3.0 |         | 3.6   | ns |

| t <sub>PTERMSU</sub>    | 2.3            |     | 2.7            |     | 3.2     |       | ns |

| t <sub>PTERMCO</sub>    |                | 1.5 |                | 1.8 |         | 2.1   | ns |

| t <sub>F1-4</sub>       |                | 0.5 |                | 0.6 |         | 0.7   | ns |

| t <sub>F5-20</sub>      |                | 1.6 |                | 1.7 |         | 1.8   | ns |

| t <sub>F20+</sub>       |                | 2.2 |                | 2.2 |         | 2.3   | ns |

| t <sub>CH</sub>         | 2.0            |     | 2.5            |     | 3.0     |       | ns |

| t <sub>CL</sub>         | 2.0            |     | 2.5            |     | 3.0     |       | ns |

| t <sub>CLRP</sub>       | 0.3            |     | 0.4            |     | 0.4     |       | ns |

| t <sub>PREP</sub>       | 0.4            |     | 0.5            |     | 0.5     |       | ns |

| t <sub>ESBCH</sub>      | 2.0            |     | 2.5            |     | 3.0     |       | ns |

| t <sub>ESBCL</sub>      | 2.0            |     | 2.5            |     | 3.0     |       | ns |

| t <sub>ESBWP</sub>      | 1.6            |     | 1.9            |     | 2.2     |       | ns |

| t <sub>ESBRP</sub>      | 1.0            |     | 1.3            |     | 1.4     |       | ns |

| Symbol                  | -1    |      | -     | -2   |      | Unit |    |

|-------------------------|-------|------|-------|------|------|------|----|

|                         | Min   | Max  | Min   | Max  | Min  | Max  |    |

| t <sub>ESBARC</sub>     |       | 1.65 |       | 2.02 |      | 2.11 | ns |

| t <sub>ESBSRC</sub>     |       | 2.21 |       | 2.70 |      | 3.11 | ns |

| t <sub>ESBAWC</sub>     |       | 3.04 |       | 3.79 |      | 4.42 | ns |

| t <sub>ESBSWC</sub>     |       | 2.81 |       | 3.56 |      | 4.10 | ns |

| t <sub>ESBWASU</sub>    | 0.54  |      | 0.66  |      | 0.73 |      | ns |

| t <sub>ESBWAH</sub>     | 0.36  |      | 0.45  |      | 0.47 |      | ns |

| t <sub>ESBWDSU</sub>    | 0.68  |      | 0.81  |      | 0.94 |      | ns |

| t <sub>ESBWDH</sub>     | 0.36  |      | 0.45  |      | 0.47 |      | ns |

| t <sub>ESBRASU</sub>    | 1.58  |      | 1.87  |      | 2.06 |      | ns |

| t <sub>ESBRAH</sub>     | 0.00  |      | 0.00  |      | 0.01 |      | ns |

| t <sub>ESBWESU</sub>    | 1.41  |      | 1.71  |      | 2.00 |      | ns |

| t <sub>ESBWEH</sub>     | 0.00  |      | 0.00  |      | 0.00 |      | ns |

| t <sub>ESBDATASU</sub>  | -0.02 |      | -0.03 |      | 0.09 |      | ns |

| t <sub>ESBDATAH</sub>   | 0.13  |      | 0.13  |      | 0.13 |      | ns |

| t <sub>ESBWADDRSU</sub> | 0.14  |      | 0.17  |      | 0.35 |      | ns |

| t <sub>ESBRADDRSU</sub> | 0.21  |      | 0.27  |      | 0.43 |      | ns |

| t <sub>ESBDATACO1</sub> |       | 1.04 |       | 1.30 |      | 1.46 | ns |

| t <sub>ESBDATACO2</sub> |       | 2.15 |       | 2.70 |      | 3.16 | ns |

| t <sub>ESBDD</sub>      |       | 2.69 |       | 3.35 |      | 3.97 | ns |

| t <sub>PD</sub>         |       | 1.55 |       | 1.93 |      | 2.29 | ns |

| t <sub>PTERMSU</sub>    | 1.01  |      | 1.23  |      | 1.52 |      | ns |

| t <sub>PTERMCO</sub>    |       | 1.06 |       | 1.32 |      | 1.04 | ns |

| Symbol                  | -1   |      | -    | 2    |      | Unit |    |

|-------------------------|------|------|------|------|------|------|----|

|                         | Min  | Max  | Min  | Max  | Min  | Max  |    |

| t <sub>ESBARC</sub>     |      | 1.79 |      | 2.44 |      | 3.25 | ns |

| t <sub>ESBSRC</sub>     |      | 2.40 |      | 3.12 |      | 4.01 | ns |

| t <sub>ESBAWC</sub>     |      | 3.41 |      | 4.65 |      | 6.20 | ns |

| t <sub>ESBSWC</sub>     |      | 3.68 |      | 4.68 |      | 5.93 | ns |

| t <sub>ESBWASU</sub>    | 1.55 |      | 2.12 |      | 2.83 |      | ns |

| t <sub>ESBWAH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns |

| t <sub>ESBWDSU</sub>    | 1.71 |      | 2.33 |      | 3.11 |      | ns |

| t <sub>ESBWDH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns |

| t <sub>ESBRASU</sub>    | 1.72 |      | 2.34 |      | 3.13 |      | ns |

| t <sub>ESBRAH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns |

| t <sub>ESBWESU</sub>    | 1.63 |      | 2.36 |      | 3.28 |      | ns |

| t <sub>ESBWEH</sub>     | 0.00 |      | 0.00 |      | 0.00 |      | ns |

| t <sub>ESBDATASU</sub>  | 0.07 |      | 0.39 |      | 0.80 |      | ns |

| t <sub>ESBDATAH</sub>   | 0.13 |      | 0.13 |      | 0.13 |      | ns |

| t <sub>ESBWADDRSU</sub> | 0.27 |      | 0.67 |      | 1.17 |      | ns |

| t <sub>ESBRADDRSU</sub> | 0.34 |      | 0.75 |      | 1.28 |      | ns |

| t <sub>ESBDATACO1</sub> |      | 1.03 |      | 1.20 |      | 1.40 | ns |

| t <sub>ESBDATACO2</sub> |      | 2.33 |      | 3.18 |      | 4.24 | ns |

| t <sub>ESBDD</sub>      |      | 3.41 |      | 4.65 |      | 6.20 | ns |

| t <sub>PD</sub>         |      | 1.68 |      | 2.29 |      | 3.06 | ns |

| t <sub>PTERMSU</sub>    | 0.96 |      | 1.48 |      | 2.14 |      | ns |

| t <sub>PTERMCO</sub>    |      | 1.05 |      | 1.22 |      | 1.42 | ns |

| Table 81. EP2      | Table 81. EP20K300E f <sub>MAX</sub> Routing Delays |      |     |      |     |      |      |  |  |  |  |  |  |

|--------------------|-----------------------------------------------------|------|-----|------|-----|------|------|--|--|--|--|--|--|

| Symbol             | -                                                   | 1    |     | -2   | -;  | 3    | Unit |  |  |  |  |  |  |

|                    | Min                                                 | Max  | Min | Max  | Min | Мах  |      |  |  |  |  |  |  |

| t <sub>F1-4</sub>  |                                                     | 0.22 |     | 0.24 |     | 0.26 | ns   |  |  |  |  |  |  |

| t <sub>F5-20</sub> |                                                     | 1.33 |     | 1.43 |     | 1.58 | ns   |  |  |  |  |  |  |

| t <sub>F20+</sub>  |                                                     | 3.63 |     | 3.93 |     | 4.35 | ns   |  |  |  |  |  |  |

### **Altera Corporation**

# Version 4.1

APEX 20K Programmable Logic Device Family Data Sheet version 4.1 contains the following changes:

- *t*<sub>ESBWEH</sub> added to Figure 37 and Tables 35, 50, 56, 62, 68, 74, 86, 92, 97, and 104.

- Updated EP20K300E device internal and external timing numbers in Tables 79 through 84.