Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | HCS12                                                                  |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 25MHz                                                                  |

| Connectivity               | I²C, SCI, SPI                                                          |

| Peripherals                | PWM, WDT                                                               |

| Number of I/O              | 59                                                                     |

| Program Memory Size        | 32KB (32K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 1K x 8                                                                 |

| RAM Size                   | 4K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 5.25V                                                          |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 80-QFP                                                                 |

| Supplier Device Package    | 80-QFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s12a32cfuer |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|       | on 4 Modes of Operation                    |

|-------|--------------------------------------------|

| 4.1   | Overview                                   |

| 4.2   | Chip Configuration Summary                 |

| 4.3   | Security70                                 |

| 4.3.1 | Securing the Microcontroller70             |

| 4.3.2 | Operation of the Secured Microcontroller70 |

| 4.3.3 | Unsecuring the Microcontroller71           |

| 4.4   | Low Power Modes                            |

| 4.4.1 | Stop                                       |

| 4.4.2 | Pseudo Stop71                              |

| 4.4.3 | Wait                                       |

| 4.4.4 | Run72                                      |

| Secti | on 5 Resets and Interrupts                 |

| 5.1   | Overview                                   |

| 5.1   |                                            |

| 5.2.1 | Vectors  .73   Vector Table  .73           |

| _     |                                            |

| 5.3   | Effects of Reset                           |

| 5.3.1 | I/O pins                                   |

| 5.3.2 | Memory                                     |

| Secti | on 6 HCS12 Core Block Description          |

| 6.1   | CPU12 Block Description                                           | 77 |

|-------|-------------------------------------------------------------------|----|

| 6.1.1 | Device-specific information                                       | 77 |

| 6.2   | HCS12 Module Mapping Control (MMC) Block Description              | 77 |

| 6.2.1 | Device-specific information                                       | 77 |

| 6.3   | HCS12 Multiplexed External Bus Interface (MEBI) Block Description | 77 |

| 6.3.1 | Device-specific information                                       | 77 |

| 6.4   | HCS12 Interrupt (INT) Block Description                           |    |

| 6.5   | HCS12 Background Debug (BDM) Block Description                    |    |

| 6.5.1 | Device-specific information                                       |    |

| 6.6   | HCS12 Breakpoint (BKP) Block Description                          | 78 |

| Sect  | ion 7 Clock and Reset Generator (CRG) Block Description           |    |

| 7.1   | Device-specific information                                       | 78 |

| Sect  | ion 8 Oscillator (OSC) Block Description                          |    |

| 8.1   | Device-specific information                                       | 78 |

| Sect  | ion 9 Enhanced Capture Timer (ECT) Block Description              |    |

| Sect  | ion 10 Analog to Digital Converter (ATD) Block Description        |    |

| Sect  | ion 11 Inter-IC Bus (IIC) Block Description                       |    |

| Sect  | ion 12 Serial Communications Interface (SCI) Block Description    |    |

| Sect  | ion 13 Serial Peripheral Interface (SPI) Block Description        |    |

| Sect  | ion 14 J1850 (BDLC) Block Description                             |    |

| Sect  | ion 15 Pulse Width Modulator (PWM) Block Description              |    |

| Sect  | ion 16 Flash EEPROM 64K Block Description                         |    |

| Sect  | ion 17 EEPROM 1K Block Description                                |    |

| Sect  | ion 18 RAM Block Description                                      |    |

| Sect  | ion 19 MSCAN Block Description                                    |    |

## Section 20 Port Integration Module (PIM) Block Description

## Section 21 Voltage Regulator (VREG) Block Description

## **Section 22 Printed Circuit Board Layout Proposals**

## **Appendix A Electrical Characteristics**

| A.1    | General                                       | 87  |

|--------|-----------------------------------------------|-----|

| A.1.1  | Parameter Classification                      | 87  |

| A.1.2  | Power Supply                                  | 87  |

| A.1.3  | Pins                                          | 88  |

| A.1.4  | Current Injection                             | 88  |

| A.1.5  | Absolute Maximum Ratings                      | 89  |

| A.1.6  | ESD Protection and Latch-up Immunity          | 90  |

| A.1.7  | Operating Conditions                          | 90  |

| A.1.8  | Power Dissipation and Thermal Characteristics | 91  |

| A.1.9  | I/O Characteristics                           | 93  |

| A.1.10 | Supply Currents                               | 94  |

| A.2    | ATD Characteristics                           | 97  |

| A.2.1  | ATD Operating Characteristics                 | 97  |

| A.2.2  | Factors influencing accuracy                  | 97  |

| A.2.3  | ATD accuracy                                  | 99  |

| A.3    | NVM, Flash and EEPROM                         | 101 |

| A.3.1  | NVM timing                                    | 101 |

| A.3.2  | NVM Reliability                               | 103 |

| A.4    | Voltage Regulator                             | 105 |

| A.5    | Reset, Oscillator and PLL                     |     |

| A.5.1  | Startup                                       | 107 |

| A.5.2  | Oscillator                                    | 108 |

| A.5.3  | Phase Locked Loop                             | 109 |

| A.6    | MSCAN                                         | 113 |

| A.7    | SPI                                           | 115 |

| A.7.1  | Master Mode                                   | 115 |

| A.7.2  | Slave Mode                                    | 117 |

| A.8    | External Bus Timing                           | 119 |

| A.8.1  | General Muxed Bus Timing                      | 119 |

# **List of Tables**

| Table 0-1   | Derivati | ve Differences                                                   | .15 |

|-------------|----------|------------------------------------------------------------------|-----|

| Table 0-2   | Docume   | ent References                                                   | .17 |

| Table 1-1   | Device I | Memory Map for MC9S12DJ64                                        | .25 |

| Table 1-2   | Device I | Memory Map for MC9S12D32                                         | .28 |

| \$0000 - \$ | 000F     | MEBI map 1 of 3 (HCS12 Multiplexed External Bus Interface)       | 30  |

| \$0010 - \$ | 0014     | MMC map 1 of 4 (HCS12 Module Mapping Control)                    | 30  |

| \$0015 - \$ | 0016     | INT map 1 of 2 (HCS12 Interrupt)                                 | 31  |

| \$0017 - \$ | 0019     | Reserved                                                         | 31  |

| \$001A - \$ | 001B     | Device ID Register (Table 1-4)                                   | 31  |

| \$001C - \$ | 001D     | MMC map 3 of 4 (HCS12 Module Mapping Control, <b>Table 1-5</b> ) | 31  |

| \$001E - \$ | S001E    | MEBI map 2 of 3 (HCS12 Multiplexed External Bus Interface)       | 31  |

| \$001F - \$ | 001F     | INT map 2 of 2 (HCS12 Interrupt)                                 | 32  |

| \$0020 - \$ | 0027     | Reserved                                                         | 32  |

| \$0028 - \$ | 002F     | BKP (HCS12 Breakpoint)                                           | 32  |

| \$0030 - \$ | 0031     | MMC map 4 of 4 (HCS12 Module Mapping Control)                    | 32  |

| \$0032 - \$ | 0033     | MEBI map 3 of 3 (HCS12 Multiplexed External Bus Interface)       | 32  |

| \$0034 - \$ | 003F     | CRG (Clock and Reset Generator)                                  | 33  |

| \$0040 - \$ | 007F     | ECT (Enhanced Capture Timer 16 Bit 8 Channels)                   | 33  |

| \$0080 - \$ | 009F     | ATD0 (Analog to Digital Converter 10 Bit 8 Channel)              | 36  |

| \$00A0 - \$ | 800C7    | PWM (Pulse Width Modulator 8 Bit 8 Channel)                      | 37  |

| \$00C8 - \$ | SOOCF    | SCI0 (Asynchronous Serial Interface)                             | 39  |

| \$00D0 - \$ | 800D7    | SCI1 (Asynchronous Serial Interface)                             | 39  |

| \$00D8 - \$ | 800DF    | SPI0 (Serial Peripheral Interface)                               | 40  |

| \$00E0 - \$ | 00E7     | IIC (Inter IC Bus)                                               | 40  |

| \$00E8 - \$ | 00EF     | BDLC (Bytelevel Data Link Controller J1850)                      | 41  |

| \$00F0 - \$ | 00FF     | Reserved                                                         | 41  |

| \$0100 - \$ | 010F     | Flash Control Register (fts64k)                                  | 41  |

| \$0110 - \$ | 011B     | EEPROM Control Register (eets1k)                                 | 42  |

| \$011C - \$ | 011F     | Reserved for RAM Control Register                                | 42  |

| \$0120 - \$ | 013F     | ATD1 (Analog to Digital Converter 10 Bit 8 Channel)              | 43  |

| \$0140 - \$ |          | CAN0 (Freescale Scalable CAN - FSCAN)                            |     |

| Table 1-3   | Detailed | FSCAN Foreground Receive and Transmit Buffer Layout              | .45 |

| \$0180 - \$ | 023F     | Reserved                                                         | 46  |

**Table 0-2 Document References**

| User Guide                                                                | Versi<br>on | Document Order Number |

|---------------------------------------------------------------------------|-------------|-----------------------|

| HCS12 CPU Reference Manual                                                | V02         | S12CPUV2/D            |

| HCS12 Module Mapping Control (MMC) Block Guide                            | V04         | S12MMCV4/D            |

| HCS12 Multiplexed External Bus Interface (MEBI) Block Guide               | V03         | S12MEBIV3/D           |

| HCS12 Interrupt (INT) Block Guide                                         | V01         | S12INTV1/D            |

| HCS12 Background Debug (BDM) Block Guide                                  | V04         | S12BDMV4/D            |

| HCS12 Breakpoint (BKP) Block Guide                                        | V01         | S12BKPV1/D            |

| Clock and Reset Generator (CRG) Block User Guide                          | V04         | S12CRGV4/D            |

| Oscillator (OSC) Block User Guide                                         | V02         | S12OSCV2/D            |

| Enhanced Capture Timer 16 Bit 8 Channel (ECT_16B8C) Block User Guide      | V01         | S12ECT16B8CV1/D       |

| Analog to Digital Converter 10 Bit 8 Channel (ATD_10B8C) Block User Guide | V02         | S12ATD10B8CV2/D       |

| Inter IC Bus (IIC) Block User Guide                                       | V02         | S12IICV2/D            |

| Asynchronous Serial Interface (SCI) Block User Guide                      | V02         | S12SCIV2/D            |

| Serial Peripheral Interface (SPI) Block User Guide                        | V02         | S12SPIV2/D            |

| Pulse Width Modulator 8 Bit 8 Channel (PWM_8B8C) Block User Guide         | V01         | S12PWM8B8CV1/D        |

| 64K Byte Flash (FTS64K) Block User Guide                                  | V01         | S12FTS64KV1/D         |

| 1K Byte EEPROM (EETS1K) Block User Guide                                  | V01         | S12EETS1KV1/D         |

| Byte Level Data Link Controller -J1850 (BDLC) Block User Guide            | V01         | S12BDLCV1/D           |

| Freescale Scalable CAN (MSCAN) Block User Guide                           | V02         | S12MSCANV2/D          |

| Voltage Regulator (VREG) Block User Guide                                 | V01         | S12VREGV1/D           |

| Port Integration Module (PIM_9DJ64) Block User Guide                      | V01         | S12PIM9DJ64V1/D       |

- I/O lines with 5V input and drive capability

- 5V A/D converter inputs

- Operation at 50MHz equivalent to 25MHz Bus Speed

- Development support

- Single-wire background debug<sup>TM</sup> mode (BDM)

- On-chip hardware breakpoints

## 1.3 Modes of Operation

#### User modes

- Normal and Emulation Operating Modes

- Normal Single-Chip Mode

- Normal Expanded Wide Mode

- Normal Expanded Narrow Mode

- Emulation Expanded Wide Mode

- Emulation Expanded Narrow Mode

- Special Operating Modes

- Special Single-Chip Mode with active Background Debug Mode

- Special Test Mode (Freescale use only)

- Special Peripheral Mode (Freescale use only)

#### Low power modes

- Stop Mode

- Pseudo Stop Mode

- · Wait Mode

Table 1-2 Device Memory Map for MC9S12D32

| Address         | Module                                                  |      |  |  |  |

|-----------------|---------------------------------------------------------|------|--|--|--|

| \$0000 - \$000F | HCS12 Multiplexed External Bus Interface                | 16   |  |  |  |

| \$0010 - \$0014 | HCS12 Module Mapping Control                            | 5    |  |  |  |

| \$0015 - \$0016 | HCS12 Interrupt                                         | 2    |  |  |  |

| \$0017 - \$0019 | Reserved                                                | 3    |  |  |  |

| \$001A - \$001B | Device ID register (PARTID)                             | 2    |  |  |  |

| \$001C - \$001D | HCS12 Module Mapping Control                            | 2    |  |  |  |

| \$001E          | HCS12 Multiplexed External Bus Interface                | 1    |  |  |  |

| \$001F          | HCS12 Interrupt                                         | 1    |  |  |  |

| \$0020 - \$0027 | Reserved                                                | 8    |  |  |  |

| \$0028 - \$002F | HCS12 Breakpoint Module                                 | 8    |  |  |  |

| \$0030 - \$0031 | HCS12 Module Mapping Control                            | 2    |  |  |  |

| \$0032 - \$0033 | HCS12 Multiplexed External Bus Interface                | 2    |  |  |  |

| \$0034 - \$003F | Clock and Reset Generator (PLL, RTI, COP)               | 12   |  |  |  |

| \$0040 - \$007F | Enhanced Capture Timer 16-bit 8 channels                | 64   |  |  |  |

| \$0080 - \$009F | Analog to Digital Converter 10-bit 8 channels (ATD0)    | 32   |  |  |  |

| \$00A0 - \$00C7 | Pulse Width Modulator 8-bit 8 channels (PWM)            | 40   |  |  |  |

| \$00C8 - \$00CF | Serial Communications Interface 0 (SCI0)                | 8    |  |  |  |

| \$00D0 - \$00D7 | Serial Communications Interface 0 (SCI1)                | 8    |  |  |  |

| \$00D8 - \$00DF | Serial Peripheral Interface (SPI0)                      | 8    |  |  |  |

| \$00E0 - \$00E7 | Inter IC Bus                                            | 8    |  |  |  |

| \$00E8 - \$00EF | Byte Data Link Controller (BDLC)                        | 8    |  |  |  |

| \$00F0 - \$00FF | Reserved                                                |      |  |  |  |

| \$0100- \$010F  | Flash Control Register                                  | 16   |  |  |  |

| \$0110 - \$011B | EEPROM Control Register                                 | 12   |  |  |  |

| \$011C - \$011F | Reserved                                                | 4    |  |  |  |

| \$0120 - \$013F | Analog to Digital Converter 10-bit 8 channels (ATD1)    | 32   |  |  |  |

| \$0140 - \$017F | Freescale Scalable Can (CAN0)                           |      |  |  |  |

| \$0180 - \$023F | Reserved                                                | 192  |  |  |  |

| \$0240 - \$027F | Port Integration Module (PIM)                           | 64   |  |  |  |

| \$0280 - \$03FF | Reserved                                                | 384  |  |  |  |

| \$0000 - \$07FF | EEPROM array 1k Array mapped twice in the address space | 2048 |  |  |  |

| \$0000 - \$0FFF | RAM array, lower half (\$0000-\$07FF not usable)        | 4096 |  |  |  |

| \$4000 - \$7FFF | 16k Fixed Flash FEPROM array (same as array from        |      |  |  |  |

| \$8000 - \$FFFF | \$8000 - \$FFFF 32K Fixed Flash EEPROM array            |      |  |  |  |

64

#### \$001F - \$001F

### INT map 2 of 2 (HCS12 Interrupt)

Address Name \$001F **HPRIO**

|          | Bit / | Bit |

|----------|-------|-----|

| Read:    | PSEL7 | PSF |

| Vrite∙ l | . 0   |     |

| Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 |

|-------|-------|-------|--------|--------|--------|--------|-------|

| PSEL7 | DSELE | DSELE | DGEI 1 | DCEI 2 | DGEI 3 | DQEI 1 | 0     |

| FSELI | FSELO | FSELS | FSEL4  | FSELS  | FSELZ  | FSELI  |       |

#### \$0020 - \$0027

#### Reserved

| Address  | Name    |

|----------|---------|

| \$0020 - | Pagarya |

| \$0027   | Reserve |

| Read:  |

|--------|

| Write: |

|       | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| ead:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| rite: |       |       |       |       |       |       |       |       |

#### \$0028 - \$002F

#### **BKP (HCS12 Breakpoint)**

| Address | Name   |

|---------|--------|

| \$0028  | BKPCT0 |

| \$0029  | BKPCT1 |

| \$002A  | BKP0X  |

| \$002B  | BKP0H  |

| \$002C  | BKP0L  |

| \$002D  | BKP1X  |

| \$002E  | BKP1H  |

| \$002F  | BKP1L  |

|        | Bit 7       | Bit 6   | Bit 5        | Bit 4   | Bit 3     | Bit 2    | Bit 1     | Bit 0    |  |

|--------|-------------|---------|--------------|---------|-----------|----------|-----------|----------|--|

| Read:  | ead:        |         | DICEDIA DICE | DIZTAC  | 0         | 0        | 0         | 0        |  |

| Write: | BKEN        | BKFULL  | BKBDM        | BKTAG   |           |          |           |          |  |

| Read:  | DICOMBIL    | DICOMPI | DICAMBLI     | DIZAMBI | DIKODIAKE | DICODIAL | DICADIAGE | DICA DIA |  |

| Write: | BK0MBH      | BK0MBL  | BK1MBH       | BK1MBL  | BK0RWE    | BK0RW    | BK1RWE    | BK1RW    |  |

| Read:  | 0           | 0       | DI/OV/E      | DI(O)(4 | DI(0)(0   | DI(0)(0  | DI(0)/4   | DI(0)(0  |  |

| Write: |             |         | BK0V5        | BK0V4   | BK0V3     | BK0V2    | BK0V1     | BK0V0    |  |

| Read:  | D:445       | 4.4     | 40           | 40      | 44        | 40       | _         | D:+ 0    |  |

| Write: | Bit 15 14   |         | 13           | 12      | 11        | 10       | 9         | Bit 8    |  |

| Read:  | D:: 7       | •       | _            | 4       |           | _        | 4         | D:: 0    |  |

| Write: | Bit 7       | 6       | 5            | 4       | 3         | 2        | 1         | Bit 0    |  |

| Read:  | 0           | 0       | DICANG       | DICANA  | DICANO    | DICANO.  | DICALVA   | DICAL/O  |  |

| Write: |             |         | BK1V5        | BK1V4   | BK1V3     | BK1V2    | BK1V1     | BK1V0    |  |

| Read:  | D:445       | 4.4     | 40           | 40      | 44        | 40       | _         | D:+ 0    |  |

| Write: | Bit 15   14 |         | 13           | 12      | 11        | 10       | 9         | Bit 8    |  |

| Read:  | D:4 7       | 0       | -            | 4       | 0         | 0        | 4         | D:4 0    |  |

| Write: | Bit 7       | 6       | 5            | 4       | 3         | 2        | 1         | Bit 0    |  |

|        |             |         |              |         |           |          |           |          |  |

## \$0030 - \$0031

### MMC map 4 of 4 (HCS12 Module Mapping Control)

| Address | Name     |

|---------|----------|

| \$0030  | PPAGE    |

| \$0031  | Reserved |

|        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| Read:  | 0     | 0     | PIX5  | PIX4  | PIX3  | PIX2  | PIX1  | PIX0  |

| Write: |       |       | LIVO  | FIA4  | FIAS  | FIAZ  | FIXI  | FIXU  |

| Read:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| Write: |       |       |       |       |       |       |       |       |

### \$0032 - \$0033

## MEBI map 3 of 3 (HCS12 Multiplexed External Bus Interface)

| Address | Name  |

|---------|-------|

| \$0032  | PORTK |

| \$0033  | DDRK  |

|        | DIL |

|--------|-----|

| Read:  | Bit |

| Write: | DIL |

| Read:  | Bit |

| Write: | DIL |

|        |     |

|             | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|

| ad:<br>ite: | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| ad:<br>ite: | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

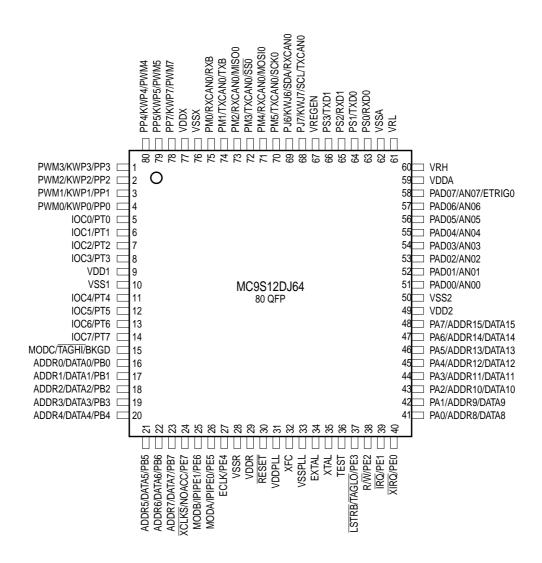

Figure 2-2 Pin Assignments in 80-pin QFP for MC9S12DJ64 and MC9S12D32

## 2.2 Signal Properties Summary

**Table 2-1** summarizes the pin functionality. Signals shown in **bold** are not available in the 80 pin package.

#### 2.3.14 PE6 / MODB / IPIPE1 — Port E I/O Pin 6

PE6 is a general purpose input or output pin. It is used as a MCU operating mode select pin during reset. The state of this pin is latched to the MODB bit at the rising edge of  $\overline{RESET}$ . This pin is shared with the instruction queue tracking signal IPIPE1. This pin is an input with a pull-down device which is only active when  $\overline{RESET}$  is low.

#### 2.3.15 PE5 / MODA / IPIPE0 — Port E I/O Pin 5

PE5 is a general purpose input or output pin. It is used as a MCU operating mode select pin during reset. The state of this pin is latched to the MODA bit at the rising edge of RESET. This pin is shared with the instruction queue tracking signal IPIPE0. This pin is an input with a pull-down device which is only active when RESET is low.

#### 2.3.16 PE4 / ECLK — Port E I/O Pin 4

PE4 is a general purpose input or output pin. It can be configured to drive the internal bus clock ECLK. ECLK can be used as a timing reference.

#### 2.3.17 PE3 / LSTRB / TAGLO — Port E I/O Pin 3

PE3 is a general purpose input or output pin. In MCU expanded modes of operation,  $\overline{LSTRB}$  can be used for the low-byte strobe function to indicate the type of bus access and when instruction tagging is on,  $\overline{TAGLO}$  is used to tag the low half of the instruction word being read into the instruction queue.

### 2.3.18 PE2 / R/W — Port E I/O Pin 2

PE2 is a general purpose input or output pin. In MCU expanded modes of operations, this pin drives the read/write output signal for the external bus. It indicates the direction of data on the external bus.

## 2.3.19 PE1 / IRQ — Port E Input Pin 1

PE1 is a general purpose input pin and the maskable interrupt request input that provides a means of applying asynchronous interrupt requests. This will wake up the MCU from STOP or WAIT mode.

## 2.3.20 PE0 / XIRQ — Port E Input Pin 0

PE0 is a general purpose input pin and the non-maskable interrupt request input that provides a means of applying asynchronous interrupt requests. This will wake up the MCU from STOP or WAIT mode.

#### 2.3.21 PH7 / KWH7 — Port H I/O Pin 7

PH7 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode.

#### 2.3.55 PS2 / RXD1 — Port S I/O Pin 2

PS2 is a general purpose input or output pin. It can be configured as the receive pin RXD of Serial Communication Interface 1 (SCI1).

#### 2.3.56 PS1 / TXD0 — Port S I/O Pin 1

PS1 is a general purpose input or output pin. It can be configured as the transmit pin TXD of Serial Communication Interface 0 (SCI0).

#### 2.3.57 PS0 / RXD0 — Port S I/O Pin 0

PS0 is a general purpose input or output pin. It can be configured as the receive pin RXD of Serial Communication Interface 0 (SCI0).

## 2.3.58 PT[7:0] / IOC[7:0] — Port T I/O Pins [7:0]

PT7-PT0 are general purpose input or output pins. They can be configured as input capture or output compare pins IOC7-IOC0 of the Enhanced Capture Timer (ECT).

## 2.4 Power Supply Pins

MC9S12DJ64 power and ground pins are described below.

**NOTE:** All VSS pins must be connected together in the application.

Table 2-2 MC9S12DJ64 Power and Ground Connection Summary

| Mnemonic      | Pin Number      | Nominal | Description                                                                                                                         |  |  |  |  |

|---------------|-----------------|---------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Willelilollic | 112-pin QFP Vol |         | Description                                                                                                                         |  |  |  |  |

| VDD1, 2       | 13, 65          | 2.5V    | Internal power and ground generated by internal regulator                                                                           |  |  |  |  |

| VSS1, 2       | 14, 66          | 0V      | internal power and ground generated by internal regulator                                                                           |  |  |  |  |

| VDDR          | 41              | 5.0V    | External power and ground, supply to pin drivers and internal                                                                       |  |  |  |  |

| VSSR          | 40              | 0V      | voltage regulator.                                                                                                                  |  |  |  |  |

| VDDX          | 107             | 5.0V    | External power and ground, supply to pin drivers.                                                                                   |  |  |  |  |

| VSSX          | 106             | 0V      | External power and ground, supply to pin drivers.                                                                                   |  |  |  |  |

| VDDA          | 83              | 5.0V    | Operating voltage and ground for the analog-to-digital                                                                              |  |  |  |  |

| VSSA          | 86              | 0V      | converters and the reference for the internal voltage regulator, allows the supply voltage to the A/D to be bypassed independently. |  |  |  |  |

| VRL           | 85              | 0V      | Reference voltages for the analog-to-digital converter.                                                                             |  |  |  |  |

| VRH           | 84              | 5.0V    | Therefore voltages for the analog-to-digital converter.                                                                             |  |  |  |  |

**NOTE:**

For devices assembled in 80-pin QFP packages all non-bonded out pins should be configured as outputs after reset in order to avoid current drawn from floating inputs. Refer to **Table 2-1** for affected pins.

## **5.3.2 Memory**

Refer to **Table 1-1** for locations of the memories depending on the operating mode after reset.

The RAM array is not automatically initialized out of reset.

#### MC9S12DJ64 Device User Guide — V01.20

VDDA, VDDX, VDDR as well as VSSA, VSSX, VSSR are connected by anti-parallel diodes for ESD protection.

NOTE:

In the following context VDD5 is used for either VDDA, VDDR and VDDX; VSS5 is used for either VSSA, VSSR and VSSX unless otherwise noted.

IDD5 denotes the sum of the currents flowing into the VDDA, VDDX and VDDR

pins.

VDD is used for VDD1, VDD2 and VDDPLL, VSS is used for VSS1, VSS2 and

VSSPLL.

IDD is used for the sum of the currents flowing into VDD1 and VDD2.

#### A.1.3 Pins

There are four groups of functional pins.

#### A.1.3.1 5V I/O pins

Those I/O pins have a nominal level of 5V. This class of pins is comprised of all port I/O pins, the analog inputs, BKGD and the RESET pins. The internal structure of all those pins is identical, however some of the functionality may be disabled. E.g. for the analog inputs the output drivers, pull-up and pull-down resistors are disabled permanently.

#### A.1.3.2 Analog Reference

This group is made up by the VRH and VRL pins.

#### A.1.3.3 Oscillator

The pins XFC, EXTAL, XTAL dedicated to the oscillator have a nominal 2.5V level. They are supplied by VDDPLL.

#### **A.1.3.4 TEST**

This pin is used for production testing only.

#### **A.1.3.5 VREGEN**

This pin is used to enable the on chip voltage regulator.

## A.1.4 Current Injection

Power supply must maintain regulation within operating  $V_{DD5}$  or  $V_{DD}$  range during instantaneous and operating maximum current conditions. If positive injection current ( $V_{in} > V_{DD5}$ ) is greater than  $I_{DD5}$ , the injection current may flow out of VDD5 and could result in external power supply going out of regulation. Ensure external VDD5 load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power; e.g. if no system clock is present, or if clock rate is very low which would reduce overall power consumption.

(M) MOTOROLA

specifies results in an error of less than 1/2 LSB (2.5mV) at the maximum leakage current. If device or operating conditions are less than worst case or leakage-induced error is acceptable, larger values of source resistance is allowed.

#### A.2.2.2 Source Capacitance

When sampling an additional internal capacitor is switched to the input. This can cause a voltage drop due to charge sharing with the external and the pin capacitance. For a maximum sampling error of the input voltage  $\leq$  1LSB, then the external filter capacitor,  $C_f \geq 1024 * (C_{INS} - C_{INN})$ .

#### A.2.2.3 Current Injection

There are two cases to consider.

- 1. A current is injected into the channel being converted. The channel being stressed has conversion values of \$3FF (\$FF in 8-bit mode) for analog inputs greater than  $V_{RH}$  and \$000 for values less than  $V_{RL}$  unless the current is higher than specified as disruptive condition.

- 2. Current is injected into pins in the neighborhood of the channel being converted. A portion of this current is picked up by the channel (coupling ratio K), This additional current impacts the accuracy of the conversion depending on the source resistance.

- The additional input voltage error on the converted channel can be calculated as  $V_{ERR} = K * R_S * I_{INJ}$ , with  $I_{INJ}$  being the sum of the currents injected into the two pins adjacent to the converted channel.

Table A-9 ATD Electrical Characteristics

| Condit | ions | s are shown in Table A-4 unless otherwise noted     |                                      |      |     |                  |      |

|--------|------|-----------------------------------------------------|--------------------------------------|------|-----|------------------|------|

| Num    | С    | Rating                                              | Symbol                               | Min  | Тур | Max              | Unit |

| 1      | С    | Max input Source Resistance                         | R <sub>S</sub>                       | -    | -   | 1                | ΚΩ   |

| 2      | Т    | Total Input Capacitance<br>Non Sampling<br>Sampling | C <sub>INN</sub><br>C <sub>INS</sub> |      |     | 10<br>22         | pF   |

| 3      | С    | Disruptive Analog Input Current                     | I <sub>NA</sub>                      | -2.5 |     | 2.5              | mA   |

| 4      | С    | Coupling Ratio positive current injection           | K <sub>p</sub>                       |      |     | 10 <sup>-4</sup> | A/A  |

| 5      | С    | Coupling Ratio negative current injection           | K <sub>n</sub>                       |      |     | 10 <sup>-2</sup> | A/A  |

## A.3 NVM, Flash and EEPROM

**NOTE:** Unless otherwise noted the abbreviation NVM (Non Volatile Memory) is used for both Flash and EEPROM.

### A.3.1 NVM timing

The time base for all NVM program or erase operations is derived from the oscillator. A minimum oscillator frequency f<sub>NVMOSC</sub> is required for performing program or erase operations. The NVM modules do not have any means to monitor the frequency and will not prevent program or erase operation at frequencies above or below the specified minimum. Attempting to program or erase the NVM modules at a lower frequency a full program or erase transition is not assured.

The Flash and EEPROM program and erase operations are timed using a clock derived from the oscillator using the FCLKDIV and ECLKDIV registers respectively. The frequency of this clock must be set within the limits specified as f<sub>NVMOP</sub>.

The minimum program and erase times shown in **Table A-11** are calculated for maximum  $f_{NVMOP}$  and maximum  $f_{bus}$ . The maximum times are calculated for minimum  $f_{NVMOP}$  and a  $f_{bus}$  of 2MHz.

#### A.3.1.1 Single Word Programming

The programming time for single word programming is dependant on the bus frequency as a well as on the frequency  $f_{NVMOP}$  and can be calculated according to the following formula.

$$t_{swpgm} = 9 \cdot \frac{1}{f_{NVMOP}} + 25 \cdot \frac{1}{f_{bus}}$$

## A.3.1.2 Row Programming

This applies only to the Flash where up to 32 words in a row can be programmed consecutively by keeping the command pipeline filled. The time to program a consecutive word can be calculated as:

$$t_{\text{bwpgm}} = 4 \cdot \frac{1}{f_{\text{NVMOP}}} + 9 \cdot \frac{1}{f_{\text{bus}}}$$

The time to program a whole row is:

$$t_{brpqm} = t_{swpqm} + 31 \cdot t_{bwpqm}$$

Row programming is more than 2 times faster than single word programming.

#### A.3.1.3 Sector Erase

Erasing a 512 byte Flash sector or a 4 byte EEPROM sector takes:

## A.3.2 NVM Reliability

The reliability of the NVM blocks is guaranteed by stress test during qualification, constant process monitors and burn-in to screen early life failures.

The failure rates for data retention and program/erase cycling are specified at the operating conditions noted.

The program/erase cycle count on the sector is incremented every time a sector or mass erase event is executed.

Table A-12 NVM Reliability Characteristics

| Condit | Conditions are shown in Table A-4 unless otherwise noted |                                                                                                           |                     |         |     |     |        |  |  |

|--------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------|---------|-----|-----|--------|--|--|

| Num    | С                                                        | Rating                                                                                                    | Symbol              | Min     | Тур | Max | Unit   |  |  |

| 1      | С                                                        | Data Retention at an average junction temperature of $T_{Javg} = 85^{\circ}C^{1}$                         | t <sub>NVMRET</sub> | 15      |     |     | Years  |  |  |

| 2      | С                                                        | Flash number of Program/Erase cycles                                                                      | n <sub>FLPE</sub>   | 10,000  |     |     | Cycles |  |  |

| 3      | С                                                        | EEPROM number of Program/Erase cycles (–40°C $\leq$ T <sub>J</sub> $\leq$ 0°C)                            | n <sub>EEPE</sub>   | 10,000  |     |     | Cycles |  |  |

| 4      | С                                                        | EEPROM number of Program/Erase cycles $(0^{\circ}\text{C} < \text{T}_{\text{J}} \le 140^{\circ}\text{C})$ | n <sub>EEPE</sub>   | 100,000 |     |     | Cycles |  |  |

#### NOTES:

<sup>1.</sup> Total time at the maximum guaranteed device operating temperature <= 1 year

# A.8 External Bus Timing

A timing diagram of the external multiplexed-bus is illustrated in **Figure A-9** with the actual timing values shown on table **Table A-20**. All major bus signals are included in the diagram. While both a data write and data read cycle are shown, only one or the other would occur on a particular bus cycle.

### A.8.1 General Muxed Bus Timing

The expanded bus timings are highly dependent on the load conditions. The timing parameters shown assume a balanced load across all outputs.

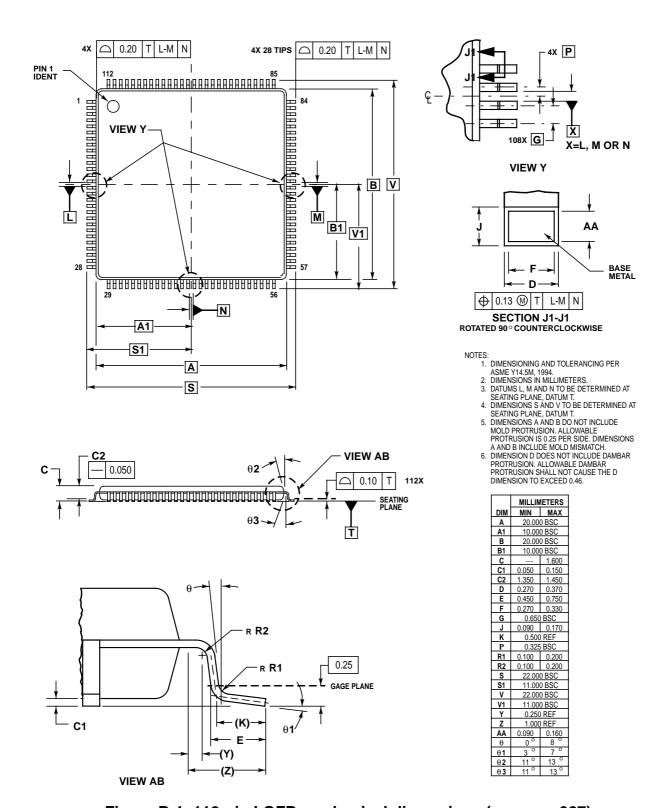

## B.2 112-pin LQFP package

Figure B-1 112-pin LQFP mechanical dimensions (case no. 987)