Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | HCS12                                                                 |

| Core Size                  | 16-Bit                                                                |

| Speed                      | 25MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                            |

| Peripherals                | PWM, WDT                                                              |

| Number of I/O              | 59                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 1K x 8                                                                |

| RAM Size                   | 4K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 5.25V                                                         |

| Data Converters            | A/D 8x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 80-QFP                                                                |

| Supplier Device Package    | 80-QFP (14x14)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s12a64cfue |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **List of Tables**

| Table 0-1 D  | Derivati | ve Differences                                             | 15 |

|--------------|----------|------------------------------------------------------------|----|

| Table 0-2 D  | Docume   | ent References                                             | 17 |

| Table 1-1 D  | Device   | Memory Map for MC9S12DJ64                                  | 25 |

| Table 1-2 D  | Device   | Memory Map for MC9S12D32                                   | 28 |

| \$0000 - \$0 | 000F     | MEBI map 1 of 3 (HCS12 Multiplexed External Bus Interface) | 30 |

| \$0010 - \$0 | 0014     | MMC map 1 of 4 (HCS12 Module Mapping Control)              | 30 |

| \$0015 - \$0 | 0016     | INT map 1 of 2 (HCS12 Interrupt)                           | 31 |

| \$0017 - \$0 | 0019     | Reserved                                                   | 31 |

| \$001A - \$  | 001B     | Device ID Register (Table 1-4)                             | 31 |

| \$001C - \$  | 001D     | MMC map 3 of 4 (HCS12 Module Mapping Control, Table 1-5)   | 31 |

| \$001E - \$  | 001E     | MEBI map 2 of 3 (HCS12 Multiplexed External Bus Interface) | 31 |

| \$001F - \$0 | 001F     | INT map 2 of 2 (HCS12 Interrupt)                           | 32 |

| \$0020 - \$0 | 0027     | Reserved                                                   | 32 |

| \$0028 - \$0 | 002F     | BKP (HCS12 Breakpoint)                                     | 32 |

| \$0030 - \$0 | 0031     | MMC map 4 of 4 (HCS12 Module Mapping Control)              | 32 |

| \$0032 - \$0 | 0033     | MEBI map 3 of 3 (HCS12 Multiplexed External Bus Interface) | 32 |

| \$0034 - \$0 | 003F     | CRG (Clock and Reset Generator)                            | 33 |

| \$0040 - \$0 | 007F     | ECT (Enhanced Capture Timer 16 Bit 8 Channels)             | 33 |

| \$0080 - \$0 | 009F     | ATD0 (Analog to Digital Converter 10 Bit 8 Channel)        | 36 |

| \$00A0 - \$  | 00C7     | PWM (Pulse Width Modulator 8 Bit 8 Channel)                | 37 |

| \$00C8 - \$  | 00CF     | SCI0 (Asynchronous Serial Interface)                       | 39 |

| \$00D0 - \$  | 00D7     | SCI1 (Asynchronous Serial Interface)                       | 39 |

| \$00D8 - \$  | 00DF     | SPI0 (Serial Peripheral Interface)                         | 40 |

| \$00E0 - \$  | 00E7     | IIC (Inter IC Bus)                                         | 40 |

| \$00E8 - \$  | 00EF     | BDLC (Bytelevel Data Link Controller J1850)                | 41 |

| \$00F0 - \$0 | 00FF     | Reserved                                                   | 41 |

| \$0100 - \$0 | 010F     | Flash Control Register (fts64k)                            | 41 |

| \$0110 - \$0 | 011B     | EEPROM Control Register (eets1k)                           | 42 |

| \$011C - \$  | 011F     | Reserved for RAM Control Register                          | 42 |

| \$0120 - \$0 | 013F     | ATD1 (Analog to Digital Converter 10 Bit 8 Channel)        | 43 |

| \$0140 - \$0 | 017F     | CAN0 (Freescale Scalable CAN - FSCAN)                      | 44 |

| Table 1-3 D  | Detailed | SCAN Foreground Receive and Transmit Buffer Layout         | 45 |

| \$0180 - \$0 | 023F     | Reserved                                                   | 46 |

| User Guide                                                                | Versi<br>on | Document Order Number |

|---------------------------------------------------------------------------|-------------|-----------------------|

| HCS12 CPU Reference Manual                                                | V02         | S12CPUV2/D            |

| HCS12 Module Mapping Control (MMC) Block Guide                            | V04         | S12MMCV4/D            |

| HCS12 Multiplexed External Bus Interface (MEBI) Block Guide               | V03         | S12MEBIV3/D           |

| HCS12 Interrupt (INT) Block Guide                                         | V01         | S12INTV1/D            |

| HCS12 Background Debug (BDM) Block Guide                                  | V04         | S12BDMV4/D            |

| HCS12 Breakpoint (BKP) Block Guide                                        | V01         | S12BKPV1/D            |

| Clock and Reset Generator (CRG) Block User Guide                          | V04         | S12CRGV4/D            |

| Oscillator (OSC) Block User Guide                                         | V02         | S12OSCV2/D            |

| Enhanced Capture Timer 16 Bit 8 Channel (ECT_16B8C) Block User Guide      | V01         | S12ECT16B8CV1/D       |

| Analog to Digital Converter 10 Bit 8 Channel (ATD_10B8C) Block User Guide | V02         | S12ATD10B8CV2/D       |

| Inter IC Bus (IIC) Block User Guide                                       | V02         | S12IICV2/D            |

| Asynchronous Serial Interface (SCI) Block User Guide                      | V02         | S12SCIV2/D            |

| Serial Peripheral Interface (SPI) Block User Guide                        | V02         | S12SPIV2/D            |

| Pulse Width Modulator 8 Bit 8 Channel (PWM_8B8C) Block User Guide         | V01         | S12PWM8B8CV1/D        |

| 64K Byte Flash (FTS64K) Block User Guide                                  | V01         | S12FTS64KV1/D         |

| 1K Byte EEPROM (EETS1K) Block User Guide                                  | V01         | S12EETS1KV1/D         |

| Byte Level Data Link Controller -J1850 (BDLC) Block User Guide            | V01         | S12BDLCV1/D           |

| Freescale Scalable CAN (MSCAN) Block User Guide                           | • V02       | S12MSCANV2/D          |

| Voltage Regulator (VREG) Block User Guide                                 | V01         | S12VREGV1/D           |

| Port Integration Module (PIM_9DJ64) Block User Guide                      | V01         | S12PIM9DJ64V1/D       |

#### Table 0-2 Document References

#### 1.5.1 Detailed Register Map

#### \$0000 - \$000F

#### MEBI map 1 of 3 (HCS12 Multiplexed External Bus Interface)

| Address                       | Name      |                 | Bit 7  | Bit 6 | Bit 5    | Bit 4    | Bit 3                                 | Bit 2 | Bit 1                                 | Bit 0 |

|-------------------------------|-----------|-----------------|--------|-------|----------|----------|---------------------------------------|-------|---------------------------------------|-------|

| \$0000                        | PORTA     | Read:<br>Write: | Bit 7  | 6     | 5        | 4        | 3                                     | 2     | 1                                     | Bit 0 |

| \$0001                        | PORTB     | Read:<br>Write: | Bit 7  | 6     | 5        | 4        | 3                                     | 2     | 1                                     | Bit 0 |

| \$0002                        | DDRA      | Read:<br>Write: | Bit 7  | 6     | 5        | 4        | 3                                     | 2     | 1                                     | Bit 0 |

| \$0003                        | DDRB      | Read:<br>Write: | Bit 7  | 6     | 5        | 4        | 3                                     | 2     | 1                                     | Bit 0 |

| \$0004                        | Reserved  | Read:           | 0      | 0     | 0        | 0        | 0                                     | 0     | 0                                     | 0     |

| <b>Ф</b> 0004                 | Reserved  | Write:          |        |       |          |          |                                       |       |                                       |       |

| \$0005                        | Reserved  | Read:           | 0      | 0     | 0        | 0        | 0                                     | 0     | 0                                     | 0     |

| \$0005                        | Reserved  | Write:          |        |       |          |          |                                       |       |                                       |       |

| \$0006                        | Reserved  | Read:           | 0      | 0     | 0        | 0        | 0                                     | 0     | 0                                     | 0     |

| φ0000                         | Reserveu  | Write:          |        |       |          |          |                                       |       |                                       |       |

| \$0007                        | Reserved  | Read:           | 0      | 0     | 0        | 0        | 0                                     | 0     | 0                                     | 0     |

| ψυυυι                         | iteseiveu | Write:          |        |       |          |          |                                       |       |                                       |       |

| \$0008                        | PORTE     | Read:<br>Write: | Bit 7  | 6     | 5        | 4        | 3                                     | 2     | Bit 1                                 | Bit 0 |

| \$0009                        | DDRE      | Read:<br>Write: | Bit 7  | 6     | 5        | 4        | 3                                     | Bit 2 | 0                                     | 0     |

| \$000A                        | PEAR      | Read:<br>Write: | NOACCE | 0     | PIPOE    | NECLK    | LSTRE                                 | RDWE  | 0                                     | 0     |

| \$000B                        | MODE      | Read:<br>Write: | MODC   | MODB  | MODA     | 0        | IVIS                                  | 0     | ЕМК                                   | EME   |

| <b>\$</b> \$\$\$ <b>\$</b> \$ | DUOD      | Read:           |        | 0     | 0        | DUDEE    | 0                                     | 0     |                                       |       |

| \$000C                        | PUCR      | Write:          | PUPKE  |       |          | PUPEE    |                                       |       | PUPBE                                 | PUPAE |

| \$000D                        | RDRIV     | Read:<br>Write: | RDPK   | 0     | 0        | RDPE     | 0                                     | 0     | RDPB                                  | RDPA  |

|                               |           | Read:           | 0      | 0     | 0        | 0        | 0                                     | 0     | 0                                     |       |

| \$000E                        | EBICTL    | Write:          | U U    | U U   | <b>v</b> | <u> </u> | , , , , , , , , , , , , , , , , , , , |       | , , , , , , , , , , , , , , , , , , , | ESTR  |

| •                             | _         | Read:           | 0      | 0     | 0        | 0        | 0                                     | 0     | 0                                     | 0     |

| \$000F                        | Reserved  | Write:          | -      | -     |          | -        | -                                     | -     | -                                     | -     |

|                               |           |                 |        |       |          |          |                                       |       |                                       |       |

\$0010 - \$0014

#### MMC map 1 of 4 (HCS12 Module Mapping Control)

| Address | Name   |        | Bit 7    | Bit 6 | Bit 5    | Bit 4 | Bit 3   | Bit 2 | Bit 1 | Bit 0    |

|---------|--------|--------|----------|-------|----------|-------|---------|-------|-------|----------|

| \$0010  | INITRM | Read:  | RAM15    | RAM14 | RAM13    | RAM12 | RAM11   | 0     | 0     | RAMHAL   |

| \$0010  |        | Write: | KAIVI 15 | NAM14 | NAIVI 13 | NAMIZ | NAIVITT |       |       | RAIVITAL |

| \$0011  | INITRG | Read:  | 0        | REG14 | REG13    | REG12 | REG11   | 0     | 0     | 0        |

| φυστι   | INTIKO | Write: |          | NL014 | NEG13    | NLG12 | NLO11   |       |       |          |

#### \$0040 - \$007F

| Address | Name      |

|---------|-----------|

| \$007C  | TC2H (hi) |

| \$007D  | TC2H (lo) |

| \$007E  | TC3H (hi) |

| \$007F  | TC3H (lo) |

#### ECT (Enhanced Capture Timer 16 Bit 8 Channels)

| [      | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------|--------|-------|-------|-------|-------|-------|-------|-------|

| Read:  | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

| Write: |        |       |       |       |       |       |       |       |

| Read:  | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| Write: |        |       |       |       |       |       |       |       |

| Read:  | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

| Write: |        |       |       |       |       |       |       |       |

| Read:  | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| Write: |        |       |       |       |       |       |       |       |

#### \$0080 - \$009F

#### ATD0 (Analog to Digital Converter 10 Bit 8 Channel)

| \$0080         ATDOCT           \$0081         ATDOCT           \$0082         ATDOCT           \$0083         ATDOCT | .1<br>Read:<br>Write:<br>Read:   | 0               | 0    | 0     | 0       | 0      | 0     | 0     | 0     |

|-----------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------|------|-------|---------|--------|-------|-------|-------|

| \$0081 ATDOCT<br>\$0082 ATDOCT                                                                                        | .1<br>Read:<br>Write:<br>Read:   |                 | 0    |       |         |        |       |       | u v l |

| \$0082 ATD0CT                                                                                                         | . <sup>1</sup> Write:<br>2 Read: |                 | 0    | 0     |         |        |       |       |       |

| \$0082 ATD0CT                                                                                                         | 2 Read:                          |                 |      | 0     | 0       | 0      | 0     | 0     | 0     |

|                                                                                                                       | .,                               |                 |      |       |         |        |       |       |       |

| \$0083 ATD0CT                                                                                                         |                                  |                 | AFFC | AWAI  | ETRIGLE | ETRIGP | ETRIG | ASCIE | ASCIF |

|                                                                                                                       | .3 Read:<br>Write:               | 0               | S8C  | S4C   | S2C     | S1C    | FIFO  | FRZ1  | FRZ0  |

| \$0084 ATD0CT                                                                                                         | .4 Read:<br>Write:               | I SRESS         | SMP1 | SMP0  | PRS4    | PRS3   | PRS2  | PRS1  | PRS0  |

| \$0085 ATD0CT                                                                                                         | .5 Read:<br>Write:               | 1 1 1 1 1 1 1 1 | DSGN | SCAN  | MULT    | 0      | СС    | СВ    | CA    |

| \$0086 ATDOSTA                                                                                                        | Read:                            | SCF             | 0    | ETORF | FIFOR   | 0      | CC2   | CC1   | CC0   |

| 40000 AID0017                                                                                                         | Write:                           | 501             |      |       |         |        |       |       |       |

| \$0087 Reserve                                                                                                        | Read:                            | 0               | 0    | 0     | 0       | 0      | 0     | 0     | 0     |

|                                                                                                                       | vvrite:                          |                 |      |       |         |        |       |       |       |

| \$0088 ATDOTES                                                                                                        | TO Read:                         |                 | 0    | 0     | 0       | 0      | 0     | 0     | 0     |

| <i>••••••</i>                                                                                                         | Write:                           |                 |      |       |         |        |       |       |       |

| \$0089 ATD0TES                                                                                                        | T1 Read:                         | 0               | 0    | 0     | 0       | 0      | 0     | 0     | SC    |

|                                                                                                                       | Write:                           |                 | -    |       |         |        | -     |       |       |

| \$008A Reserve                                                                                                        | d Read:                          | 0               | 0    | 0     | 0       | 0      | 0     | 0     | 0     |

|                                                                                                                       | Write:                           | 0057            | 0050 | 0055  | 0054    | 0050   | 0050  | 0054  | 0050  |

| \$008B ATDOSTA                                                                                                        | Γ1 Read:                         | CCF7            | CCF6 | CCF5  | CCF4    | CCF3   | CCF2  | CCF1  | CCF0  |

|                                                                                                                       | ' Write:<br>, Read:              | 0               | 0    | 0     | 0       | 0      | 0     | 0     | 0     |

| \$008C Reserve                                                                                                        | d Write:                         | 0               | 0    | 0     | 0       | 0      | 0     | 0     | 0     |

|                                                                                                                       | Read:                            |                 |      |       |         |        |       |       |       |

| \$008D ATDODIE                                                                                                        | N Write:                         |                 | 6    | 5     | 4       | 3      | 2     | 1     | Bit 0 |

|                                                                                                                       | Road.                            |                 | 0    | 0     | 0       | 0      | 0     | 0     | 0     |

| \$008E Reserve                                                                                                        | d Write:                         |                 | Ŭ    |       | Ŭ       |        |       | Ŭ     | Ű     |

|                                                                                                                       | Road.                            |                 | 6    | 5     | 4       | 3      | 2     | 1     | BIT 0 |

| \$008F PORTAL                                                                                                         | 0<br>Write:                      |                 | -    | -     |         | -      | _     |       |       |

| <b>4</b> 0000 <b>475 5 5</b>                                                                                          | Road.                            |                 | 14   | 13    | 12      | 11     | 10    | 9     | Bit8  |

| \$0090 ATD0DR                                                                                                         | H Write:                         |                 |      |       |         |        |       |       |       |

|                                                                                                                       | Road.                            |                 | Bit6 | 0     | 0       | 0      | 0     | 0     | 0     |

| \$0091 ATD0DR                                                                                                         | Write:                           |                 |      |       |         |        |       |       |       |

#### \$00D0 - \$00D7 SCI1 (Asynchronous Serial Interface)

| Address | Name     | [      | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2   | Bit 1 | Bit 0 |

|---------|----------|--------|-------|-------|-------|-------|-------|---------|-------|-------|

| \$00D5  | SCI1SR2  | Read:  | 0     | 0     | 0     | 0     | 0     | BRK13   | TXDIR | RAF   |

| \$00D3  | 30113112 | Write: |       |       |       |       |       | DIVINIO | INDIN |       |

| \$00D6  | SCI1DRH  | Read:  | R8    | Т8    | 0     | 0     | 0     | 0       | 0     | 0     |

| \$00D0  | SCHERN   | Write: |       | 10    |       |       |       |         |       |       |

| \$00D7  | SCI1DRL  | Read:  | R7    | R6    | R5    | R4    | R3    | R2      | R1    | R0    |

| 900D7   | SCHERL   | Write: | T7    | T6    | T5    | T4    | T3    | T2      | T1    | Т0    |

#### \$00D8 - \$00DF SPI0 (Serial Peripheral Interface)

|                 |          | _               |       |        |       |        |         |        |         |       |

|-----------------|----------|-----------------|-------|--------|-------|--------|---------|--------|---------|-------|

| Address         | Name     |                 | Bit 7 | Bit 6  | Bit 5 | Bit 4  | Bit 3   | Bit 2  | Bit 1   | Bit 0 |

| \$00D8          | SPI0CR1  | Read:<br>Write: | SPIE  | SPE    | SPTIE | MSTR   | CPOL    | CPHA   | SSOE    | LSBFE |

| \$00D9          | SPI0CR2  | Read:           | 0     | 0      | 0     | MODFEN | BIDIROE | 0      | SPISWAI | SPC0  |

| \$00D9          | 3FIUCKZ  | Write:          |       |        |       | WODFEN | BIDIKUE |        | SFISWAI | 3-00  |

| \$00DA          | SPI0BR   | Read:           | 0     | SPPR2  | SPPR1 | SPPR0  | 0       | SPR2   | SPR1    | SPR0  |

| 400DA           | SFIDER   | Write:          |       | 511172 | SPERT | 51110  |         | OF IX2 | SERT    | 5110  |

| \$00DB          | SPI0SR   | Read:           | SPIF  | 0      | SPTEF | MODF   | 0       | 0      | 0       | 0     |

| 900DD           | 51 1051  | Write:          |       |        |       |        |         |        |         |       |

| \$00DC          | Reserved | Read:           | 0     | 0      | 0     | 0      | 0       | 0      | 0       | 0     |

| \$00DC          | Reserved | Write:          |       |        |       |        |         |        |         |       |

| \$00DD          | SPI0DR   | Read:           | Bit7  | 6      | 5     | 4      | 3       | 2      | 1       | Bit0  |

| <b>WOODD</b>    | OFIDER   | Write:          | Diti  | 0      | 5     | 7      | 5       | 2      | I       | Dito  |

| \$00DE          | Reserved | Read:           | 0     | 0      | 0     | 0      | 0       | 0      | 0       | 0     |

| <b>JUODE</b>    | Reserved | Write:          |       |        |       |        |         |        |         |       |

| \$00DE          | Peserved | Read:           | 0     | 0      | 0     | 0      | 0       | 0      | 0       | 0     |

| \$00DF Reserved |          | Write:          |       |        |       |        |         |        |         |       |

#### \$00E0 - \$00E7

#### IIC (Inter IC Bus)

|          |         | -               |       |       |         |       |       |       |       |         |

|----------|---------|-----------------|-------|-------|---------|-------|-------|-------|-------|---------|

| Address  | Name    |                 | Bit 7 | Bit 6 | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0   |

| \$00E0   | IBAD    | Read:<br>Write: | ADR7  | ADR6  | ADR5    | ADR4  | ADR3  | ADR2  | ADR1  | 0       |

| \$00E1   | IBFD    | Read:<br>Write: | IBC7  | IBC6  | IBC5    | IBC4  | IBC3  | IBC2  | IBC1  | IBC0    |

| \$00E2   | IBCR    | Read:           | IBEN  | IBIE  | MS/SL   | TX/RX | ТХАК  | 0     | 0     | IBSWAI  |

| ΦU0E2    | IDUK    | Write:          | IDEIN | IDIE  | IVIO/OL | 1///  | IVAU  | RSTA  |       | IDSVVAI |

| \$00E3   | IBSR    | Read:           | TCF   | IAAS  | IBB     | IBAL  | 0     | SRW   | IBIF  | RXAK    |

| \$U0E3   | IDOK    | Write:          |       |       |         | IDAL  |       |       | IDIF  |         |

| \$00E4   | IBDR    | Read:<br>Write: | D7    | D6    | D5      | D4    | D3    | D2    | D1    | D 0     |

| \$00E5 R | eserved | Read:           | 0     | 0     | 0       | 0     | 0     | 0     | 0     | 0       |

| 900E2 K  | eserved | Write:          |       |       |         |       |       |       |       |         |

|          | eserved | Read:           | 0     | 0     | 0       | 0     | 0     | 0     | 0     | 0       |

| \$00E6 R | eserved | Write:          |       |       |         |       |       |       |       |         |

| ¢00E7 D  | acarvad | Read:           | 0     | 0     | 0       | 0     | 0     | 0     | 0     | 0       |

| \$00E7 R | eserved | Write:          |       |       |         |       |       |       |       |         |

#### \$0240 - \$027F

#### PIM (Port Integration Module)

| Address                                                            | Name                                                        |                                                                                                                                                                                                               | Bit 7                                                               | Bit 6                                                               | Bit 5                                                               | Bit 4                                                               | Bit 3                                                               | Bit 2                                                               | Bit 1                                                               | Bit 0                                                               |

|--------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|

| \$024A                                                             | DDRS                                                        | Read:<br>Write:                                                                                                                                                                                               | DDRS7                                                               | DDRS7                                                               | DDRS5                                                               | DDRS4                                                               | DDRS3                                                               | DDRS2                                                               | DDRS1                                                               | DDRS0                                                               |

| \$024B                                                             | RDRS                                                        | Read:                                                                                                                                                                                                         | RDRS7                                                               | RDRS6                                                               | RDRS5                                                               | RDRS4                                                               | RDRS3                                                               | RDRS2                                                               | RDRS1                                                               | RDRS0                                                               |

|                                                                    |                                                             | Write:<br>Read:                                                                                                                                                                                               |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |

| \$024C                                                             | PERS                                                        | Write:                                                                                                                                                                                                        | PERS7                                                               | PERS6                                                               | PERS5                                                               | PERS4                                                               | PERS3                                                               | PERS2                                                               | PERS1                                                               | PERS0                                                               |

| \$024D                                                             | PPSS                                                        | Read:<br>Write:                                                                                                                                                                                               | PPSS7                                                               | PPSS6                                                               | PPSS5                                                               | PPSS4                                                               | PPSS3                                                               | PPSS2                                                               | PPSS1                                                               | PPSS0                                                               |

| \$024E                                                             | WOMS                                                        | Read:<br>Write:                                                                                                                                                                                               | WOMS7                                                               | WOMS6                                                               | WOMS5                                                               | WOMS4                                                               | WOMS3                                                               | WOMS2                                                               | WOMS1                                                               | WOMS0                                                               |

| \$024F                                                             | Reserved                                                    | Read:<br>Write:                                                                                                                                                                                               | 0                                                                   | 0                                                                   | 0                                                                   | 0                                                                   | 0                                                                   | 0                                                                   | 0                                                                   | 0                                                                   |

| \$0250                                                             | PTM                                                         | Read:                                                                                                                                                                                                         | PTM7                                                                | PTM6                                                                | PTM5                                                                | PTM4                                                                | PTM3                                                                | PTM2                                                                | PTM1                                                                | PTM0                                                                |

|                                                                    |                                                             | Write:<br>Read:                                                                                                                                                                                               | PTIM7                                                               | PTIM6                                                               | PTIM5                                                               | PTIM4                                                               | PTIM3                                                               | PTIM2                                                               | PTIM1                                                               | PTIMO                                                               |

| \$0251                                                             | PTIM                                                        | Write:                                                                                                                                                                                                        |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     | 1 11112                                                             |                                                                     |                                                                     |

| \$0252                                                             | DDRM                                                        | Read:<br>Write:                                                                                                                                                                                               | DDRM7                                                               | DDRM7                                                               | DDRM5                                                               | DDRM4                                                               | DDRM3                                                               | DDRM2                                                               | DDRM1                                                               | DDRM0                                                               |

| \$0253                                                             | RDRM                                                        | Read:<br>Write:                                                                                                                                                                                               | RDRM7                                                               | RDRM6                                                               | RDRM5                                                               | RDRM4                                                               | RDRM3                                                               | RDRM2                                                               | RDRM1                                                               | RDRM0                                                               |

| \$0254                                                             | PERM                                                        | Read:<br>Write:                                                                                                                                                                                               | PERM7                                                               | PERM6                                                               | PERM5                                                               | PERM4                                                               | PERM3                                                               | PERM2                                                               | PERM1                                                               | PERM0                                                               |

| \$0255                                                             | PPSM                                                        | Read:<br>Write:                                                                                                                                                                                               | PPSM7                                                               | PPSM6                                                               | PPSM5                                                               | PPSM4                                                               | PPSM3                                                               | PPSM2                                                               | PPSM1                                                               | PPSM0                                                               |

| \$0256                                                             | WOMM                                                        | Read:<br>Write:                                                                                                                                                                                               | WOMM7                                                               | WOMM6                                                               | WOMM5                                                               | WOMM4                                                               | WOMM3                                                               | WOMM2                                                               | WOMM1                                                               | WOMM0                                                               |

| \$0257                                                             | MODRR                                                       | Read:<br>Write:                                                                                                                                                                                               | 0                                                                   | 0                                                                   | 0                                                                   | MODRR4                                                              | 0                                                                   | 0                                                                   | MODRR1                                                              | MODRR0                                                              |

| \$0258                                                             |                                                             |                                                                                                                                                                                                               |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |

|                                                                    | PTP                                                         | Read:<br>Write:                                                                                                                                                                                               | PTP7                                                                | PTP6                                                                | PTP5                                                                | PTP4                                                                | PTP3                                                                | PTP2                                                                | PTP1                                                                | PTP0                                                                |

| \$0259                                                             | PTP<br>PTIP                                                 | Write:<br>Read:                                                                                                                                                                                               | PTP7<br>PTIP7                                                       | PTP6<br>PTIP6                                                       | PTP5<br>PTIP5                                                       | PTP4<br>PTIP4                                                       | PTP3<br>PTIP3                                                       | PTP2<br>PTIP2                                                       | PTP1<br>PTIP1                                                       | PTP0<br>PTIP0                                                       |

| \$0259                                                             | PTIP                                                        | Write:<br>Read:<br>Write:                                                                                                                                                                                     | PTIP7                                                               | PTIP6                                                               | PTIP5                                                               | PTIP4                                                               | PTIP3                                                               | PTIP2                                                               | PTIP1                                                               | PTIP0                                                               |

| \$0259<br>\$025A                                                   |                                                             | Write:<br>Read:<br>Write:<br>Read:<br>Write:                                                                                                                                                                  |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |

|                                                                    | PTIP                                                        | Write:<br>Read:<br>Write:<br>Read:                                                                                                                                                                            | PTIP7                                                               | PTIP6                                                               | PTIP5                                                               | PTIP4                                                               | PTIP3                                                               | PTIP2                                                               | PTIP1                                                               | PTIP0                                                               |

| \$025A                                                             | PTIP<br>DDRP                                                | Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:                                                                                                                                                         | PTIP7<br>DDRP7                                                      | PTIP6<br>DDRP7                                                      | PTIP5<br>DDRP5                                                      | PTIP4<br>DDRP4                                                      | PTIP3<br>DDRP3                                                      | PTIP2<br>DDRP2                                                      | PTIP1<br>DDRP1                                                      | PTIP0<br>DDRP0                                                      |

| \$025A<br>\$025B                                                   | PTIP<br>DDRP<br>RDRP                                        | Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:                                                                                                                                      | PTIP7<br>DDRP7<br>RDRP7                                             | PTIP6<br>DDRP7<br>RDRP6                                             | PTIP5<br>DDRP5<br>RDRP5                                             | PTIP4<br>DDRP4<br>RDRP4                                             | PTIP3<br>DDRP3<br>RDRP3                                             | PTIP2<br>DDRP2<br>RDRP2                                             | PTIP1<br>DDRP1<br>RDRP1                                             | PTIP0<br>DDRP0<br>RDRP0                                             |

| \$025A<br>\$025B<br>\$025C                                         | PTIP<br>DDRP<br>RDRP<br>PERP                                | Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:                                                                             | PTIP7<br>DDRP7<br>RDRP7<br>PERP7                                    | PTIP6<br>DDRP7<br>RDRP6<br>PERP6                                    | PTIP5<br>DDRP5<br>RDRP5<br>PERP5                                    | PTIP4<br>DDRP4<br>RDRP4<br>PERP4                                    | PTIP3<br>DDRP3<br>RDRP3<br>PERP3                                    | PTIP2<br>DDRP2<br>RDRP2<br>PERP2                                    | PTIP1<br>DDRP1<br>RDRP1<br>PERP1                                    | PTIP0<br>DDRP0<br>RDRP0<br>PERP0                                    |

| \$025A<br>\$025B<br>\$025C<br>\$025D                               | PTIP<br>DDRP<br>RDRP<br>PERP<br>PPSP                        | Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:                                                                             | PTIP7<br>DDRP7<br>RDRP7<br>PERP7<br>PPSP7                           | PTIP6<br>DDRP7<br>RDRP6<br>PERP6<br>PPSP6                           | PTIP5<br>DDRP5<br>RDRP5<br>PERP5<br>PPSP5                           | PTIP4<br>DDRP4<br>RDRP4<br>PERP4<br>PPSP4                           | PTIP3<br>DDRP3<br>RDRP3<br>PERP3<br>PPSP3                           | PTIP2<br>DDRP2<br>RDRP2<br>PERP2<br>PPSP2                           | PTIP1<br>DDRP1<br>RDRP1<br>PERP1<br>PPSP1                           | PTIP0<br>DDRP0<br>RDRP0<br>PERP0<br>PPSS0                           |

| \$025A<br>\$025B<br>\$025C<br>\$025D<br>\$025E                     | PTIP<br>DDRP<br>RDRP<br>PERP<br>PPSP<br>PIEP                | Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Mrite:<br>Read:                                       | PTIP7<br>DDRP7<br>RDRP7<br>PERP7<br>PPSP7<br>PIEP7                  | PTIP6<br>DDRP7<br>RDRP6<br>PERP6<br>PPSP6<br>PIEP6                  | PTIP5<br>DDRP5<br>RDRP5<br>PERP5<br>PPSP5<br>PIEP5                  | PTIP4<br>DDRP4<br>RDRP4<br>PERP4<br>PPSP4<br>PIEP4                  | PTIP3<br>DDRP3<br>RDRP3<br>PERP3<br>PPSP3<br>PIEP3                  | PTIP2<br>DDRP2<br>RDRP2<br>PERP2<br>PPSP2<br>PIEP2                  | PTIP1<br>DDRP1<br>RDRP1<br>PERP1<br>PPSP1<br>PIEP1                  | PTIP0<br>DDRP0<br>RDRP0<br>PERP0<br>PPSS0<br>PIEP0                  |

| \$025A<br>\$025B<br>\$025C<br>\$025D<br>\$025E<br>\$025F<br>\$0260 | PTIP<br>DDRP<br>RDRP<br>PERP<br>PPSP<br>PIEP<br>PIFP<br>PTH | Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:                    | PTIP7<br>DDRP7<br>RDRP7<br>PERP7<br>PPSP7<br>PIEP7<br>PIFP7         | PTIP6<br>DDRP7<br>RDRP6<br>PERP6<br>PIEP6<br>PIFP6                  | PTIP5<br>DDRP5<br>RDRP5<br>PERP5<br>PPSP5<br>PIEP5<br>PIFP5         | PTIP4<br>DDRP4<br>RDRP4<br>PERP4<br>PPSP4<br>PIEP4<br>PIFP4         | PTIP3<br>DDRP3<br>RDRP3<br>PERP3<br>PPSP3<br>PIEP3<br>PIFP3         | PTIP2<br>DDRP2<br>RDRP2<br>PERP2<br>PPSP2<br>PIEP2<br>PIFP2         | PTIP1<br>DDRP1<br>RDRP1<br>PERP1<br>PPSP1<br>PIEP1<br>PIFP1         | PTIP0<br>DDRP0<br>RDRP0<br>PERP0<br>PPSS0<br>PIEP0<br>PIFP0         |

| \$025A<br>\$025B<br>\$025C<br>\$025D<br>\$025E<br>\$025F           | PTIP<br>DDRP<br>RDRP<br>PERP<br>PPSP<br>PIEP<br>PIFP        | Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read: | PTIP7<br>DDRP7<br>RDRP7<br>PERP7<br>PPSP7<br>PIEP7<br>PIFP7<br>PTH7 | PTIP6<br>DDRP7<br>RDRP6<br>PERP6<br>PPSP6<br>PIEP6<br>PIFP6<br>PTH6 | PTIP5<br>DDRP5<br>RDRP5<br>PERP5<br>PPSP5<br>PIEP5<br>PIFP5<br>PTH5 | PTIP4<br>DDRP4<br>RDRP4<br>PERP4<br>PPSP4<br>PIEP4<br>PIFP4<br>PTH4 | PTIP3<br>DDRP3<br>RDRP3<br>PERP3<br>PPSP3<br>PIEP3<br>PIFP3<br>PTH3 | PTIP2<br>DDRP2<br>RDRP2<br>PERP2<br>PPSP2<br>PIEP2<br>PIFP2<br>PTH2 | PTIP1<br>DDRP1<br>RDRP1<br>PERP1<br>PPSP1<br>PIEP1<br>PIFP1<br>PTH1 | PTIP0<br>DDRP0<br>RDRP0<br>PERP0<br>PPSS0<br>PIEP0<br>PIFP0<br>PTH0 |

#### 2.3.14 PE6 / MODB / IPIPE1 — Port E I/O Pin 6

PE6 is a general purpose input or output pin. It is used as a MCU operating mode select pin during reset. The state of this pin is latched to the MODB bit at the rising edge of  $\overline{\text{RESET}}$ . This pin is shared with the instruction queue tracking signal IPIPE1. This pin is an input with a pull-down device which is only active when  $\overline{\text{RESET}}$  is low.

#### 2.3.15 PE5 / MODA / IPIPE0 — Port E I/O Pin 5

PE5 is a general purpose input or output pin. It is used as a MCU operating mode select pin during reset. The state of this pin is latched to the MODA bit at the rising edge of  $\overline{\text{RESET}}$ . This pin is shared with the instruction queue tracking signal IPIPE0. This pin is an input with a pull-down device which is only active when  $\overline{\text{RESET}}$  is low.

#### 2.3.16 PE4 / ECLK — Port E I/O Pin 4

PE4 is a general purpose input or output pin. It can be configured to drive the internal bus clock ECLK. ECLK can be used as a timing reference.

#### 2.3.17 PE3 / LSTRB / TAGLO — Port E I/O Pin 3

PE3 is a general purpose input or output pin. In MCU expanded modes of operation,  $\overline{\text{LSTRB}}$  can be used for the low-byte strobe function to indicate the type of bus access and when instruction tagging is on,  $\overline{\text{TAGLO}}$  is used to tag the low half of the instruction word being read into the instruction queue.

#### 2.3.18 PE2 / R/W - Port E I/O Pin 2

PE2 is a general purpose input or output pin. In MCU expanded modes of operations, this pin drives the read/write output signal for the external bus. It indicates the direction of data on the external bus.

### 2.3.19 PE1 / IRQ — Port E Input Pin 1

PE1 is a general purpose input pin and the maskable interrupt request input that provides a means of applying asynchronous interrupt requests. This will wake up the MCU from STOP or WAIT mode.

#### 2.3.20 PE0 / XIRQ — Port E Input Pin 0

PE0 is a general purpose input pin and the non-maskable interrupt request input that provides a means of applying asynchronous interrupt requests. This will wake up the MCU from STOP or WAIT mode.

#### 2.3.21 PH7 / KWH7 — Port H I/O Pin 7

PH7 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode.

| Mnemonic  | Pin Number  | Nominal | Description                                                                                                                                    |  |  |  |

|-----------|-------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| winemonic | 112-pin QFP | Voltage | Description                                                                                                                                    |  |  |  |

| VDDPLL    | 43          | 2.5V    | Provides operating voltage and ground for the Phased-Locked                                                                                    |  |  |  |

| VSSPLL    | 45          | 0V      | Loop. This allows the supply voltage to the PLL to be<br>bypassed independently. Internal power and ground<br>generated by internal regulator. |  |  |  |

| VREGEN    | 97          | 5.0V    | Internal Voltage Regulator enable/disable                                                                                                      |  |  |  |

#### 2.4.1 VDDX, VSSX — Power & Ground Pins for I/O Drivers

External power and ground for I/O drivers. Because fast signal transitions place high, short-duration current demands on the power supply, use bypass capacitors with high-frequency characteristics and place them as close to the MCU as possible. Bypass requirements depend on how heavily the MCU pins are loaded.

VDDX and VSSX are the supplies for Ports J, K, M, P, T and S.

# 2.4.2 VDDR, VSSR — Power & Ground Pins for I/O Drivers & for Internal Voltage Regulator

External power and ground for I/O drivers and input to the internal voltage regulator. Because fast signal transitions place high, short-duration current demands on the power supply, use bypass capacitors with high-frequency characteristics and place them as close to the MCU as possible. Bypass requirements depend on how heavily the MCU pins are loaded.

VDDR and VSSR are the supplies for Ports A, B, E and H.

#### 2.4.3 VDD1, VDD2, VSS1, VSS2 — Internal Logic Power Supply Pins

Power is supplied to the MCU through VDD and VSS. Because fast signal transitions place high, short-duration current demands on the power supply, use bypass capacitors with high-frequency characteristics and place them as close to the MCU as possible. This 2.5V supply is derived from the internal voltage regulator. There is no static load on those pins allowed. The internal voltage regulator is turned off, if VREGEN is tied to ground.

**NOTE:** No load allowed except for bypass capacitors.

#### 2.4.4 VDDA, VSSA — Power Supply Pins for ATD0/ATD1 and VREG

VDDA, VSSA are the power supply and ground input pins for the voltage regulator and the two analog to digital converters. It also provides the reference for the internal voltage regulator. This allows the supply voltage to ATD0/ATD1 and the reference voltage to be bypassed independently.

#### 4.3.2.2 Executing from External Memory

The user may wish to execute from external space with a secured microcontroller. This is accomplished by resetting directly into expanded mode. The internal FLASH and EEPROM will be disabled. BDM operations will be blocked.

#### 4.3.3 Unsecuring the Microcontroller

In order to unsecure the microcontroller, the internal FLASH and EEPROM must be erased. This can be done through an external program in expanded mode or via a sequence of BDM commands. Unsecuring is also possible via the Backdoor Key Access. Refer to Flash Block Guide for details.

Once the user has erased the FLASH and EEPROM, the part can be reset into special single chip mode. This invokes a program that verifies the erasure of the internal FLASH and EEPROM. Once this program completes, the user can erase and program the FLASH security bits to the unsecured state. This is generally done through the BDM, but the user could also change to expanded mode (by writing the mode bits through the BDM) and jumping to an external program (again through BDM commands). Note that if the part goes through a reset before the security bits are reprogrammed to the unsecure state, the part will be secured again.

### 4.4 Low Power Modes

The microcontroller features three main low power modes. Consult the respective Block User Guide for information on the module behavior in Stop, Pseudo Stop, and Wait Mode. An important source of information about the clock system is the Clock and Reset Generator User Guide (CRG).

#### 4.4.1 Stop

Executing the CPU STOP instruction stops all clocks and the oscillator thus putting the chip in fully static mode. Wake up from this mode can be done via reset or external interrupts.

#### 4.4.2 Pseudo Stop

This mode is entered by executing the CPU STOP instruction. In this mode the oscillator is still running and the Real Time Interrupt (RTI) or Watchdog (COP) sub module can stay active. Other peripherals are turned off. This mode consumes more current than the full STOP mode, but the wake up time from this mode is significantly shorter.

#### 4.4.3 Wait

This mode is entered by executing the CPU WAI instruction. In this mode the CPU will not execute instructions. The internal CPU signals (address and data bus) will be fully static. All peripherals stay active. For further power consumption the peripherals can individually turn off their local clocks.

#### 4.4.4 Run

Although this is not a low power mode, unused peripheral modules should not be enabled in order to save power.

#### MC9S12DJ64 Device User Guide — V01.20

Consult the FTS64K Block User Guide for information about the flash module.

The "S12 LRAE" is a generic Load RAM and Execute (LRAE) program which will be programmed into the flash memory of this device during manufacture. This LRAE program will provide greater programming flexibility to the end users by allowing the device to be programmed directly using CAN or SCI after it is assembled on the PCB. Use of the LRAE program is at the discretion of the end user and, if not required, it must simply be erased prior to flash programming. For more details of the S12 LRAE and its implementation, please see the S12 LREA Application Note (AN2546/D).

It is planned that most HC9S12 devices manufactured after Q1 of 2004 will be shipped with the S12 LRAE programmed in the Flash. Exact details of the changeover (ie blank to programmed) for each product will be communicated in advance via GPCN and will be traceable by the customer via datecode marking on the device.

Please contact Freescale SPS Sales if you have any additional questions.

# Section 17 EEPROM 1K Block Description

Consult the EETS1K Block User Guide for information about the EEPROM module.

# Section 18 RAM Block Description

This module supports single-cycle misaligned word accesses.

# Section 19 MSCAN Block Description

Consult the MSCAN Block User Guide for information about the Freescale Scalable CAN Module.

# Section 20 Port Integration Module (PIM) Block Description

Consult the PIM\_9DJ64 Block User Guide for information about the Port Integration Module.

# Section 21 Voltage Regulator (VREG) Block Description

Consult the VREG Block User Guide for information about the dual output linear voltage regulator.

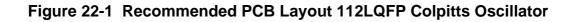

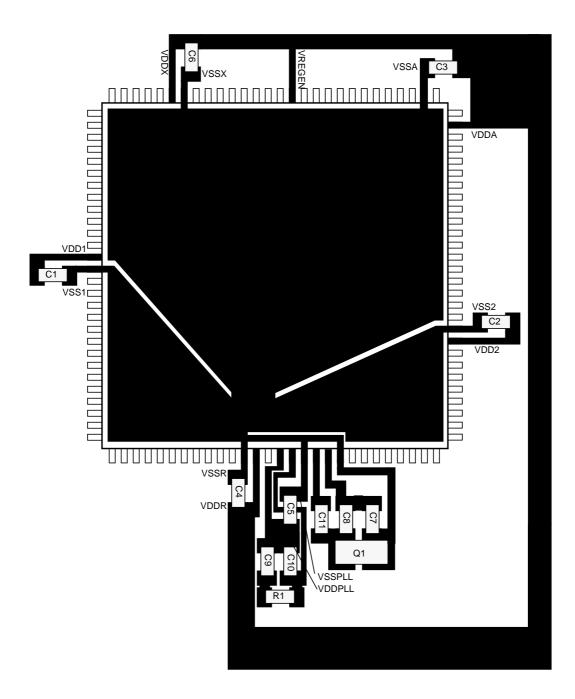

# Section 22 Printed Circuit Board Layout Proposals

Figure 22-2 Recommended PCB Layout for 80QFP Colpitts Oscillator

$T_{\Delta}$  = Ambient Temperature, [°C]

$P_{D}$  = Total Chip Power Dissipation, [W]

$$\Theta_{JA}$$

= Package Thermal Resistance, [°C/W]

The total power dissipation can be calculated from:

P<sub>INT</sub> = Chip Internal Power Dissipation, [W]

Two cases with internal voltage regulator enabled and disabled must be considered:

1. Internal Voltage Regulator disabled

$$P_{INT} = I_{DD} \cdot V_{DD} + I_{DDPLL} \cdot V_{DDPLL} + I_{DDA} \cdot V_{DDA}$$

$$P_{IO} = \sum_{i} R_{DSON} \cdot I_{IO}^{2}_{i}$$

$P_{\rm IO}$  is the sum of all output currents on I/O ports associated with VDDX and VDDR.

For R<sub>DSON</sub> is valid:

$$R_{DSON} = \frac{V_{OL}}{I_{OL}}$$

; for outputs driven low

respectively

$$R_{DSON} = \frac{V_{DD5} - V_{OH}}{I_{OH}}$$

; for outputs driven high

2. Internal voltage regulator enabled

$$P_{INT} = I_{DDR} \cdot V_{DDR} + I_{DDA} \cdot V_{DDA}$$

$I_{DDR}$  is the current shown in **Table A-7** and not the overall current flowing into VDDR, which additionally contains the current flowing into the external loads with output high.

$$P_{IO} = \sum_{i} R_{DSON} \cdot I_{IO_{i}}^{2}$$

$P_{IO}$  is the sum of all output currents on I/O ports associated with VDDX and VDDR.

## A.2 ATD Characteristics

This section describes the characteristics of the analog to digital converter.

#### A.2.1 ATD Operating Characteristics

The **Table A-8** shows conditions under which the ATD operates.

The following constraints exist to obtain full-scale, full range results:

$V_{SSA} \le V_{RL} \le V_{IN} \le V_{RH} \le V_{DDA}$ . This constraint exists since the sample buffer amplifier can not drive beyond the power supply levels that it ties to. If the input level goes outside of this range it will effectively be clipped.

| Conditions are shown in Table A-4 unless otherwise noted |   |                                                                                                                 |                                          |                                         |      |                                         |              |

|----------------------------------------------------------|---|-----------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------------|------|-----------------------------------------|--------------|

| Num                                                      | С | Rating                                                                                                          | Symbol                                   | Min                                     | Тур  | Max                                     | Unit         |

| 1                                                        | D | Reference Potential<br>Low<br>High                                                                              | V <sub>RL</sub><br>V <sub>RH</sub>       | V <sub>SSA</sub><br>V <sub>DDA</sub> /2 |      | V <sub>DDA</sub> /2<br>V <sub>DDA</sub> | V<br>V       |

| 2                                                        | С | Differential Reference Voltage <sup>1</sup>                                                                     | $V_{RH}-V_{RL}$                          | 4.50                                    | 5.00 | 5.25                                    | V            |

| 3                                                        | D | ATD Clock Frequency                                                                                             | f <sub>ATDCLK</sub>                      | 0.5                                     |      | 2.0                                     | MHz          |

| 4                                                        | D | ATD 10-Bit Conversion Period<br>Clock Cycles <sup>2</sup><br>Conv, Time at 2.0MHz ATD Clock f <sub>ATDCLK</sub> |                                          | 14<br>7                                 |      | 28<br>14                                | Cycles<br>μs |

| 5                                                        | D | ATD 8-Bit Conversion Period<br>Clock Cycles <sup>2</sup><br>Conv, Time at 2.0MHz ATD Clock f <sub>ATDCLK</sub>  | N <sub>CONV8</sub><br>T <sub>CONV8</sub> | 12<br>6                                 |      | 26<br>13                                | Cycles<br>μs |

| 6                                                        | D | Recovery Time (V <sub>DDA</sub> =5.0 Volts)                                                                     | t <sub>REC</sub>                         |                                         |      | 20                                      | μs           |

| 7                                                        | Р | Reference Supply current 2 ATD blocks on                                                                        | I <sub>REF</sub>                         |                                         |      | 0.750                                   | mA           |

| 8                                                        | Ρ | Reference Supply current 1 ATD block on                                                                         | I <sub>REF</sub>                         |                                         |      | 0.375                                   | mA           |

| Table A-8 | ATD | Operating | Characteristics |

|-----------|-----|-----------|-----------------|

|-----------|-----|-----------|-----------------|

NOTES:

1. Full accuracy is not guaranteed when differential voltage is less than 4.50V

2. The minimum time assumes a final sample period of 2 ATD clocks cycles while the maximum time assumes a final sample period of 16 ATD clocks.

### A.2.2 Factors influencing accuracy

Three factors - source resistance, source capacitance and current injection - have an influence on the accuracy of the ATD.

#### A.2.2.1 Source Resistance:

Due to the input pin leakage current as specified in **Table A-6** in conjunction with the source resistance there will be a voltage drop from the signal source to the ATD input. The maximum source resistance  $R_S$

| Condit | Conditions are shown in <b>Table A-4</b> unless otherwise noted, $C_{LOAD} = 50 pF$ |                                                                          |                  |     |     |     |      |

|--------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------|-----|-----|-----|------|

| Num    | С                                                                                   | Rating                                                                   | Symbol           | Min | Тур | Max | Unit |

| 32     | D                                                                                   | NOACC hold time                                                          | t <sub>NOH</sub> | 2   |     |     | ns   |

| 33     | D                                                                                   | IPIPO[1:0] delay time                                                    | t <sub>P0D</sub> | 2   |     | 7   | ns   |

| 34     | D                                                                                   | IPIPO[1:0] valid time to E rise (PW <sub>EL</sub> -t <sub>P0D</sub> )    | t <sub>P0V</sub> | 11  |     |     | ns   |

| 35     | D                                                                                   | IPIPO[1:0] delay time <sup>1</sup> (PW <sub>EH</sub> -t <sub>P1V</sub> ) | t <sub>P1D</sub> | 2   |     | 25  | ns   |

| 36     | D                                                                                   | IPIPO[1:0] valid time to E fall                                          | t <sub>P1V</sub> | 11  |     |     | ns   |

#### Table A-20 Expanded Bus Timing Characteristics

NOTES:

1. Affected by clock stretch: add N x  $t_{cyc}$  where N=0,1,2 or 3, depending on the number of clock stretches.

# **User Guide End Sheet**