Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                      |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | HCS12                                                       |

| Core Size                  | 16-Bit                                                      |

| Speed                      | 25MHz                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SPI                          |

| Peripherals                | PWM, WDT                                                    |

| Number of I/O              | 59                                                          |

| Program Memory Size        | 64KB (64K x 8)                                              |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | 1K x 8                                                      |

| RAM Size                   | 4K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 5.25V                                               |

| Data Converters            | A/D 8x10b                                                   |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                          |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 80-QFP                                                      |

| Supplier Device Package    | 80-QFP (14x14)                                              |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s12dj64mfue |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Appendix B Package Information

| B.1 | General              | 123 |

|-----|----------------------|-----|

| B.2 | 112-pin LQFP package | 124 |

| B.3 | 80-pin QFP package   | 125 |

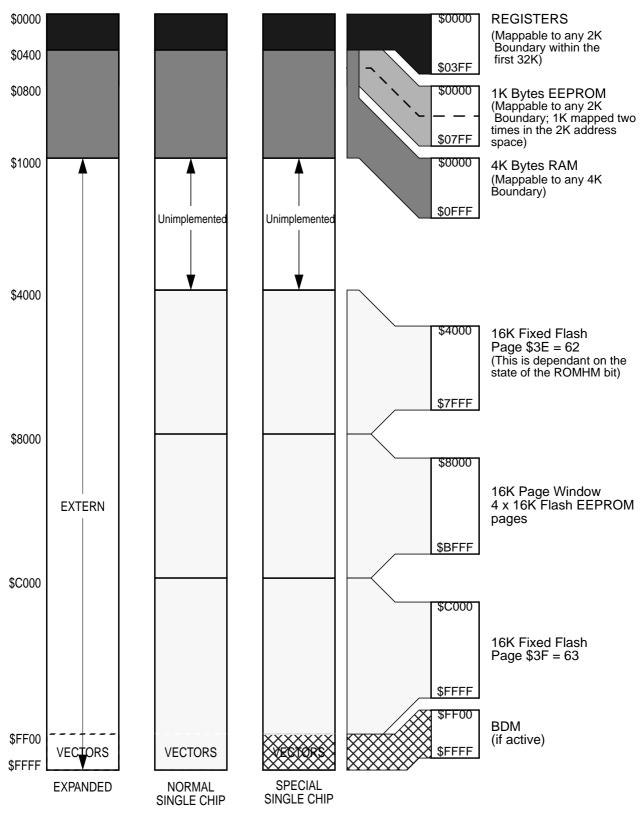

\$0100 - \$010F

Address \$010A

\$010B

\$010C -

\$010F

### Flash Control Register (fts64k)

| Name     | [               | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|-----------------|--------|-------|-------|-------|-------|-------|-------|-------|

| FDATAHI  | Read:<br>Write: | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

| FDATALO  | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| Reserved | Read:           | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| Reserveu | Write:          |        |       |       |       |       |       |       |       |

### \$0110 - \$011B

### **EEPROM Control Register (eets1k)**

|                  |                    | -                        |                 |         |         |         |         |         |        |                |

|------------------|--------------------|--------------------------|-----------------|---------|---------|---------|---------|---------|--------|----------------|

| Address          | Name               |                          | Bit 7           | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0          |

| \$0110           | ECLKDIV            | Read:                    | EDIVLD          | PRDIV8  | EDIV5   | EDIV4   | EDIV3   | EDIV2   | EDIV1  | EDIV0          |

| φσττο            | LOLINDIV           | Write:                   |                 |         | _       |         | _       |         |        | 20110          |

| \$0111           | Reserved           | Read:                    | 0               | 0       | 0       | 0       | 0       | 0       | 0      | 0              |

| φυττι            | iteseiveu          | Write:                   |                 |         |         |         |         |         |        |                |

| \$0112           | Reserved           | Read:                    | 0               | 0       | 0       | 0       | 0       | 0       | 0      | 0              |

| φυτιζ            | Reserveu           | Write:                   |                 |         |         |         |         |         |        |                |

| \$0113           | ECNFG              | Read:                    | CBEIE           | CCIE    | 0       | 0       | 0       | 0       | 0      | 0              |

| φυτισ            | LONIG              | Write:                   | ODLIL           | COL     |         |         |         |         |        |                |

| ¢0114            | EPROT              | Read:                    | EPOPEN          | NV6     | NV5     | NV4     | EPDIS   | EP2     | EP1    | EP0            |

| \$0114           | EPROI              | Write:                   | EPOPEN          |         |         |         | EPDIS   | EP2     | EPI    | EPU            |

| \$0115           | ESTAT              | Read:                    | CBEIF           | CCIF    | PVIOL   | ACCERR  | 0       | BLANK   | 0      | 0              |

| <b>J</b> 0115    | ESTAI              | Write:                   | CDEIF           |         | FVIOL   | ACCERR  |         | DLAINN  |        |                |

| \$0116           | ECMD               | Read:                    | 0               | CMDB6   | CMDB5   | 0       | 0       | CMDB2   | 0      | CMDB0          |

| φυτιο            | ECIVID             | Write:                   |                 | CIVIDBO | CIVIDBS |         |         | CIVIDBZ |        | CIVIDBO        |

| \$0117           | Reserved for       | Read:                    | 0               | 0       | 0       | 0       | 0       | 0       | 0      | 0              |

| φυτιγ            | Factory Test       | Write:                   |                 |         |         |         |         |         |        |                |

| <b>©0110</b>     |                    | Read:                    | 0               | 0       | 0       | 0       | 0       | 0       | 0      | D:4 0          |

| \$0118           | EADDRHI            | Write:                   |                 |         |         |         |         |         |        | Bit 8          |

|                  |                    | wine.                    |                 |         |         |         |         |         |        |                |

| <b>©0110</b>     |                    | Read:                    | D:4 7           | 0       |         | 4       | 2       | 0       | 4      | D:4 0          |

| \$0119           | EADDRLO            |                          | Bit 7           | 6       | 5       | 4       | 3       | 2       | 1      | Bit 0          |

|                  |                    | Read:                    |                 | -       |         |         |         |         |        |                |

| \$0119<br>\$011A | EADDRLO<br>EDATAHI | Read:<br>Write:          | Bit 7<br>Bit 15 | 6<br>14 | 5<br>13 | 4<br>12 | 3<br>11 | 2<br>10 | 1<br>9 | Bit 0<br>Bit 8 |

|                  |                    | Read:<br>Write:<br>Read: |                 | -       |         |         |         |         |        |                |

#### \$011C - \$011F

### **Reserved for RAM Control Register**

| Address  | Name     |        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|----------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$011C - | Reserved | Read:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$011F   | Reserveu | Write: |       |       |       |       |       |       |       |       |

#### \$0120 - \$013F

## ATD1 (Analog to Digital Converter 10 Bit 8 Channel)

| Address | Name      | [               | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3  | Bit 2 | Bit 1 | Bit 0 |

|---------|-----------|-----------------|-------|-------|-------|---------|--------|-------|-------|-------|

| \$0120  | ATD1CTL0  | Read:           | 0     | 0     | 0     | 0       | 0      | 0     | 0     | 0     |

|         |           | Write:<br>Read: | 0     | 0     | 0     | 0       | 0      | 0     | 0     | 0     |

| \$0121  | ATD1CTL1  | Write:          |       |       |       |         | •      | •     |       |       |

| \$0122  | ATD1CTL2  | Read:<br>Write: | ADPU  | AFFC  | AWAI  | ETRIGLE | ETRIGP | ETRIG | ASCIE | ASCIF |

| \$0123  | ATD1CTL3  | Read:<br>Write: | 0     | S8C   | S4C   | S2C     | S1C    | FIFO  | FRZ1  | FRZ0  |

| \$0124  | ATD1CTL4  | Read:<br>Write: | SRES8 | SMP1  | SMP0  | PRS4    | PRS3   | PRS2  | PRS1  | PRS0  |

| \$0125  | ATD1CTL5  | Read:<br>Write: | DJM   | DSGN  | SCAN  | MULT    | 0      | СС    | СВ    | CA    |

| \$0126  | ATD1STAT0 | Read:<br>Write: | SCF   | 0     | ETORF | FIFOR   | 0      | CC2   | CC1   | CC0   |

| \$0127  | Reserved  | Read:<br>Write: | 0     | 0     | 0     | 0       | 0      | 0     | 0     | 0     |

| \$0128  | ATD1TEST0 | Read:<br>Write: | 0     | 0     | 0     | 0       | 0      | 0     | 0     | 0     |

| \$0129  | ATD1TEST1 | Read:<br>Write: | 0     | 0     | 0     | 0       | 0      | 0     | 0     | SC    |

| \$012A  | Reserved  | Read:<br>Write: | 0     | 0     | 0     | 0       | 0      | 0     | 0     | 0     |

| \$012B  | ATD1STAT1 | Read:<br>Write: | CCF7  | CCF6  | CCF5  | CCF4    | CCF3   | CCF2  | CCF1  | CCF0  |

| \$012C  | Reserved  | Read:<br>Write: | 0     | 0     | 0     | 0       | 0      | 0     | 0     | 0     |

| \$012D  | ATD1DIEN  | Read:<br>Write: | Bit 7 | 6     | 5     | 4       | 3      | 2     | 1     | Bit 0 |

| \$012E  | Reserved  | Read:<br>Write: | 0     | 0     | 0     | 0       | 0      | 0     | 0     | 0     |

| \$012F  | PORTAD1   | Read:<br>Write: | Bit7  | 6     | 5     | 4       | 3      | 2     | 1     | BIT 0 |

| \$0130  | ATD1DR0H  | Read:<br>Write: | Bit15 | 14    | 13    | 12      | 11     | 10    | 9     | Bit8  |

| \$0131  | ATD1DR0L  | Read:<br>Write: | Bit7  | Bit6  | 0     | 0       | 0      | 0     | 0     | 0     |

| \$0132  | ATD1DR1H  | Read:<br>Write: | Bit15 | 14    | 13    | 12      | 11     | 10    | 9     | Bit8  |

| \$0133  | ATD1DR1L  | Read:<br>Write: | Bit7  | Bit6  | 0     | 0       | 0      | 0     | 0     | 0     |

| \$0134  | ATD1DR2H  | Read:<br>Write: | Bit15 | 14    | 13    | 12      | 11     | 10    | 9     | Bit8  |

| \$0135  | ATD1DR2L  | Read:<br>Write: | Bit7  | Bit6  | 0     | 0       | 0      | 0     | 0     | 0     |

| \$0136  | ATD1DR3H  | Read:<br>Write: | Bit15 | 14    | 13    | 12      | 11     | 10    | 9     | Bit8  |

| \$0137  | ATD1DR3L  | Read:<br>Write: | Bit7  | Bit6  | 0     | 0       | 0      | 0     | 0     | 0     |

| \$0138  | ATD1DR4H  | Read:<br>Write: | Bit15 | 14    | 13    | 12      | 11     | 10    | 9     | Bit8  |

#### \$0120 - \$013F

### ATD1 (Analog to Digital Converter 10 Bit 8 Channel)

| Address           | Name     | [      | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------------|----------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$0139            | ATD1DR4L | Read:  | Bit7  | Bit6  | 0     | 0     | 0     | 0     | 0     | 0     |

| φ0139             | AIDIDR4L | Write: |       |       |       |       |       |       |       |       |

| \$013A            | ATD1DR5H | Read:  | Bit15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit8  |

| ψυισ <del>Α</del> | AIDIDIGI | Write: |       |       |       |       |       |       |       |       |

| \$013B            | ATD1DR5L | Read:  | Bit7  | Bit6  | 0     | 0     | 0     | 0     | 0     | 0     |

| φ013D             | AIDIDKSL | Write: |       |       |       |       |       |       |       |       |

| \$013C            | ATD1DR6H | Read:  | Bit15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit8  |

| ψ013C             | AIDIDION | Write: |       |       |       |       |       |       |       |       |

| \$013D            | ATD1DR6L | Read:  | Bit7  | Bit6  | 0     | 0     | 0     | 0     | 0     | 0     |

| ψ013D             | AIDIDROL | Write: |       |       |       |       |       |       |       |       |

| \$013E            | ATD1DR7H | Read:  | Bit15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit8  |

| ψ013L             | AIDIDINI | Write: |       |       |       |       |       |       |       |       |

| \$013F            | ATD1DR7L | Read:  | Bit7  | Bit6  | 0     | 0     | 0     | 0     | 0     | 0     |

| φυτογ             | AIDIDRIL | Write: |       |       |       |       |       |       |       |       |

#### \$0140 - \$017F

### **CAN0 (Freescale Scalable CAN - FSCAN)**

| Address | Name            |                 | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  |

|---------|-----------------|-----------------|--------|--------|---------|---------|---------|---------|--------|--------|

| \$0140  | CAN0CTL0        | Read:<br>Write: | RXFRM  | RXACT  | CSWAI   | SYNCH   | TIME    | WUPE    | SLPRQ  | INITRQ |

| \$0141  | CAN0CTL1        | Read:<br>Write: | CANE   | CLKSRC | LOOPB   | LISTEN  | 0       | WUPM    | SLPAK  | INITAK |

| \$0142  | CAN0BTR0        | Read:<br>Write: | SJW1   | SJW0   | BRP5    | BRP4    | BRP3    | BRP2    | BRP1   | BRP0   |

| \$0143  | CAN0BTR1        | Read:<br>Write: | SAMP   | TSEG22 | TSEG21  | TSEG20  | TSEG13  | TSEG12  | TSEG11 | TSEG10 |

| \$0144  | CANORFLG        | Read:<br>Write: | WUPIF  | CSCIF  | RSTAT1  | RSTAT0  | TSTAT1  | TSTAT0  | OVRIF  | RXF    |

| \$0145  | <b>CAN0RIER</b> | Read:<br>Write: | WUPIE  | CSCIE  | RSTATE1 | RSTATE0 | TSTATE1 | TSTATE0 | OVRIE  | RXFIE  |

| \$0146  | CAN0TFLG        | Read:<br>Write: | 0      | 0      | 0       | 0       | 0       | TXE2    | TXE1   | TXE0   |

| \$0147  | <b>CAN0TIER</b> | Read:<br>Write: | 0      | 0      | 0       | 0       | 0       | TXEIE2  | TXEIE1 | TXEIE0 |

| \$0148  | CAN0TARQ        | Read:<br>Write: | 0      | 0      | 0       | 0       | 0       | ABTRQ2  | ABTRQ1 | ABTRQ0 |

| \$0149  | CAN0TAAK        | Read:<br>Write: | 0      | 0      | 0       | 0       | 0       | ABTAK2  | ABTAK1 | ABTAK0 |

| \$014A  | CAN0TBSEL       | Read:<br>Write: | 0      | 0      | 0       | 0       | 0       | TX2     | TX1    | ТХ0    |

| \$014B  | CANOIDAC        | Read:<br>Write: | 0      | 0      | IDAM1   | IDAM0   | 0       | IDHIT2  | IDHIT1 | IDHIT0 |

| \$014C  | Reserved        | Read:<br>Write: | 0      | 0      | 0       | 0       | 0       | 0       | 0      | 0      |

| \$014D  | Reserved        | Read:<br>Write: | 0      | 0      | 0       | 0       | 0       | 0       | 0      | 0      |

| \$014E  | CANORXERR       | Read:<br>Write: | RXERR7 | RXERR6 | RXERR5  | RXERR4  | RXERR3  | RXERR2  | RXERR1 | RXERR0 |

### \$0240 - \$027F

## PIM (Port Integration Module)

| Address                                                            | Name                                                        |                                                                                                                                                                                                               | Bit 7                                                               | Bit 6                                                      | Bit 5                                                               | Bit 4                                                               | Bit 3                                                               | Bit 2                                                               | Bit 1                                                               | Bit 0                                                               |

|--------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|

| \$024A                                                             | DDRS                                                        | Read:<br>Write:                                                                                                                                                                                               | DDRS7                                                               | DDRS7                                                      | DDRS5                                                               | DDRS4                                                               | DDRS3                                                               | DDRS2                                                               | DDRS1                                                               | DDRS0                                                               |

| \$024B                                                             | RDRS                                                        | Read:                                                                                                                                                                                                         | RDRS7                                                               | RDRS6                                                      | RDRS5                                                               | RDRS4                                                               | RDRS3                                                               | RDRS2                                                               | RDRS1                                                               | RDRS0                                                               |

|                                                                    |                                                             | Write:<br>Read:                                                                                                                                                                                               |                                                                     |                                                            |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |

| \$024C                                                             | PERS                                                        | Write:                                                                                                                                                                                                        | PERS7                                                               | PERS6                                                      | PERS5                                                               | PERS4                                                               | PERS3                                                               | PERS2                                                               | PERS1                                                               | PERS0                                                               |

| \$024D                                                             | PPSS                                                        | Read:<br>Write:                                                                                                                                                                                               | PPSS7                                                               | PPSS6                                                      | PPSS5                                                               | PPSS4                                                               | PPSS3                                                               | PPSS2                                                               | PPSS1                                                               | PPSS0                                                               |

| \$024E                                                             | WOMS                                                        | Read:<br>Write:                                                                                                                                                                                               | WOMS7                                                               | WOMS6                                                      | WOMS5                                                               | WOMS4                                                               | WOMS3                                                               | WOMS2                                                               | WOMS1                                                               | WOMS0                                                               |

| \$024F                                                             | Reserved                                                    | Read:<br>Write:                                                                                                                                                                                               | 0                                                                   | 0                                                          | 0                                                                   | 0                                                                   | 0                                                                   | 0                                                                   | 0                                                                   | 0                                                                   |

| \$0250                                                             | PTM                                                         | Read:                                                                                                                                                                                                         | PTM7                                                                | PTM6                                                       | PTM5                                                                | PTM4                                                                | PTM3                                                                | PTM2                                                                | PTM1                                                                | PTM0                                                                |

|                                                                    |                                                             | Write:<br>Read:                                                                                                                                                                                               | PTIM7                                                               | PTIM6                                                      | PTIM5                                                               | PTIM4                                                               | PTIM3                                                               | PTIM2                                                               | PTIM1                                                               | PTIMO                                                               |

| \$0251                                                             | PTIM                                                        | Write:                                                                                                                                                                                                        |                                                                     |                                                            |                                                                     |                                                                     |                                                                     | 1 11112                                                             |                                                                     |                                                                     |

| \$0252                                                             | DDRM                                                        | Read:<br>Write:                                                                                                                                                                                               | DDRM7                                                               | DDRM7                                                      | DDRM5                                                               | DDRM4                                                               | DDRM3                                                               | DDRM2                                                               | DDRM1                                                               | DDRM0                                                               |

| \$0253                                                             | RDRM                                                        | Read:<br>Write:                                                                                                                                                                                               | RDRM7                                                               | RDRM6                                                      | RDRM5                                                               | RDRM4                                                               | RDRM3                                                               | RDRM2                                                               | RDRM1                                                               | RDRM0                                                               |

| \$0254                                                             | PERM                                                        | Read:<br>Write:                                                                                                                                                                                               | PERM7                                                               | PERM6                                                      | PERM5                                                               | PERM4                                                               | PERM3                                                               | PERM2                                                               | PERM1                                                               | PERM0                                                               |

| \$0255                                                             | PPSM                                                        | Read:<br>Write:                                                                                                                                                                                               | PPSM7                                                               | PPSM6                                                      | PPSM5                                                               | PPSM4                                                               | PPSM3                                                               | PPSM2                                                               | PPSM1                                                               | PPSM0                                                               |

| \$0256                                                             | WOMM                                                        | Read:<br>Write:                                                                                                                                                                                               | WOMM7                                                               | WOMM6                                                      | WOMM5                                                               | WOMM4                                                               | WOMM3                                                               | WOMM2                                                               | WOMM1                                                               | WOMM0                                                               |

| \$0257                                                             | MODRR                                                       | Read:<br>Write:                                                                                                                                                                                               | 0                                                                   | 0                                                          | 0                                                                   | MODRR4                                                              | 0                                                                   | 0                                                                   | MODRR1                                                              | MODRR0                                                              |

| \$0258                                                             |                                                             |                                                                                                                                                                                                               |                                                                     |                                                            |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |

|                                                                    | PTP                                                         | Read:<br>Write:                                                                                                                                                                                               | PTP7                                                                | PTP6                                                       | PTP5                                                                | PTP4                                                                | PTP3                                                                | PTP2                                                                | PTP1                                                                | PTP0                                                                |

| \$0259                                                             | PTP<br>PTIP                                                 | Write:<br>Read:                                                                                                                                                                                               | PTP7<br>PTIP7                                                       | PTP6<br>PTIP6                                              | PTP5<br>PTIP5                                                       | PTP4<br>PTIP4                                                       | PTP3<br>PTIP3                                                       | PTP2<br>PTIP2                                                       | PTP1<br>PTIP1                                                       | PTP0<br>PTIP0                                                       |

| \$0259                                                             | PTIP                                                        | Write:<br>Read:<br>Write:                                                                                                                                                                                     | PTIP7                                                               | PTIP6                                                      | PTIP5                                                               | PTIP4                                                               | PTIP3                                                               | PTIP2                                                               | PTIP1                                                               | PTIP0                                                               |

| \$0259<br>\$025A                                                   |                                                             | Write:<br>Read:<br>Write:<br>Read:<br>Write:                                                                                                                                                                  |                                                                     |                                                            |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |                                                                     |

|                                                                    | PTIP                                                        | Write:<br>Read:<br>Write:<br>Read:                                                                                                                                                                            | PTIP7                                                               | PTIP6                                                      | PTIP5                                                               | PTIP4                                                               | PTIP3                                                               | PTIP2                                                               | PTIP1                                                               | PTIP0                                                               |

| \$025A                                                             | PTIP<br>DDRP                                                | Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:                                                                                                                                                         | PTIP7<br>DDRP7                                                      | PTIP6<br>DDRP7                                             | PTIP5<br>DDRP5                                                      | PTIP4<br>DDRP4                                                      | PTIP3<br>DDRP3                                                      | PTIP2<br>DDRP2                                                      | PTIP1<br>DDRP1                                                      | PTIP0<br>DDRP0                                                      |

| \$025A<br>\$025B                                                   | PTIP<br>DDRP<br>RDRP                                        | Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:                                                                                                                                      | PTIP7<br>DDRP7<br>RDRP7                                             | PTIP6<br>DDRP7<br>RDRP6                                    | PTIP5<br>DDRP5<br>RDRP5                                             | PTIP4<br>DDRP4<br>RDRP4                                             | PTIP3<br>DDRP3<br>RDRP3                                             | PTIP2<br>DDRP2<br>RDRP2                                             | PTIP1<br>DDRP1<br>RDRP1                                             | PTIP0<br>DDRP0<br>RDRP0                                             |

| \$025A<br>\$025B<br>\$025C                                         | PTIP<br>DDRP<br>RDRP<br>PERP                                | Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:                                                                             | PTIP7<br>DDRP7<br>RDRP7<br>PERP7                                    | PTIP6<br>DDRP7<br>RDRP6<br>PERP6                           | PTIP5<br>DDRP5<br>RDRP5<br>PERP5                                    | PTIP4<br>DDRP4<br>RDRP4<br>PERP4                                    | PTIP3<br>DDRP3<br>RDRP3<br>PERP3                                    | PTIP2<br>DDRP2<br>RDRP2<br>PERP2                                    | PTIP1<br>DDRP1<br>RDRP1<br>PERP1                                    | PTIP0<br>DDRP0<br>RDRP0<br>PERP0                                    |

| \$025A<br>\$025B<br>\$025C<br>\$025D                               | PTIP<br>DDRP<br>RDRP<br>PERP<br>PPSP                        | Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:                                                                             | PTIP7<br>DDRP7<br>RDRP7<br>PERP7<br>PPSP7                           | PTIP6<br>DDRP7<br>RDRP6<br>PERP6<br>PPSP6                  | PTIP5<br>DDRP5<br>RDRP5<br>PERP5<br>PPSP5                           | PTIP4<br>DDRP4<br>RDRP4<br>PERP4<br>PPSP4                           | PTIP3<br>DDRP3<br>RDRP3<br>PERP3<br>PPSP3                           | PTIP2<br>DDRP2<br>RDRP2<br>PERP2<br>PPSP2                           | PTIP1<br>DDRP1<br>RDRP1<br>PERP1<br>PPSP1                           | PTIP0<br>DDRP0<br>RDRP0<br>PERP0<br>PPSS0                           |

| \$025A<br>\$025B<br>\$025C<br>\$025D<br>\$025E                     | PTIP<br>DDRP<br>RDRP<br>PERP<br>PPSP<br>PIEP                | Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Mrite:<br>Read:                                       | PTIP7<br>DDRP7<br>RDRP7<br>PERP7<br>PPSP7<br>PIEP7                  | PTIP6<br>DDRP7<br>RDRP6<br>PERP6<br>PPSP6<br>PIEP6         | PTIP5<br>DDRP5<br>RDRP5<br>PERP5<br>PPSP5<br>PIEP5                  | PTIP4<br>DDRP4<br>RDRP4<br>PERP4<br>PPSP4<br>PIEP4                  | PTIP3<br>DDRP3<br>RDRP3<br>PERP3<br>PPSP3<br>PIEP3                  | PTIP2<br>DDRP2<br>RDRP2<br>PERP2<br>PPSP2<br>PIEP2                  | PTIP1<br>DDRP1<br>RDRP1<br>PERP1<br>PPSP1<br>PIEP1                  | PTIP0<br>DDRP0<br>RDRP0<br>PERP0<br>PPSS0<br>PIEP0                  |

| \$025A<br>\$025B<br>\$025C<br>\$025D<br>\$025E<br>\$025F<br>\$0260 | PTIP<br>DDRP<br>RDRP<br>PERP<br>PPSP<br>PIEP<br>PIFP<br>PTH | Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:                    | PTIP7<br>DDRP7<br>RDRP7<br>PERP7<br>PPSP7<br>PIEP7<br>PIFP7         | PTIP6<br>DDRP7<br>RDRP6<br>PERP6<br>PIEP6<br>PIFP6         | PTIP5<br>DDRP5<br>RDRP5<br>PERP5<br>PPSP5<br>PIEP5<br>PIFP5         | PTIP4<br>DDRP4<br>RDRP4<br>PERP4<br>PPSP4<br>PIEP4<br>PIFP4         | PTIP3<br>DDRP3<br>RDRP3<br>PERP3<br>PPSP3<br>PIEP3<br>PIFP3         | PTIP2<br>DDRP2<br>RDRP2<br>PERP2<br>PPSP2<br>PIEP2<br>PIFP2         | PTIP1<br>DDRP1<br>RDRP1<br>PERP1<br>PPSP1<br>PIEP1<br>PIFP1         | PTIP0<br>DDRP0<br>RDRP0<br>PERP0<br>PPSS0<br>PIEP0<br>PIFP0         |

| \$025A<br>\$025B<br>\$025C<br>\$025D<br>\$025E<br>\$025F           | PTIP<br>DDRP<br>RDRP<br>PERP<br>PPSP<br>PIEP<br>PIFP        | Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read:<br>Write:<br>Read: | PTIP7<br>DDRP7<br>RDRP7<br>PERP7<br>PPSP7<br>PIEP7<br>PIFP7<br>PTH7 | PTIP6<br>DDRP7<br>RDRP6<br>PERP6<br>PIEP6<br>PIFP6<br>PTH6 | PTIP5<br>DDRP5<br>RDRP5<br>PERP5<br>PPSP5<br>PIEP5<br>PIFP5<br>PTH5 | PTIP4<br>DDRP4<br>RDRP4<br>PERP4<br>PPSP4<br>PIEP4<br>PIFP4<br>PTH4 | PTIP3<br>DDRP3<br>RDRP3<br>PERP3<br>PPSP3<br>PIEP3<br>PIFP3<br>PTH3 | PTIP2<br>DDRP2<br>RDRP2<br>PERP2<br>PPSP2<br>PIEP2<br>PIFP2<br>PTH2 | PTIP1<br>DDRP1<br>RDRP1<br>PERP1<br>PPSP1<br>PIEP1<br>PIFP1<br>PTH1 | PTIP0<br>DDRP0<br>RDRP0<br>PERP0<br>PPSS0<br>PIEP0<br>PIFP0<br>PTH0 |

### \$0240 - \$027F

### **PIM (Port Integration Module)**

| Address             | Name       |                 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------------------|------------|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$0263              | RDRH       | Read:<br>Write: | RDRH7 | RDRH6 | RDRH5 | RDRH4 | RDRH3 | RDRH2 | RDRH1 | RDRH0 |

| \$0264              | PERH       | Read:<br>Write: | PERH7 | PERH6 | PERH5 | PERH4 | PERH3 | PERH2 | PERH1 | PERH0 |

| \$0265              | PPSH       | Read:<br>Write: | PPSH7 | PPSH6 | PPSH5 | PPSH4 | PPSH3 | PPSH2 | PPSH1 | PPSH0 |

| \$0266              | PIEH       | Read:<br>Write: | PIEH7 | PIEH6 | PIEH5 | PIEH4 | PIEH3 | PIEH2 | PIEH1 | PIEH0 |

| \$0267              | PIFH       | Read:<br>Write: | PIFH7 | PIFH6 | PIFH5 | PIFH4 | PIFH3 | PIFH2 | PIFH1 | PIFH0 |

| \$0268              | PTJ        | Read:<br>Write: | PTJ7  | PTJ6  | 0     | 0     | 0     | 0     | PTJ1  | PTJ0  |

| \$0269              | PTIJ       | Read:           | PTIJ7 | PTIJ6 | 0     | 0     | 0     | 0     | PTIJ1 | PTIJ0 |

| <i><b>Q0200</b></i> | 1 110      | Write:          |       |       |       |       |       |       |       |       |

| \$026A              | DDRJ       | Read:<br>Write: | DDRJ7 | DDRJ7 | 0     | 0     | 0     | 0     | DDRJ1 | DDRJ0 |

| \$026B              | RDRJ       | Read:<br>Write: | RDRJ7 | RDRJ6 | 0     | 0     | 0     | 0     | RDRJ1 | RDRJ0 |

| \$026C              | PERJ       | Read:<br>Write: | PERJ7 | PERJ6 | 0     | 0     | 0     | 0     | PERJ1 | PERJ0 |

| \$026D              | PPSJ       | Read:<br>Write: | PPSJ7 | PPSJ6 | 0     | 0     | 0     | 0     | PPSJ1 | PPSJ0 |

| \$026E              | PIEJ       | Read:           | PIEJ7 | PIEJ6 | 0     | 0     | 0     | 0     | PIEJ1 | PIEJ0 |

| ΨULUL               | 1120       | Write:          |       | 11200 |       |       |       |       |       | 11200 |

| \$026F              | PIFJ       | Read:<br>Write: | PIFJ7 | PIFJ6 | 0     | 0     | 0     | 0     | PIFJ1 | PIFJ0 |

| \$0270 -            | Reserved   | Read:           | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$027F              | 176961 460 | Write:          |       |       |       |       |       |       |       |       |

### \$0280 - \$03FF

### Reserved

| Address  | Name      |        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|-----------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$0280 - | Percented | Read:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$03FF   | Reserved  | Write: |       |       |       |       |       |       |       |       |

## **1.6 Part ID Assignments**

The part ID is located in two 8-bit registers PARTIDH and PARTIDL (addresses \$001A and \$001B after reset). The read-only value is a unique part ID for each revision of the chip. **Table 1-4** shows the assigned part ID number.

| Device     | Mask Set Number | Part ID <sup>1</sup> |

|------------|-----------------|----------------------|

| MC9S12DJ64 | 0L86D           | \$0200               |

| MC9S12DJ64 | 1L86D           | \$0201               |

| MC9S12DJ64 | 2L86D           | \$0201 <sup>2</sup>  |

| MC9S12DJ64 | 3L86D           | \$0203               |

| MC9S12DJ64 | 4L86D           | \$0204               |

| MC9S12DJ64 | 0M89C           | \$0204               |

### **Table 1-4 Assigned Part ID Numbers**

NOTES:

1. The coding is as follows:

Bit 15-12: Major family identifier

Bit 11-8: Minor family identifier

Bit 7-4: Major mask set revision number including FAB transfers

Bit 3-0: Minor - non full - mask set revision

2. 1L86D is identical to 2L86D except improved ESD performance on 2L86D

The device memory sizes are located in two 8-bit registers MEMSIZ0 and MEMSIZ1 (addresses \$001C and \$001D after reset). **Table 1-5** shows the read-only values of these registers. Refer to HCS12 Module Mapping Control (MMC) Block Guide for further details.

#### Table 1-5 Memory size registers

| Register name | Value |

|---------------|-------|

| MEMSIZ0       | \$11  |

| MEMSIZ1       | \$80  |

### 2.3.55 PS2 / RXD1 — Port S I/O Pin 2

PS2 is a general purpose input or output pin. It can be configured as the receive pin RXD of Serial Communication Interface 1 (SCI1).

### 2.3.56 PS1 / TXD0 - Port S I/O Pin 1

PS1 is a general purpose input or output pin. It can be configured as the transmit pin TXD of Serial Communication Interface 0 (SCI0).

### 2.3.57 PS0 / RXD0 - Port S I/O Pin 0

PS0 is a general purpose input or output pin. It can be configured as the receive pin RXD of Serial Communication Interface 0 (SCI0).

### 2.3.58 PT[7:0] / IOC[7:0] — Port T I/O Pins [7:0]

PT7-PT0 are general purpose input or output pins. They can be configured as input capture or output compare pins IOC7-IOC0 of the Enhanced Capture Timer (ECT).

## 2.4 Power Supply Pins

MC9S12DJ64 power and ground pins are described below.

**NOTE:** All VSS pins must be connected together in the application.

| Mnemonic  | Pin Number  | Nominal | Description                                                                                                                               |  |  |  |

|-----------|-------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| winemonic | 112-pin QFP | Voltage | Description                                                                                                                               |  |  |  |

| VDD1, 2   | 13, 65      | 2.5V    | Internal power and ground generated by internal regulator                                                                                 |  |  |  |

| VSS1, 2   | 14, 66      | 0V      | internal power and ground generated by internal regulator                                                                                 |  |  |  |

| VDDR      | 41          | 5.0V    | External power and ground, supply to pin drivers and internal                                                                             |  |  |  |

| VSSR      | 40          | 0V      | voltage regulator.                                                                                                                        |  |  |  |

| VDDX      | 107         | 5.0V    | External power and ground, supply to pin drivers.                                                                                         |  |  |  |

| VSSX      | 106         | 0V      | External power and ground, supply to pirrunvers.                                                                                          |  |  |  |

| VDDA      | 83          | 5.0V    | Operating voltage and ground for the analog-to-digital                                                                                    |  |  |  |

| VSSA      | 86          | 0V      | converters and the reference for the internal voltage regulator,<br>allows the supply voltage to the A/D to be bypassed<br>independently. |  |  |  |

| VRL       | 85          | 0V      | Reference voltages for the analog-to-digital converter.                                                                                   |  |  |  |

| VRH       | 84          | 5.0V    |                                                                                                                                           |  |  |  |

Table 2-2

MC9S12DJ64 Power and Ground Connection Summary

#### Table 4-2 Clock Selection Based on PE7

| PE7 = XCLKS | Description                               |

|-------------|-------------------------------------------|

| 0           | Pierce Oscillator/external clock selected |

#### Table 4-3 Voltage Regulator VREGEN

|                                      | VREGEN | Description                                                                                  |  |  |  |

|--------------------------------------|--------|----------------------------------------------------------------------------------------------|--|--|--|

| 1 Internal Voltage Regulator enabled |        |                                                                                              |  |  |  |

|                                      | 0      | Internal Voltage Regulator disabled, VDD1,2 and VDDPLL must be supplied externally with 2.5V |  |  |  |

## 4.3 Security

The device will make available a security feature preventing the unauthorized read and write of the memory contents. This feature allows:

- Protection of the contents of FLASH,

- Protection of the contents of EEPROM,

- Operation in single-chip mode,

- Operation from external memory with internal FLASH and EEPROM disabled.

The user must be reminded that part of the security must lie with the user's code. An extreme example would be user's code that dumps the contents of the internal program. This code would defeat the purpose of security. At the same time the user may also wish to put a back door in the user's program. An example of this is the user downloads a key through the SCI which allows access to a programming routine that updates parameters stored in EEPROM.

### 4.3.1 Securing the Microcontroller

Once the user has programmed the FLASH and EEPROM (if desired), the part can be secured by programming the security bits located in the FLASH module. These non-volatile bits will keep the part secured through resetting the part and through powering down the part.

The security byte resides in a portion of the Flash array.

Check the Flash Block User Guide for more details on the security configuration.

### 4.3.2 Operation of the Secured Microcontroller

### 4.3.2.1 Normal Single Chip Mode

This will be the most common usage of the secured part. Everything will appear the same as if the part was not secured with the exception of BDM operation. The BDM operation will be blocked.

# **Appendix A Electrical Characteristics**

# A.1 General

This introduction is intended to give an overview on several common topics like power supply, current injection etc.

## A.1.1 Parameter Classification

The electrical parameters shown in this supplement are guaranteed by various methods. To give the customer a better understanding the following classification is used and the parameters are tagged accordingly in the tables where appropriate.

P:

Those parameters are guaranteed during production testing on each individual device.

C:

Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.

T:

Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category.

D:

Those parameters are derived mainly from simulations.

## A.1.2 Power Supply

The MC9S12DJ64 and MC9S12D32 utilize several pins to supply power to the I/O ports, A/D converter, oscillator, PLL and internal logic.

The VDDA, VSSA pair supplies the A/D converter and the resistor ladder of the internal voltage regulator.

The VDDX, VSSX, VDDR and VSSR pairs supply the I/O pins, VDDR supplies also the internal voltage regulator.

VDD1, VSS1, VDD2 and VSS2 are the supply pins for the digital logic, VDDPLL, VSSPLL supply the oscillator and the PLL.

VSS1 and VSS2 are internally connected by metal.

**NOTE:** This classification is shown in the column labeled "C" in the parameter tables where appropriate.

| Num | С | Rating                                                                                                                  | Symbol                               | Min                    | Тур | Max                    | Unit |

|-----|---|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------|-----|------------------------|------|

| 1   | Р | Input High Voltage                                                                                                      | V <sub>IH</sub>                      | 0.65*V <sub>DD5</sub>  | -   | V <sub>DD5</sub> + 0.3 | V    |

| 2   | Р | Input Low Voltage                                                                                                       | V <sub>IL</sub>                      | V <sub>SS5</sub> - 0.3 | -   | 0.35*V <sub>DD5</sub>  | V    |

| 3   | С | Input Hysteresis                                                                                                        | V <sub>HYS</sub>                     |                        | 250 |                        | mV   |

| 4   | Р | Input Leakage Current (pins in high impedance input mode)<br>$V_{in} = V_{DD5} \text{ or } V_{SS5}$                     | l <sub>in</sub>                      | -1                     | -   | 1                      | μA   |

| 5   | Р | Output High Voltage (pins in output mode)<br>Partial Drive I <sub>OH</sub> = −2mA<br>Full Drive I <sub>OH</sub> = −10mA | V <sub>OH</sub>                      | V <sub>DD5</sub> – 0.8 | -   | -                      | V    |

| 6   | Р | Output Low Voltage (pins in output mode)<br>Partial Drive I <sub>OL</sub> = +2mA<br>Full Drive I <sub>OL</sub> = +10mA  | V <sub>OL</sub>                      | -                      | -   | 0.8                    | V    |

| 7   | Р | Internal Pull Up Device Current,<br>tested at V <sub>IL</sub> Max.                                                      | I <sub>PUL</sub>                     | -                      | -   | -130                   | μΑ   |

| 8   | с | Internal Pull Up Device Current,<br>tested at V <sub>IH</sub> Min.                                                      | I <sub>PUH</sub>                     | -10                    | -   | -                      | μΑ   |

| 9   | Р | Internal Pull Down Device Current,<br>tested at V <sub>IH</sub> Min.                                                    | I <sub>PDH</sub>                     | -                      | -   | 130                    | μA   |

| 10  | с | Internal Pull Down Device Current,<br>tested at V <sub>IL</sub> Max.                                                    | I <sub>PDL</sub>                     | 10                     | -   | -                      | μA   |

| 11  | D | Input Capacitance                                                                                                       | C <sub>in</sub>                      |                        | 6   | -                      | pF   |

| 12  | т | Injection current <sup>1</sup><br>Single Pin limit<br>Total Device Limit. Sum of all injected currents                  | I <sub>ICS</sub><br>I <sub>ICP</sub> | -2.5<br>-25            | -   | 2.5<br>25              | mA   |

| 13  | Р | Port H, J, P Interrupt Input Pulse filtered <sup>2</sup>                                                                | t <sub>pign</sub>                    |                        |     | 3                      | μs   |

| 14  | Ρ | Port H, J, P Interrupt Input Pulse passed <sup>2</sup>                                                                  | t <sub>pval</sub>                    | 10                     |     |                        | μs   |

#### Table A-6 5V I/O Characteristics

NOTES:

1. Refer to Section A.1.4 Current Injection, for more details

2. Parameter only applies in STOP or Pseudo STOP mode.

## A.1.10 Supply Currents

This section describes the current consumption characteristics of the device as well as the conditions for the measurements.

### A.1.10.1 Measurement Conditions

All measurements are without output loads. Unless otherwise noted the currents are measured in single chip mode, internal voltage regulator enabled and at 25MHz bus frequency using a 4MHz oscillator in Colpitts mode. Production testing is performed using a square wave signal at the EXTAL input.

### A.1.10.2 Additional Remarks

In expanded modes the currents flowing in the system are highly dependent on the load at the address, data and control signals as well as on the duty cycle of those signals. No generally applicable numbers can be given. A very good estimate is to take the single chip currents and add the currents due to the external loads.

| Condit | Conditions are shown in Table A-4 unless otherwise noted           |                                                                                                                                                                                          |                   |     |                                                              |                             |      |

|--------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----|--------------------------------------------------------------|-----------------------------|------|

| Num    | С                                                                  | Rating                                                                                                                                                                                   | Symbol            | Min | Тур                                                          | Max                         | Unit |

| 1      | Р                                                                  | Run supply currents<br>Single Chip, Internal regulator enabled                                                                                                                           | I <sub>DD5</sub>  |     |                                                              | 50                          | mA   |

| 2      | P<br>P                                                             | Wait Supply current<br>All modules enabled, PLL on<br>only RTI enabled <sup>1</sup>                                                                                                      | I <sub>DDW</sub>  |     |                                                              | 30<br>5                     | mA   |

| 3      | CPCCPCPCP                                                          | Pseudo Stop Current (RTI and COP disabled) <sup>1, 2</sup><br>-40°C<br>27°C<br>70°C<br>85°C<br>"C" Temp Option 100°C<br>105°C<br>"V" Temp Option 120°C<br>125°C<br>"M" Temp Option 140°C | I <sub>DDPS</sub> |     | 370<br>400<br>450<br>550<br>600<br>650<br>800<br>850<br>1200 | 500<br>1600<br>2100<br>5000 | μΑ   |

| 4      | с<br>с<br>с<br>с<br>с<br>с<br>с<br>с<br>с<br>с<br>с<br>с<br>с<br>с | Pseudo Stop Current (RTI and COP enabled) <sup>1, 2</sup><br>-40°C<br>27°C<br>70°C<br>85°C<br>105°C<br>125°C<br>140°C                                                                    | I <sub>DDPS</sub> |     | 570<br>600<br>650<br>750<br>850<br>1200<br>1500              |                             | μΑ   |

| 5      | C P C C P C P<br>C P C P                                           | Stop Current <sup>2</sup><br>-40°C<br>27°C<br>70°C<br>85°C<br>"C" Temp Option 100°C<br>105°C<br>"V" Temp Option 120°C<br>125°C<br>"M" Temp Option 140°C                                  | I <sub>DDS</sub>  |     | 12<br>25<br>100<br>130<br>160<br>200<br>350<br>400<br>600    | 100<br>1200<br>1700<br>5000 | μΑ   |

### **Table A-7 Supply Current Characteristics**

#### MC9S12DJ64 Device User Guide — V01.20

This is very important to notice with respect to timers, serial modules where a pre-scaler will eliminate the effect of the jitter to a large extent.

| Condit | ions | s are shown in Table A-4 unless otherwise noted            |                   |     |      |      |                |

|--------|------|------------------------------------------------------------|-------------------|-----|------|------|----------------|

| Num    | С    | Rating                                                     | Symbol            | Min | Тур  | Max  | Unit           |

| 1      | Р    | Self Clock Mode frequency                                  | f <sub>SCM</sub>  | 1   |      | 5.5  | MHz            |

| 2      | D    | VCO locking range                                          | f <sub>VCO</sub>  | 8   |      | 50   | MHz            |

| 3      | D    | Lock Detector transition from Acquisition to Tracking mode | $ \Delta_{trk} $  | 3   |      | 4    | % <sup>1</sup> |

| 4      | D    | Lock Detection                                             | $ \Delta_{Lock} $ | 0   |      | 1.5  | % <sup>1</sup> |

| 5      | D    | Un-Lock Detection                                          | Δ <sub>unl</sub>  | 0.5 |      | 2.5  | % <sup>1</sup> |

| 6      | D    | Lock Detector transition from Tracking to Acquisition mode | Δ <sub>unt</sub>  | 6   |      | 8    | % <sup>1</sup> |

| 7      | С    | PLLON Total Stabilization delay (Auto Mode) <sup>2</sup>   | t <sub>stab</sub> |     | 0.5  |      | ms             |

| 8      | D    | PLLON Acquisition mode stabilization delay <sup>2</sup>    | t <sub>acq</sub>  |     | 0.3  |      | ms             |

| 9      | D    | PLLON Tracking mode stabilization delay <sup>2</sup>       | t <sub>al</sub>   |     | 0.2  |      | ms             |

| 10     | D    | Fitting parameter VCO loop gain                            | K <sub>1</sub>    |     | -100 |      | MHz/V          |

| 11     | D    | Fitting parameter VCO loop frequency                       | f <sub>1</sub>    |     | 60   |      | MHz            |

| 12     | D    | Charge pump current acquisition mode                       | i <sub>ch</sub>   |     | 38.5 |      | μA             |

| 13     | D    | Charge pump current tracking mode                          | i <sub>ch</sub>   |     | 3.5  |      | μA             |

| 14     | С    | Jitter fit parameter 1 <sup>2</sup>                        | j <sub>1</sub>    |     |      | 1.1  | %              |

| 15     | С    | Jitter fit parameter 2 <sup>2</sup>                        | j <sub>2</sub>    |     |      | 0.13 | %              |

| Table A-16 | PLL | Characteristics |

|------------|-----|-----------------|

|------------|-----|-----------------|

NOTES:

1. % deviation from target frequency

2.  $f_{OSC} = 4MHz$ ,  $f_{BUS} = 25MHz$  equivalent  $f_{VCO} = 50MHz$ : REFDV = #\$03, SYNR = #\$018, Cs = 4.7nF, Cp = 470pF, Rs = 10K\Omega.

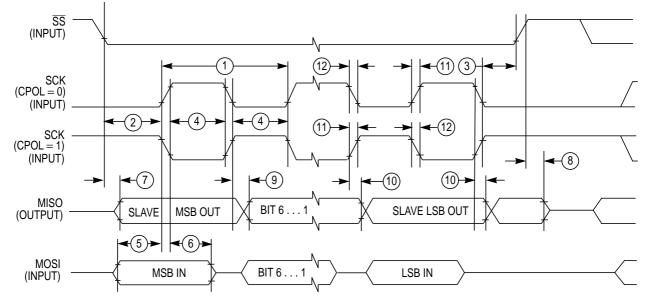

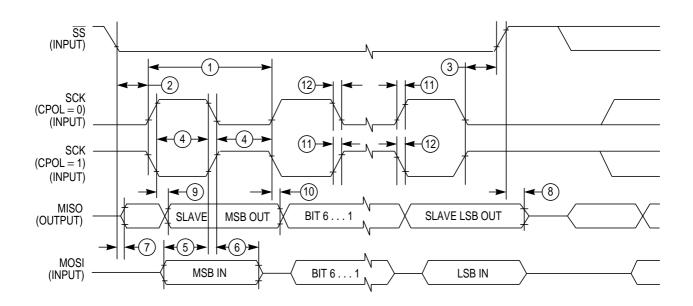

### A.7.2 Slave Mode

Figure A-7 and Figure A-8 illustrate the slave mode timing. Timing values are shown in Table A-19.

Figure A-7 SPI Slave Timing (CPHA = 0)

Figure A-8 SPI Slave Timing (CPHA =1)

# A.8 External Bus Timing

A timing diagram of the external multiplexed-bus is illustrated in **Figure A-9** with the actual timing values shown on table **Table A-20**. All major bus signals are included in the diagram. While both a data write and data read cycle are shown, only one or the other would occur on a particular bus cycle.

### A.8.1 General Muxed Bus Timing

The expanded bus timings are highly dependent on the load conditions. The timing parameters shown assume a balanced load across all outputs.

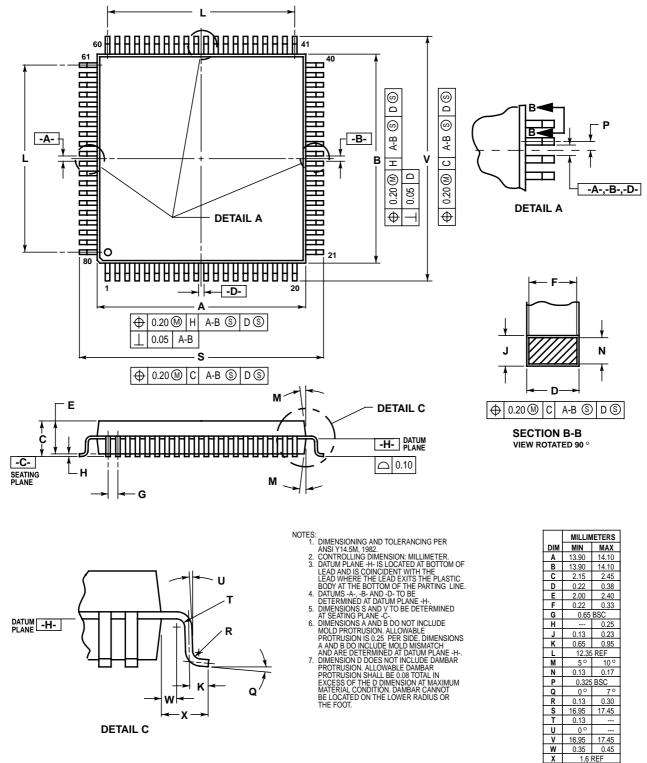

## B.3 80-pin QFP package

Figure B-2 80-pin QFP Mechanical Dimensions (case no. 841B)

## FINAL PAGE OF 128 PAGES