Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Not For New Designs                                                    |

| Core Processor             | HCS12                                                                  |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 25MHz                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SPI                                     |

| Peripherals                | PWM, WDT                                                               |

| Number of I/O              | 59                                                                     |

| Program Memory Size        | 64KB (64K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 1K x 8                                                                 |

| RAM Size                   | 4K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 5.25V                                                          |

| Data Converters            | A/D 16x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 80-QFP                                                                 |

| Supplier Device Package    | 80-QFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12d64f0vfue |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Version<br>Number | Revision<br>Date | Effective Date  | Author | Description of Changes                                                                                                                                                      |

|-------------------|------------------|-----------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V01.15            | 22 July<br>2003  | 22 July<br>2003 |        | Mentioned "S12 LRAE" bootloader in Flash section Section Document References: corrected S12 CPU document reference                                                          |

| V01.16            | 24 Feb.<br>2004  | 24 Feb.<br>2004 |        | Added 3L86D maskset with corresponding Part ID Table Oscillator Characteristics: Added more details for EXTAL pin                                                           |

| V01.17            | 21 May<br>2004   | 21 May<br>2004  |        | Added 4L86D maskset with corresponding Part ID Table "MC9S12DJ64 Memory Map out of Reset": corrected \$1000 - \$3fff memory in single chip modes to "unimplemented".        |

| V01.18            | 13 July<br>2004  | 13 July<br>2004 |        | Added MC9S12D32 and MC9S12A32                                                                                                                                               |

| V01.19            | 2 Sept.<br>2004  | 2 Sept.<br>2004 |        | Appendix, Table "Oscillator Characteristics": changed item 13 VIH,EXTAL min value from 0.7*VDDPLL to 0.75*VDDPLL item 14 VIL,EXTAL max value from 0.3*VDDPLL to 0.25*VDDPLL |

| V01.20            | 6 April<br>2005  | 6 April<br>2005 |        | Table "Assigned Part ID Numbers": added mask set number 0M89C Table "NVM Reliability Characteristics": added footnote concerning data retention                             |

#### MC9S12DJ64 Device User Guide — V01.20

| 2.3.21 | PH7 / KWH7 — Port H I/O Pin 7                  | 59 |

|--------|------------------------------------------------|----|

| 2.3.22 | PH6 / KWH6 — Port H I/O Pin 6                  | 60 |

| 2.3.23 | PH5 / KWH5 — Port H I/O Pin 5                  | 60 |

| 2.3.24 | PH4 / KWH4 — Port H I/O Pin 2                  | 60 |

| 2.3.25 | PH3 / KWH3 — Port H I/O Pin 3                  | 60 |

| 2.3.26 | PH2 / KWH2 — Port H I/O Pin 2                  | 60 |

| 2.3.27 | PH1 / KWH1 — Port H I/O Pin 1                  | 60 |

| 2.3.28 | PH0 / KWH0 — Port H I/O Pin 0                  | 60 |

| 2.3.29 | PJ7 / KWJ7 / SCL / TXCAN0 — PORT J I/O Pin 7   | 60 |

| 2.3.30 | PJ6 / KWJ6 / SDA / RXCAN0 — PORT J I/O Pin 6   | 61 |

| 2.3.31 | PJ[1:0] / KWJ[1:0] — Port J I/O Pins [1:0]     | 61 |

| 2.3.32 | PK7 / ECS / ROMCTL — Port K I/O Pin 7          |    |

| 2.3.33 | PK[5:0] / XADDR[19:14] — Port K I/O Pins [5:0] | 61 |

| 2.3.34 | PM7 — Port M I/O Pin 7                         |    |

| 2.3.35 | PM6 — Port M I/O Pin 6                         |    |

| 2.3.36 | PM5 / TXCAN0 / SCK0 — Port M I/O Pin 5         |    |

| 2.3.37 | PM4 / RXCAN0 / MOSI0 — Port M I/O Pin 4        |    |

| 2.3.38 | PM3 / TXCAN0 / SS0 — Port M I/O Pin 3          |    |

| 2.3.39 | PM2 / RXCAN0 / MISO0 — Port M I/O Pin 2        |    |

| 2.3.40 | PM1 / TXCAN0 / TXB — Port M I/O Pin 1          |    |

| 2.3.41 | PM0 / RXCAN0 / RXB — Port M I/O Pin 0          |    |

| 2.3.42 | PP7 / KWP7 / PWM7 — Port P I/O Pin 7           |    |

| 2.3.43 | PP6 / KWP6 / PWM6 — Port P I/O Pin 6           |    |

| 2.3.44 | PP5 / KWP5 / PWM5 — Port P I/O Pin 5           |    |

| 2.3.45 | PP4 / KWP4 / PWM4 — Port P I/O Pin 4           |    |

| 2.3.46 | PP3 / KWP3 / PWM3 — Port P I/O Pin 3           |    |

| 2.3.47 | PP2 / KWP2 / PWM2 — Port P I/O Pin 2           |    |

| 2.3.48 | PP1 / KWP1 / PWM1 — Port P I/O Pin 1           |    |

| 2.3.49 | PP0 / KWP0 / PWM0 — Port P I/O Pin 0           |    |

| 2.3.50 | PS7 / SS0 — Port S I/O Pin 7                   |    |

| 2.3.51 | PS6 / SCK0 — Port S I/O Pin 6                  |    |

| 2.3.52 | PS5 / MOSI0 — Port S I/O Pin 5                 |    |

| 2.3.53 | PS4 / MISO0 — Port S I/O Pin 4                 |    |

| 2.3.54 | PS3 / TXD1 — Port S I/O Pin 3                  |    |

| 2.3.55 | PS2 / RXD1 — Port S I/O Pin 2                  |    |

| 2.3.56 | PS1 / TXD0 — Port S I/O Pin 1                  | 64 |

# **List of Figures**

| Figure 0-1  | Order Partnumber Example                                   | 15  |

|-------------|------------------------------------------------------------|-----|

| Figure 1-1  | MC9S12DJ64 Block Diagram                                   | 23  |

| Figure 1-2  | MC9S12DJ64 Memory Map out of Reset                         | 27  |

| Figure 1-3  | MC9S12D32 Memory Map out of Reset                          | 29  |

| Figure 2-1  | Pin Assignments in 112-pin LQFP for MC9S12DJ64             | 52  |

| Figure 2-2  | Pin Assignments in 80-pin QFP for MC9S12DJ64 and MC9S12D32 | 53  |

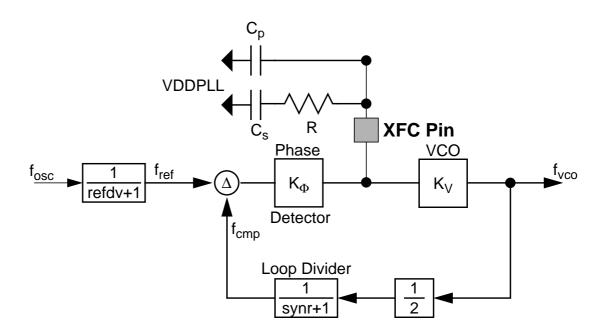

| Figure 2-3  | PLL Loop Filter Connections                                | 56  |

| Figure 2-4  | Colpitts Oscillator Connections (PE7=1)                    | 58  |

| Figure 2-5  | Pierce Oscillator Connections (PE7=0)                      | 58  |

| Figure 2-6  | External Clock Connections (PE7=0)                         | 58  |

| Figure 3-1  | Clock Connections                                          | 67  |

| Figure 22-1 | Recommended PCB Layout 112LQFP Colpitts Oscillator         | 82  |

| Figure 22-2 | Recommended PCB Layout for 80QFP Colpitts Oscillator       | 83  |

| Figure 22-3 | Recommended PCB Layout for 112LQFP Pierce Oscillator       | 84  |

| Figure 22-4 | Recommended PCB Layout for 80QFP Pierce Oscillator         | 85  |

| Figure A-1  | ATD Accuracy Definitions                                   | 100 |

| Figure A-2  | Basic PLL functional diagram                               | 109 |

| Figure A-3  | Jitter Definitions                                         | 111 |

| Figure A-4  | Maximum bus clock jitter approximation                     | 111 |

| Figure A-5  | SPI Master Timing (CPHA = 0)                               | 115 |

| Figure A-6  | SPI Master Timing (CPHA =1)                                | 116 |

| Figure A-7  | SPI Slave Timing (CPHA = 0)                                | 117 |

| Figure A-8  | SPI Slave Timing (CPHA =1)                                 | 117 |

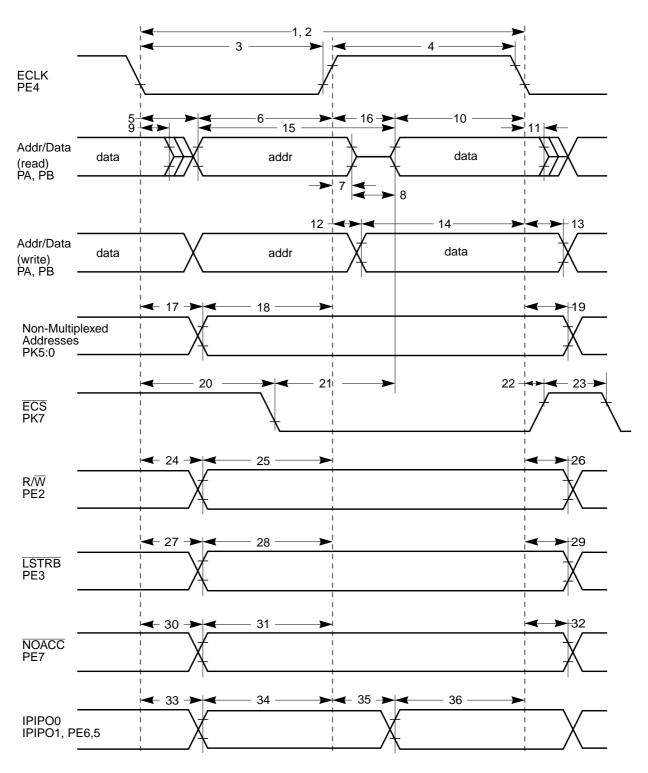

| Figure A-9  | General External Bus Timing                                | 120 |

| Figure B-1  | 112-pin LQFP mechanical dimensions (case no. 987)          | 124 |

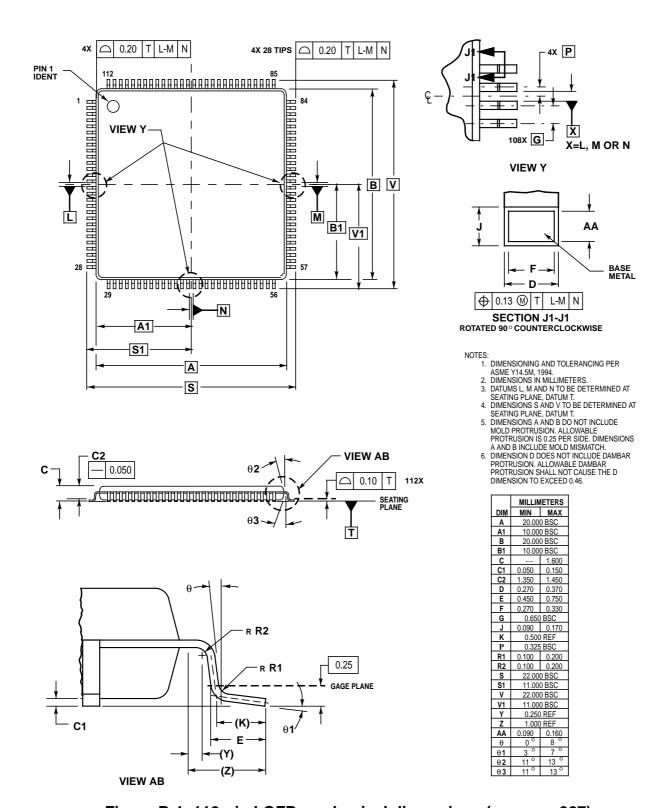

| Figure B-2  | 80-pin QFP Mechanical Dimensions (case no. 841B)           | 125 |

# 1.4 Block Diagram

**Figure 1-1** shows a block diagram of the MC9S12DJ64 device.

## \$0040 - \$007F

## **ECT (Enhanced Capture Timer 16 Bit 8 Channels)**

| Address | Name                |                 | Bit 7  | Bit 6 | Bit 5 | Bit 4      | Bit 3     | Bit 2 | Bit 1 | Bit 0 |

|---------|---------------------|-----------------|--------|-------|-------|------------|-----------|-------|-------|-------|

| \$0063  | PACN2 (Io)          | Read:<br>Write: | Bit 7  | 6     | 5     | 4          | 3         | 2     | 1     | Bit 0 |

| \$0064  | PACN1 (hi)          | Read:<br>Write: | Bit 7  | 6     | 5     | 4          | 3         | 2     | 1     | Bit 0 |

| \$0065  | PACN0 (Io)          | Read:<br>Write: | Bit 7  | 6     | 5     | 4          | 3         | 2     | 1     | Bit 0 |

| \$0066  | MCCTL               | Read:<br>Write: | MCZI   | MODMC | RDMCL | 0<br>ICLAT | 0<br>FLMC | MCEN  | MCPR1 | MCPR0 |

| \$0067  | MCFLG               | Read:<br>Write: | MCZF   | 0     | 0     | 0          | POLF3     | POLF2 | POLF1 | POLF0 |

| \$0068  | ICPAR               | Read:<br>Write: | 0      | 0     | 0     | 0          | PA3EN     | PA2EN | PA1EN | PA0EN |

| \$0069  | DLYCT               | Read:<br>Write: | 0      | 0     | 0     | 0          | 0         | 0     | DLY1  | DLY0  |

| \$006A  | ICOVW               | Read:<br>Write: | NOVW7  | NOVW6 | NOVW5 | NOVW4      | NOVW3     | NOVW2 | NOVW1 | NOVW0 |

| \$006B  | ICSYS               | Read:<br>Write: | SH37   | SH26  | SH15  | SH04       | TFMOD     | PACMX | BUFEN | LATQ  |

| \$006C  | Reserved            | Read:<br>Write: |        |       |       |            |           |       |       |       |

| \$006D  | TIMTST<br>Test Only | Read:<br>Write: | 0      | 0     | 0     | 0          | 0         | 0     | TCBYP | 0     |

| \$006E  | Reserved            | Read:<br>Write: |        |       |       |            |           |       |       |       |

| \$006F  | Reserved            | Read:<br>Write: |        |       |       |            |           |       |       |       |

| \$0070  | PBCTL               | Read:<br>Write: | 0      | PBEN  | 0     | 0          | 0         | 0     | PBOVI | 0     |

| \$0071  | PBFLG               | Read:<br>Write: | 0      | 0     | 0     | 0          | 0         | 0     | PBOVF | 0     |

| \$0072  | PA3H                | Read:<br>Write: | Bit 7  | 6     | 5     | 4          | 3         | 2     | 1     | Bit 0 |

| \$0073  | PA2H                | Read:<br>Write: | Bit 7  | 6     | 5     | 4          | 3         | 2     | 1     | Bit 0 |

| \$0074  | PA1H                | Read:<br>Write: | Bit 7  | 6     | 5     | 4          | 3         | 2     | 1     | Bit 0 |

| \$0075  | PA0H                | Read:<br>Write: | Bit 7  | 6     | 5     | 4          | 3         | 2     | 1     | Bit 0 |

| \$0076  | MCCNT (hi)          | Read:<br>Write: | Bit 15 | 14    | 13    | 12         | 11        | 10    | 9     | Bit 8 |

| \$0077  | MCCNT (lo)          | Read:<br>Write: | Bit 7  | 6     | 5     | 4          | 3         | 2     | 1     | Bit 0 |

| \$0078  | TC0H (hi)           | Read:<br>Write: | Bit 15 | 14    | 13    | 12         | 11        | 10    | 9     | Bit 8 |

| \$0079  | TC0H (lo)           | Read:<br>Write: | Bit 7  | 6     | 5     | 4          | 3         | 2     | 1     | Bit 0 |

| \$007A  | TC1H (hi)           | Read:<br>Write: | Bit 15 | 14    | 13    | 12         | 11        | 10    | 9     | Bit 8 |

| \$007B  | TC1H (lo)           | Read:<br>Write: | Bit 7  | 6     | 5     | 4          | 3         | 2     | 1     | Bit 0 |

### \$00D0 - \$00D7

## **SCI1 (Asynchronous Serial Interface)**

| Address | Name    |

|---------|---------|

| \$00D5  | SCI1SR2 |

| \$00D6  | SCI1DRH |

| \$00D7  | SCI1DRI |

|        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| Read:  | 0     | 0     | 0     | 0     | 0     | BRK13 | TXDIR | RAF   |

| Write: |       |       |       |       |       | DKKIS | IADIK |       |

| Read:  | R8    | Т8    | 0     | 0     | 0     | 0     | 0     | 0     |

| Write: |       | 10    |       |       |       |       |       |       |

| Read:  | R7    | R6    | R5    | R4    | R3    | R2    | R1    | R0    |

| Write: | T7    | T6    | T5    | T4    | T3    | T2    | T1    | T0    |

## \$00D8 - \$00DF

## **SPI0 (Serial Peripheral Interface)**

| Address | Name     |

|---------|----------|

| \$00D8  | SPI0CR1  |

| \$00D9  | SPI0CR2  |

| \$00DA  | SPI0BR   |

| \$00DB  | SPI0SR   |

| \$00DC  | Reserved |

| \$00DD  | SPI0DR   |

| \$00DE  | Reserved |

| \$00DF  | Reserved |

| _               |       |       |       |           |         |       |         |       |

|-----------------|-------|-------|-------|-----------|---------|-------|---------|-------|

|                 | Bit 7 | Bit 6 | Bit 5 | Bit 4     | Bit 3   | Bit 2 | Bit 1   | Bit 0 |

| Read:<br>Write: | SPIE  | SPE   | SPTIE | MSTR      | CPOL    | СРНА  | SSOE    | LSBFE |

| Read:           | 0     | 0     | 0     | MODFEN    | BIDIROE | 0     | SPISWAI | SPC0  |

| Write:          |       |       |       | INIODELIN | BIDIKOL |       | SFISWAI | 3500  |

| Read:           | 0     | SPPR2 | SPPR1 | SPPR0     | 0       | SPR2  | SPR1    | SPR0  |

| Write:          |       | SFFNZ | SEEKI | SFFRU     |         | SFRZ  | SEKT    | SFRU  |

| Read:           | SPIF  | 0     | SPTEF | MODF      | 0       | 0     | 0       | 0     |

| Write:          |       |       |       |           |         |       |         |       |

| Read:           | 0     | 0     | 0     | 0         | 0       | 0     | 0       | 0     |

| Write:          |       |       |       |           |         |       |         |       |

| Read:<br>Write: | Bit7  | 6     | 5     | 4         | 3       | 2     | 1       | Bit0  |

| Read:           | 0     | 0     | 0     | 0         | 0       | 0     | 0       | 0     |

| Write:          |       |       |       |           |         |       |         |       |

| Read:           | 0     | 0     | 0     | 0         | 0       | 0     | 0       | 0     |

| Write:          |       |       |       |           |         |       |         |       |

### \$00E0 - \$00E7

## IIC (Inter IC Bus)

| Address | Name     |

|---------|----------|

| \$00E0  | IBAD     |

| \$00E1  | IBFD     |

| \$00E2  | IBCR     |

| \$00E3  | IBSR     |

| \$00E4  | IBDR     |

| \$00E5  | Reserved |

| \$00E6  | Reserved |

| \$00E7  | Reserved |

|                 | Bit 7 | Bit 6 | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0   |

|-----------------|-------|-------|---------|-------|-------|-------|-------|---------|

| Read:<br>Write: | ADR7  | ADR6  | ADR5    | ADR4  | ADR3  | ADR2  | ADR1  | 0       |

| Read:<br>Write: | IBC7  | IBC6  | IBC5    | IBC4  | IBC3  | IBC2  | IBC1  | IBC0    |

| Read:           | IBEN  | IBIE  | MS/SL   | TX/RX | TXAK  | 0     | 0     | IBSWAI  |

| Write:          | IDEN  | IDIE  | IVIO/OL | IA/NA | IAAN  | RSTA  |       | IDSVVAI |

| Read:           | TCF   | IAAS  | IBB     | IBAL  | 0     | SRW   | IBIF  | RXAK    |

| Write:          |       |       |         | IDAL  |       |       | IDIF  |         |

| Read:<br>Write: | D7    | D6    | D5      | D4    | D3    | D2    | D1    | D 0     |

| Read:           | 0     | 0     | 0       | 0     | 0     | 0     | 0     | 0       |

| Write:          |       |       |         |       |       |       |       |         |

| Read:           | 0     | 0     | 0       | 0     | 0     | 0     | 0     | 0       |

| Write:          |       |       |         |       |       |       |       |         |

| Read:           | 0     | 0     | 0       | 0     | 0     | 0     | 0     | 0       |

| Write:          |       |       |         |       |       |       |       |         |

### 2.3.38 PM3 / TXCAN0 / SS0 — Port M I/O Pin 3

PM3 is a general purpose input or output pin. It can be configured as the transmit pin TXCAN of the Freescale Scalable Controller Area Network controller 0 (CAN0). It can be configured as the slave select pin  $\overline{SS}$  of the Serial Peripheral Interface 0 (SPI0).

#### 2.3.39 PM2 / RXCAN0 / MISO0 — Port M I/O Pin 2

PM2 is a general purpose input or output pin. It can be configured as the receive pin RXCAN of the Freescale Scalable Controller Area Network controller 0 (CAN0). It can be configured as the master input (during master mode) or slave output pin (during slave mode) MISO for the Serial Peripheral Interface 0 (SPI0).

#### 2.3.40 PM1 / TXCAN0 / TXB — Port M I/O Pin 1

PM1 is a general purpose input or output pin. It can be configured as the transmit pin TXCAN of the Freescale Scalable Controller Area Network controller 0 (CAN0). It can be configured as the transmit pin TXB of the BDLC.

#### 2.3.41 PM0 / RXCAN0 / RXB — Port M I/O Pin 0

PM0 is a general purpose input or output pin. It can be configured as the receive pin RXCAN of the Freescale Scalable Controller Area Network controller 0 (CAN0). It can be configured as the receive pin RXB of the BDLC.

#### 2.3.42 PP7 / KWP7 / PWM7 — Port P I/O Pin 7

PP7 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as Pulse Width Modulator (PWM) channel 7 output.

#### 2.3.43 PP6 / KWP6 / PWM6 — Port P I/O Pin 6

PP6 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as Pulse Width Modulator (PWM) channel 6 output.

#### 2.3.44 PP5 / KWP5 / PWM5 — Port P I/O Pin 5

PP5 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as Pulse Width Modulator (PWM) channel 5 output.

#### 2.3.45 PP4 / KWP4 / PWM4 — Port P I/O Pin 4

PP4 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as Pulse Width Modulator (PWM) channel 4 output.

(A) MOTOROLA

Table 4-2 Clock Selection Based on PE7

| PE7 = XCLKS | Description                               |

|-------------|-------------------------------------------|

| 0           | Pierce Oscillator/external clock selected |

**Table 4-3 Voltage Regulator VREGEN**

| VREGEN | Description                                                                                  |  |  |  |  |

|--------|----------------------------------------------------------------------------------------------|--|--|--|--|

| 1      | Internal Voltage Regulator enabled                                                           |  |  |  |  |

|        | Internal Voltage Regulator disabled, VDD1,2 and VDDPLL must be supplied externally with 2.5V |  |  |  |  |

## 4.3 Security

The device will make available a security feature preventing the unauthorized read and write of the memory contents. This feature allows:

- Protection of the contents of FLASH,

- Protection of the contents of EEPROM,

- Operation in single-chip mode,

- Operation from external memory with internal FLASH and EEPROM disabled.

The user must be reminded that part of the security must lie with the user's code. An extreme example would be user's code that dumps the contents of the internal program. This code would defeat the purpose of security. At the same time the user may also wish to put a back door in the user's program. An example of this is the user downloads a key through the SCI which allows access to a programming routine that updates parameters stored in EEPROM.

## 4.3.1 Securing the Microcontroller

Once the user has programmed the FLASH and EEPROM (if desired), the part can be secured by programming the security bits located in the FLASH module. These non-volatile bits will keep the part secured through resetting the part and through powering down the part.

The security byte resides in a portion of the Flash array.

Check the Flash Block User Guide for more details on the security configuration.

## 4.3.2 Operation of the Secured Microcontroller

#### 4.3.2.1 Normal Single Chip Mode

This will be the most common usage of the secured part. Everything will appear the same as if the part was not secured with the exception of BDM operation. The BDM operation will be blocked.

(M) MOTOROLA

#### 4.3.2.2 Executing from External Memory

The user may wish to execute from external space with a secured microcontroller. This is accomplished by resetting directly into expanded mode. The internal FLASH and EEPROM will be disabled. BDM operations will be blocked.

### 4.3.3 Unsecuring the Microcontroller

In order to unsecure the microcontroller, the internal FLASH and EEPROM must be erased. This can be done through an external program in expanded mode or via a sequence of BDM commands. Unsecuring is also possible via the Backdoor Key Access. Refer to Flash Block Guide for details.

Once the user has erased the FLASH and EEPROM, the part can be reset into special single chip mode. This invokes a program that verifies the erasure of the internal FLASH and EEPROM. Once this program completes, the user can erase and program the FLASH security bits to the unsecured state. This is generally done through the BDM, but the user could also change to expanded mode (by writing the mode bits through the BDM) and jumping to an external program (again through BDM commands). Note that if the part goes through a reset before the security bits are reprogrammed to the unsecure state, the part will be secured again.

### 4.4 Low Power Modes

The microcontroller features three main low power modes. Consult the respective Block User Guide for information on the module behavior in Stop, Pseudo Stop, and Wait Mode. An important source of information about the clock system is the Clock and Reset Generator User Guide (CRG).

## 4.4.1 Stop

Executing the CPU STOP instruction stops all clocks and the oscillator thus putting the chip in fully static mode. Wake up from this mode can be done via reset or external interrupts.

## 4.4.2 Pseudo Stop

This mode is entered by executing the CPU STOP instruction. In this mode the oscillator is still running and the Real Time Interrupt (RTI) or Watchdog (COP) sub module can stay active. Other peripherals are turned off. This mode consumes more current than the full STOP mode, but the wake up time from this mode is significantly shorter.

#### 4.4.3 Wait

This mode is entered by executing the CPU WAI instruction. In this mode the CPU will not execute instructions. The internal CPU signals (address and data bus) will be fully static. All peripherals stay active. For further power consumption the peripherals can individually turn off their local clocks.

## 4.4.4 Run

Although this is not a low power mode, unused peripheral modules should not be enabled in order to save power.

C3 VDDA VDD1<sup>C</sup> C2 VDDR VSSPLL VDDPLL

Figure 22-1 Recommended PCB Layout 112LQFP Colpitts Oscillator

VSSA VSSX VDDA VDD2 VSSR VDDR VSSPLL VDDPLL

Figure 22-2 Recommended PCB Layout for 80QFP Colpitts Oscillator

**NOTE:** Please refer to the temperature rating of the device (C, V, M) with regards to the ambient temperature  $T_A$  and the junction temperature  $T_J$ . For power dissipation calculations refer to **Section A.1.8 Power Dissipation and Thermal** Characteristics.

**Table A-4 Operating Conditions**

| Rating                                           | Symbol             | Min               | Тур | Max  | Unit |

|--------------------------------------------------|--------------------|-------------------|-----|------|------|

| I/O, Regulator and Analog Supply Voltage         | $V_{DD5}$          | 4.5               | 5   | 5.25 | V    |

| Digital Logic Supply Voltage <sup>1</sup>        | V <sub>DD</sub>    | 2.35              | 2.5 | 2.75 | V    |

| PLL Supply Voltage <sup>1</sup>                  | V <sub>DDPLL</sub> | 2.35              | 2.5 | 2.75 | V    |

| Voltage Difference VDDX to VDDR and VDDA         | $\Delta_{VDDX}$    | -0.1              | 0   | 0.1  | V    |

| Voltage Difference VSSX to VSSR and VSSA         | $\Delta_{VSSX}$    | -0.1              | 0   | 0.1  | V    |

| Oscillator                                       | f <sub>osc</sub>   | 0.5               | -   | 16   | MHz  |

| Bus Frequency                                    | f <sub>bus</sub>   | 0.25 <sup>2</sup> | -   | 25   | MHz  |

| MC9S12DJ64 <b>C</b>                              |                    |                   |     |      |      |

| Operating Junction Temperature Range             | $T_J$              | -40               | -   | 100  | °C   |

| Operating Ambient Temperature Range <sup>3</sup> | T <sub>A</sub>     | -40               | 27  | 85   | °C   |

| MC9S12DJ64 <b>V</b>                              |                    |                   |     |      |      |

| Operating Junction Temperature Range             | $T_J$              | -40               | -   | 120  | °C   |

| Operating Ambient Temperature Range <sup>3</sup> | T <sub>A</sub>     | -40               | 27  | 105  | °C   |

| MC9S12DJ64 <b>M</b>                              |                    |                   |     |      |      |

| Operating Junction Temperature Range             | $T_J$              | -40               | -   | 140  | °C   |

| Operating Ambient Temperature Range <sup>3</sup> | T <sub>A</sub>     | -40               | 27  | 125  | °C   |

#### NOTES:

## A.1.8 Power Dissipation and Thermal Characteristics

Power dissipation and thermal characteristics are closely related. The user must assure that the maximum operating junction temperature is not exceeded. The average chip-junction temperature ( $T_J$ ) in  ${}^{\circ}C$  can be obtained from:

$$\mathsf{T}_\mathsf{J} = \mathsf{T}_\mathsf{A} + (\mathsf{P}_\mathsf{D} \bullet \Theta_\mathsf{JA})$$

$T_{,I}$  = Junction Temperature, [°C]

<sup>1.</sup> The device contains an internal voltage regulator to generate the logic and PLL supply out of the I/O supply. The given operating range applies when this regulator is disabled and the device is powered from an external source.

Some blocks e.g. ATD (conversion) and NVMs (program/erase) require higher bus frequencies for proper operation.

<sup>3.</sup> Please refer to **Section A.1.8 Power Dissipation and Thermal Characteristics** for more details about the relation between ambient temperature T<sub>A</sub> and device junction temperature T<sub>J</sub>.

#### MC9S12DJ64 Device User Guide — V01.20

#### NOTES:

- PLL off

At those low power dissipation levels T<sub>J</sub> = T<sub>A</sub> can be assumed

96

## A.3 NVM, Flash and EEPROM

**NOTE:** Unless otherwise noted the abbreviation NVM (Non Volatile Memory) is used for both Flash and EEPROM.

### A.3.1 NVM timing

The time base for all NVM program or erase operations is derived from the oscillator. A minimum oscillator frequency f<sub>NVMOSC</sub> is required for performing program or erase operations. The NVM modules do not have any means to monitor the frequency and will not prevent program or erase operation at frequencies above or below the specified minimum. Attempting to program or erase the NVM modules at a lower frequency a full program or erase transition is not assured.

The Flash and EEPROM program and erase operations are timed using a clock derived from the oscillator using the FCLKDIV and ECLKDIV registers respectively. The frequency of this clock must be set within the limits specified as f<sub>NVMOP</sub>.

The minimum program and erase times shown in **Table A-11** are calculated for maximum  $f_{NVMOP}$  and maximum  $f_{bus}$ . The maximum times are calculated for minimum  $f_{NVMOP}$  and a  $f_{bus}$  of 2MHz.

#### A.3.1.1 Single Word Programming

The programming time for single word programming is dependant on the bus frequency as a well as on the frequency  $f_{NVMOP}$  and can be calculated according to the following formula.

$$t_{\text{swpgm}} = 9 \cdot \frac{1}{f_{\text{NVMOP}}} + 25 \cdot \frac{1}{f_{\text{bus}}}$$

## A.3.1.2 Row Programming

This applies only to the Flash where up to 32 words in a row can be programmed consecutively by keeping the command pipeline filled. The time to program a consecutive word can be calculated as:

$$t_{bwpgm} = 4 \cdot \frac{1}{f_{NVMOP}} + 9 \cdot \frac{1}{f_{bus}}$$

The time to program a whole row is:

$$t_{brpqm} = t_{swpqm} + 31 \cdot t_{bwpqm}$$

Row programming is more than 2 times faster than single word programming.

#### A.3.1.3 Sector Erase

Erasing a 512 byte Flash sector or a 4 byte EEPROM sector takes:

#### NOTES:

- 1. Depending on the crystal a damping series resistor might be necessary

- 2.  $f_{OSC} = 4MHz$ , C = 22pF.

- 3. Maximum value is for extreme cases using high Q, low frequency crystals

- 4. Only valid if Pierce oscillator/external clock mode is selected

#### A.5.3 Phase Locked Loop

The oscillator provides the reference clock for the PLL. The PLL's Voltage Controlled Oscillator (VCO) is also the system clock source in self clock mode.

#### A.5.3.1 XFC Component Selection

This section describes the selection of the XFC components to achieve a good filter characteristics.

Figure A-2 Basic PLL functional diagram

The following procedure can be used to calculate the resistance and capacitance values using typical values for  $K_1$ ,  $f_1$  and  $i_{ch}$  from **Table A-16**.

The grey boxes show the calculation for  $f_{VCO} = 50 MHz$  and  $f_{ref} = 1 MHz$ . E.g., these frequencies are used for  $f_{OSC} = 4 MHz$  and a 25MHz bus clock.

The VCO Gain at the desired VCO frequency is approximated by:

$$K_V = K_1 \cdot e^{\frac{(f_1 - f_{vco})}{K_1 \cdot 1V}} = -100 \cdot e^{\frac{(60 - 50)}{-100}} = -90.48MHz/V$$

Figure A-9 General External Bus Timing

## **Table A-20 Expanded Bus Timing Characteristics**

| Conditions are shown in <b>Table A-4</b> unless otherwise noted, $C_{LOAD} = 50pF$ |   |                                                                          |                  |     |     |     |      |  |  |

|------------------------------------------------------------------------------------|---|--------------------------------------------------------------------------|------------------|-----|-----|-----|------|--|--|

| Num                                                                                | С | Rating                                                                   | Symbol           | Min | Тур | Max | Unit |  |  |

| 32                                                                                 | D | NOACC hold time                                                          | t <sub>NOH</sub> | 2   |     |     | ns   |  |  |

| 33                                                                                 | D | IPIPO[1:0] delay time                                                    | t <sub>P0D</sub> | 2   |     | 7   | ns   |  |  |

| 34                                                                                 | D | IPIPO[1:0] valid time to E rise (PW <sub>EL</sub> -t <sub>P0D</sub> )    | t <sub>P0V</sub> | 11  |     |     | ns   |  |  |

| 35                                                                                 | D | IPIPO[1:0] delay time <sup>1</sup> (PW <sub>EH</sub> -t <sub>P1V</sub> ) | t <sub>P1D</sub> | 2   |     | 25  | ns   |  |  |

| 36                                                                                 | D | IPIPO[1:0] valid time to E fall                                          | t <sub>P1V</sub> | 11  |     |     | ns   |  |  |

#### NOTES:

<sup>1.</sup> Affected by clock stretch: add N x  $t_{cyc}$  where N=0,1,2 or 3, depending on the number of clock stretches.

## B.2 112-pin LQFP package

Figure B-1 112-pin LQFP mechanical dimensions (case no. 987)

## FINAL PAGE OF 128 PAGES