Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M0+                                                           |

|                            |                                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                     |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                            |

| Number of I/O              | 50                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 16K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                              |

| Data Converters            | A/D 16x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 64-QFN (9x9)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml22j17a-mut |

# **Table of Contents**

| Int | roduc                       | tion                                  | 1  |  |

|-----|-----------------------------|---------------------------------------|----|--|

| Fe  | atures                      | S                                     | 1  |  |

| 1.  | Description                 |                                       |    |  |

| 2.  | Conf                        | figuration Summary                    | 7  |  |

| 3.  | Orde                        | ering Information                     | 9  |  |

|     | 3.1.                        | SAM L22N                              | 9  |  |

|     | 3.2.                        | SAM L22J                              | 9  |  |

|     | 3.3.                        | SAM L22G                              | 10 |  |

|     | 3.4.                        | Device Identification                 | 10 |  |

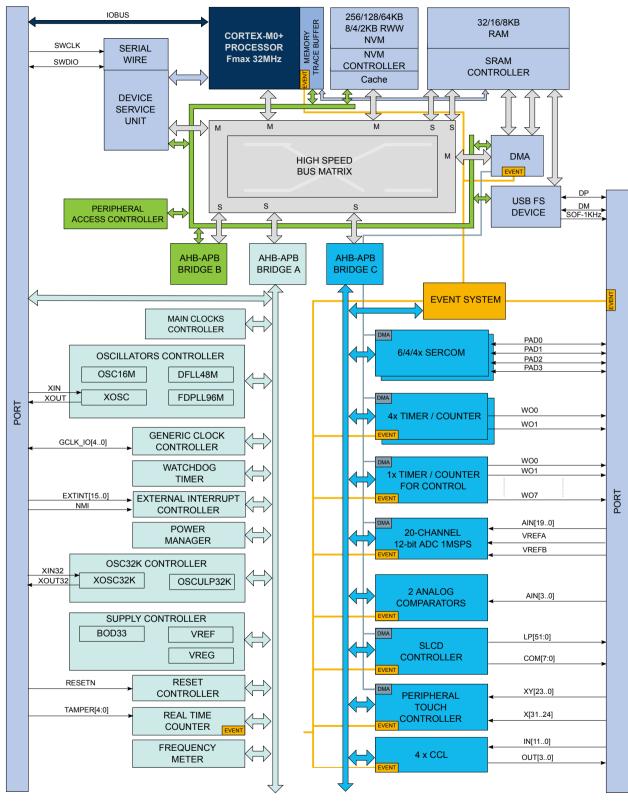

| 4.  | Bloc                        | k Diagram                             | 12 |  |

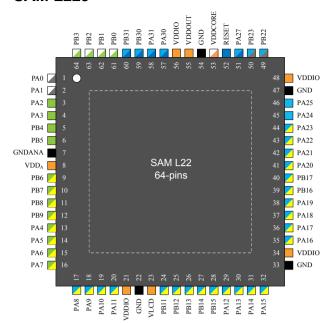

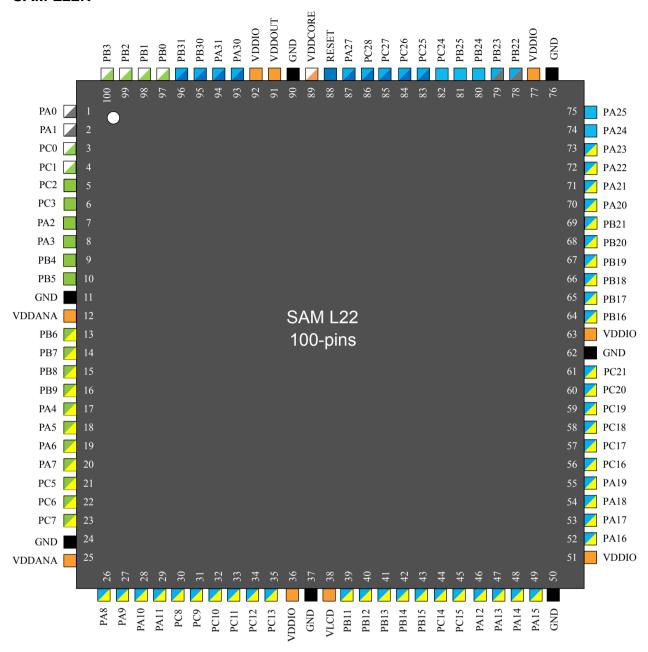

| 5.  | Pino                        | ut                                    | 14 |  |

|     | 5.1.                        | SAM L22G                              | 14 |  |

|     | 5.2.                        | SAM L22J                              |    |  |

|     | 5.3.                        | SAM L22N                              | 16 |  |

| 6.  | S. Signal Descriptions List |                                       |    |  |

| 7   | I/O N                       | Aultiplexing and Considerations       | 20 |  |

| ٠.  | 7.1.                        | Multiplexed Signals                   |    |  |

|     | 7.1.<br>7.2.                | Other Functions                       |    |  |

| 8   | Pow                         | er Supply and Start-Up Considerations | 25 |  |

| О.  | 8.1.                        | Power Domain Overview                 |    |  |

|     | 8.2.                        | Power Supply Considerations           |    |  |

|     | 8.3.                        | Power-Up                              |    |  |

|     | 8.4.                        | Power-On Reset and Brown-Out Detector |    |  |

|     | 8.5.                        | Performance Level Overview            |    |  |

| 9.  | Prod                        | luct Mapping                          | 30 |  |

| 10. | . Mem                       | nories                                | 31 |  |

|     | 10.1.                       | Embedded Memories                     | 31 |  |

|     |                             | Physical Memory Map                   |    |  |

|     |                             | NVM User Row Mapping                  |    |  |

|     | 10.4.                       | NVM Software Calibration Area Mapping | 33 |  |

|     | 10.5.                       | Serial Number                         | 33 |  |

| 11. | Proc                        | essor and Architecture                | 34 |  |

|     | 11.1.                       | Cortex M0+ Processor                  | 34 |  |

|     | 11 2                        | Nested Vector Interrunt Controller    | 36 |  |

## 4. Block Diagram

Note:

## 5.2. SAM L22J

## 5.3. SAM L22N

# 6. Signal Descriptions List

The following table gives details on signal names classified by peripheral.

Table 6-1. Signal Descriptions List

| Signal Name                         | Function                                                              | Туре           | Active Level |  |  |  |

|-------------------------------------|-----------------------------------------------------------------------|----------------|--------------|--|--|--|

| Analog Comparators - AC             |                                                                       |                |              |  |  |  |

| AIN[3:0]                            | AC Analog Inputs                                                      | Analog         |              |  |  |  |

| CMP[1:0]                            | AC Analog Output                                                      | Analog         |              |  |  |  |

| <b>Analog Digital Conve</b>         | rter - ADC                                                            |                |              |  |  |  |

| AIN[19:0]                           | ADC Analog Inputs                                                     | Analog         |              |  |  |  |

| VREFA                               | ADC Voltage External Reference A                                      | Analog         |              |  |  |  |

| VREFB                               | ADC Voltage External Reference B                                      | Analog         |              |  |  |  |

| External Interrupt Co               | ntroller - EIC                                                        |                |              |  |  |  |

| EXTINT[15:0]                        | External Interrupts inputs                                            | Digital        |              |  |  |  |

| NMI                                 | External Non-Maskable Interrupt input                                 | Digital        |              |  |  |  |

| Generic Clock Gener                 | ator - GCLK                                                           |                |              |  |  |  |

| GCLK_IO[4:0]                        | Generic Clock (source clock inputs or generic clock generator output) | Digital        |              |  |  |  |

| <b>Custom Control Logi</b>          | c - CCL                                                               |                |              |  |  |  |

| IN[11:0]                            | Logic Inputs                                                          | Digital        |              |  |  |  |

| OUT[3:0]                            | Logic Outputs                                                         | Digital        |              |  |  |  |

| Supply Controller - S               | UPC                                                                   |                |              |  |  |  |

| VBAT                                | External battery supply Inputs                                        | Analog         |              |  |  |  |

| PSOK                                | Main Power Supply OK input                                            | Digital        |              |  |  |  |

| OUT[1:0]                            | Logic Outputs                                                         | Digital        |              |  |  |  |

| Power Manager - PM                  |                                                                       |                |              |  |  |  |

| RESETN                              | Reset input                                                           | Digital        | Low          |  |  |  |

| Serial Communicatio                 | n Interface - SERCOMx                                                 |                |              |  |  |  |

| PAD[3:0] SERCOM Inputs/Outputs Pads |                                                                       | Digital        |              |  |  |  |

| Oscillators Control -               | OSCCTRL                                                               |                |              |  |  |  |

| XIN                                 | Crystal or external clock Input                                       | Analog/Digital |              |  |  |  |

| XOUT                                | Crystal Output                                                        | Analog         |              |  |  |  |

| Signal Name Function                        |               | Туре    | Active Level |  |  |

|---------------------------------------------|---------------|---------|--------------|--|--|

| SOF 1kHz USB Start of Frame                 |               | Digital |              |  |  |

| Real Timer Clock - RTC                      |               |         |              |  |  |

| RTC_IN[4:0] Tamper or external wake-up pins |               | Digital |              |  |  |

| RTC_OUT                                     | Tamper output | Digital |              |  |  |

Table 7-2. Oscillator Pinout

| Oscillator     | Supply | Signal | I/O pin |

|----------------|--------|--------|---------|

| XOSC           | VDDIO  | XIN    | PB22    |

|                |        | XOUT   | PB23    |

| XOSC32K VSWOUT | XIN32  | PA00   |         |

|                |        | XOUT32 | PA01    |

**Note:** In order to minimize the cycle-to-cycle jitter of the external oscillator, keep the neighboring pins as steady as possible. For neighboring pin details, refer to the Oscillator Pinout section.

Table 7-3. XOSC32K Jitter Minimization

| Package | Steady Signal Recommended          |

|---------|------------------------------------|

| L22N    | PB00, PB01, PB02, PB03, PC00, PC01 |

| L22J    | PB00, PB01, PB02, PB03, PA02, PA03 |

| L22G    | PB02, PB03, PA02, PA03             |

### 7.2.2. Serial Wire Debug Interface Pinout

Only the SWCLK pin is mapped to the normal PORT functions. A debugger cold-plugging or hot-plugging detection will automatically switch the SWDIO port to the SWDIO function.

Table 7-4. Serial Wire Debug Interface Pinout

| Signal | Supply | I/O pin |

|--------|--------|---------|

| SWCLK  | VDDIO  | PA30    |

| SWDIO  | VDDIO  | PA31    |

## 7.2.3. SERCOM USART and I<sup>2</sup>C Configurations

The SAM L22 has up to six instances of the serial communication interface (SERCOM) peripheral. The following table lists the supported communication protocols for each SERCOM instance.

Table 7-5. SERCOM USART and I<sup>2</sup>C Protocols

|                                    | SERCOM Instance |         |         |         |         |         |

|------------------------------------|-----------------|---------|---------|---------|---------|---------|

| Protocol                           | SERCOM0         | SERCOM1 | SERCOM2 | SERCOM3 | SERCOM4 | SERCOM5 |

| I <sup>2</sup> C                   | no              | yes     | yes     | yes     | yes     | yes     |

| I <sup>2</sup> C at<br>3.4MHz      | no              | yes     | no      | no      | no      | yes     |

| USART including RS485 and ISO 7816 | yes             | yes     | yes     | yes     | yes     | yes     |

| SPI                                | yes             | yes     | yes     | yes     | yes     | yes     |

**Note:** Not all available I<sup>2</sup>C pins support I<sup>2</sup>C mode at 3.4MHz.

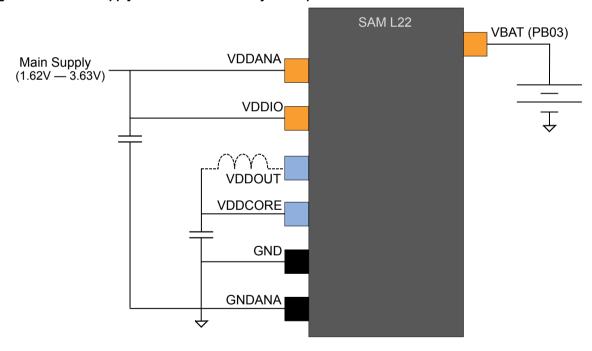

Main Supply (1.62V — 3.63V)

VDDIO

VDDOUT

VDDCORE

GND

Figure 8-2. Power Supply Connection for Switching/Linear Mode

Figure 8-3. Power Supply Connection for Battery Backup

### 8.2.4. Power-Up Sequence

## 8.2.4.1. Supply Order

VDDIO and VDDANA must have the same supply sequence. Ideally, they must be connected together.

## 8.2.4.2. Minimum Rise Rate

One integrated power-on reset (POR) circuits monitoring VDDIO requires a minimum rise rate.

#### 8.2.4.3. Maximum Rise Rate

The rise rate of the power supplies must not exceed the values described in Electrical Characteristics.

### 8.3. Power-Up

This section summarizes the power-up sequence of the SAM L22. The behavior after power-up is controlled by the Power Manager.

### 8.3.1. Starting of Internal Regulator

After power-up, the device is set to its initial state and kept in Reset, until the power has stabilized throughout the device. The default performance level after power-up is PL0.

The internal regulator provides the internal VDDCORE corresponding to this performance level. Once the external voltage VDDIO and the internal VDDCORE reach a stable value, the internal Reset is released.

#### 8.3.2. Starting of Clocks

Once the power has stabilized and the internal Reset is released, the device will use a 4MHz clock by default. The clock source for this clock signal is OSC16M, which is enabled and configured at 4MHz after a reset by default. This is also the default time base for Generic Clock Generator 0. In turn, Generator 0 provides the main clock GCLK MAIN which is used by the Power Manager (PM).

Some synchronous system clocks are active after Start-Up, allowing software execution. Refer to the "Clock Mask Register" section in the PM-Power Manager documentation for the list of clocks that are running by default. Synchronous system clocks that are running receive the 4MHz clock from Generic Clock Generator 0. Other generic clocks are disabled.

#### 8.3.3. I/O Pins

After power-up, the I/O pins are tri-stated except PA30, which is pull-up enabled and configured as input.

#### 8.3.4. Fetching of Initial Instructions

After Reset has been released, the CPU starts fetching PC and SP values from the Reset address, 0x00000000. This points to the first executable address in the internal Flash memory. The code read from the internal Flash can be used to configure the clock system and clock sources. See the related peripheral documentation for details. Refer to the ARM Architecture Reference Manual for more information on CPU startup (http://www.arm.com).

### 8.4. Power-On Reset and Brown-Out Detector

The SAM L22 embeds three features to monitor, warn and/or reset the device:

- POR: Power-on Reset on VSWOUT and VDDIO

- BOD33: Brown-out detector on VSWOUT/VBAT

- Brown-out detector internal to the voltage regulator for VDDCORE. BOD12 is calibrated in production and its calibration parameters are stored in the NVM User Row. This data should not be changed if the User Row is written to in order to assure correct behavior.

#### 8.4.1. Power-On Reset on VSWOUT

VSWOUT is monitored by POR. Monitoring is always activated, including startup and all sleep modes. If VSWOUT goes below the threshold voltage, the entire chip is reset.

#### 8.4.2. Power-On Reset on VDDIO

VDDIO is monitored by POR. Monitoring is always activated, including startup and all sleep modes. If VDDIO goes below the threshold voltage, all I/Os supplied by VDDIO are reset.

#### 8.4.3. Brown-Out Detector on VSWOUT/VBAT

BOD33 monitors VSWOUT or VBAT depending on configuration.

#### 8.4.4. Brown-Out Detector on VDDCORE

Once the device has started up, BOD12 monitors the internal VDDCORE.

## 8.5. Performance Level Overview

By default, the device will start in Performance Level 0. This PL0 is aiming for the lowest power consumption by limiting logic speeds and the CPU frequency. As a consequence, all GCLK will have limited capabilities, and some peripherals and clock sources will not work or with limited capabilities:

List of peripherals/clock sources not available in PL0:

- USB (limited by logic frequency)

- DFLL48M

List of peripherals/clock sources with limited capabilities in PL0:

- All AHB/APB peripherals are limited by CPU frequency

- DPLL96M: may be able to generate 48MHz internally, but the output cannot be used by logic

- GCLK: the maximum frequency is by factor 4 compared to PL2

- SW interface: the maximum frequency is by factor 4 compared to PL2

- TC: the maximum frequency is by factor 4 compared to PL2

- TCC:the maximum frequency is by factor 4 compared to PL2

- SERCOM: the maximum frequency is by factor 4 compared to PL2

List of peripherals/clock sources with full capabilities in PL0:

- AC

- ADC

- EIC

- OSC16M

- PTC

- All 32KHz clock sources and peripherals

Full functionality and capability will be ensured in PL2. When transitioning between performance levels, the Supply Controller (SUPC) will provide a configurable smooth voltage scaling transition.

## 10.3. NVM User Row Mapping

The Non Volatile Memory (NVM) User Row contains calibration data that are automatically read at device power-on.

The NVM User Row can be read at address 0x00804000.

To write the NVM User Row refer to the documentation of the NVMCTRL - Non-Volatile Memory Controller.

**Note:** When writing to the User Row, the new values do not get loaded by the other peripherals on the device until a device Reset occurs.

Table 10-4. NVM User Row Mapping

| Bit Pos. | Name             | Usage                                                   | Factory<br>Setting | Related Peripheral<br>Register |

|----------|------------------|---------------------------------------------------------|--------------------|--------------------------------|

| 2:0      | BOOTPROT         | Used to select one of eight different bootloader sizes. | 0x7                | NVMCTRL                        |

| 3        | Reserved         | _                                                       | 0x1                | _                              |

| 6:4      | EEPROM           | Used to select one of eight different EEPROM sizes.     | 0x7                | NVMCTRL                        |

| 7        | Reserved         | _                                                       | 0x1                | _                              |

| 13:8     | BOD33 Level      | BOD33 threshold level at power-on.                      | 0x06               | SUPC.BOD33                     |

| 14       | BOD33 Disable    | BOD33 Disable at power-on.                              | 0x0                | SUPC.BOD33                     |

| 16:15    | BOD33 Action     | BOD33 Action at power-on.                               | 0x1                | SUPC.BOD33                     |

| 25:17    | Reserved         | Factory settings - do not change.                       | 0x08F              | -                              |

| 26       | WDT Enable       | WDT Enable at power-on.                                 | 0x0                | WDT.CTRLA                      |

| 27       | WDT Always-On    | WDT Always-On at power-on.                              | 0x0                | WDT.CTRLA                      |

| 31:28    | WDT Period       | WDT Period at power-on.                                 | 0xB                | WDT.CONFIG                     |

| 35:32    | WDT Window       | WDT Window mode time-out at power-on.                   | 0xB                | WDT.CONFIG                     |

| 39:36    | WDT EWOFFSET     | WDT Early Warning Interrupt Time Offset at power-on.    | 0xB                | WDT.EWCTRL                     |

| 40       | WDT WEN          | WDT Timer Window Mode Enable at power-on.               | 0x0                | WDT.CTRLA                      |

| 41       | BOD33 Hysteresis | BOD33 Hysteresis configuration at power-on.             | 0x0                | SUPC.BOD33                     |

| 47:42    | Reserved         | Factory settings - do not change.                       | 0x3E               | _                              |

| 63:48    | LOCK             | NVM Region Lock Bits.                                   | 0xFFFF             | NVMCTRL                        |

## 11.2. Nested Vector Interrupt Controller

#### 11.2.1. Overview

The Nested Vectored Interrupt Controller (NVIC) in the SAM L22 supports 32 interrupts with four different priority levels. For more details, refer to the Cortex-M0+ Technical Reference Manual (http://www.arm.com).

### 11.2.2. Interrupt Line Mapping

Each of the interrupt lines is connected to one peripheral instance, as shown in the table below. Each peripheral can have one or more interrupt flags, located in the peripheral's Interrupt Flag Status and Clear (INTFLAG) register.

An interrupt flag is set when the interrupt condition occurs. Each interrupt in the peripheral can be individually enabled by writing a '1' to the corresponding bit in the peripheral's Interrupt Enable Set (INTENSET) register, and disabled by writing '1' to the corresponding bit in the peripheral's Interrupt Enable Clear (INTENCLR) register.

An interrupt request is generated from the peripheral when the interrupt flag is set and the corresponding interrupt is enabled.

The interrupt requests for one peripheral are ORed together on system level, generating one interrupt request for each peripheral. An interrupt request will set the corresponding interrupt pending bit in the NVIC interrupt pending registers (SETPEND/CLRPEND bits in ISPR/ICPR).

For the NVIC to activate the interrupt, it must be enabled in the NVIC interrupt enable register (SETENA/ CLRENA bits in ISER/ICER). The NVIC interrupt priority registers IPR0-IPR7 provide a priority field for each interrupt.

Table 11-3. Interrupt Line Mapping

| Peripheral source                         | NVIC line |

|-------------------------------------------|-----------|

| EIC NMI – External Interrupt Controller   | NMI       |

| PM – Power Manager                        | 0         |

| MCLK - Main Clock                         |           |

| OSCCTRL - Oscillators Controller          |           |

| OSC32KCTRL - 32KHz Oscillators Controller |           |

| PAC - Peripheral Access Controller        |           |

| SUPC - Supply Controller                  |           |

| WDT – Watchdog Timer                      | 1         |

| RTC – Real Time Counter                   | 2         |

| EIC – External Interrupt Controller       | 3         |

| FREQM - Frequency Meter                   | 4         |

| USB - Universal Serial Bus                | 5         |

| NVMCTRL – Non-Volatile Memory Controller  | 6         |

| DMAC - Direct Memory Access Controller    | 7         |

| SRAM Port<br>Connection                                              | Port ID | Connection Type | QoS                       | default QoS |

|----------------------------------------------------------------------|---------|-----------------|---------------------------|-------------|

| DMAC - Direct<br>Memory Access<br>Controller - Fetch<br>Access       | 3, 4    | Direct          | IP-<br>QOSCTRL.FQOS       | 0x2         |

| DMAC - Direct<br>Memory Access<br>Controller - Write-<br>Back Access | 5, 6    | Direct          | IP-<br>QOSCTRL.WRBQ<br>OS | 0x2         |

| USB - Universal<br>Serial Bus                                        | 7       | Direct          | IP-QOSCTRL                | 0x3         |

| MTB - Micro Trace<br>Buffer                                          | 8       | Direct          | STATIC-3                  | 0x3         |

Note: 1. Using 32-bit access only.

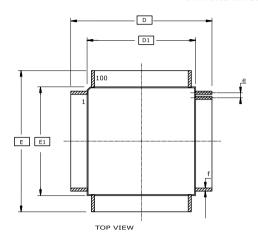

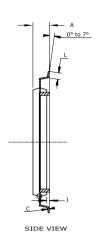

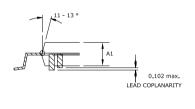

## 12.2. Package Drawings

## 12.2.1. 100 pin TQFP

DRAWINGS NOT SCALED

COMMON DIMENSIONS

(Unit of Measure = mm)

SYMBOL MIN NOM MAX NOTE

DETAIL VIEW

| А     |          |  | 1.20 |   |

|-------|----------|--|------|---|

| A1    | 0.95     |  | 1.05 |   |

| С     | 0.09     |  | 0.20 |   |

| D/E   | 16.00    |  |      |   |

| D1/E1 | 14.00    |  |      | 2 |

| J     | 0.05     |  | 0.15 |   |

| L     | 0.45     |  | 0.75 |   |

| e     | 0.50 BSC |  |      |   |

| f     | 0.17     |  | 0.27 |   |

| n     | 100      |  |      |   |

|       |          |  |      |   |

Notes: 1. This drawing is for general information only. Refer to JEDEC Drawing MS-026, Variation AED.

2. Dimensions D1 and E1 do not include mold protrusion. Allowable protrusion is 0.25mm per side.

Dimensions D1 and E1 are maximum plastic body size dimensions including mold mismatch.

3. Lead coplanarity is 0.10mm maximum.

#### Table 12-2. Device and Package Maximum Weight

| 520 | mg |

|-----|----|

|-----|----|

## **Table 12-3. Package Characteristics**

| Moisture Sensitivity Level | MSL3 |

|----------------------------|------|

## Table 12-4. Package Reference

| JEDEC Drawing Reference | MS-026, variant AED |

|-------------------------|---------------------|

| JESD97 Classification   | e3                  |

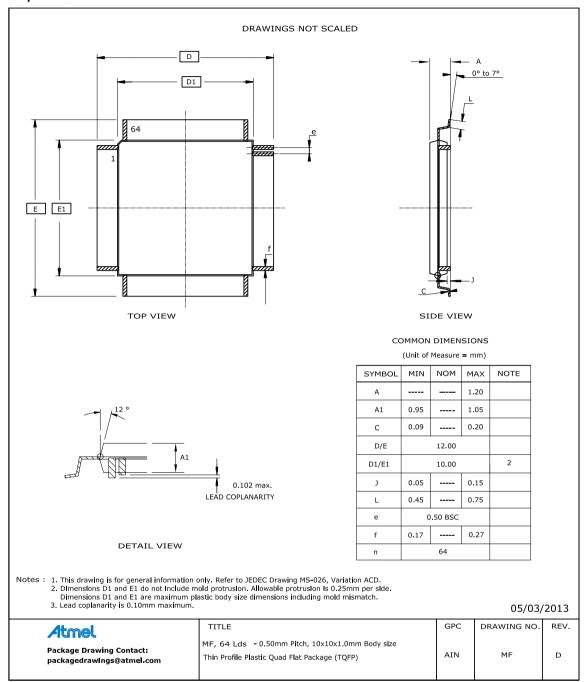

## 12.2.2. 64 pin TQFP

Table 12-5. Device and Package Maximum Weight

| 300   mg | 300 | mg |

|----------|-----|----|

|----------|-----|----|

### **Table 12-6. Package Characteristics**

| Moisture Sensitivity Level | MSL3 |

|----------------------------|------|

|----------------------------|------|

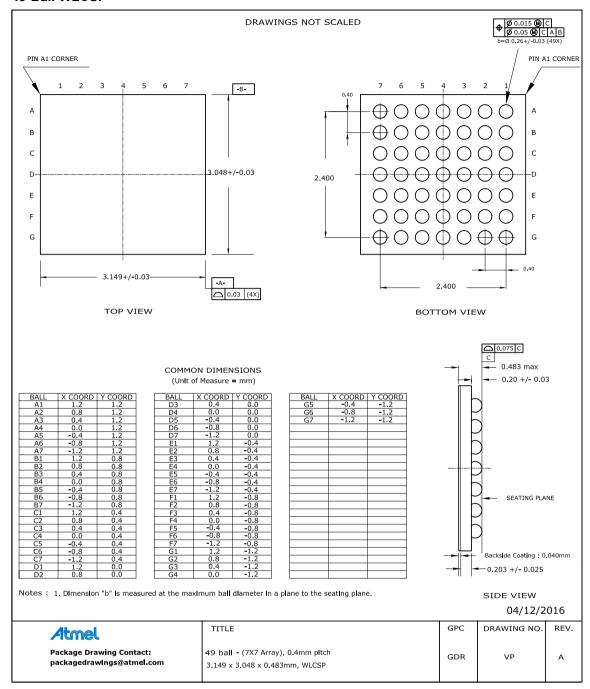

#### 12.2.4. 49-Ball WLCSP

Table 12-11. Device and Package Maximum Weight

| 8.45 | mg |

|------|----|

|      |    |

### Table 12-12. Package Characteristics

| Moisture Sensitivity Level | MSL1 |

|----------------------------|------|

| ·                          |      |

### Table 12-13. Package Reference

| JEDEC Drawing Reference | N/A |

|-------------------------|-----|

| JESD97 Classification   | E1  |

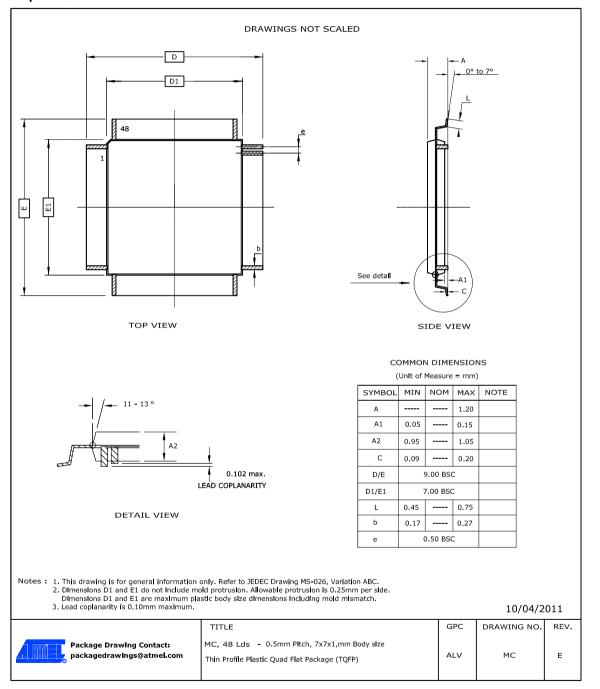

## 12.2.5. 48 pin TQFP

Table 12-14. Device and Package Maximum Weight

| 140 | mg |  |

|-----|----|--|

|     |    |  |

### **Table 12-15. Package Characteristics**

| Moisture Sensitivity Level | MSL3 |

|----------------------------|------|

| ,                          |      |

Table 12-16. Package Reference

| JEDEC Drawing Reference | MS-026 |

|-------------------------|--------|

| JESD97 Classification   | E3     |

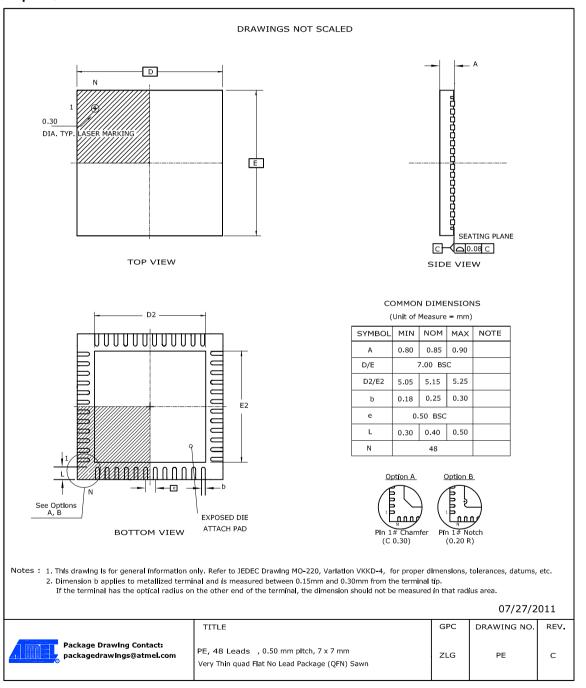

### 12.2.6. 48 pin QFN

**Note:** The exposed die attach pad is not connected electrically inside the device.

## Table 12-17. Device and Package Maximum Weight

| 140  | mg |

|------|----|

| 1.10 | 9  |

## **Table 12-18. Package Characteristics**

| Moisture Sensitivity Level | MSL3 |

|----------------------------|------|

| •                          |      |

### Table 12-19. Package Reference

| JEDEC Drawing Reference | MO-220 |

|-------------------------|--------|

| JESD97 Classification   | E3     |

## 12.3. Soldering Profile

The following table gives the recommended soldering profile from J-STD-20.

### Table 12-20.

| Profile Feature                            | Green Package  |

|--------------------------------------------|----------------|

| Average Ramp-up Rate (217°C to peak)       | 3°C/s max.     |

| Preheat Temperature 175°C ±25°C            | 150-200°C      |

| Time Maintained Above 217°C                | 60-150s        |

| Time within 5°C of Actual Peak Temperature | 30s            |

| Peak Temperature Range                     | 260°C          |

| Ramp-down Rate                             | 6°C/s max.     |

| Time 25°C to Peak Temperature              | 8 minutes max. |

A maximum of three reflow passes is allowed per component.

# Atmet | Enabling Unlimited Possibilities

**Atmel Corporation**

1600 Technology Drive, San Jose, CA 95110 USA

T: (+1)(408) 441.0311

F: (+1)(408) 436.4200

www.atmel.com

© 2016 Atmel Corporation. / Rev.: Atmel-42402E-SAM L22G / L22J / L22N Summary Datasheet Summary-07/2016

Atmel®, Atmel logo and combinations thereof, Enabling Unlimited Possibilities®, and others are registered trademarks or trademarks of Atmel Corporation in U.S. and other countries. ARM®, ARM Connected® logo, and others are the registered trademarks or trademarks of ARM Ltd. Other terms and product names may be trademarks of others.

DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death ("Safety-Critical Applications") without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems. Atmel products are not designed nor intended for use in military or aerospace applications or environments unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as automotive-grade.

Atmel®, Atmel logo and combinations thereof, Enabling Unlimited Possibilities®, and others are registered trademarks or trademarks of Atmel Corporation in U.S. and other countries. ARM®, ARM Connected® logo, and others are the registered trademarks or trademarks of ARM Ltd. Other terms and product names may be trademarks of others.

DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death ("Safety-Critical Applications") without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems. Atmel products are not designed nor intended for use in military or aerospace applications or environments unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as automotive-grade.