Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | C800                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, PWM, WDT                                           |

| Number of I/O              | 18                                                                         |

| Program Memory Size        | 8KB (8K x 8)                                                               |

| Program Memory Type        | RAM                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                  |

| Data Converters            | A/D 5x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 38-TFSOP (0.173", 4.40mm Width)                                            |

| Supplier Device Package    | PG-TSSOP-38                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-c868-1sr-ba |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# C868 8-Bit Single-Chip Microcontroller

## Microcontrollers

Never stop thinking.

- One 8-bit and one 5 bits general purpose push-pull I/O ports

- Enhanced sink current of 10 mA on Port 1/3 (total max current of 43 mA @ 100°C)

- Three 16-bit timers/counters –Timer 0 / 1 (C501 compatible)

- -Timer 2 (up/down counter feature)

- -Timer 1 or 2 can be used for serial baudrate generator

- Capture/compare unit for PWM signal generation –3-channel, 16-bit capture/compare unit –1-channel, 16-bit compare unit

- Full duplex serial interface (UART)

- 5 channel 8-bit A/D Converter

Start of conversion can be synchronized to capture/compare timer 12/13.

- 13 interrupt vectors with four priority levels

- Programmable 16-bit Watchdog Timer

- Brown out detection

- Power Saving Modes

- -Slow-down mode

- -Idle mode (can be combined with slow-down mode)\_

- -Power-down mode with wake up capability through INT0 or RxD pins.

- Single power supply of 3.3V, internal voltage regulator for core voltage of 2.5V.

- P-DSO-28-1, P-TSSOP-38-1 packages

- Temperature ranges:

SAF-C868-1RR BA, SAF-C868-1SR BA, SAF-C868-1RG BA, SAF-C868-1SG BA, SAF-C868A-1RR BA, SAF-C868A-1SR BA, SAF-C868A-1RG BA, SAF-C868A-1SG BA, SAF-C868P-1SR BA, SAF-C868P-1SG BA  $T_A = -40$  to 85 °C SAK-C868-1RR BA, SAK-C868-1SR BA, SAK-C868-1RG BA, SAK-C868-1SG BA, SAK-C868A-1RR BA, SAK-C868A-1SR BA, SAK-C868A-1RG BA, SAK-C868A-1SG BA, SAK-C868A-1RG BA, SAK-C868A-1SG BA, SAK-C868A-1RG BA, SAK-C868A-1SG BA, SAK-C868A-1SR BA, SAK-C868A-1SG BA, SAK-C868A-1RG BA, SAK-C868A-1SG BA, SAK-C868A-1SR BA, SAK-C868A-1SG BA, SAK-C868A-1SR BA, SAK-C868A-1SG BA, SAK-C868A-1RG BA, SAK-C868A-1SG BA, SAK-C868A-1SR BA, SAK-C868A-1SG BA, SAK-C868A-1SR BA, SAK-C868A-1SG BA, SAK-C868A-1SR BA, SAK-C868A-1SG BA,

BA, SAK-C868P-1SR BA, SAK-C868P-1SG BA,  $T_A = -40$  to 125 °C

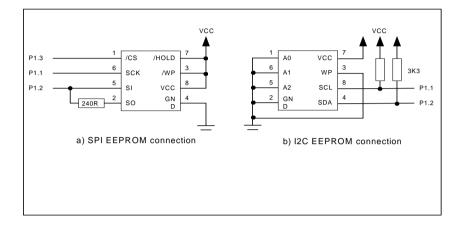

#### Figure 9 EEPROM connections for a) SPI and b) I2C

C868

| Block                  | Symbol                                                                                               | Name                                                                                                                                                                     | Add-<br>ress                                                                                                                 | Contents<br>after<br>Reset                                                                                                              |

|------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| A/D-<br>Con-<br>verter | ADCON0<br>ADCON1<br>ADDATH                                                                           | A/D Converter Control Register 0<br>A/D Converter Control Register 1<br>A/D Converter Data Register                                                                      | <b>D8<sub>H</sub></b> <sup>1)</sup><br>D9 <sub>H</sub><br>DB <sub>H</sub>                                                    | <b>00<sub>H</sub></b><br>XX000000 <sub>B<sup>2)</sup></sub><br>00 <sub>H</sub>                                                          |

| Ports                  | P1 <sup>4)</sup><br>P1DIR <sup>3)</sup><br>P3 <sup>4)</sup><br>P3DIR <sup>3)</sup><br>P3ALT<br>P1ALT | Port 1 Register<br>Port 1 Direction Register<br>Port 3 Register<br>Port 3 Direction Register<br>Port 3 Alternate Function Register<br>Port 1 Alternate Function Register | 90H <sup>1)</sup><br>90H <sup>1)</sup><br>B0H <sup>1)</sup><br>B0H <sup>1)</sup><br>B1 <sub>H</sub><br>B4 <sub>H</sub>       | FF <sub>H</sub><br>FF <sub>H</sub><br>FF <sub>H</sub><br>00 <sub>H</sub><br>XXX00X00 <sub>B<sup>2</sup></sub>                           |

| Watch<br>dog           | WDTCON<br>WDTREL<br>WDTL<br>WDTH                                                                     | Watchdog Timer Control Register<br>Watchdog Timer Reload Register<br>Watchdog Timer, Low Byte<br>Watchdog Timer, High Byte                                               | A2 <sub>H</sub><br>A3 <sub>H</sub><br>B2 <sub>H</sub><br>B3 <sub>H</sub>                                                     | XXXXXX00 <sub>B<sup>2)</sup><br/>00<sub>H</sub><br/>00<sub>H</sub><br/>00<sub>H</sub></sub>                                             |

| Timer<br>2             | T2CON<br>T2MOD<br>RC2H<br>RC2L<br>T2H<br>T2L                                                         | Timer 2 Control Register<br>Timer 2 Mode Register<br>Timer 2 Reload/Capture, High Byte<br>Timer 2 Reload/Capture, Low Byte<br>Timer 2, High Byte<br>Timer 2, Low Byte    | C8 <sub>H</sub> <sup>1)</sup><br>C9 <sub>H</sub><br>CB <sub>H</sub><br>CA <sub>H</sub><br>CD <sub>H</sub><br>CC <sub>H</sub> | <b>00<sub>H</sub></b><br>XXXXXX0 <sub>B</sub> <sup>2)</sup><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub> |

#### Table 6 Special Function Registers - Functional Blocks (cont'd)

1) Bit-addressable special function registers

2) "X" means that the value is undefined and the location is reserved

3) Register is mapped by bit RMAP in SYSCON0.4=1

4) Register is mapped by bit RMAP in SYSCON0.4=0

| Block | Symbol                 | Name                                    | Add-<br>ress    | Contents<br>after<br>Reset |

|-------|------------------------|-----------------------------------------|-----------------|----------------------------|

| Cap-  | ISSL <sup>3)</sup>     | Cap/Com Int Status Set Reg, Low Byte    | BC <sub>H</sub> | 00 <sub>H</sub>            |

| ture/ | ISSH <sup>3)</sup>     | Cap/Com Int Status Set Reg, High Byte   | BD <sub>H</sub> | 00 <sub>H</sub>            |

| Com-  | ISRL <sup>4)</sup>     | Cap/Com Int Status Reset Reg, Low Byte  | BC <sub>H</sub> | 00 <sub>H</sub>            |

| pare  | ISRH <sup>4)</sup>     | Cap/Com Int Status Reset Reg, High Byte | BD <sub>H</sub> | 00 <sub>H</sub>            |

| Unit  | INPL <sup>3)</sup>     | Cap/Com Int Node Ptr Reg, Low Byte      | BE <sub>H</sub> | 40 <sub>H</sub>            |

|       | INPH <sup>3)</sup>     | Cap/Com Int Node Ptr Reg, High Byte     | BF <sub>H</sub> | 39 <sub>H</sub>            |

|       | IENL <sup>4)</sup>     | Cap/Com Interrupt Register, Low Byte    | BE <sub>H</sub> | 00 <sub>H</sub>            |

|       | IENH <sup>4)</sup>     | Cap/Com Interrupt Register, High Byte   | BF <sub>H</sub> | 00 <sub>H</sub>            |

|       | CC60SRL                | Cap/Com Channel 0 Shadow, Low Byte      | FA <sub>H</sub> | 00 <sub>H</sub>            |

|       | CC60SRH                | Cap/Com Channel 0 Shadow, High Byte     | FB <sub>H</sub> | 00 <sub>H</sub>            |

|       | CC61SRL                | Cap/Com Channel 1 Shadow, Low Byte      | FC <sub>H</sub> | 00 <sub>H</sub>            |

|       | CC61SRH                | Cap/Com Channel 1 Shadow, High Byte     | FD <sub>H</sub> | 00 <sub>H</sub>            |

|       | CC62SRL                | Cap/Com Channel 2 Shadow, Low Byte      | FE <sub>H</sub> | 00 <sub>H</sub>            |

|       | CC62SRH                | Cap/Com Channel 2 Shadow, High Byte     | FF <sub>H</sub> | 00 <sub>H</sub>            |

|       | CC63SRL                | T13 Compare Shadow Reg, Low Byte        | B6 <sub>H</sub> | 00 <sub>H</sub>            |

|       | CC63SRH                | T13 Compare Shadow Reg, High Byte       | B7 <sub>H</sub> | 00 <sub>H</sub>            |

|       | MODCTRL <sup>3)</sup>  | Modulation Control Register, Low Byte   | D6 <sub>H</sub> | 00 <sub>H</sub>            |

|       | MODCTRH <sup>3)</sup>  | Modulation Control Register, High Byte  | D7 <sub>H</sub> | 00 <sub>H</sub>            |

|       | TRPCTRL                | Trap Control Register, Low Byte         | CEH             | 00 <sub>H</sub>            |

|       | TRPCTRH                | Trap Control Register, High Byte        | CF <sub>H</sub> | 00 <sub>H</sub>            |

|       | PSLRL                  | Passive State Level Register, Low Byte  | A6 <sub>H</sub> | 00 <sub>H</sub>            |

|       | MCMOUTL <sup>3)</sup>  | MCM Output Register, Low Byte           | DCH             | 00 <sub>H</sub>            |

|       | MCMOUTH <sup>3)</sup>  | MCM Output Register, High Byte          | $DD_H$          | 00 <sub>H</sub>            |

|       | MCMOUTSL <sup>4)</sup> | MCM Output Shadow Register, Low Byte    | DCH             | 00 <sub>H</sub>            |

|       | MCMOUTSH <sup>4)</sup> | MCM Output Shadow Register, High Byte   | $DD_H$          | 00 <sub>H</sub>            |

|       | MCMCTRLL <sup>4)</sup> | MCM Control Register, Low Byte          | D6 <sub>H</sub> | 00 <sub>H</sub>            |

|       | T12MSELL               | T12 Cap/Com Mode Sel Reg, Low Byte      | F6 <sub>H</sub> | 00 <sub>H</sub>            |

|       | T12MSELH               | T12 Cap/Com Mode Sel Reg, High Byte     | F7 <sub>H</sub> | 00 <sub>H</sub>            |

#### Table 6 Special Function Registers - Functional Blocks (cont'd)

1) Bit-addressable special function registers

3) Register is mapped by bit RMAP in SYSCON0.4=1

4) Register is mapped by bit RMAP in SYSCON0.4=0

| Table 7  | Contonts of the SERs  | . SFRs in numeric order of their addresses |

|----------|-----------------------|--------------------------------------------|

| I able I | Contents of the SERS, |                                            |

| Addr               | Reg-<br>ister | Content<br>after<br>Reset <sup>1)</sup> | Bit 7       | Bit 6        | Bit 5        | Bit 4       | Bit 3        | Bit 2       | Bit 1        | Bit 0       |

|--------------------|---------------|-----------------------------------------|-------------|--------------|--------------|-------------|--------------|-------------|--------------|-------------|

| E6 <sub>H</sub>    | T12DT<br>CL   | 00 <sub>H</sub>                         |             | -            | DTM5         | DTM4        | DTM3         | DTM2        | DTM1         | DTM0        |

| E7 <sub>H</sub>    | T12DT<br>CH   | 00 <sub>H</sub>                         | -           | DTR2         | DTR1         | DTR0        | _            | DTE2        | DTE1         | DTE0        |

| E8 <sub>H</sub>    | PMCO<br>N1    | XXXX<br>X000 <sub>B</sub>               | -           | -            | -            | -           | -            | CCUDI<br>S  | T2DIS        | ADCDI<br>S  |

| EA <sub>H</sub>    | CMPM<br>ODIFL | 00 <sub>H</sub>                         | -           | MCC6<br>3S   | _            | -           | -            | MCC6<br>2S  | MCC6<br>1S   | MCC6<br>0S  |

| EB <sub>H</sub>    | CMPM<br>ODIFH | 00 <sub>H</sub>                         | -           | MCC6<br>3R   | -            | -           | _            | MCC6<br>2R  | MCC6<br>1R   | MCC6<br>0R  |

| ECH                | T12L          | 00 <sub>H</sub>                         | .7          | .6           | .5           | .4          | .3           | .2          | .1           | .0          |

| ED <sub>H</sub>    | T12H          | 00 <sub>H</sub>                         | .7          | .6           | .5           | .4          | .3           | .2          | .1           | .0          |

| EEH                | T13L          | 00 <sub>H</sub>                         | .7          | .6           | .5           | .4          | .3           | .2          | .1           | .0          |

| EF <sub>H</sub>    | T13H          | 00 <sub>H</sub>                         | .7          | .6           | .5           | .4          | .3           | .2          | .1           | .0          |

| F0 <sub>H</sub>    | В             | 00 <sub>H</sub>                         | .7          | .6           | .5           | .4          | .3           | .2          | .1           | .0          |

| F2 <sub>H</sub> ²) | TCTR<br>4L    | 00 <sub>H</sub>                         | T12ST<br>D  | T12ST<br>R   | _            | _           | DTRE<br>S    | T12RE<br>S  | T12RS        | T12RR       |

| F2 <sub>H</sub> 3) | TCTR<br>2L    | 00 <sub>H</sub>                         | -           | T13TE<br>D1  | T13TE<br>D0  | T13TE<br>C2 | T13TE<br>C1  | T13TE<br>C0 | T13SS<br>C   | T12SS<br>C  |

| F3 <sub>H</sub> ²) | TCTR<br>4H    | 00 <sub>H</sub>                         | T13ST<br>D  | T13ST<br>R   | -            | -           | -            | T13RE<br>S  | T13RS        | T13RR       |

| F4 <sub>H</sub>    | CMPS<br>TATL  | 00 <sub>H</sub>                         | -           | CC63S<br>T   | -            | -           | -            | CC62S<br>T  | CC61S<br>T   | CC60S<br>T  |

| F5 <sub>H</sub>    | CMPS<br>TATH  | 00 <sub>H</sub>                         | T13IM       | COUT<br>63PS | COUT<br>62PS | CC62P<br>S  | COUT<br>61PS | CC61P<br>S  | COUT<br>60PS | CC60P<br>S  |

| F6 <sub>H</sub>    | T12M<br>SELL  | 00 <sub>H</sub>                         | MSEL<br>613 | MSEL<br>612  | MSEL<br>611  | MSEL<br>610 | MSEL<br>603  | MSEL<br>602 | MSEL<br>601  | MSEL<br>600 |

| F7 <sub>H</sub>    | T12M<br>SELH  | 00 <sub>H</sub>                         | -           | -            | -            | -           | MSEL<br>623  | MSEL<br>622 | MSEL<br>621  | MSEL<br>620 |

1) X means that the value is undefined and the location is reserved

2) This register is mapped with RMAP (SYSCON0.4)=0

3) This register is mapped with RMAP (SYSCON0.4)=1

Shaded registers are bit-addressable special function registers

#### Timer/Counter 2 with Compare/Capture/Capture

Timer 2 is a 16-bit timer/counter with an up/down count feature. It has three operating modes:

- 16-bit auto-reload mode (up or down counting)

- 16-bit capture mode

- Baudrate generator

#### Table 9 Timer/Counter 2 Operating Modes

| Mode                  | T2CO               | Ν                 |     | T2MOD | T2CON | T2EX         | Remarks                                        | Syste<br>Cloci         |                                |

|-----------------------|--------------------|-------------------|-----|-------|-------|--------------|------------------------------------------------|------------------------|--------------------------------|

|                       | RCLK<br>or<br>TCLK | <u>CP/</u><br>RL2 | TR2 | DCEN  | EXEN  |              |                                                | Inte-<br>rnal          | T2                             |

| 16-bit<br>Auto-       | 0                  | 0                 | 1   | 0     | 0     | Х            | reload upon<br>overflow                        | <i>f</i> sys<br>/12    | max<br><i>f</i> sys            |

| reload                | 0                  | 0                 | х   | 0     | 1     | $\downarrow$ | reload trigger<br>(falling edge)               |                        | /24                            |

|                       | 0                  | 0                 | 1   | 1     | Х     | 0            | down counting                                  |                        |                                |

|                       | 0                  | 0                 | 1   | 1     | Х     | 1            | up counting                                    |                        |                                |

| 16-bit<br>Capture     | 0                  | 1                 | 1   | Х     | 0     | Х            | 16-bit Timer/<br>Counter (only<br>up-counting) | <i>f</i> sys<br>/12    | max<br><sup>ƒ</sup> sys<br>/24 |

|                       | 0                  | 1                 | 1   | x     | 1     | $\downarrow$ | capture<br>T2H,T2L-><br>RC2H,RC2L              |                        |                                |

| Baudrate<br>Generator | 1                  | Х                 | 1   | Х     | 0     | Х            | no overflow<br>interrupt<br>request(TF2)       | f <sub>SYS</sub><br>/2 | -                              |

|                       | 1                  | х                 | 1   | Х     | 1     | $\downarrow$ | extra external<br>interrupt<br>("Timer 2")     |                        |                                |

| off                   | Х                  | Х                 | 0   | Х     | Х     | Х            | Timer 2 stops                                  | -                      | -                              |

Note: denotes a falling edge

**Switching Examples**

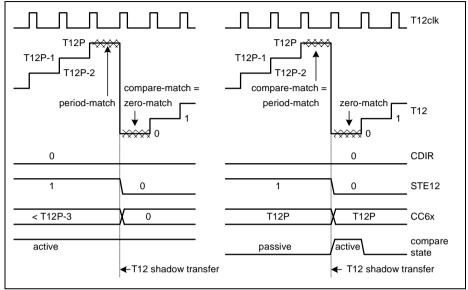

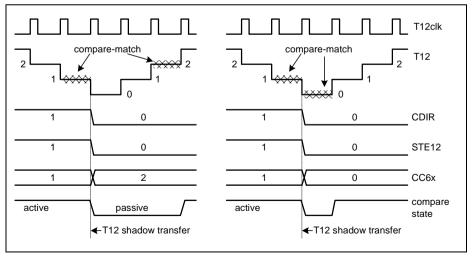

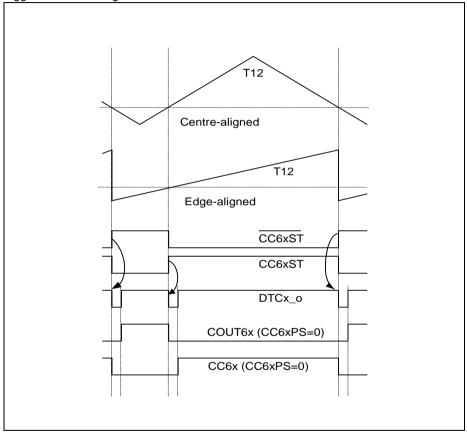

Figure 16 Edge-aligned mode with duty cycles near 100% and near 0%. Applicable to T13 as well.

#### **Dead-time Generation**

The dead-time generation logic is built in a similar way for all three channels of T12. Each of the three channels works independently with its own dead-time counter and the trigger and enable signals.

Figure 18 Dead-time generation for centre and edge aligned modes

#### Capture Mode

In capture mode the bits CC6xST indicate the occurrence of the selected capture event according to the bit fields MSEL6x. A rising and/or a falling edge on the pins CC6x can be selected as capture event, that is used to transfer the contents of timer T12 to the CC6xR and CC6xSR registers. In order to work in capture mode, the capture pins have to be configured as inputs.

#### Hall Sensor Mode

In **Brushless-DC motors** the next multi-channel state values depend on the pattern of the Hall inputs. There is a strong correlation between the **Hall pattern** (CURH) and the **modulation pattern** (MCMP). Because of different machine types the modulation pattern for driving the motor can be different. Therefore it is wishful to have a wide flexibility in defining the correlation between the Hall pattern and the corresponding modulation pattern. The CCU6 offers this by having a register which contains the actual Hall pattern (CURHS), the next expected Hall pattern (EXPHS) and its output pattern (MCMPS). At every correct Hall event (CHE, see figure *Hall Event Actions*) a new Hall pattern with its corresponding output pattern can be loaded (from a predefined table) by software into the register MCMOUTS. Loading this shadow register can also be done by a write action on MCMOUTS with bit STRHP = '1'

The **sampling** of the Hall pattern (on CCPOSx) is done with the T12 clock. By using the dead-time counter DTC0 (mode MSEL6x= '1000') a hardware **noise filter** can be implemented to suppress spikes on the Hall inputs due to high di/dt in rugged inverter environment. In case of a Hall event the DTC0 is reloaded and starts counting. When the counter value of one is reached, the CCPOSx inputs are sampled (without noise and spikes) and are compared to the current Hall pattern (CURH) and to the expected Hall pattern (EXPH). If the sampled pattern equals to the current pattern the edge on CCPOSx was due to a noise spike and no action will be triggered (implicit noise filter). If the sampled pattern equals to the next expected pattern the edge on CCPOSx was a correct Hall event, the bit CHE is set which causes an interrupt and the resets T12 (for speed measurement, see description mode '1000' below).

This correct Hall event can be used as a transfer request event for register MCMOUTS. The transfer from MCMOUTS to MCMOUT transfers the new CURH-pattern as well as the next EXPH-pattern. In case of the sampled Hall inputs were neither the current nor the expected Hall pattern, the bit WHE (wrong Hall event) is set which also can cause an interrupt and sets the IDLE mode clearing MCMP (modulation outputs are inactive). To restart from IDLE the transfer request of MCMOUTS have to be initiated by software (bit STRHP and bitfields SWSEL/SWSYN).

#### A/D Converter

The C868 includes a high performance / high speed 8-bit A/D-Converter (ADC) with 5 analog input channels. It operates with a successive approximation technique and uses self calibration mechanisms for reduction and compensation of offset and linearity errors. The A/D converter provides the following features:

- 5 multiplexed input channels, which can also be used as digital inputs

- 8-bit resolution with TUE of +/- 2 LSB8.

- Single or continuous conversion mode

- Start of conversion by software and hardware

- Interrupt request generation after each conversion

- Using successive approximation conversion technique via a capacitor array

- Powerdown in normal, idle and slow-down modes

The ADC supports two conversion modes - single and continuous conversions. For each mode, there are two ways in which conversion can be started - by software and by the T13PM signal from the CCU module.

Writing a '0' to bit CCU\_ADEX select conversion control by ADST. Writing a '1' to bit field ADST starts conversion on the channel that is specified by ADCH. In single conversion mode, bit field ADM is cleared to '0'. This is the default mode selected after hardware reset. When a conversion is started, the channel specified is sampled. The busy flag ADBSY is set and ADST is cleared. When the conversion is completed, the interrupt request signal ADCIRQ is asserted possitively for 2 clocks and the 8-bit result together with the number of the converted channel is transferred to the result register ADDATH.

In continuous conversion mode, bit field ADM is set to '1'. In this mode, the ADC repeatedly converts the channel specified by ADCH. Bit ADST is cleared at the beginning of the first conversion. The busy flag ADBSY is asserted until the last conversion is completed. At the end of each conversion, the interrupt request signal ADCIRQ will be activated. To stop conversion, ADM has to be reset by software. If the channel number ADCH is changed while continuous conversion is in progress, the new channel specified will be sampled in the conversions that follow.

A new request to start conversion will be allowed only after the completion of any conversion that is in progress.

Writing a '1' to bit CCU\_ADEX select conversion control by T13PM trigger signal from the CCU module.

Note: Caution must be taken when changing conversion start source. To change conversion source from software to hardware trigger, it is best to let remaining software conversion to complete before changing. To change conversion source from hardware trigger to software, it is best to change source first, let any

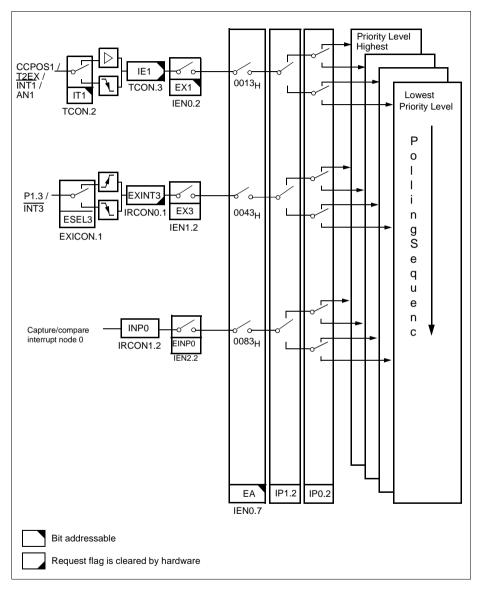

#### Figure 25 Interrupt Structure, Overview Part 2

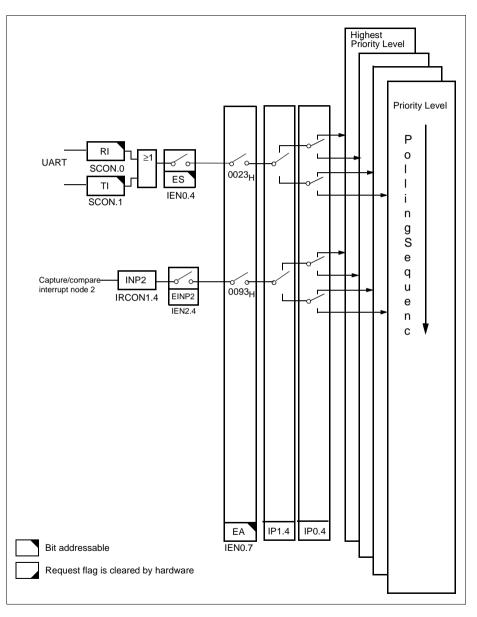

#### Figure 27 Interrupt Structure, Overview Part 4

| Mode                 | Entering                                                                                                                                                                                        | Leaving by                                                                                                                                                                                                                                 | Remarks                                                                                                                                                                         |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ldle<br>Mode         | ORL PCON,#01 <sub>H</sub>                                                                                                                                                                       | Occurance of any<br>enabled interrupt                                                                                                                                                                                                      | CPU clock is stopped;<br>CPU maintains its                                                                                                                                      |

|                      |                                                                                                                                                                                                 | Hardware Reset                                                                                                                                                                                                                             | data;<br>peripheral units are<br>active (if enabled) and<br>provided with clock                                                                                                 |

| Slow<br>Down<br>Mode | In normal mode:<br>ORL PCON,#10 <sub>H</sub>                                                                                                                                                    | ANL PCON,#0EF <sub>H</sub><br>or Hardware Reset                                                                                                                                                                                            | Internal clock rate is<br>reduced to a<br>configurable factor of<br>$1/_2$ to $1/_{32}$ of the<br>system clock rate                                                             |

|                      | With idle mode:<br>ORL PCON,#11 <sub>H</sub>                                                                                                                                                    | Occurance of any<br>enabled interrupt to<br>exit idle mode and<br>the instruction<br>ANL PCON,#0EF <sub>H</sub><br>to terminate slow<br>down mode                                                                                          | CPU clock is stopped;<br>CPU maintains all its<br>data;<br>Peripheral units are<br>active (if enabled) and<br>provided with a<br>configurable factor of<br>1/2 to $1/32$ of the |

|                      |                                                                                                                                                                                                 | Hardware Reset                                                                                                                                                                                                                             | system clock rate                                                                                                                                                               |

| Software<br>Power    | With external wake-up                                                                                                                                                                           | Hardware Reset                                                                                                                                                                                                                             | Oscillator is stopped;                                                                                                                                                          |

| Down<br>mode         | capability from power down<br>enabled<br>ORL PMCON0,#01 <sub>H</sub><br>(to wake-up via pin INT0)<br>or<br>ORL PMCON0,#03 <sub>H</sub><br>(to wake-up via pin RxD)<br>ORL PCON,#02 <sub>H</sub> | When $\overline{INT0}$ or $RxD$<br>goes low for at least<br>10 $\mu$ s (latch phase).<br>But it is desired that<br>the corresponding<br>pin must be held at<br>high level during the<br>power down mode<br>entry and up to the<br>wake-up. | Contents of on-chip<br>RAM and SFR's are<br>maintained                                                                                                                          |

|                      | With external wake-up<br>capability from power down<br>disabled<br>ORL PCON,#02 <sub>H</sub>                                                                                                    | Hardware Reset                                                                                                                                                                                                                             |                                                                                                                                                                                 |

#### Table 15 Power Saving Modes Overview

#### **Operating Conditions**

The following operating conditions must not be exceeded in order to ensure correct operation of the C868. All parameters specified in the following sections refer to these operating conditions, unless otherwise noticed.

#### **Operating Condition Parameters**

| Parameter                                                                               | Symbol                    | Limit                  | Values                 | Unit | Notes                                         |  |

|-----------------------------------------------------------------------------------------|---------------------------|------------------------|------------------------|------|-----------------------------------------------|--|

|                                                                                         |                           | min.                   | max.                   |      |                                               |  |

| Digital supply voltage                                                                  | V <sub>DDP</sub>          | 3.0                    | 3.6                    | V    | Active mode,<br>$f_{SYSmax} = 40 \text{ MHz}$ |  |

|                                                                                         |                           | tbd                    | 3.6                    | V    | PowerDown<br>mode <sup>1)</sup>               |  |

| Digital ground voltages                                                                 | $V_{\rm SSC,}V_{\rm SSP}$ |                        | 0                      | V    | -                                             |  |

| Ambient temperature                                                                     | T <sub>A</sub>            | -40                    | 85                     | °C   | SAF-C868                                      |  |

|                                                                                         |                           | -40                    | 125                    | °C   | SAK-C868                                      |  |

| Analog reference voltage                                                                | V <sub>AREF</sub>         | 3.0V                   | V <sub>DDP</sub> + 0.1 | V    | -                                             |  |

| Analog ground voltage                                                                   | V <sub>AGND</sub>         | V <sub>SSP</sub> - 0.1 | V <sub>SSP</sub> + 0.1 | V    | -                                             |  |

| Analog input voltage                                                                    | V <sub>AIN</sub>          | V <sub>AGND</sub>      | V <sub>AREF</sub>      | V    | -                                             |  |

| External Clock                                                                          | fosc                      | 6.67                   | 10.67                  | MHz  | -                                             |  |

| Input current on any<br>pin during overload<br>condition except int/<br>analog and XTAL | I <sub>OV0</sub>          | -5                     | 5                      | mA   | _2)3)                                         |  |

| int/analog pin                                                                          | I <sub>OV1</sub>          | -2                     | 5                      | mA   | _3)4)                                         |  |

| XTAL pin                                                                                | I <sub>OV2</sub>          | -5                     | 5                      | mA   | _3)5)                                         |  |

| Absolute sum of all input currents during overload condition                            | ΣI <sub>OV</sub>          | -                      | 20                     | mA   | _3)                                           |  |

#### Notes:

<sup>1)</sup> Oscillator or external clock disabled.

<sup>&</sup>lt;sup>2)</sup> Overload conditions under operating conditions occur if the voltage on the respective pin exceeds the specified operating range (i.e. V<sub>OV</sub> > V<sub>DDP</sub> +0.5V or V<sub>OV</sub> < V<sub>SSP</sub> -0.5V). The absolute sum of input currents on all port pins may not exceed 20mA. The suply voltages V<sub>DDP</sub> and V<sub>SSP</sub> must remain within the specified limits.

<sup>&</sup>lt;sup>3)</sup> Not 100% tested, but guaranteed by design characterization.

#### **DC Characteristics**

(Operating Conditions apply)

| Parameter                                                                  | Symbol                                          | Limit                                                             | Values                                                                  | Unit        | <b>Test Condition</b>                                 |

|----------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------|-------------|-------------------------------------------------------|

|                                                                            |                                                 | min.                                                              | max.                                                                    |             |                                                       |

| Input low voltages<br>all except XTAL2, int/analog<br>int/analog<br>XTAL2  | $V_{\rm IL0}$<br>$V_{\rm IL1}$<br>$V_{\rm IL2}$ | -0.5<br>-0.5<br>-0.5                                              | 0.3V <sub>DDP</sub><br>0.3V <sub>DDC</sub><br>0.1V <sub>DDC</sub>       | V<br>V<br>V | _1)                                                   |

| Input high voltages<br>all except XTAL2, int/analog<br>int/analog<br>XTAL2 | $V_{\rm IH0}$<br>$V_{\rm IH1}$<br>$V_{\rm IH2}$ | 0.7V <sub>DDP</sub><br>0.7V <sub>DDC</sub><br>0.7V <sub>DDC</sub> | V <sub>DDP</sub> +0.5<br>V <sub>DDP</sub> +0.5<br>V <sub>DDC</sub> +0.5 | V<br>V<br>V | _                                                     |

| Output low voltage                                                         | V <sub>OL</sub>                                 | -                                                                 | 0.45                                                                    | V           | SAF-C868<br>I <sub>OL</sub> =10mA                     |

|                                                                            |                                                 | -                                                                 | 0.55                                                                    | V           | SAK-C868<br>I <sub>OL</sub> =10mA                     |

| Output high voltage                                                        | V <sub>OH</sub>                                 | 2.4                                                               | -                                                                       | V           | I <sub>OH</sub> =10mA                                 |

| Input leakage current (all except int/analog)                              | I <sub>LIO</sub>                                | -                                                                 | ±0.5                                                                    | uA          | 0.4 <v<sub>IN<v<sub>DDP</v<sub></v<sub>               |

| Input leakage current (int/<br>analog)                                     | I <sub>LI1</sub>                                | -                                                                 | ±0.5                                                                    | uA          | 0.4 <v<sub>IN<v<sub>DDP<sup>2)</sup></v<sub></v<sub>  |

| Input low current (XTAL2)                                                  | I <sub>LI2</sub>                                | -                                                                 | ±10                                                                     | uA          | 0.4 <v<sub>IN<v<sub>DDC</v<sub></v<sub>               |

| Digital supply voltage                                                     | V <sub>DDC</sub>                                | 2.25 <sup>3)</sup>                                                | 2.75                                                                    | V           | -                                                     |

| Blocking capacitor for $V_{\text{DDC}}$                                    |                                                 | 136                                                               | 470                                                                     | nF          | _4)                                                   |

| Pin capacitance                                                            | C <sub>IO</sub>                                 | -                                                                 | 10                                                                      | pF          | $f_{\rm C}$ = 1MHz<br>$T_{\rm A}$ = 25 <sup>0</sup> C |

#### Note:

- Interrupt/analog pins are input only and has CMOS characteristics whereas the other I/O pins have TTL characteristics.

- <sup>2)</sup> The leakage current of interrupt/analog pins depends on the leakage current of the CMOS pad for the digital functions and the analog pad.

- <sup>3)</sup> The V<sub>DDC</sub> is measured under the following conditions:

Microcontroller in power down mode;  $\overline{\text{RESET}} = V_{\text{DDP}}$ ;  $\text{XTAL2} = V_{\text{SSC}}$ ; XTAL1 = N.C.;  $V_{\text{AGND}} = V_{\text{SSP}}$ ;  $V_{\text{AREF}} = V_{\text{DDP}}$ ;  $\text{RxD/INT0} = V_{\text{DDP}}$ ; all other pins are set to input and connected to gnd; ALE output disabled and connected to gnd; 20mA current sourced from the  $V_{\text{DDC}}$  pin.

$^{4)}\,$  Ceramic type (±20%) max ESR: 25m $\Omega$  ,max trace length to capacitor is 10mm.

- <sup>4)</sup> During the sample time the input capacitance C<sub>AIN</sub> must be charged/discharged by the external source. The internal resistance of the analog source must allow the capacitance to reach their final voltage level within t<sub>S</sub>. After the end of the sample time t<sub>S</sub>, changes of the analog input voltage have no effect on the conversion result.

- <sup>5)</sup> Not 100% tested, but guaranteed by design characterization.

#### **Clock calculation table for ADC**

| TVC <sup>1)</sup> |     |     |     |     | 32  |     |     |     |                  |

|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|------------------|

| STC <sup>2)</sup> | 2   | 4   | 6   | 8   | 10  | 12  | 14  | 16  | $t_{ADC}^{3)}$   |

| t <sub>ADCC</sub> | 322 | 386 | 450 | 514 | 578 | 642 | 706 | 770 | t <sub>SYS</sub> |

| t <sub>S</sub>    | 64  | 128 | 192 | 256 | 320 | 384 | 448 | 512 | t <sub>SYS</sub> |

| TVC <sup>1)</sup> |     |     |     |     | 28  |     |     |     |                  |

| STC <sup>2)</sup> | 2   | 4   | 6   | 8   | 10  | 12  | 14  | 16  | $t_{ADC}^{3)}$   |

| t <sub>ADCC</sub> | 282 | 338 | 394 | 450 | 506 | 562 | 618 | 674 | t <sub>SYS</sub> |

| t <sub>S</sub>    | 56  | 112 | 168 | 224 | 280 | 336 | 392 | 448 | t <sub>SYS</sub> |

| TVC <sup>1)</sup> |     |     |     |     | 24  |     |     |     |                  |

| STC <sup>2)</sup> | 2   | 4   | 6   | 8   | 10  | 12  | 14  | 16  | $t_{ADC}^{3)}$   |

| t <sub>ADCC</sub> | 242 | 290 | 338 | 386 | 434 | 482 | 530 | 578 | t <sub>SYS</sub> |

| t <sub>S</sub>    | 48  | 96  | 144 | 192 | 240 | 288 | 336 | 384 | t <sub>SYS</sub> |

| TVC <sup>1)</sup> |     |     |     |     | 20  |     |     |     |                  |

| STC <sup>2)</sup> | 2   | 4   | 6   | 8   | 10  | 12  | 14  | 16  | $t_{ADC}^{3)}$   |

| t <sub>ADCC</sub> | 202 | 242 | 282 | 322 | 362 | 402 | 442 | 482 | t <sub>SYS</sub> |

| t <sub>S</sub>    | 40  | 80  | 120 | 160 | 200 | 240 | 280 | 320 | t <sub>SYS</sub> |

| TVC <sup>1)</sup> |     |     |     |     | 16  |     |     |     |                  |

| STC <sup>2)</sup> | 2   | 4   | 6   | 8   | 10  | 12  | 14  | 16  | $t_{ADC}^{3)}$   |

| t <sub>ADCC</sub> | 162 | 194 | 226 | 258 | 290 | 322 | 354 | 386 | t <sub>SYS</sub> |

| t <sub>S</sub>    | 32  | 64  | 96  | 128 | 160 | 192 | 224 | 256 | t <sub>SYS</sub> |

| TVC <sup>1)</sup> |     |     |     |     | 12  |     |     |     |                  |

| STC <sup>2)</sup> | 2   | 4   | 6   | 8   | 10  | 12  | 14  | 16  | $t_{ADC}^{3)}$   |

| t <sub>ADCC</sub> | 122 | 146 | 170 | 194 | 218 | 242 | 266 | 290 | t <sub>SYS</sub> |

| ts                | 24  | 48  | 72  | 96  | 120 | 144 | 168 | 192 | t <sub>SYS</sub> |

#### **AC Characteristics**

#### (Operating Condition Apply)

#### **External Clock Drive Characteristics**

| Parameter          | Symbol                | Limit Values |                              | Unit |

|--------------------|-----------------------|--------------|------------------------------|------|

|                    |                       |              | ole Ext Clock<br>o 10.67 MHz |      |

|                    |                       | min          | max                          |      |

| Oscillating period | t <sub>OSC</sub>      | 93.75        | 150                          | ns   |

| High time          | $t_1$                 | 46.875       | 75                           | ns   |

| Low time           | <i>t</i> <sub>2</sub> | 46.875       | 75                           | ns   |

| Rise time          | $t_R$                 | -            | 10                           | ns   |

| Fall time          | $t_F$                 | -            | 10                           | ns   |

#### ALE Characteristics

| Parameter       | Symbol           | Lin | Unit                              |    |

|-----------------|------------------|-----|-----------------------------------|----|

|                 |                  |     | = 6.25MHz to 40MHz<br>/ Cycle 0.5 |    |

|                 |                  | min | max                               |    |

| ALE pulse width | t <sub>AWD</sub> | 50  | 320                               | ns |

| ALE period      | t <sub>ACY</sub> | 150 | 960                               | ns |

### Infineon goes for Business Excellence

"Business excellence means intelligent approaches and clearly defined processes, which are both constantly under review and ultimately lead to good operating results. Better operating results and business excellence mean less

idleness and wastefulness for all of us, more professional success, more accurate information, a better overview and, thereby, less frustration and more satisfaction."

Dr. Ulrich Schumacher

http://www.infineon.com