Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI                                                     |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 336 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-TQFP                                                                   |

| Supplier Device Package    | 64-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c926t-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

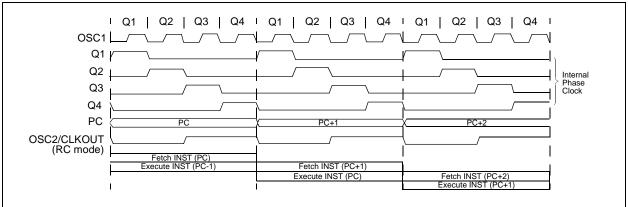

#### 1.1 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 1-2.

## 1.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined, such that fetch takes one instruction cycle, while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g. GOTO), then two cycles are required to complete the instruction (Example 1-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 1-2: CLOCK/INSTRUCTION CYCLE

#### EXAMPLE 1-1: INSTRUCTION PIPELINE FLOW

|                         | TCY0       | TCY1      | TCY2      | TCY3      | TCY4        | TCY5          |

|-------------------------|------------|-----------|-----------|-----------|-------------|---------------|

| 1. MOVLW 55h            | Fetch 1    | Execute 1 |           |           |             |               |

| 2. MOVWF PORTB          |            | Fetch 2   | Execute 2 |           |             |               |

| 3. CALL SUB_1           |            |           | Fetch 3   | Execute 3 | ]           |               |

| 4. BSF PORTA, BIT3 (F   | orced NOP) |           |           | Fetch 4   | Flush       |               |

| 5. Instruction @ addres | s SUB_1    |           |           |           | Fetch SUB_1 | Execute SUB_1 |

|                         |            |           |           |           |             |               |

All instructions are single cycle, except for any program branches. These take two cycles, since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

## 4.0 I/O PORTS

Some pins for these ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

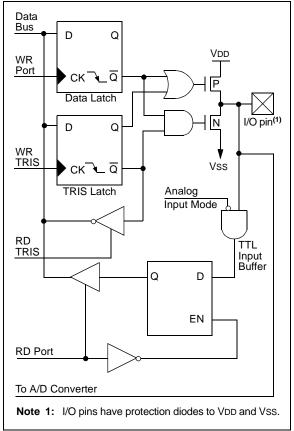

## 4.1 PORTA and TRISA Register

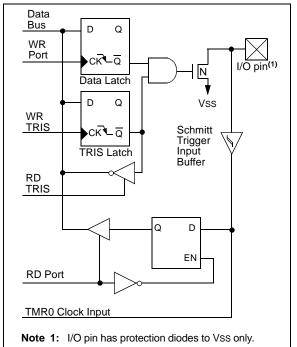

The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers. All RA pins have data direction bits (TRISA register), which can configure these pins as output or input.

Setting a bit in the TRISA register puts the corresponding output driver in a Hi-Impedance mode. Clearing a bit in the TRISA register puts the contents of the output latch on the selected pin.

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch.

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The other PORTA pins are multiplexed with analog inputs and the analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

| Note: | On a Power-on Reset, these pins are con-  |

|-------|-------------------------------------------|

|       | figured as analog inputs and read as '0'. |

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

#### EXAMPLE 4-1: INITIALIZING PORTA

| BCF<br>BCF | STATUS, RPO<br>STATUS, RP1 | ; Select Bank0          |

|------------|----------------------------|-------------------------|

| CLRF       | PORTA                      | ; Initialize PORTA      |

| BSF        | STATUS, RPO                | ; Select Bank1          |

| MOVLW      | 0xCF                       | ; Value used to         |

|            |                            | ; initialize data       |

|            |                            | ; direction             |

| MOVWF      | TRISA                      | ; Set RA<3:0> as inputs |

|            |                            | ; RA<5:4> as outputs    |

|            |                            | ; RA<7:6> are always    |

|            |                            | ; read as '0'.          |

#### FIGURE 4-1: BLOCK DIAGRAM OF

#### PINS RA3:RA0 AND RA5

FIGURE 4-2:

#### BLOCK DIAGRAM OF RA4/T0CKI PIN

#### 4.2 PORTB and TRISB Register

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. Setting a bit in the TRISB register puts the corresponding output driver in a Hi-Impedance Input mode. Clearing a bit in the TRISB register puts the contents of the output latch on the selected pin(s).

| EXAMPLE 4-2: | INITIALIZING PORTB |

|--------------|--------------------|

|              |                    |

| BCF   | STATUS, | RP0 | ; | Select Bank0          |

|-------|---------|-----|---|-----------------------|

| BCF   | STATUS, | RP1 |   |                       |

| CLRF  | PORTB   |     | ; | Initialize PORTB      |

| BSF   | STATUS, | RP0 | ; | Select Bank1          |

| MOVLW | 0xCF    |     | ; | Value used to         |

|       |         |     | ; | initialize data       |

|       |         |     | ; | direction             |

| MOVWF | TRISB   |     | ; | Set RB<3:0> as inputs |

|       |         |     | ; | RB<5:4> as outputs    |

|       |         |     | ; | RB<7:6> as inputs     |

|       |         |     |   |                       |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are also disabled on a Power-on Reset.

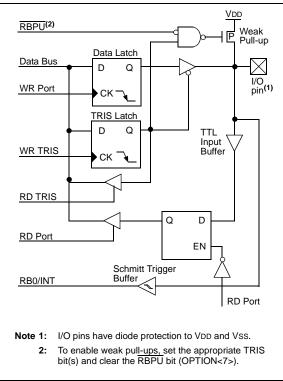

FIGURE 4-3: BLOCK DIAGRAM OF RB3:RB0 PINS

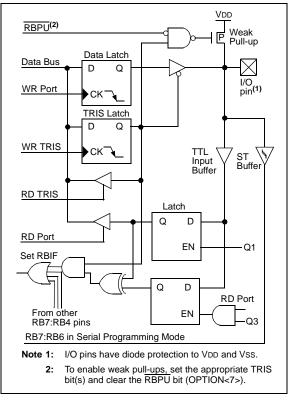

Four of the PORTB pins (RB7:RB4) have an interrupt-on-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupt-on-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition, and allow flag bit RBIF to be cleared.

This interrupt-on-mismatch feature, together with software configurable pull-ups on these four pins, allow easy interface to a keypad and make it possible for wake-up on key depression. Refer to the Embedded Control Handbook, "Implementing Wake-Up on Key Stroke" (AN552).

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

FIGURE 4-4:

#### BLOCK DIAGRAM OF RB7:RB4 PINS

### 4.8 I/O Programming Considerations

#### 4.8.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the contents of the data latch may now be unknown.

Reading the port register reads the values of the port pins. Writing to the port register, writes the value to the port latch. When using read-modify-write instructions (e.g. BCF, BSF) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 4-8 shows the effect of two sequential read-modify-write instructions on an I/O port. A pin actively outputting a Low or High should not be driven from external devices at the same time, in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

#### EXAMPLE 4-8: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

| ;Initial PORT settings: PORTB<7:4> Inputs  |  |

|--------------------------------------------|--|

| ; PORTB<3:0> Outputs                       |  |

| ;PORTB<7:6> have external pull-ups and are |  |

| ;not connected to other circuitry          |  |

| ;                                          |  |

| ; PORT latch PORT pins                     |  |

| ;                                          |  |

| BCF PORTB, 7 ; 01pp pppp 11pp pppp         |  |

| BCF PORTB, 6 ; 10pp pppp 11pp pppp         |  |

| BCF STATUS, RP1 ; Select Bank1             |  |

| BSF STATUS, RPO ;                          |  |

| BCF TRISB, 7 ; 10pp pppp 11pp pppp         |  |

| BCF TRISB, 6 ; 10pp pppp 10pp ppp          |  |

| ;                                          |  |

| ;Note that the user may have expected the  |  |

| ;pin values to be 00pp ppp. The 2nd BCF    |  |

| ;caused RB7 to be latched as the pin value |  |

| ; (high).                                  |  |

|                                            |  |

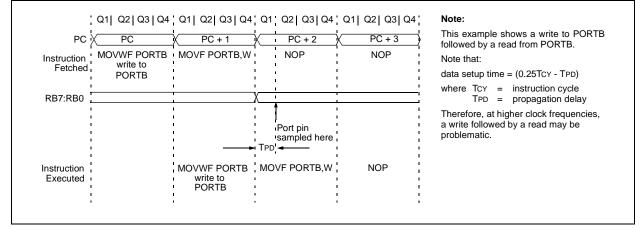

# 4.8.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 4-10). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before the next instruction, which causes that file to be read into the CPU, is executed. Otherwise, the previous state of that pin may be read into the CPU, rather than the new state. When in doubt, it is better to separate these instructions with a NOP, or another instruction not accessing this I/O port.

#### FIGURE 4-10: SUCCESSIVE I/O OPERATION

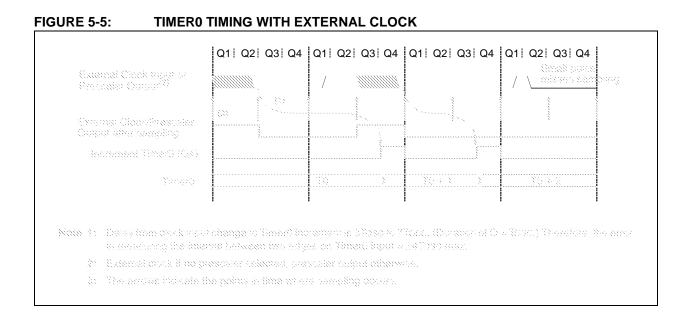

#### 5.2 Using Timer0 with an External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 5.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 5-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple counter type prescaler, so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

### 5.2.2 TMR0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 5-5 shows the delay from the external clock edge to the timer incrementing.

| Address                 | Name    | Bit 7                      | Bit 6                      | Bit 5        | Bit 4         | Bit 3         | Bit 2      | Bit 1      | Bit 0  | Valu<br>Powe<br>Res | er-on | all o | e on<br>other<br>SETS |

|-------------------------|---------|----------------------------|----------------------------|--------------|---------------|---------------|------------|------------|--------|---------------------|-------|-------|-----------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON  | GIE                        | PEIE                       | TMR0IE       | INTE          | RBIE          | TMR0IF     | INTF       | RBIF   | 0000                | 000x  | 0000  | 000u                  |

| 0Ch                     | PIR1    | LCDIF                      | ADIF                       | _            | _             | SSPIF         | CCP1IF     | TMR2IF     | TMR1IF | 00                  | 0000  | 00    | 0000                  |

| 8Ch                     | PIE1    | LCDIE                      | ADIE                       | —            | —             | SSPIE         | CCP1IE     | TMR2IE     | TMR1IE | 00                  | 0000  | 00    | 0000                  |

| 87h                     | TRISC   | —                          | _                          | PORTC Da     | ata Direction | Control Reg   | jister     |            |        | 11                  | 1111  | 11    | 1111                  |

| 0Eh                     | TMR1L   | Holding                    | register f                 | or the Least | t Significant | Byte of the 1 | 6-bit TMR1 | I Register |        | xxxx                | xxxx  | uuuu  | uuuu                  |

| 0Fh                     | TMR1H   | Holding                    | register f                 | or the Most  | Significant E | Byte of the 1 | 6-bit TMR1 | Register   |        | xxxx                | xxxx  | uuuu  | uuuu                  |

| 10h                     | T1CON   | —                          | _                          | T1CKPS1      | T1CKPS0       | T1OSCEN       | T1SYNC     | TMR1CS     | TMR10N | 00                  | 0000  | uu    | uuuu                  |

| 15h                     | CCPR1L  | Capture                    | Capture/Compare/PWM1 (LSB) |              |               |               |            |            |        |                     | xxxx  | uuuu  | uuuu                  |

| 16h                     | CCPR1H  | Capture/Compare/PWM1 (MSB) |                            |              |               |               |            |            |        |                     | xxxx  | uuuu  | uuuu                  |

| 17h                     | CCP1CON | —                          | —                          | CCP1X        | CCP1Y         | CCP1M3        | CCP1M2     | CCP1M1     | CCP1M0 | 00                  | 0000  | 0 0   | 0000                  |

#### TABLE 8-3: REGISTERS ASSOCIATED WITH TIMER1, CAPTURE AND COMPARE

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used in these modes.

#### TABLE 8-4: REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Address                 | Name    | Bit 7    | Bit 6                      | Bit 5      | Bit 4         | Bit 3      | Bit 2  | Bit 1   | Bit 0   | Value<br>Power<br>Rese | r-on |      | e on<br>other<br>ETS |

|-------------------------|---------|----------|----------------------------|------------|---------------|------------|--------|---------|---------|------------------------|------|------|----------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON  | GIE      | PEIE                       | TMR0IE     | INTE          | RBIE       | TMR0IF | INTF    | RBIF    | 0000 (                 | 000x | 0000 | 000u                 |

| 0Ch                     | PIR1    | LCDIF    | ADIF                       | —          | —             | SSPIF      | CCP1IF | TMR2IF  | TMR1IF  | 00 0                   | 0000 | 00   | 0000                 |

| 8Ch                     | PIE1    | LCDIE    | ADIE                       | —          | —             | SSPIE      | CCP1IE | TMR2IE  | TMR1IE  | 00 0                   | 0000 | 00   | 0000                 |

| 87h                     | TRISC   | _        | —                          | PORTC Da   | ata Direction | Control Re | gister |         |         | 11 1                   | 1111 | 11   | 1111                 |

| 11h                     | TMR2    | Timer2 N | /lodule Regi               | ster       |               |            |        |         |         | 0000 0                 | 0000 | 0000 | 0000                 |

| 92h                     | PR2     | Timer2 N | Nodule Peric               | d Register |               |            |        |         |         | 1111 1                 | 1111 | 1111 | 1111                 |

| 12h                     | T2CON   | —        | TOUTPS3                    | TOUTPS2    | TOUTPS1       | TOUTPS0    | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0                 | 0000 | -000 | 0000                 |

| 15h                     | CCPR1L  | Capture/ | Capture/Compare/PWM1 (LSB) |            |               |            |        |         |         |                        |      | uuuu | uuuu                 |

| 16h                     | CCPR1H  | Capture/ | Capture/Compare/PWM1 (MSB) |            |               |            |        |         |         |                        |      | uuuu | uuuu                 |

| 17h                     | CCP1CON |          |                            | CCP1X      | CCP1Y         | CCP1M3     | CCP1M2 | CCP1M1  | CCP1M0  | 00 0                   | 0000 | 00   | 0000                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used in this mode.

## 9.0 SYNCHRONOUS SERIAL PORT (SSP) MODULE

The Synchronous Serial Port (SSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The SSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI™)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

Refer to Application Note AN578, "Use of the SSP Module in the I  $^2\mathrm{C}$  Multi-Master Environment."

#### REGISTER 9-1: SSPSTAT: SERIAL PORT STATUS REGISTER (ADDRESS 94h)

|        | R/W-0                                                                                   | R/W-0                             | R-0               | R-0             | R-0                | R-0             | R-0            | R-0           |  |  |  |  |  |

|--------|-----------------------------------------------------------------------------------------|-----------------------------------|-------------------|-----------------|--------------------|-----------------|----------------|---------------|--|--|--|--|--|

|        | SMP                                                                                     | CKE                               | D/A               | Р               | S                  | R/W             | UA             | BF            |  |  |  |  |  |

|        | bit 7                                                                                   |                                   |                   |                 |                    |                 |                | bit 0         |  |  |  |  |  |

|        |                                                                                         |                                   |                   |                 |                    |                 |                |               |  |  |  |  |  |

| bit 7  | SMP: SPI D                                                                              | ata Input Sam                     | ple Phase bit     |                 |                    |                 |                |               |  |  |  |  |  |

|        | SPI Master r                                                                            |                                   |                   |                 |                    |                 |                |               |  |  |  |  |  |

|        |                                                                                         | ta sampled at                     |                   |                 |                    |                 |                |               |  |  |  |  |  |

|        | 0 = Input data sampled at middle of data output time<br><u>SPI Slave mode:</u>          |                                   |                   |                 |                    |                 |                |               |  |  |  |  |  |

|        | SMP must be cleared when SPI is used in Slave mode                                      |                                   |                   |                 |                    |                 |                |               |  |  |  |  |  |

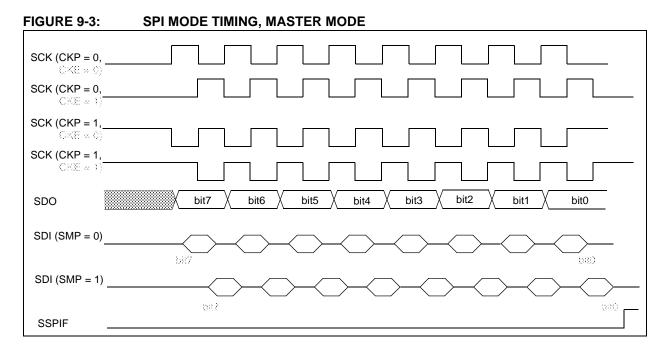

| bit 6  | CKE: SPI Clock Edge Select bit (see Figure 9-3, Figure 9-4, and Figure 9-5)             |                                   |                   |                 |                    |                 |                |               |  |  |  |  |  |

|        | CKE: SPI Clock Edge Select bit (see Figure 9-3, Figure 9-4, and Figure 9-5)<br>CKP = 0: |                                   |                   |                 |                    |                 |                |               |  |  |  |  |  |

|        |                                                                                         | nsmitted on ris                   |                   |                 |                    |                 |                |               |  |  |  |  |  |

|        |                                                                                         | nsmitted on fa                    | Illing edge of    | SCK             |                    |                 |                |               |  |  |  |  |  |

|        | <u>CKP = 1:</u><br>1 = Data transmitted on falling edge of SCK                          |                                   |                   |                 |                    |                 |                |               |  |  |  |  |  |

|        |                                                                                         | nsmitted on ris                   |                   |                 |                    |                 |                |               |  |  |  |  |  |

| bit 5  |                                                                                         | ddress bit (I <sup>2</sup> C      |                   |                 |                    |                 |                |               |  |  |  |  |  |

|        | 1 = Indicate                                                                            | s that the last                   | byte received     | l or transmitte | ed was data        |                 |                |               |  |  |  |  |  |

|        |                                                                                         | s that the last                   | •                 |                 |                    |                 |                |               |  |  |  |  |  |

| bit 4  |                                                                                         | (I <sup>2</sup> C mode on         | ly. This bit is o | cleared when    | the SSP mod        | dule is disable | ed, or when th | e START       |  |  |  |  |  |

|        | bit was deter                                                                           | cted last.)<br>s that a STOP      | hit haa haan      | detected leas   | (this hit is '0'   |                 |                |               |  |  |  |  |  |

|        |                                                                                         | it was not dete                   |                   | uelecteu las    |                    | UN RESET)       |                |               |  |  |  |  |  |

| bit 3  |                                                                                         | t (I <sup>2</sup> C mode o        |                   | cleared whe     | n the SSP mo       | odule is disab  | led, or when t | he STOP       |  |  |  |  |  |

|        | bit was dete                                                                            | cted last.)                       |                   |                 |                    |                 | ,              |               |  |  |  |  |  |

|        | 1 = Indicate                                                                            | s that a STAR                     | T bit has bee     | n detected la   | st (this bit is '( | )' on RESET)    |                |               |  |  |  |  |  |

| 1.11.0 | _                                                                                       | bit was not de                    |                   |                 |                    |                 |                |               |  |  |  |  |  |

| bit 2  |                                                                                         | Vrite bit Inforn<br>Is the R/W bi |                   |                 | last address       | match This      | hit is only y  | alid from the |  |  |  |  |  |

|        |                                                                                         | ch to the next                    |                   |                 |                    |                 | DIL IS UTILY V |               |  |  |  |  |  |

|        | 1 = Read                                                                                |                                   |                   |                 |                    |                 |                |               |  |  |  |  |  |

|        | 0 = Write                                                                               |                                   |                   |                 |                    |                 |                |               |  |  |  |  |  |

| bit 1  |                                                                                         | Address (10-b                     |                   | • /             |                    |                 |                |               |  |  |  |  |  |

|        |                                                                                         | s that the use                    |                   |                 | ess in the SS      | PADD registe    | r              |               |  |  |  |  |  |

| hit O  | 0 = Address                                                                             | does not nee                      |                   | eu              |                    |                 |                |               |  |  |  |  |  |

| bit 0  |                                                                                         | I and I <sup>2</sup> C mod        | les).             |                 |                    |                 |                |               |  |  |  |  |  |

|        |                                                                                         | complete, SS                      |                   |                 |                    |                 |                |               |  |  |  |  |  |

|        | 0 = Receive                                                                             | not complete                      |                   | empty           |                    |                 |                |               |  |  |  |  |  |

|        |                                                                                         | C mode only)                      |                   |                 |                    |                 |                |               |  |  |  |  |  |

|        |                                                                                         | t in progress,<br>t complete, SS  |                   |                 |                    |                 |                |               |  |  |  |  |  |

|        |                                                                                         | t complete, St                    | וווש פו יוסט יכ   | pry             |                    |                 |                |               |  |  |  |  |  |

|        | Legend:                                                                                 |                                   |                   |                 |                    |                 |                |               |  |  |  |  |  |

|        | R = Readab                                                                              | le bit                            | W = Wr            | itable bit      | U = Unim           | plemented bit   | , read as '0'  |               |  |  |  |  |  |

|        | - n = Value a                                                                           | at POR                            | '1' = Bit         | is set          | '0' = Bit is       | cleared         | x = Bit is un  | known         |  |  |  |  |  |

|        |                                                                                         |                                   | i = Dil           | 13 301          |                    | CIEdleu         |                | KIOWII        |  |  |  |  |  |

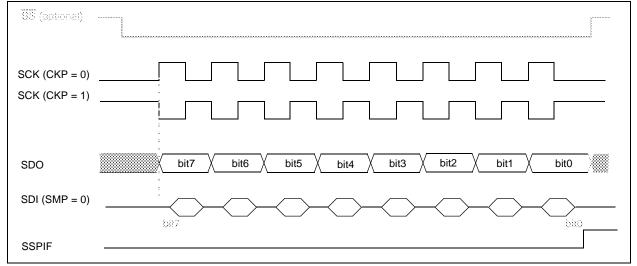

The  $\overline{SS}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode (SSPCON<3:0> = 04h) and the TRISA<5> bit must be set for the Synchronous Slave mode to be enabled. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable, depending on the application.

Note 1: When the SPI is in Slave mode with SS pin control enabled (SSPCON<3:0> = 0100), the SPI module will reset if the SS pin is set to VDD.

> 2: If the SPI is used in Slave mode with CKE = '1', then the SS pin control must be enabled.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver, the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

#### FIGURE 9-4: SPI MODE TIMING (SLAVE MODE WITH CKE = 0)

## 10.5 A/D Operation During SLEEP

The A/D module can operate during SLEEP mode. This requires that the A/D clock source be set to RC (ADCS<1:0> = 11). When the RC clock source is selected, the A/D module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed, which eliminates all digital switching noise from the conversion. When the conversion is completed, the GO/DONE bit will be cleared and the result loaded into the ADRES register. If the A/D interrupt is enabled, the device will wake-up from SLEEP. If the A/D interrupt is not enabled, the ADON bit will remain set.

When the A/D clock source is another clock option (not RC), a SLEEP instruction will cause the present conversion to be aborted and the A/D module to be turned off, though the ADON bit will remain set.

Turning off the A/D places the A/D module in its lowest current consumption state.

| Note: | For the A/D module to operate in SLEEP,   |

|-------|-------------------------------------------|

|       | the A/D clock source must be set to RC    |

|       | (ADCS < 1:0 > = 11). To allow the conver- |

|       | sion to occur during SLEEP, ensure the    |

|       | SLEEP instruction immediately follows the |

|       | instruction that sets the GO/DONE bit.    |

## 10.6 Effects of a RESET

A device RESET forces all registers to their RESET state. This forces the A/D module to be turned off, and any conversion is aborted. All A/D input pins are configured as analog inputs.

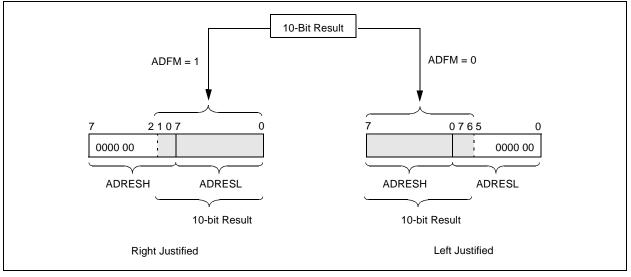

The value that is in the ADRESH:ADRESL registers is not modified for a Power-on Reset. The ADRESH:ADRESL registers will contain unknown data after a Power-on Reset.

| Address | Name   | Bit 7    | Bit 6      | Bit 5      | Bit 4     | Bit 3      | Bit 2       | Bit 1     | Bit 0   | POR,<br>BOR | MCLR,<br>WDT |

|---------|--------|----------|------------|------------|-----------|------------|-------------|-----------|---------|-------------|--------------|

| 0Bh     | INTCON | GIE      | PEIE       | TMR0IE     | INTE      | RBIE       | TMR0IF      | INTF      | RBIF    | 0000 000x   | 0000 000u    |

| 0Ch     | PIR1   | LCDIF    | ADIF       | (1)        | (1)       | SSPIF      | CCP1IF      | TMR2IF    | TMR1IF  | r0rr 0000   | r0rr 0000    |

| 8Ch     | PIE1   | LCDIE    | ADIE       | (1)        | (1)       | SSPIE      | CCP1IE      | TMR2IE    | TMR1IE  | r0rr 0000   | r0rr 0000    |

| 1Eh     | ADRESH | A/D Resu | lt Registe | r High Byt | е         |            |             |           |         | xxxx xxxx   | uuuu uuuu    |

| 9Eh     | ADRESL | A/D Resu | lt Registe | r Low Byte | 9         |            |             |           |         | xxxx xxxx   | uuuu uuuu    |

| 1Fh     | ADCON0 | ADCS1    | ADCS0      | CHS2       | CHS1      | CHS0       | GO/DONE     | _         | ADON    | 0000 00-0   | 0000 00-0    |

| 9Fh     | ADCON1 | ADFM     | _          | _          | _         | PCFG3      | PCFG2       | PCFG1     | PCFG0   | 0- 0000     | 0- 0000      |

| 85h     | TRISA  |          | _          | PORTA D    | ata Direc | tion Regis |             | 11 1111   | 11 1111 |             |              |

| 05h     | PORTA  | —        | _          | PORTA D    | ata Latch | when wri   | tten: PORTA | pins wher | n read  | 0x 0000     | 0u 0000      |

#### TABLE 10-2: REGISTERS/BITS ASSOCIATED WITH A/D

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for A/D conversion. **Note 1:** These bits are reserved; always maintain these bits clear.

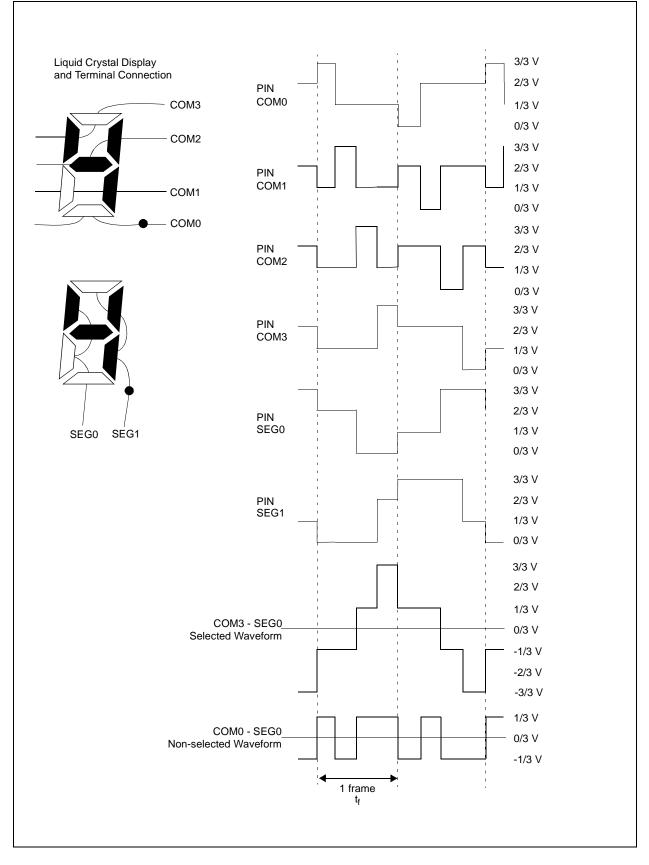

### FIGURE 11-5: WAVEFORMS IN QUARTER-DUTY CYCLE DRIVE (B TYPE)

## 12.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits to deal with the needs of real time applications. The PIC16CXXX family has a host of such features, intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator Selection

- RESET

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code Protection

- ID Locations

- In-Circuit Serial Programming

The PIC16CXXX has a Watchdog Timer which can be shut-off only through configuration bits. It runs off its own RC oscillator for added reliability.

There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. With these two timers on-chip, most applications need no external RESET circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer Wake-up, or through an interrupt.

Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. A set of configuration bits are used to select various options.

## 12.1 Configuration Bits

The configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space and can be accessed only during programming.

# PIC16C925/926

| CLRF                                             | Clear f                                                               |                                                                |                 |                          |  |

|--------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------|-----------------|--------------------------|--|

| Syntax:                                          | [label] CLRF f                                                        |                                                                |                 |                          |  |

| Operands:                                        | $0 \le f \le 12$                                                      | .7                                                             |                 |                          |  |

| Operation:                                       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |                                                                |                 |                          |  |

| Status Affected:                                 | Z                                                                     |                                                                |                 |                          |  |

| Encoding:                                        | 0 0                                                                   | 0001                                                           | lfff            | ffff                     |  |

| Description:                                     |                                                                       | The contents of register 'f' are cleared and the Z bit is set. |                 |                          |  |

| Words:                                           | 1                                                                     |                                                                |                 |                          |  |

| Cycles:                                          | 1                                                                     |                                                                |                 |                          |  |

| Q Cycle Activity:                                | Q1                                                                    | Q2                                                             | Q3              | Q4                       |  |

|                                                  | Decode                                                                | Read<br>register<br>'f'                                        | Process<br>data | Write<br>register<br>'f' |  |

| Example                                          | CLRF                                                                  | FLAG_RE                                                        | G               |                          |  |

| Before Instruction:<br>FLAG_REG = 0x5A           |                                                                       |                                                                |                 |                          |  |

| After Instruction:<br>$FLAG_REG = 0x00$<br>Z = 1 |                                                                       |                                                                |                 |                          |  |

| CLRW              | Clear W                                                               |                 |                 |               |  |  |

|-------------------|-----------------------------------------------------------------------|-----------------|-----------------|---------------|--|--|

| Syntax:           | [label]                                                               | CLRW            |                 |               |  |  |

| Operands:         | None                                                                  |                 |                 |               |  |  |

| Operation:        | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |                 |                 |               |  |  |

| Status Affected:  | Z                                                                     |                 |                 |               |  |  |

| Encoding:         | 00                                                                    | 0001            | 0xxx            | xxxx          |  |  |

| Description:      | W register is cleared. Zero bit (Z) is set.                           |                 |                 |               |  |  |

| Words:            | 1                                                                     |                 |                 |               |  |  |

| Cycles:           | 1                                                                     |                 |                 |               |  |  |

| Q Cycle Activity: | Q1                                                                    | Q2              | Q3              | Q4            |  |  |

|                   | Decode                                                                | No<br>Operation | Process<br>data | Write to<br>W |  |  |

| Example           | CLRW                                                                  |                 |                 |               |  |  |

| Before Instruction: |   |      |  |  |  |

|---------------------|---|------|--|--|--|

| W                   | = | 0x5A |  |  |  |

| After Instruction:  |   |      |  |  |  |

| W                   | = | 0x00 |  |  |  |

| Z                   | = | 1    |  |  |  |

# 14.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK™ Object Linker/

- MPLIB<sup>™</sup> Object Librarian

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- ICEPIC<sup>™</sup> In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD for PIC16F87X

- Device Programmers

- PRO MATE<sup>®</sup> II Universal Device Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Development Programmer

- Low Cost Demonstration Boards

- PICDEM<sup>™</sup>1 Demonstration Board

- PICDEM 2 Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 17 Demonstration Board

- KEELOQ<sup>®</sup> Demonstration Board

#### 14.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup>-based application that contains:

- · An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- A full-featured editor

- · A project manager

- Customizable toolbar and key mapping

- A status bar

- On-line help

The MPLAB IDE allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- machine code

The ability to use MPLAB IDE with multiple debugging tools allows users to easily switch from the costeffective simulator to a full-featured emulator with minimal retraining.

### 14.2 MPASM Assembler

The MPASM assembler is a full-featured universal macro assembler for all PIC MCUs.

The MPASM assembler has a command line interface and a Windows shell. It can be used as a stand-alone application on a Windows 3.x or greater system, or it can be used through MPLAB IDE. The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file that contains source lines and generated machine code, and a COD file for debugging.

The MPASM assembler features include:

- Integration into MPLAB IDE projects.

- User-defined macros to streamline assembly code.

- Conditional assembly for multi-purpose source files.

- Directives that allow complete control over the assembly process.

### 14.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI 'C' compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

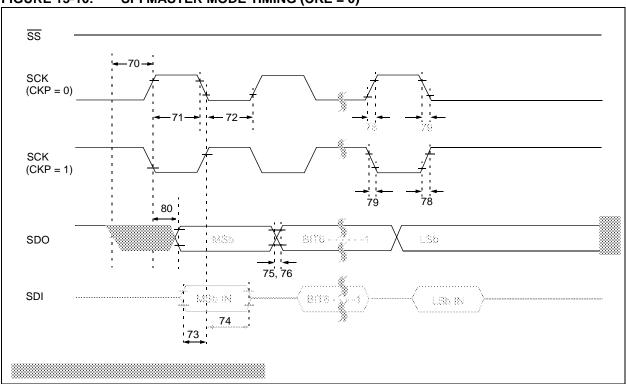

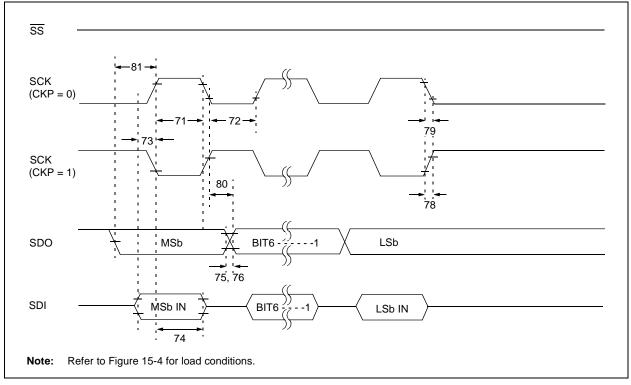

## FIGURE 15-11: SPI MASTER MODE TIMING (CKE = 1)

FIGURE 15-10: SPI MASTER MODE TIMING (CKE = 0)

| Param<br>No. | Symbol                | Characteristic                                                        |             | Min          | Тур† | Max              | Units | Conditions |

|--------------|-----------------------|-----------------------------------------------------------------------|-------------|--------------|------|------------------|-------|------------|

| 70           | TssL2scH,<br>TssL2scL | $\overline{SS}\downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ input | Тсү         | —            | —    | ns               |       |            |

| 71           | TscH                  | SCK input high time (Slave                                            | Continuous  | 1.25Tcy + 30 | _    |                  | ns    |            |

| 71A          |                       | mode)                                                                 | Single Byte | 40           | —    | —                | ns    |            |

| 72           | TscL                  | SCK input low time (Slave                                             | Continuous  | 1.25Tcy + 30 | —    | $\leq 1$         | ns    |            |

| 72A          |                       | mode)                                                                 | Single Byte | 40           | D    | $) \leq \langle$ |       |            |

| 73           | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input                                          | 50          | X H          | >    | ns               |       |            |

| 74           | TscH2diL,<br>TscL2diL | Hold time of SDI data input to                                        | 50          | <u> </u>     | —    | ns               |       |            |

| 75           | TdoR                  | SDO data output rise time                                             |             | <u> </u>     | 10   | 25               | ns    |            |

| 76           | TdoF                  | SDO data output fall time                                             |             | —            | 10   | 25               | ns    |            |

| 77           | TssH2doZ              | 55 to SDO output himpedance                                           |             | 10           | —    | 50               | ns    |            |

| 78           | TscR                  | SCK output rise time (Master mode)                                    |             | —            | 10   | 25               | ns    |            |

| 79           | TscF                  | SCK output fall time (Master mode)                                    |             | —            | 10   | 25               | ns    |            |

| 80           | TscH2doV,<br>TscL2doV | SDO data output valid after SCK edge                                  |             | —            | —    | 50               | ns    |            |

| 81           | TdoV2scH,<br>TdoV2scL | SDO data output setup to SCK edge                                     |             | Тсү          | —    | —                | ns    |            |

| 82           | TssL2doV              | SDO data output valid after $\overline{SS}\downarrow$ edge            |             | —            | —    | 50               | ns    |            |

| 83           | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK edge                                                   |             | 1.5Tcy + 40  | —    | —                | ns    |            |

| 84           | Tb2b                  | Delay between consecutive bytes                                       |             | 1.5TCY + 40  |      |                  | ns    |            |

#### TABLE 15-8: SPI MODE REQUIREMENTS

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# PIC16C925/926

NOTES:

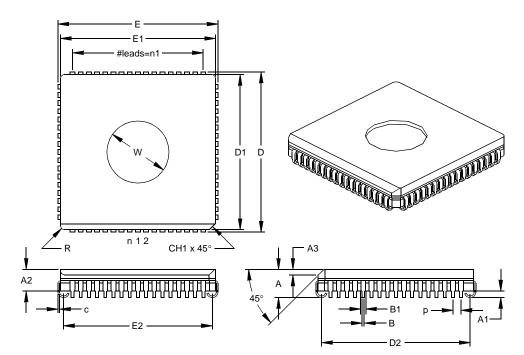

#### 68-Lead Ceramic Leaded (CL) Chip Carrier with Window - Square (CERQUAD)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units  | INCHES* |      |      | MILLIMETERS |       |       |

|------------------------|--------|---------|------|------|-------------|-------|-------|

| Dimension              | Limits | MIN     | NOM  | MAX  | MIN         | NOM   | MAX   |

| Number of Pins         | n      |         | 68   |      |             | 68    |       |

| Pitch                  | р      |         | .050 |      |             | 1.27  |       |

| Overall Height         | А      | .165    | .175 | .185 | 4.19        | 4.45  | 4.70  |

| Package Thickness      | A2     | .118    | .137 | .155 | 3.00        | 3.48  | 3.94  |

| Standoff §             | A1     | .030    | .040 | .050 | 0.76        | 1.02  | 1.27  |

| Side One Chamfer Dim.  | A3     | .030    | .035 | .040 | 0.76        | 0.89  | 1.02  |

| Corner Chamfer (1)     | CH1    | .030    | .040 | .050 | 0.76        | 1.02  | 1.27  |

| Corner Radius (Others) | R      | .020    | .025 | .030 | 0.51        | 0.64  | 0.76  |

| Overall Package Width  | E      | .983    | .988 | .993 | 24.97       | 25.10 | 25.22 |

| Overall Package Length | D      | .983    | .988 | .993 | 24.97       | 25.10 | 25.22 |

| Ceramic Package Width  | E1     | .942    | .950 | .958 | 23.93       | 24.13 | 24.33 |

| Ceramic Package Length | D1     | .942    | .950 | .958 | 23.93       | 24.13 | 24.33 |

| Footprint Width        | E2     | .890    | .910 | .930 | 22.61       | 23.11 | 23.62 |

| Footprint Length       | D2     | .890    | .910 | .930 | 22.61       | 23.11 | 23.62 |

| Pins each side         | n1     |         | 17   |      |             | 17    |       |

| Lead Thickness         | С      | .008    | .010 | .012 | 0.20        | 0.25  | 0.30  |

| Upper Lead Width       | B1     | .026    | .029 | .031 | 0.66        | 0.72  | 0.79  |

| Lower Lead Width       | В      | .015    | .018 | .021 | 0.38        | 0.46  | 0.53  |

| Window Diameter        | W      | .370    | .380 | .390 | 9.40        | 9.65  | 9.91  |

\* Controlling Parameter § Significant Characteristic JEDEC Equivalent: MO-087 Drawing No. C04-097

## APPENDIX C: CONVERSION CONSIDERATIONS

Considerations for converting to the devices listed in this data sheet from previous device types are summarized in Table C-1.

| TABLE C-1: | <br>ONVERSION<br>ONSIDERATIO | NS |

|------------|------------------------------|----|

|            |                              |    |

| Feature                         | PIC16C923/<br>924     | PIC16C925/<br>926      |

|---------------------------------|-----------------------|------------------------|

| Operating<br>Frequency          | DC - 8 MHz            | DC - 20 MHz            |

| EPROM Program<br>Memory (words) | 4K                    | 4K (925)<br>8K (926)   |

| Data Memory<br>(bytes)          | 176                   | 176 (925)<br>336 (926) |

| A/D Converter<br>Resolution     | 8-bit<br>(924 only)   | 10-bit                 |

| A/D Converter<br>Channels       | none (923)<br>5 (924) | 5                      |

| Interrupt Sources               | 8 (923)<br>9 (924)    | 9                      |

| Brown-out Reset                 | No                    | Yes                    |

# PIC16C925/926

| Code Protection           | 2 |

|---------------------------|---|

| Associated Registers58    | 3 |

| Block Diagram             | 5 |

| Pin Configuration55       | 5 |

| Software Interrupt Mode55 | 5 |

| Special Event Trigger55   | 5 |

| Timer1 Mode55             | 5 |

| Computed GOTO 58          |   |