Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

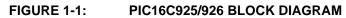

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I²C, SPI                                                                   |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 176 × 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | A/D 5x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc925t-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

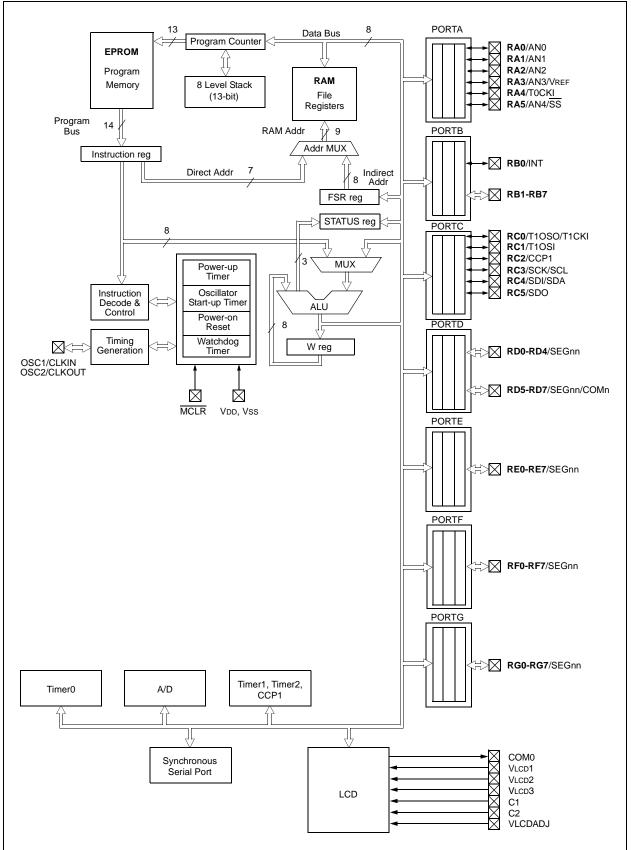

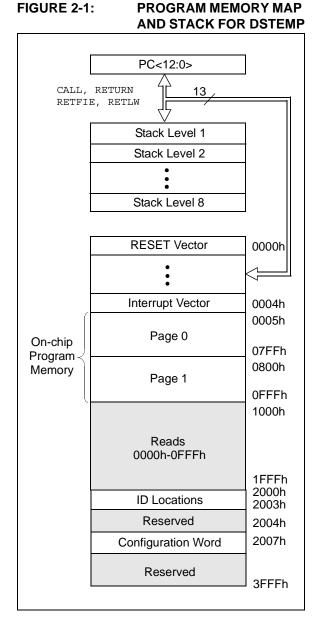

## 2.0 MEMORY ORGANIZATION

## 2.1 Program Memory Organization

The PIC16C925/926 family has a 13-bit program counter capable of addressing an 8K x 14 program memory space.

For the PIC16C925, only the first 4K x 14 (0000h-0FFFh) are physically implemented. Accessing a location above the physically implemented addresses will cause a wraparound. The RESET vector is at 0000h and the interrupt vector is at 0004h.

### 2.3.1 STATUS REGISTER

The STATUS register, shown in Register 2-1, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as  $000u \ u1uu$  (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions, not affecting any status bits, see the "Instruction Set Summary."

Note: The <u>C</u> and <u>DC</u> bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

## REGISTER 2-1: STATUS REGISTER (ADDRESS 03h, 83h, 103h, 183h)

|         | R/W-0                                                                                       | R/W-0                            | R/W-0                         | R-1           | R-1             | R/W-x         | R/W-x         | R/W-x        |  |  |

|---------|---------------------------------------------------------------------------------------------|----------------------------------|-------------------------------|---------------|-----------------|---------------|---------------|--------------|--|--|

|         | IRP                                                                                         | RP1                              | RP0                           | TO            | PD              | Z             | DC            | С            |  |  |

|         | bit 7                                                                                       |                                  |                               |               |                 |               |               | bit 0        |  |  |

|         |                                                                                             |                                  |                               |               |                 |               |               |              |  |  |

| bit 7   | IRP: Register Bank Select bit (used for indirect addressing)<br>1 = Bank 2, 3 (100h - 1FFh) |                                  |                               |               |                 |               |               |              |  |  |

|         |                                                                                             | , 3 (100n - 1<br>), 1 (00h - FF  |                               |               |                 |               |               |              |  |  |

| bit 6-5 | RP1:RP0:                                                                                    | Register Ba                      | nk Select bit                 | s (used for a | direct addre    | ssing)        |               |              |  |  |

|         |                                                                                             | 3 (180h - 1F                     |                               |               |                 |               |               |              |  |  |

|         |                                                                                             | 2 (100h - 17<br>1 (80h - FFh     |                               |               |                 |               |               |              |  |  |

|         |                                                                                             | 0 (00h - 7Fh                     |                               |               |                 |               |               |              |  |  |

| bit 4   | TO: Time-c                                                                                  | out bit                          |                               |               |                 |               |               |              |  |  |

|         |                                                                                             | ower-up, CL:<br>⁻ time-out oc    |                               | ction, or SLE | EP instructi    | on            |               |              |  |  |

| bit 3   | <b>PD</b> : Power                                                                           |                                  |                               |               |                 |               |               |              |  |  |

|         | 1 = After p                                                                                 | ower-up or b                     | y the CLRWI                   | or instructio | n               |               |               |              |  |  |

|         | 0 = By exe                                                                                  | cution of the                    | SLEEP inst                    | ruction       |                 |               |               |              |  |  |

| bit 2   | Z: Zero bit                                                                                 |                                  |                               |               |                 |               |               |              |  |  |

|         |                                                                                             | sult of an ari<br>sult of an ari |                               |               |                 | C             |               |              |  |  |

| bit 1   |                                                                                             | arry/borrow<br>the polarity      |                               |               | LW,SUBWF        | instructions) |               |              |  |  |

|         |                                                                                             | r-out from the<br>ry-out from t  |                               |               |                 | irred         |               |              |  |  |

| bit 0   |                                                                                             | prrow bit (AD<br>the polarity    |                               |               | BWF instru      | ctions)       |               |              |  |  |

|         |                                                                                             | r-out from the<br>ry-out from t  |                               |               |                 |               |               |              |  |  |

|         | Note:                                                                                       |                                  |                               |               |                 | complement    |               |              |  |  |

|         |                                                                                             | •                                | RRF, RLF) in<br>purce registe |               | nis bit is load | ded with eith | er the high o | or low order |  |  |

|         | Legend:                                                                                     |                                  |                               |               |                 |               |               |              |  |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## 2.3.2 OPTION REGISTER

The OPTION register is a readable and writable register, which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT pin interrupt, TMR0, and the weak pull-ups on PORTB. **Note:** To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

## **REGISTER 2-2:** OPTION REGISTER (ADDRESS 81h, 181h)

|         | R/W-1            | R/W-1                            | R/W-1            | R/W-1        | R/W-1         | R/W-1     | R/W-1        | R/W-1  |  |

|---------|------------------|----------------------------------|------------------|--------------|---------------|-----------|--------------|--------|--|

|         | RBPU             | INTEDG                           | TOCS             | T0SE         | PSA           | PS2       | PS1          | PS0    |  |

|         | bit 7            |                                  |                  |              |               |           |              | bit 0  |  |

| bit 7   | RBPU: P          | ORTB Pull-up                     | Enable bit       |              |               |           |              |        |  |

| 2       | 1 = PORT         | B pull-ups ar<br>B pull-ups ar   | e disabled       | v individual | oort latch va | lues      |              |        |  |

| bit 6   |                  | Interrupt Edg                    |                  | y marriada   |               |           |              |        |  |

|         |                  | upt on rising e                  | 0                |              |               |           |              |        |  |

| bit 5   | <b>T0CS</b> : TM | IR0 Clock So                     | urce Select      | bit          |               |           |              |        |  |

|         |                  | ition on RA4/<br>al instruction  | •                | (CLKOUT)     |               |           |              |        |  |

| bit 4   | TOSE: TM         | IR0 Source E                     | dge Select I     | oit          |               |           |              |        |  |

|         |                  | nent on high-<br>nent on low-to  |                  |              |               |           |              |        |  |

| bit 3   | PSA: Pre         | scaler Assign                    | ment bit         |              |               |           |              |        |  |

|         |                  | aler is assign<br>aler is assign |                  |              | e             |           |              |        |  |

| bit 2-0 | PS2:PS0          | Prescaler Ra                     | ate Select bi    | ts           |               |           |              |        |  |

|         | Bit Value        | TMR0 Rate                        | WDT Rate         |              |               |           |              |        |  |

|         | 000              | 1:2                              | 1:1              |              |               |           |              |        |  |

|         | 001<br>010       | 1:4<br>1:8                       | 1:2<br>1:4       |              |               |           |              |        |  |

|         | 011              | 1:16                             | 1:8              |              |               |           |              |        |  |

|         | 100<br>101       | 1:32<br>1:64                     | 1 : 16<br>1 : 32 |              |               |           |              |        |  |

|         | 110              | 1:128                            | 1:64             |              |               |           |              |        |  |

|         | 111              | 1 : 256                          | 1 : 128          |              |               |           |              |        |  |

|         |                  |                                  |                  |              |               |           |              |        |  |

|         | Legend:          |                                  |                  |              |               |           |              |        |  |

|         | R = Read         |                                  |                  | ritable bit  |               |           | bit, read as |        |  |

|         | - n = Valu       | e at POR                         | '1' = B          | it is set    | '0' = Bit i   | s cleared | x = Bit is u | nknown |  |

## 4.0 I/O PORTS

Some pins for these ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

## 4.1 PORTA and TRISA Register

The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers. All RA pins have data direction bits (TRISA register), which can configure these pins as output or input.

Setting a bit in the TRISA register puts the corresponding output driver in a Hi-Impedance mode. Clearing a bit in the TRISA register puts the contents of the output latch on the selected pin.

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch.

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The other PORTA pins are multiplexed with analog inputs and the analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

| Note: | On a Power-on Reset, these pins are con-  |

|-------|-------------------------------------------|

|       | figured as analog inputs and read as '0'. |

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

#### EXAMPLE 4-1: INITIALIZING PORTA

| BCF<br>BCF | STATUS, RPO<br>STATUS, RP1 | ; Select Bank0          |

|------------|----------------------------|-------------------------|

| CLRF       | PORTA                      | ; Initialize PORTA      |

| BSF        | STATUS, RPO                | ; Select Bank1          |

| MOVLW      | 0xCF                       | ; Value used to         |

|            |                            | ; initialize data       |

|            |                            | ; direction             |

| MOVWF      | TRISA                      | ; Set RA<3:0> as inputs |

|            |                            | ; RA<5:4> as outputs    |

|            |                            | ; RA<7:6> are always    |

|            |                            | ; read as '0'.          |

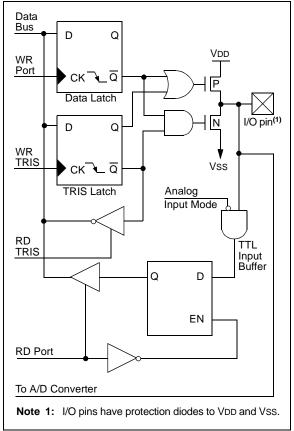

### FIGURE 4-1: BLOCK DIAGRAM OF

### PINS RA3:RA0 AND RA5

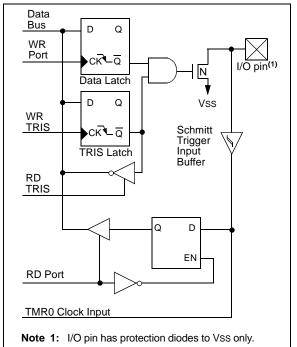

FIGURE 4-2:

#### BLOCK DIAGRAM OF RA4/T0CKI PIN

| REGISTER 7-1: | T2CON: TIMER2 CONTROL REGISTER (ADDRESS 12h) |                                                                                                              |             |               |               |           |              |         |  |

|---------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------|---------------|---------------|-----------|--------------|---------|--|

|               | U-0                                          | R/W-0                                                                                                        | R/W-0       | R/W-0         | R/W-0         | R/W-0     | R/W-0        | R/W-0   |  |

|               |                                              | TOUTPS3                                                                                                      | TOUTPS2     | TOUTPS1       | TOUTPS0       | TMR2ON    | T2CKPS1      | T2CKPS0 |  |

|               | bit 7                                        |                                                                                                              |             |               |               |           |              | bit 0   |  |

| bit 7         | Unimple                                      | mented: Re                                                                                                   | ad as '0'   |               |               |           |              |         |  |

| bit 6-3       | TOUTPS                                       | 3:TOUTPS0                                                                                                    | : Timer2 Ou | tput Postscal | e Select bits |           |              |         |  |

|               | 0000 = 1                                     | <b>TOUTPS3:TOUTPS0</b> : Timer2 Output Postscale Select bits<br>0000 = 1:1 Postscale<br>0001 = 1:2 Postscale |             |               |               |           |              |         |  |

|               | •                                            |                                                                                                              |             |               |               |           |              |         |  |

|               | •                                            |                                                                                                              |             |               |               |           |              |         |  |

|               | 1111 <b>= 1</b>                              | :16 Postscal                                                                                                 | е           |               |               |           |              |         |  |

| bit 2         | TMR2ON                                       | I: Timer2 On                                                                                                 | bit         |               |               |           |              |         |  |

|               | 1 = Time<br>0 = Time                         |                                                                                                              |             |               |               |           |              |         |  |

| bit 1-0       | T2CKPS                                       | 1:T2CKPS0                                                                                                    | Timer2 Clo  | ck Prescale S | Select bits   |           |              |         |  |

|               | 01 = Pre:                                    | scaler is 1<br>scaler is 4<br>scaler is 16                                                                   |             |               |               |           |              |         |  |

|               |                                              |                                                                                                              |             |               |               |           |              |         |  |

|               | Legend:                                      |                                                                                                              |             |               |               |           |              |         |  |

|               | R = Read                                     | dable bit                                                                                                    | W = V       | Vritable bit  | U = Unim      | plemented | bit, read as | '0'     |  |

|               | - n = Valu                                   | ue at POR                                                                                                    | '1' = E     | Bit is set    | '0' = Bit is  | s cleared | x = Bit is u | nknown  |  |

## TABLE 7-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Address                 | Name   | Bit 7                    | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0     | Value on<br>Power-on<br>Reset | Value on<br>all other<br>RESETS |

|-------------------------|--------|--------------------------|---------|---------|---------|---------|--------|---------|-----------|-------------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON | GIE                      | PEIE    | TMR0IE  | INTE    | RBIE    | TMR0IF | INTF    | RBIF      | 0000 000x                     | 0000 000u                       |

| 0Ch                     | PIR1   | LCDIF                    | ADIF    | _       | _       | SSPIF   | CCP1IF | TMR2IF  | TMR1IF    | 00 0000                       | 00 0000                         |

| 8Ch                     | PIE1   | LCDIE                    | ADIE    | _       |         | SSPIE   | CCP1IE | TMR2IE  | TMR1IE    | 00 0000                       | 00 0000                         |

| 11h                     | TMR2   | Timer2 Module's Register |         |         |         |         |        |         |           | 0000 0000                     | 0000 0000                       |

| 12h                     | T2CON  | _                        | TOUTPS3 | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0   | -000 0000                     | -000 0000                       |

| 92h                     | PR2    | Timer2 Period Register   |         |         |         |         |        |         | 1111 1111 | 1111 1111                     |                                 |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

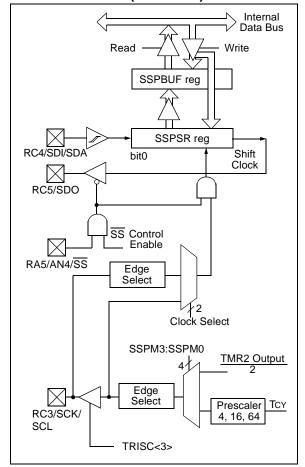

## 9.1 SPI Mode

The SPI mode allows 8-bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- Serial Data In (SDI) RC4/SDI

- Serial Clock (SCK) RC3/SCK

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS) RA5/AN4/SS

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON register (SSPCON<5:0>) and SSPSTAT<7:6>. These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Clock Edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- · Slave Select mode (Slave mode only)

The SSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR. until the received data is ready. Once the 8-bits of data have been received, that byte is moved to the SSPBUF register. Then, the buffer full detect bit, BF (SSPSTAT<0>), and interrupt flag bit, SSPIF (PIR1<3>), are set. This double buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPBUF register during transmission/reception of data will be ignored, and the write collision detect bit, WCOL (SSPCON<7>), will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully. When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. Buffer full bit, BF (SSPSTAT<0>), indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, bit BF is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the SSP interrupt is used to determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 9-1 shows the loading of the SSPBUF (SSPSR) for data transmission. The MOVWF RXDATA instruction (shaded) is only required if the received data is meaningful.

#### EXAMPLE 9-1: LOADING THE SSPBUF (SSPSR) REGISTER

|      | BCF   | STATUS, RP1 | ;Select Bank1                    |

|------|-------|-------------|----------------------------------|

|      | BSF   | STATUS, RPO | ;                                |

| LOOP | BTFSS | SSPSTAT, BF | ;Has data been                   |

|      |       |             | ;received                        |

|      |       |             | ;(transmit                       |

|      |       |             | ;complete)?                      |

|      | GOTO  | LOOP        | ;No                              |

|      | BCF   | STATUS, RPO | ;Select Bank0                    |

|      | MOVF  | SSPBUF, W   | ;W reg = contents<br>;of SSPBUF  |

|      | MOVWF | RXDATA      | ;Save in user RAM                |

|      | MOVF  | TXDATA, W   | ;W reg = contents<br>; of TXDATA |

|      | MOVWF | SSPBUF      | ;New data to xmit                |

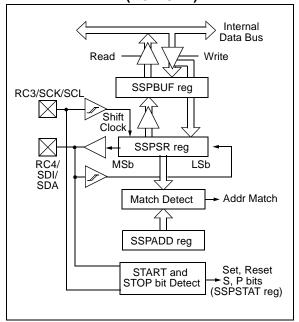

The block diagram of the SSP module, when in SPI mode (Figure 9-1), shows that the SSPSR is not directly readable or writable, and can only be accessed from addressing the SSPBUF register. Additionally, the SSP status register (SSPSTAT) indicates the various status conditions.

FIGURE 9-1:

#### SSP BLOCK DIAGRAM (SPI MODE)

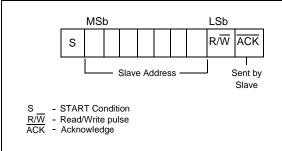

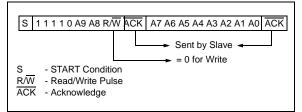

## 9.2.2 ADDRESSING I<sup>2</sup>C DEVICES

There are two address formats. The simplest is the 7-bit address format with a R/W bit (Figure 9-7). The more complex is the 10-bit address with a R/W bit (Figure 9-8). For 10-bit address format, two bytes must be transmitted with the first five bits specifying this to be a 10-bit address.

## FIGURE 9-8:

FORMAT

I<sup>2</sup>C 10-BIT ADDRESS

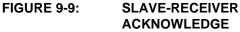

#### 9.2.3 TRANSFER ACKNOWLEDGE

All data must be transmitted per byte, with no limit to the number of bytes transmitted per data transfer. After each byte, the slave-receiver generates an Acknowledge bit (ACK) (see Figure 9-9). When a slave-receiver doesn't acknowledge the slave address or received data, the master must abort the transfer. The slave must leave SDA high so that the master can generate the STOP condition (Figure 9-6).

If the master is receiving the data (master-receiver), it generates an Acknowledge signal for each received byte of data, except for the last byte. To signal the end of data to the slave-transmitter, the master does not generate an Acknowledge (Not Acknowledge). The slave then releases the SDA line so the master can generate the STOP condition. The master can also generate the STOP condition during the Acknowledge pulse for valid termination of data transfer.

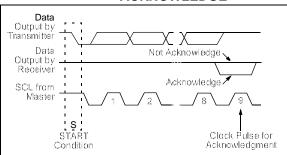

If the slave needs to delay the transmission of the next byte, holding the SCL line low will force the master into a wait state. Data transfer continues when the slave releases the SCL line. This allows the slave to move the received data, or fetch the data it needs to transfer before allowing the clock to start. This wait state technique can also be implemented at the bit level, Figure 9-10. The slave will inherently stretch the clock when it is a transmitter, but will not when it is a receiver. The slave will have to clear the SSPCON<4> bit to enable clock stretching when it is a receiver.

#### FIGURE 9-10: DATA TRANSFER WAIT STATE

## 9.3 SSP I<sup>2</sup>C Operation

The SSP module in  $l^2$ C mode fully implements all slave functions, except general call support, and provides interrupts on START and STOP bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the standard mode specifications as well as 7-bit and 10-bit addressing. Two pins are used for data transfer. These are the RC3/SCK/SCL pin, which is the clock (SCL), and the RC4/SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISC<4:3> bits. The SSP module functions are enabled by setting SSP enable bit, SSPEN (SSPCON<5>).

## FIGURE 9-16: SSP BLOCK DIAGRAM

(I<sup>2</sup>C MODE)

The SSP module has five registers for  $\mathsf{I}^2\mathsf{C}$  operation. These are the:

- SSP Control Register (SSPCON)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with START and STOP bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address), with START and STOP bit interrupts enabled

- I<sup>2</sup>C Firmware controlled Master mode, slave is idle

Selection of any I<sup>2</sup>C mode, with the SSPEN bit set, forces the SCL and SDA pins to be open drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits.

The SSPSTAT register gives the status of the data transfer. This information includes detection of a START or STOP bit, specifies if the received byte was data or address, if the next byte is the completion of 10-bit address, and if this will be a read or write data transfer. The SSPSTAT register is read only.

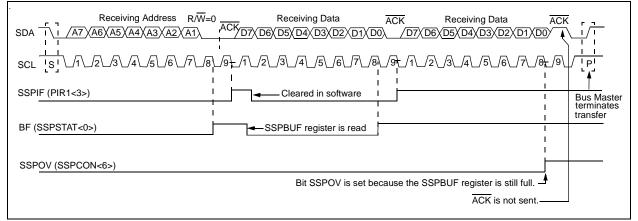

The SSPBUF is the register to which transfer data is written to or read from. The SSPSR register shifts the data in or out of the device. In receive operations, the SSPBUF and SSPSR create a doubled buffered receiver. This allows reception of the next byte to begin before reading the last byte of received data. When the complete byte is received, it is transferred to the SSPBUF register and flag bit SSPIF is set. If another complete byte is received before the SSPBUF register is read, a receiver overflow has occurred and bit SSPOV (SSPCON<6>) is set and the byte in the SSPSR is lost.

The SSPADD register holds the slave address. In 10-bit mode, the user needs to write the high byte of the address (1111 0 A9 A8 0). Following the high byte address match, the low byte of the address needs to be loaded (A7:A0).

### 9.3.1.2 Reception

When the R/W bit of the address byte is clear and an address match occurs, the R/W bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address <u>byte</u> overflow condition exists, then no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set, or bit SSPOV (SSPCON<6>) is set.

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

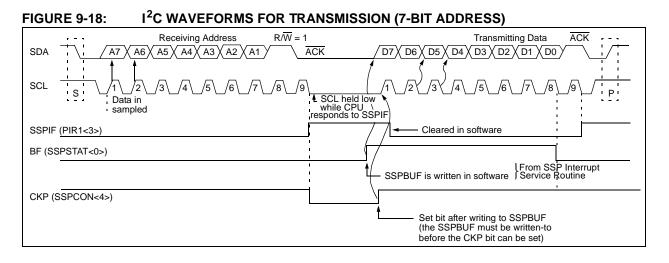

## 9.3.1.3 Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit, and pin RC3/SCK/SCL is held low. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then, pin RC3/SCK/SCL should be enabled by setting bit CKP (SSPCON<4>). The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 9-18). An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF must be cleared in software, and the SSPSTAT register is used to determine the status of the byte. Flag bit SSPIF is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the  $\overline{ACK}$  pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not  $\overline{ACK}$ ), then the data transfer is complete. When the  $\overline{ACK}$  is latched by the slave, the slave logic is reset and the slave then monitors for another occurrence of the START bit. If the SDA line was low ( $\overline{ACK}$ ), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then, pin RC3/SCK/SCL should be enabled by setting bit CKP.

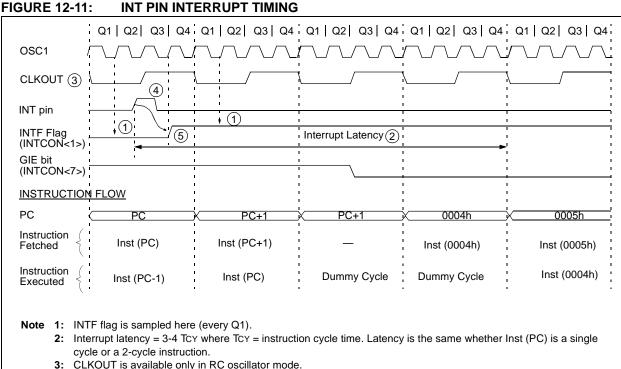

- 3: CLKOUT is available only in RC oscillator mode.

- 4: For minimum width of INT pulse, refer to AC specs.

- 5: INTF can be set any time during the Q4-Q1 cycles.

### 12.5.1 INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered: either rising if bit INTEDG (OPTION\_REG<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit, GIE, decides whether or not the processor branches to the interrupt vector following wake-up. See Section 12.8 for details on SLEEP mode.

### 12.5.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit, TMR0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit, TMR0IE (INTCON<5>) (Section 5.0).

#### 12.5.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit, RBIE (INTCON<4>) (Section 4.2).

| BTFSS             | Bit Test f, Skip if Set                                                          | CALL               | Call Subroutine                                                   |  |  |  |

|-------------------|----------------------------------------------------------------------------------|--------------------|-------------------------------------------------------------------|--|--|--|

| Syntax:           | [ <i>label</i> ]BTFSS f[,b]                                                      | Syntax:            | [ <i>label</i> ] CALL k                                           |  |  |  |

| Operands:         | $0 \le f \le 127$                                                                | Operands:          | $0 \le k \le 2047$                                                |  |  |  |

|                   | $0 \le b < 7$                                                                    | Operation:         | (PC)+ 1 $\rightarrow$ TOS,                                        |  |  |  |

| Operation:        | skip if (f <b>) = 1</b>                                                          |                    | $k \rightarrow PC < 10:0>,$                                       |  |  |  |

| Status Affected:  | None                                                                             |                    | $(PCLATH{<}4:3{>}) \rightarrow PC{<}12:11{>}$                     |  |  |  |

| Encoding:         | 01 11bb bfff ffff                                                                | Status Affected:   | None                                                              |  |  |  |

| Description:      | If bit 'b' in register 'f' is '0', then the                                      | Encoding:          | 10 Okkk kkkk kkkk                                                 |  |  |  |

|                   | next instruction is executed.                                                    | Description:       | Call Subroutine. First, return                                    |  |  |  |

|                   | If bit 'b' is '1', then the next instruc-<br>tion is discarded and a NOP is exe- |                    | address (PC+1) is pushed onto the stack. The eleven-bit immediate |  |  |  |

|                   | cuted instead, making this a 2TCY                                                |                    | address is loaded into PC bits                                    |  |  |  |

|                   | instruction.                                                                     |                    | <10:0>. The upper bits of the PC are                              |  |  |  |

| Words:            | 1                                                                                |                    | loaded from PCLATH. CALL is a two-cycle instruction.              |  |  |  |

| Cycles:           | 1(2)                                                                             | Words:             | 1                                                                 |  |  |  |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                      | Cycles:            | 2                                                                 |  |  |  |

|                   | Decode Read Process No                                                           | -                  | 2<br>Q1 Q2 Q3 Q4                                                  |  |  |  |

|                   | register 'f' data Operation                                                      | Q Cycle Activity:  | r                                                                 |  |  |  |

| If Skip:          | (2nd Cycle)                                                                      |                    | Read<br>Iiteral 'k', Process Write to                             |  |  |  |

|                   | Q1 Q2 Q3 Q4                                                                      | 1st Cycle          | Decode Push PC data PC                                            |  |  |  |

|                   | No No No No                                                                      |                    | to Stack                                                          |  |  |  |

|                   | Operation Operation Operation                                                    | 2nd Cycle          | No No No No<br>Operation Operation Operation                      |  |  |  |

|                   |                                                                                  |                    |                                                                   |  |  |  |

| Example           | HERE BTFSC FLAG,1<br>FALSE GOTO PROCESS CODE                                     | Example            | HERE CALL THERE                                                   |  |  |  |

|                   | TRUE •                                                                           | Before Instru      |                                                                   |  |  |  |

|                   | :                                                                                | PC                 | = Address HERE                                                    |  |  |  |

| Before Instru     | ction:                                                                           | After Instruction: |                                                                   |  |  |  |

| PC                | = address HERE                                                                   | PC                 | = Address THERE                                                   |  |  |  |

| After Instruct    | ion:                                                                             | TOS                | = Address HERE+1                                                  |  |  |  |

| if FLAG<          | - /                                                                              |                    |                                                                   |  |  |  |

| PC<br>if FLAG<    | = address FALSE<br><1> = 1,                                                      |                    |                                                                   |  |  |  |

| PC                | = address TRUE                                                                   |                    |                                                                   |  |  |  |

| MOVWF                                                             | Move W                  | to f                     |                 |                       |

|-------------------------------------------------------------------|-------------------------|--------------------------|-----------------|-----------------------|

| Syntax:                                                           | [ label ]               | MOVWI                    | F f             |                       |

| Operands:                                                         | $0 \le f \le 12$        | 27                       |                 |                       |

| Operation:                                                        | $(W) \rightarrow (f)$   |                          |                 |                       |

| Status Affected:                                                  | None                    |                          |                 |                       |

| Encoding:                                                         | 00                      | 0000                     | lfff            | ffff                  |

| Description:                                                      | Move dat<br>register 'f |                          | V register      | to                    |

| Words:                                                            | 1                       |                          |                 |                       |

| Cycles:                                                           | 1                       |                          |                 |                       |

| Q Cycle Activity:                                                 | Q1                      | Q2                       | Q3              | Q4                    |

|                                                                   | Decode                  | Read<br>register<br>'f'  | Process<br>data | Write<br>register 'f' |

| Example                                                           | MOVWF                   | OPTIC                    | N_REG           |                       |

| Before Instruct<br>OPTION<br>W<br>After Instructio<br>OPTION<br>W | = 0<br>= 0              | xFF<br>x4F<br>x4F<br>x4F |                 |                       |

| NOP               | No Oper   | ation           |                 |                 |

|-------------------|-----------|-----------------|-----------------|-----------------|

| Syntax:           | [ label ] | NOP             |                 |                 |

| Operands:         | None      |                 |                 |                 |

| Operation:        | No opera  | ation           |                 |                 |

| Status Affected:  | None      |                 |                 |                 |

| Encoding:         | 00        | 0000            | 0xx0            | 0000            |

| Description:      | No opera  | ation.          |                 |                 |

| Words:            | 1         |                 |                 |                 |

| Cycles:           | 1         |                 |                 |                 |

| Q Cycle Activity: | Q1        | Q2              | Q3              | Q4              |

|                   | Decode    | No<br>Operation | No<br>Operation | No<br>Operation |

|                   |           |                 |                 |                 |

Example

NOP

| OPTION           | Load Option Register                                                                                                                                                                                                                                         |      |      |        |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|--------|

| Syntax:          | [ label ] OPTION                                                                                                                                                                                                                                             |      |      |        |

| Operands:        | None                                                                                                                                                                                                                                                         |      |      |        |

| Operation:       | $(W) \rightarrow OPTION$                                                                                                                                                                                                                                     |      |      |        |

| Status Affected: | None                                                                                                                                                                                                                                                         |      |      |        |

| Encoding:        | 0 0                                                                                                                                                                                                                                                          | 0000 | 0110 | 0010   |

| Description:     | escription: The contents of the W register are<br>loaded in the OPTION register.<br>This instruction is supported for<br>code compatibility with PIC16C5X<br>products. Since OPTION is a<br>readable/writable register, the user<br>can directly address it. |      |      |        |

| Words:           | 1                                                                                                                                                                                                                                                            |      |      |        |

| Cycles:          | 1                                                                                                                                                                                                                                                            |      |      |        |

| Example          |                                                                                                                                                                                                                                                              |      |      |        |

|                  | To maintain upward compatibility<br>with future PIC16CXXX products,<br>do not use this instruction.                                                                                                                                                          |      |      | ducts, |

|                  |                                                                                                                                                                                                                                                              |      |      |        |

REG1 = 1110 0110 W = 1100 1100

= 1

С

| RETURN            | Return from Subroutine                                                                                          | RLF               | Rotate Left f through Carry                                                                                                     |

|-------------------|-----------------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Syntax:           | [label] RETURN                                                                                                  | Syntax:           | [ <i>label</i> ] RLF f[,d]                                                                                                      |

| Operands:         | None                                                                                                            | Operands:         | $0 \le f \le 127$                                                                                                               |

| Operation:        | $TOS \rightarrow PC$                                                                                            |                   | d ∈ [0,1]                                                                                                                       |

| Status Affected:  | None                                                                                                            | Operation:        | See description below                                                                                                           |

| Encoding:         | 00 0000 0000 1000                                                                                               | Status Affected:  | С                                                                                                                               |

| Description:      | Return from subroutine. The stack is                                                                            | Encoding:         | 00 1101 dfff ffff                                                                                                               |

|                   | POPed and the top of the stack (TOS)<br>is loaded into the program counter.<br>This is a two-cycle instruction. | Description:      | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0, the result is placed in |

| Words:            | 1                                                                                                               |                   | the W register. If 'd' is 1, the result is stored back in register 'f'.                                                         |

| Cycles:           | 2                                                                                                               |                   | C ← C ← Register f ←                                                                                                            |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                     |                   |                                                                                                                                 |

| 1st Cycle         | Decode No No Pop from Operation Operation                                                                       | Words:<br>Cycles: | 1<br>1                                                                                                                          |

| 2nd Cycle         | No No No No<br>Operation Operation Operation                                                                    | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                     |

| Example           | RETURN                                                                                                          |                   | Decode Read<br>register<br>'f' Process Write to<br>data destination                                                             |

| After Interrup    | t:                                                                                                              |                   |                                                                                                                                 |

| PC =              | TOS                                                                                                             | Example           | RLF REG1,0                                                                                                                      |

|                   |                                                                                                                 |                   | <b>tion:</b><br>= 1110 0110<br>= 0                                                                                              |

|                   |                                                                                                                 | After Instruction | on:                                                                                                                             |

NOTES:

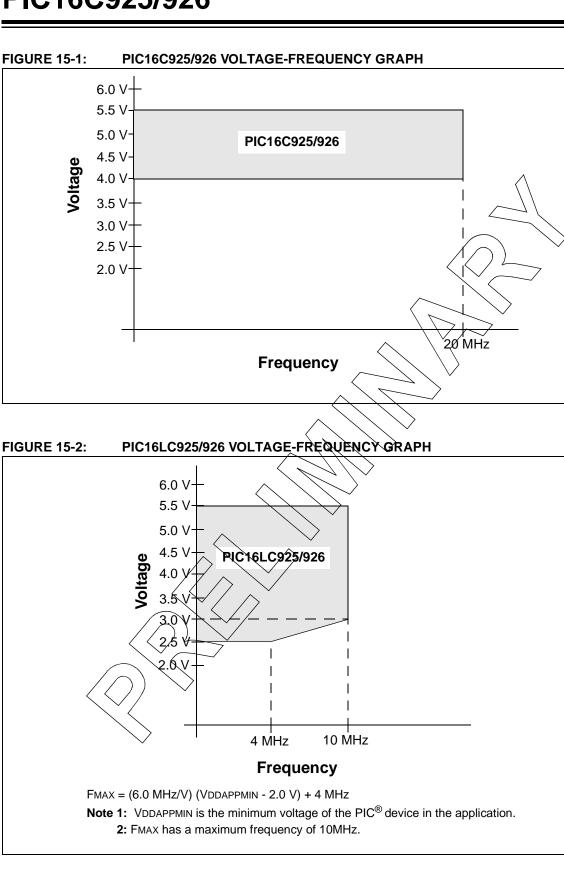

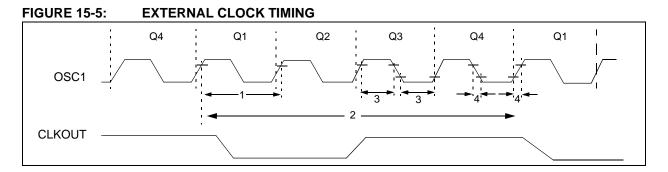

# 15.3 Timing Parameter Symbology

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2ppS                                          |                                  | 3. Тсс:sт (I <sup>2</sup> | 3. Tcc:st (I <sup>2</sup> C specifications only) |  |  |  |

|------------------------------------------------------|----------------------------------|---------------------------|--------------------------------------------------|--|--|--|

| 2. TppS 4. Ts (I <sup>2</sup> C specifications only) |                                  |                           |                                                  |  |  |  |

| Т                                                    |                                  |                           |                                                  |  |  |  |

| F                                                    | Frequency                        | Т                         | Time                                             |  |  |  |

| Lowercase                                            | letters (pp) and their meanings: |                           |                                                  |  |  |  |

| рр                                                   |                                  |                           |                                                  |  |  |  |

| сс                                                   | CCP1                             | osc                       | OSC1                                             |  |  |  |

| ck                                                   | CLKOUT                           | rd                        | RD                                               |  |  |  |

| cs                                                   | CS                               | rw                        | RD or WR                                         |  |  |  |

| di                                                   | SDI                              | SC                        | SCK                                              |  |  |  |

| do                                                   | SDO                              | SS                        | SS                                               |  |  |  |

| dt                                                   | Data in                          | tO                        | TOCKI                                            |  |  |  |

| io                                                   | I/O port                         | t1                        | T1CKI                                            |  |  |  |

| mc                                                   | MCLR                             | wr                        | WR                                               |  |  |  |

| Uppercase                                            | letters and their meanings:      |                           |                                                  |  |  |  |

| S                                                    |                                  |                           |                                                  |  |  |  |

| F                                                    | Fall                             | Р                         | Period                                           |  |  |  |

| н                                                    | High                             | R                         | Rise                                             |  |  |  |

| I                                                    | Invalid (Hi-impedance)           | V                         | Valid                                            |  |  |  |

| L                                                    | Low                              | Z                         | Hi-impedance                                     |  |  |  |

| I <sup>2</sup> C only                                |                                  |                           |                                                  |  |  |  |

| AA                                                   | output access                    | High                      | High                                             |  |  |  |

| BUF                                                  | Bus free                         | Low                       | Low                                              |  |  |  |

| TCC:ST (I <sup>2</sup> C                             | specifications only)             | <u> </u>                  |                                                  |  |  |  |

| CC                                                   |                                  |                           |                                                  |  |  |  |

| HD                                                   | Hold                             | SU                        | Setup                                            |  |  |  |

| ST                                                   |                                  |                           |                                                  |  |  |  |

| DAT                                                  | DATA input hold                  | STO                       | STOP condition                                   |  |  |  |

| STA                                                  | START condition                  |                           |                                                  |  |  |  |

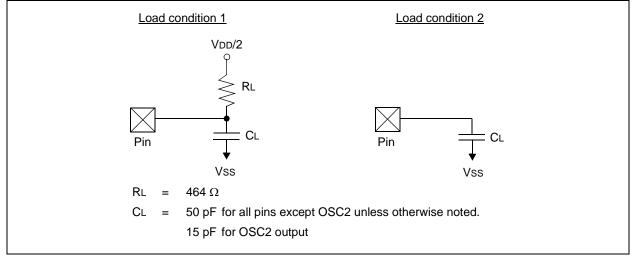

## FIGURE 15-4: LOAD CONDITIONS

## **15.4** Timing Diagrams and Specifications

#### TABLE 15-3: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                   | Min  | Тур†           | Max                           | Units             | Conditions         |

|------------------|-------|----------------------------------|------|----------------|-------------------------------|-------------------|--------------------|

|                  | Fosc  | External CLKIN Frequency         | DC   |                | 4                             |                   | XT and RC osc mode |

|                  |       | (Note 1)                         | DC   | —              | 20                            | MHz               | HS osc mode        |

|                  |       |                                  | DC   | —              | 200                           | (k₩z)             | LP osc mode        |

|                  |       | Oscillator Frequency             | DC   | —              | 4                             | MHz<              | RC osc mode        |

|                  |       | (Note 1)                         | 0.1  | —              | 4                             | MHZ               | XT osc mode        |

|                  |       |                                  | 4    | —              | _20 \`                        | ∕ <b>j∕it</b> Hz∕ | HS osc mode        |

|                  |       |                                  | 5    | —              | 200                           | kHz               | LP osc mode        |

| 1                | Tosc  | External CLKIN Period            | 250  | <              |                               | , ns              | XT and RC osc mode |

|                  |       | (Note 1)                         | 125  |                | $\langle \mathcal{F} \rangle$ | ns                | HS osc mode        |

|                  |       |                                  | 5    | $\langle \not$ | $\searrow$                    | μS                | LP osc mode        |

|                  |       | Oscillator Period                | 250  | A              | >`−                           | ns                | RC osc mode        |

|                  |       | (Note 1)                         | 250  | $\searrow$     | 10,000                        | ns                | XT osc mode        |

|                  |       |                                  | 125  | $\searrow$     | 250                           | ns                | HS osc mode        |

|                  |       | $\land$                          | 5    | >–             | —                             | μS                | LP osc mode        |

| 2                | Тсү   | Instruction Cycle Time (Note 1)  | 500> | _              | DC                            | ns                | TCY = 4/FOSC       |

| 3                | TosL, | External Clock in (OSC1) High or | 50   | —              | —                             | ns                | XT oscillator      |

|                  | TosH  | Low Time                         | 2.5  | —              | —                             | μS                | LP oscillator      |

|                  |       |                                  | 10   | —              | —                             | ns                | HS oscillator      |

| 4                | TosR, | External Clock in (OSC1) Rise or | _    | _              | 25                            | ns                | XT oscillator      |

|                  | TosF  | Fall Time                        | —    | —              | 50                            | ns                | LP oscillator      |

|                  |       |                                  | —    | —              | 15                            | ns                | HS oscillator      |

† Data in "Typ" column is at 5 以25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin.

When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

## Package Marking Information (Continued)

68-Lead CERQUAD Windowed

Example

## **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| TO:<br>RE: | Technical Publications Manager<br>Reader Response                                           | Total Pages Sent            |  |  |  |  |  |

|------------|---------------------------------------------------------------------------------------------|-----------------------------|--|--|--|--|--|

|            | : Name                                                                                      |                             |  |  |  |  |  |

| FIOIII     |                                                                                             |                             |  |  |  |  |  |

|            | Company<br>Address                                                                          |                             |  |  |  |  |  |

|            | City / State / ZIP / Country                                                                |                             |  |  |  |  |  |

|            | Telephone: ()                                                                               | FAX: ()                     |  |  |  |  |  |

| Applie     | cation (optional):                                                                          |                             |  |  |  |  |  |

| Would      | d you like a reply?YN                                                                       |                             |  |  |  |  |  |

| Devic      |                                                                                             | Literature Number: DS39544B |  |  |  |  |  |

| Ques       | tions:                                                                                      |                             |  |  |  |  |  |

| 1. V       | 1. What are the best features of this document?                                             |                             |  |  |  |  |  |

|            |                                                                                             |                             |  |  |  |  |  |

| 2. H       | 2. How does this document meet your hardware and software development needs?                |                             |  |  |  |  |  |

| _          |                                                                                             |                             |  |  |  |  |  |

| _          |                                                                                             |                             |  |  |  |  |  |

| 3. D       | 3. Do you find the organization of this document easy to follow? If not, why?               |                             |  |  |  |  |  |

|            |                                                                                             |                             |  |  |  |  |  |

| 4. V       | 4. What additions to the document do you think would enhance the structure and subject?     |                             |  |  |  |  |  |

| _          |                                                                                             |                             |  |  |  |  |  |

|            |                                                                                             |                             |  |  |  |  |  |

| 5. V       | 5. What deletions from the document could be made without affecting the overall usefulness? |                             |  |  |  |  |  |

|            |                                                                                             |                             |  |  |  |  |  |

| 6. Is      | there any incorrect or misleading information (what and                                     | where)?                     |  |  |  |  |  |

|            |                                                                                             |                             |  |  |  |  |  |

| 7. H       | ow would you improve this document?                                                         |                             |  |  |  |  |  |

|            |                                                                                             |                             |  |  |  |  |  |

| -          |                                                                                             |                             |  |  |  |  |  |